Диодно-транзисторная логика — Википедия

Материал из Википедии — свободной энциклопедии

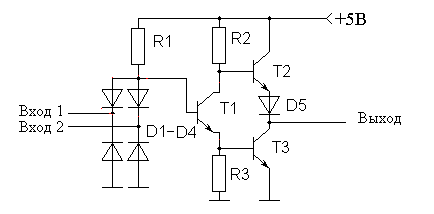

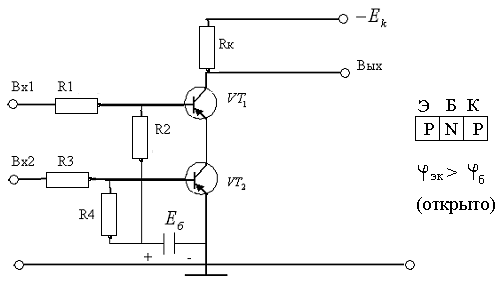

Текущая версия страницы пока не проверялась опытными участниками и может значительно отличаться от версии, проверенной 7 октября 2017; проверки требует 1 правка. Текущая версия страницы пока не проверялась опытными участниками и может значительно отличаться от версии, проверенной 7 октября 2017; проверки требует 1 правка. Упрощённая схема двухвходового ДТЛ-элемента 2И-НЕ.

Упрощённая схема двухвходового ДТЛ-элемента 2И-НЕ.Диодно-транзисторная логика (ДТЛ), англ. Diode–transistor logic (DTL) — технология построения цифровых схем на основе биполярных транзисторов, диодов и резисторов. Своё название технология получила благодаря реализации логических функций (например, 2И) с помощью диодных цепей, а усиления и инверсии сигнала — с помощью транзистора (для сравнения см. резисторно-транзисторная логика и транзисторно-транзисторная логика).

Показанная на рисунке схема представляет собой типичный элемент 2И-НЕ.

Если хотя бы на одном из входов уровень логического нуля, то ток течёт через R1 и диод во входную цепь. На анодах диодов напряжение 0,7 В, которого недостаточно для открывания транзистора. Транзистор закрыт. На выходе формируется уровень логической единицы.

Если на все входы поступает уровень логической единицы, ток течёт через R1 на базу транзистора, образуя на анодах диодов напряжение 1,4 В. Поскольку напряжение уровня логической единицы больше этой величины, входы диодов обратносмещены и не участвуют в работе схемы. Транзистор открыт в режиме насыщения. В транзистор втекает ток нагрузки, по величине значительно больший тока нагрузки в состоянии логической единицы.

Основное преимущество ДТЛ перед более ранней технологией РТЛ — возможность создания большого числа входов. Задержка прохождения сигнала по-прежнему достаточно высока, из-за медленного процесса утечки заряда с базы в режиме насыщения (когда все входы имеют высокий уровень) при подаче на один из входов низкого уровня. Эту задержку можно уменьшить подключением базы транзистора через резистор к общему проводу или к источнику отрицательного напряжения.

Логический элемент 3И-НЕ в серии микросхем 74LS(К555)[1]В более современной и эффективной технологии ТТЛ данная проблема решена путём замены диодов на мультиэмиттерный транзистор. Это также уменьшает площадь кристалла (в случае реализации в виде интегральной схемы), и соответственно позволяет добиться более высокой плотности элементов.

Однако в ещё более современных и эффективных микросхемах ТТЛ (74S, 74LS, 74AS, 74ALS, 74F) с диодами Шоттки (ТТЛШ, ТТЛ Шоттки), фактически произошёл возврат к ДТЛ, на основе новой технологии — диодах и транзисторах Шоттки[1]. Эти серии многоэмиттерного транзистора не содержат, фактически являются ДТЛ, и носят название ТТЛ (ТТЛШ) лишь «по традиции», будучи развитием именно ДТЛ.

Часто используются в декодерах для управления разными устройствами. Логические элементы на основе ДТЛ являлись основой для многих ЭВМ второго поколения, например БЭСМ-6, IBM 1401, и др.

Серии ДТЛ-микросхем отечественного производства[править | править код]

- В СССР выпускались серии 104, 109, 121, 128, 146, 156, 205, 215, 217, 218, 221, 240, 511 (и соответствующие им с индексом «К» в начале условного обозначения) микросхем широкого применения.[2]

Как создать схему? | Volt-info

Введение

Эта статья написана для начинающих радиолюбителей, имеющих смутное представление о работе электронных схем, имеет много повторяющихся моментов и может показаться слишком скучной для тех, кто уже имеет определённый опыт работы в схемотехнике. Продвинутым электронщикам читать точно не рекомендую – ни чего нового, и скучно. Начинающим советую воспользоваться лишней возможностью пополнить свой багаж знаний и опыта.

Источники сигналов

В радиолюбительской практике источники сигналов играют весьма немаловажную роль. Их можно смело ставить в ряды инструментария первой необходимости радиолюбительской лаборатории на один уровень с измерительными приборами. На практике, большинство электронных схем, а особенно сегодня, в век цифровых технологий, связано с обработкой сигналов различной формы. Чтобы удачно спроектировать и реализовать даже не сложную схему, содержащую два и более функциональных блоков, на этапе проектирования желательно собрать каждый из блоков на отдельном макете и убедиться в его работоспособности, а заодно и скорректировать те или иные номиналы деталей, рабочие характеристики компонент и т.д. Часто работа таких блоков зависит от подачи на них сигналов конкретной либо произвольной формы, будь то усилитель низких, или высоких частот, силовые ключи преобразователей, или даже элементарного электромагнитного реле. Но где их взять, если устройство ещё не закончено. Конечно же, лучший способ, это использовать готовый источник сигналов, а если его нет, то сделать его самому, чем мы и займёмся в рамках данной статьи.

В зависимости от того, какой формы, периодичности и амплитуды требуется получить сигнал, генерирующие их устройства должны иметь свои особенности, поэтому для начала мы рассмотрим множество простых устройств, дающих понимание принципов действия. Более сложные устройства в дальнейшем спроектировать или собрать по готовой схеме Вы сможете уже самостоятельно.

Логический элемент «НЕ» на одном транзисторе

Рисунок 1. Логический элемент «НЕ» на транзисторе.

Напомню, как работает транзистор, если рассматривать его с точки зрения простого логического элемента.

Условимся, что Uп, это у нас напряжение источника питания относительно минуса питания, или корпуса, к которому подпаяны общие выводы входа и выхода. Мы будем рассматривать его величину, как логическую единицу, а напряжение, приближенное (сниженное) к минусу питания – логический ноль.

При включении питания на выводе Q1 устанавливается логическая единица, поскольку транзистор закрыт (не пропускает ток), и на его коллектор через резистор R2 подано напряжение питания.

Подадим на вход X1 напряжение логической единицы, тогда через резистор R1 и переход транзистора база-эмиттер потечёт ток, который называют током базы. При этом слой базы насытится электронами, коллекторный переход станет проводить ток, т.е. транзистор откроется, и на его коллекторе напряжение упадёт почти до нуля, при этом на выходе Q1 установится логический ноль. Усвоили? Теперь давайте короче, чтобы не отвлекаться на механику процессов:

— При подаче на вход X1 логической единицы, на выходе Q1 установится логический ноль;

— при подаче на вход X1 логического нуля, на выходе Q1 установится логическая единица.

Если сделать табличку и свести в неё возможные состояния входов и соответствующих этим состояниям состояния выходов, то мы получим перечень состояний, который обычно называется таблицей истинности логического устройства. У нас она получится проще некуда:

Входы | Выходы |

X1 | Q1 |

1 | 0 |

0 | 1 |

Если вы ещё не заметили, обращаю Ваше внимание на то, что выход схемы как бы переворачивает входной сигнал. Такое поведение называется логической инверсией, или просто инверсией.

И так, мы заметили, что пока через базу транзистора течёт ток, он открыт (условно можно сказать, что цепь коллектор-эмиттер закорочена), а на выходе схемы устанавливается напряжение, близкое к минусу источника питания. Когда напряжение на базе снижено до такой степени, что через неё прекращает течь ток, транзистор закрывается, переход коллектор-эмиттер становится электрически не проводящим, и на коллекторе через резистор R2 устанавливается напряжение, близкое к напряжению положительного вывода источника питания.

Теперь рассмотрим ещё несколько простых схем на пассивных элементах.

RC цепи задержки.

На рисунке 2-а) конденсатор включен параллельно выходу. Когда конденсатор разряжен, напряжение на выходе приближено к нулю, т.е. к минусу источника питания. При подаче на вход напряжения плюса источника питания, конденсатор начнёт заряжаться, и напряжение на нём будет расти не мгновенно, а по мере заряда. Чем больше сопротивление резистора R1, тем медленней будет проходить зарядка. Но по истечению некоторого времени, напряжение на конденсаторе приблизится по значению к напряжению, поданному на вход X1. Такой своеобразный эффект задержки сигнала дал название этим схемам.

Рисунок 2. RC-цепи.

Когда конденсатор заряжен, на выходе Q1 присутствует напряжение. Если мы на входе X1 снизим напряжение до нуля (замкнём вход), то конденсатор начнёт разряжаться, а напряжение на нём будет снижаться не сразу, а постепенно с течением времени. Чем больше сопротивление резистора R1, тем медленней будет происходить разрядка конденсатора и тем длительнее будет происходить процесс установления выходного сигнала.

На рисунке б) схема несколько изменена. При разряженном конденсаторе и нулевом напряжении на входе, на выходе будет ноль. При подаче напряжения на вход X1, через резистор R1 конденсатор C1 начнёт заряжаться. Поскольку напряжение на конденсаторе не может подняться быстро, а лишь по мере заряда, то в первоначальный момент времени на резисторе R1 возникнет напряжение, поданное на вход, и тут же начнёт снижаться по мере заряда конденсатора. Напряжение на резисторе пропорционально току заряда конденсатора и будет убывать с той же скоростью, с какой будет нарастать напряжение на конденсаторе.

Когда конденсатор заряжен, на выходе Q1 устанавливается ноль. Если теперь напряжение на входе снизить до нуля (замкнуть вход), то всё напряжение заряженного конденсатора приложится к резистору R1 и сразу же начнёт снижаться по мере разряда конденсатора. Здесь важно заметить, что импульс этого напряжения будет иметь отрицательную полярность относительно общего вывода (минуса источника питания), а почему, постарайтесь догадаться сами. Если эта задачка Вам по зубам – двигаемся дальше.

Если есть желание наглядно изучить работу описанных выше схем, и у Вас случайно оказался в наличии осциллограф, да ещё двухлучевой, предлагаю немного модернизировать рассмотренные схемы для удобства проведения опытов, рисунок 3.

Рисунок 3. Тестовые схемы для практических опытов.

Если у Вас пока ещё нет осциллографа, в опытах можно использовать два вольтметра.

Общий щуп осциллографа (корпус) подключается к любому общему выводу схемы. Тестовый щуп первого канала осциллографа подключается к зажиму «А», второй – к зажиму «Б». Аналогично подключаются щупы первого и второго вольтметра, но при этом общие щупы вольтметра должны быть подключены к общим выводам устройства. Напряжение источника питания может быть и ниже указанного, вплоть до 3 В, это повлияет лишь на характер измеряемых сигналов, но тенденция останется неизменной.

Если вы сравните рассмотренные ранее схемы и представленные на рисунке 3, то заметите некоторые дополнения. Они следующие. Rб – балластное сопротивление, необходимо для имитации на входе логической единицы, подаваемой от источника питания. Выключатель SA1 необходим для имитации логического нуля на входе, замыканием выводов. При замыкании выводов ток выключателя ограничивается балластным сопротивлением Rб, предотвращая короткое замыкание в схеме.

Таким образом, включая и выключая выключатель SA1 вы можете имитировать входной сигнал устройства. А теперь собирайте схему, подключайте приборы, включайте питание, и поехали…

При должной настройке осциллографа, вы сможете наблюдать картинки, аналогичные следующим:

а) б) в)

Рисунок 4. Диаграммы входных и выходных сигналов тестовых схем, рассмотренных на рисунке 3 соответственно — а), б) и в).

Диаграммы на рисунке 4 соответствует сигналам, получаемым при тестировании схемы на рисунке 3.

Из того, что мы теперь знаем, уже можно кое что сделать.

Таймер включения

Давайте слегка модернизируем нашу транзисторную схему как показано на рисунке 5.

Транзистор VT1 выполняет роль электронного ключа, управляющего нагрузкой с помощью силового реле, включенного параллельно резистору R2, который в данной схеме можно было бы исключить.

а) б) в)

Рисунок 5. а) Схема, имитирующая таймер отключения нагрузки; б) момент включения нагрузки при подаче логической единицы на вход таймера; в) момент разрядки конденсатора при подаче логического нуля на вход таймера.

При включении питания конденсатор C1 находится в разряженном состоянии, ток базы отсутствует, транзистор закрыт, через обмотку реле не протекает ток, контакты реле разомкнуты, лампа Л1 не включена. В данной схеме реализована имитация подачи логических сигналов с помощью двухпозиционного выключателя с перекидными контактами. В одном из состояний выключатель замыкает вход схемы на корпус (минус источника питания), при этом, если конденсатор был заряжен, то разрядится через резистор R1 и коммутирующий диод VD1 (рисунок 5 в).

При подаче на вход схемы логической единицы (рис. 5 б), разряженный конденсатор начинает заряжаться по цепочке R1 от плюса источника питания и база-эмиттер VT1 от минуса. При этом, через базу VT1 протекает ток заряда, транзистор открывается, через R2 и реле К1 начинает протекать ток, реле срабатывает, включая лампу Л1. С течением времени конденсатор C1 заряжается, зарядный ток через базу транзистора снижается, достигая значения, не достаточного для насыщения базы транзистора, транзистор закрывается, реле отключает лампу Л1. Дальнейшее присутствие на входе схемы логической единицы уже не грает роли, поскольку конденсатор заряжен и ток через него больше не потечёт.

Для приведения схемы в состояние готовности необходимо разрядить конденсатор. Для этого переводим выключатель SA1 в положение контакта, замыкающего вход на корпус. Конденсатор разрядится через R1 и VD1.

Чем больше будет ёмкость конденсатора в данной схеме, тем дольше он будет заряжаться, и соответственно, тем больше будет задержка времени до отключения нагрузки. Соответственно, чем больше сопротивление R1, тем меньше будет ток заряда, что тоже увеличит выдержку времени, но при этом необходимо учитывать условие, что ток заряда должен быть не меньше требуемого тока насыщения транзистора, в противном случае транзистор может не включить реле.

Диод VD1 в данной схеме принципиально важен, поскольку именно через него разряжается конденсатор, так как при входе, замкнутом на корпус, на базе возникнет напряжение заряда со знаком минус относительно эмиттера (обратите внимание на полярность заряда конденсатора). Такое напряжение является обратным смещением для p-n переход транзистора, при котором переход закрыт, а соответственно, конденсатор не будет иметь возможности разрядиться.

На выходе схемы Q1 мы получим инверсию сигнала включенной лампы Л1, т.е. пока лампа включена, на выходе логический ноль, когда лампа выключена – единица.

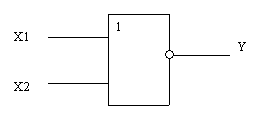

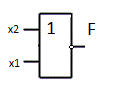

Логический повторитель

И так, теперь мы знаем, что операция «НЕ» инвертирует логические уровни напряжений, т.е. логическая единица на входе соответствует логическому нулю на выходе элемента, и соответственно, входному нулю отвечает единица на выходе. Если мы обработаем входной сигнал последовательно двумя элементами «НЕ», то на выходе второго элемента получим сигнал, повторяющий состояния входа первого. И действительно, если автомобиль сделает два разворота, то будет двигаться в том же направлений, как и до маневрирования. Казалось бы, зачем нужна операция, которая в результате даёт то же, что мы уже имели? На практике это применяется с большой пользой.

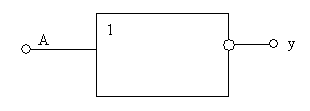

Рисунок 6. Логический повторитель.

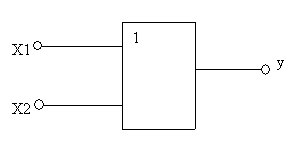

Соединяем последовательно два элемента «НЕ», рисунок 6. X1 – вход, Q1 – инверсный выход и одновременно вход второго элемента «НЕ» на транзисторе VT2, Q2 – выход. В результате получаем устройство, которое на выход выдаёт сигнал, повторяющий входной. Эту повторюшку будем называть логическим повторителем. Такие элементы на схемах обозначаются единичкой – «1».

При подаче питания на схему, транзистор VT2 открывается током базы через резисторы R2-R3, на выходе Q2 устанавливается ноль. При подаче сигнала единицы на X1, транзистор VT1 «садит» резистор R3 на корпус, VT2 закрывается, на выходе Q2 устанавливается единица. При снятии сигнала со входа выход сбрасывается в ноль.

Интересно, что получится, если мы подадим сигнал выхода на вход? Давайте посмотрим, рисунок 7.

Рисунок 7. Подача выходного сигнала на вход.

В данной схеме можно заметить, что входы смешались с выходами, и вообще наша схема как-то закольцевалась. Для большей наглядности предлагаю упростить схему.

Рисунок 8. Преобразованная схема.

На рисунке 8 преобразованная схема. Входы я не стал показывать, поскольку не имеет смысла, они замкнуты с выходами, и изобразил я только их. Рассмотрим поведение схемы в работе.

При включении питания оба транзистора должны открыться током базы через резисторы R4-R1 и R2-R3. Но, поскольку открывающийся транзистор одного плеча схемы «подтягивает» базовый резистор транзистора другого плеча к корпусу, а говоря словами цифровых сигналов – к нулю, то оба транзистора должны открыться лишь до некоторого уравновешенного значения, а сигналы на выходах принять промежуточное значение напряжения между единицей и нулём. Но на практике симметрия процессов даже в такой симметричной схеме не достижима, и в результате один из транзисторов открываясь чуть сильнее другого ускорит процесс разбаланса схемы, в результате один из транзисторов откроется полностью, другой закроется. Это состояние схемы устойчиво без воздействия извне. При соблюдении симметрии в выборе номиналов деталей, угадать, какой транзистор первым окажется открыт невозможно, а при очень точной подгонке номиналов, результаты запуска схемы могут отличаться случайным образом. Чтобы исключить элемент случайности в таком случае, достаточно внести ассиметрию в номиналы схемы. Например, если сопротивления R1 и R4 выбрать на одну-две ступени меньше, чем R2 и R3, то в результате большего тока базы транзистор VT1 при включении питания всегда будет открываться первым, на выходе Q1 будет устанавливаться «0», на Q2 – «1». При постоянно включенном питании состояние такой схемы будет всегда стабильно, но при этом она бесполезна. Давайте добавим в эту схему кое какие элементы управления.

Триггер

На рисунке 9 изображена схема, которая отличается от предыдущей наличием входных каналов X1-R2 и X2-R5. Рассмотрим работу схемы.

Рисунок 9. Транзисторный триггер.

Так как симметричные элементы схемы на практике имеют некоторые отклонения электрических характеристик, то при включении питания один из транзисторов, например, VT2 будет открываться немного быстрее другого. Открываясь, транзистор VT2 будет подтягивать своим коллектором вывод резистора R3 к «нулю», снижая ток базы транзистора VT1 и закрывая его. В результате этого переходного процесса транзистор VT2 полностью откроется, а VT1 – закроется. На выходах Q1 и Q2 установятся «1» и «0» соответственно. Это состояние устойчиво, но может быть изменено.

Подадим кратковременно логическую единицу на вход X1. Через резистор R2 и базу транзистора VT1 начнет протекать ток, VT1 откроется и подтянет своим коллектором резистор R4 к нулю. Ток через резистор R4 и базу транзистора VT2 прекратится, транзистор VT2 закроется, схема изменить свое состояние на противоположное: на выходах Q1 и Q2 установятся «0» и «1» соответственно. Это состояние будет сохраняться до кратковременной подачи на вход X2 логической единицы.

Схемы, подобным образом изменяющие своё состояние называются «триггерными», а элементы на их основе – триггерами. Один такой элемент представляет из себя элементарную ячейку памяти с возможностью записи и хранения информации в период между включением и выключением питания. Аналогичные элементы содержит оперативная память компьютера.

Рисунок 10. Выключатель нагрузки с применением триггера.

Для примера практического применения этой схемы, немного дополним её. На рисунке 10 мы ввели в схему две кнопки, и конденсатор C1.

При включении питания триггера, конденсатор C1 на некоторое время заряда шунтирует (реализует задержку сигнала) базу транзистора VT2, в результате VT1 открывается первым и фиксирует состояние схемы. Через обмотку реле K1 протекает малый ток базы транзистора VT1, не достаточный для срабатывания реле. Лампа выключена.

Нажатием на кнопку SB2 «Вкл.» на базу транзистора принудительно кратковременно подаётся логическая единица. Конденсатор заряжается, возникает напряжение на базе VT2, от чего транзистор открывается, своим коллектором подтягивая к нулю резистор R3. VT1 закрывается, состояние схемы фиксируется, через обмотку реле K1 протекает номинальный ток реле, контакты реле замыкаются, лампа включается.

Кратковременное нажатие на кнопку SB1 «Выкл.» схема приходит в исходное состояние, лампа выключается.

Вот так, изучая и комбинируя простые элементы схем можно научиться создавать полезные интересные устройства. Последняя схема имеет элементы управления, а функционально лишь фиксирует заданное состояние, или говоря языком электроники – запоминает значение заданного логического уровня. А давайте в следующей своей выдумке подумаем, как сделать устройство без элементов управления, но чтобы оно самостоятельно изменяло состояния логических выходов.

Мультивибратор

Давайте ещё раз обратим внимание на схему рисунка 8 и цепи задержки на рисунке 2.

Рисунок 11. Схема мультивибратора.

Мы знаем, что резисторы в цепи базы транзистора обеспечивают постоянный ток базы, именно поэтому состояния схемы являются устойчивыми. Для того, чтобы схема переключалась сама по себе, воспользуемся возможностями цепей задержки. Для начала в цепи базы вместо резисторов установим конденсаторы (рисунок 11 а). При включении питания конденсаторы C1 и C2 начнут заряжаться через резисторы R1, R2 и базы транзисторов. Транзисторы начнут открываться, но первым откроется тот, у которого ток базы и коэффициент усиления по току в совокупности окажется больше другого. Например, первым открылся VT1 и подтянул своим коллектором конденсатор C1 к нулю, ток через него не течёт. VT1 открыт, VT2 – закрыт.

По мере заряда конденсатора C2 через него прекращает протекать ток базы транзистора VT1 и он начинает закрываться, отвязав от нуля конденсатор C1. C1 начинает заряжаться через резистор R1 и базу VT2, в результате чего VT2 открывается и подтягивает положительно заряженный полюс конденсатора C2 к нулю. Отрицательно заряженный полюс C2 создаёт обратное смещение на переходе база-эмиттер, переход закрыт, конденсатор остаётся заряженным. Когда заряд C1 прекращается, ток базы VT2 прекращается, транзистор закрывается и отвязывает положительно заряженный вывод C2, а поскольку С2 уже заряжен, как и C1, то через них уже не будет протекать ток, и они больше не смогут воздействовать на транзисторы. Такая схема способна произвести всего один такт переключения состояний, а её применение ограничено из-за невозможности быстрого разряда конденсаторов, что бы схему можно было использовать повторно через короткие промежутки времени.

Подключим к базам транзисторов сопротивления R3 и R4 (рисунок 11 б), которые будут создавать положительное (открывающее транзистор) смещение базы относительно коллектора. При включении питания, один из транзисторов, например, VT1 открывается током базы, обусловленным суммарным током заряда конденсатора C2 и резистора R4. В это время конденсатор C1, подтянутый к нулю, будет заряжаться резистором R3, и по мере заряда конденсатора создаст на базе VT2 положительное смещение, достаточное для его открывания. Открываясь, VT2 начнёт подтягивать положительно заряженный вывод конденсатора к нулю, а отрицательно заряженный вывод C2 ещё не успевшего перезарядиться, создаст отрицательное смещение на базе VT1, закрыв его. Эти процессы переключения транзисторов и перезарядки конденсаторов чередуются непрерывно. Время переключения происходит очень быстро, а времена между переключениями зависят от ёмкостей конденсаторов и номиналов сопротивлений схемы.

Такая схема позволяет формировать периодический сигнал на выходе в автоматическом режиме, который ещё называют автогенераторным. Но у подобных схем есть механический предшественник – устройство с вибрирующим контактом, который за счёт механической вибрации мог с определённой периодичностью замыкать и размыкать контакты, или поочерёдно переключать контакт между двумя другими. Эти устройства вполне обоснованно получили название мультивибраторов, а их электронные последователи уже просто позаимствовали это название.

Заключение

Некоторые могут посчитать статью неполной в виду отсутствия диаграмм, графиков и таблиц там, где их можно показать и т.д. Во-первых, это сделано с целью сократить объём, поскольку и так «многа букаф», тяжело читать, но главная задача, это дать возможность читателю самостоятельно приложить полученные знания в одном месте к тем местах, где это уместно, это даст возможность немного развивить мышление, иначе смысла во всей этой писанине нет.

Этот небольшой экскурс написан специально для самых начинающих радиолюбителей, чтобы показать, что нет ни чего сложного в понимании принципов работы различных электронных устройств, и более того, нет причин не научиться изобретать такие устройства самостоятельно. Если у меня не получилось что-то объяснить, приму любую критику в Ваших комментариях и готов буду доработать статью. Если эта статья показала Вам простоту и доступность мира электроники, значит цель достигнута.

Читать статью в формате PDF

Логические элементы в дискретном исполнении

Базисные логические функции(логические элементы) могут быть представлены как в дискретном исполнении, так и методами интегральной технологии. Базисные логические функции(логические элементы) «И», «ИЛИ» и «НЕ» могут выполняться на диодах, резисторах, биполярных полевых транзисторах. В соответствии с конструкцией построения логических элементов различают резисторно-транзисторную логику(РТЛ), диодно-транзисторную(ДТЛ), транзисторно-транзисторную логику(ТТЛ), а также логику на полевых транзисторах(«р»-канальная-рМОП, «n»-nМОП), комплементарную (КМДП) и динамическую (МОП).

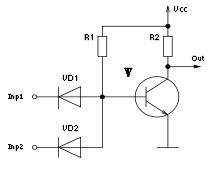

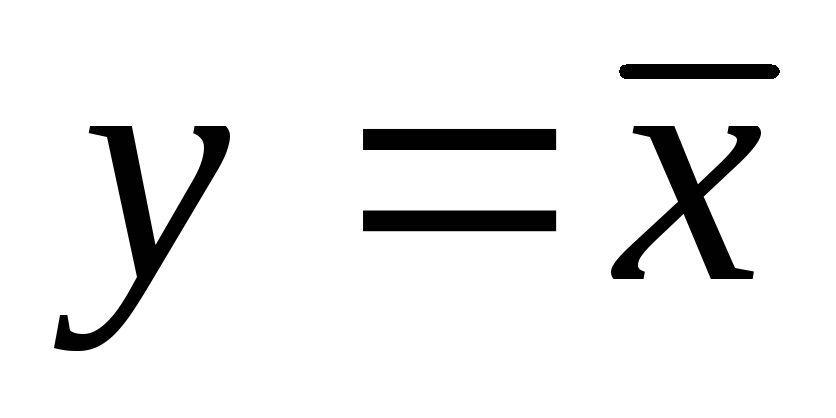

Логический элемент «НЕ» (логическое отрицание).

Логический элемент «НЕ» имеет один вход и один выход. Условно обозначается в схемах:

Таблица истинности операции «НЕ» имеет вид:

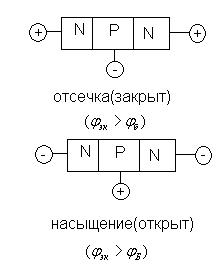

Логический элемент » НЕ» представляет собой усилительный каскад на транзисторе, включённом по схеме ОЭ и работает в ключевом режиме. На вход подаются положительные сигналы в положительной логике. Используется транзистор типаn-p-n(рис.14-12.).

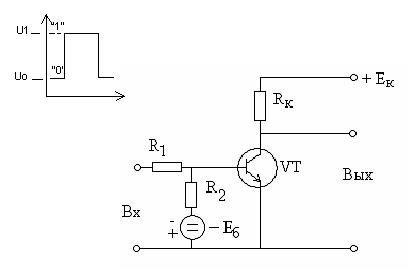

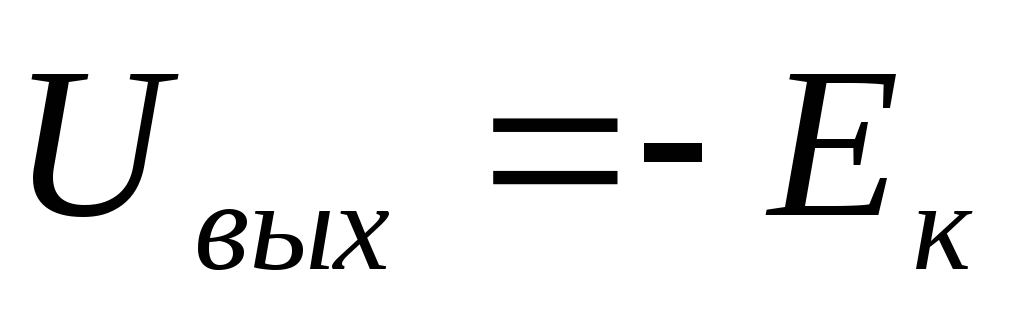

Рис. 14-12. Электронная схема реализующая логический элемент «НЕ».

Допустим, что транзистор VT закрыт отрицательным потенциалом на

базе от -Еб. Если на»Вх»

подать низкий потенциал, соответствующий

«0»  ,

то VT

остаётся закрытым, а при этом Iк=0

и

,

то VT

остаётся закрытым, а при этом Iк=0

и  .

Следовательно,

на выходе будет высокое напряжение

соответствующее «I».

.

Следовательно,

на выходе будет высокое напряжение

соответствующее «I».

Если на “Вх” подать высокий положительный

потенциал соответствующий «I»,

тоVT будет в состоянии насыщения и .Такой

логический элемент еще называют

«инвертором».

.Такой

логический элемент еще называют

«инвертором».

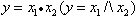

Логический элемент «И» (логическое умножение).

Обозначается .

Элемент имеет как минимум два входа и

один выход. Условное обозначение

элемента “И”:

.

Элемент имеет как минимум два входа и

один выход. Условное обозначение

элемента “И”:

Таблица истинности операции «И» имеет вид:

X1

X2

Y

0

0

0

0

1

0

1

0

0

1

1

1

Схема двухходового элемента «И» на биполярных транзисторах показана на рис 14-13.

Рис 14-13. Электронная схема, реализующая логический элемент «И».

Из схемы (рис 14-13) видно, что транзисторы VT1 иVT2 соединены последовательно и электрический ток может протекать тогда, когда открыты оба транзистора. В том случае, когда один из транзисторов будет закрыт, то на входе напряжение будет равно «0», что соответствует таблице истинности. Этот логический элемент называется конъюктор.

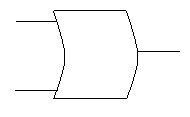

Логический элемент «ИЛИ» (логическое сложение)

Обозначается  .

.

Таблица истинности операции «или» имеет вид:

X1

X2

Y

0

0

0

0

1

1

1

0

1

1

1

1

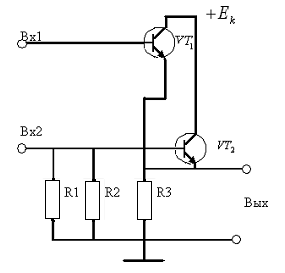

Схема двухходового логического элемента «ИЛИ» показаны на рис 14-14.

Рис 14-14. Электронная схема, реализующая логический элемент «ИЛИ».

Схема элемента «ИЛИ» выполнена на биполярных транзисторах (технология

транзисторно-транзисторной логики).

Если на входы  и

и не подается

не подается

напряжение, то TV1 иTV2

заперты и на (на выходе) нет напряжения, и это

соответствует тому, что на выходе

логический «0». Если на один вход или на

оба входа подается положительное

напряжение (логическая «1»), то один или

оба транзистора открываются и на выходе

появляется положительное напряжение,

отображающее «1», что соответствует

таблице истинности. Этот логический

элемент еще называют дизъюнкцией.

(на выходе) нет напряжения, и это

соответствует тому, что на выходе

логический «0». Если на один вход или на

оба входа подается положительное

напряжение (логическая «1»), то один или

оба транзистора открываются и на выходе

появляется положительное напряжение,

отображающее «1», что соответствует

таблице истинности. Этот логический

элемент еще называют дизъюнкцией.

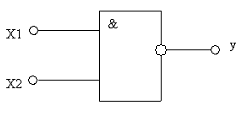

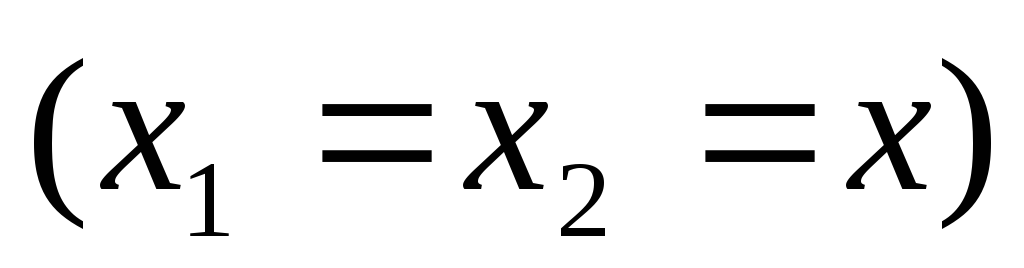

Логический элемент «И-НЕ»(отрицание умножения, штрих Шеффера)

Условное обозначение в схемах.

Таблица истинности операции “И-НЕ” имеет вид:

X1 | X2 | Y |

0 | 0 | 1 |

0 | 1 | 1 |

1 | 0 | 1 |

1 | 1 | 0 |

Рассмотрим схему «И-НЕ» транзисторно-транзисторной логики (ТТЛ) (элемент Шеффера, рис 14-15)

Рис 14-15. Электронная схема, реализующая логический элемент «И-НЕ» (выполнена в ТТЛ).

Данная схема предназначен для работы от сигналов в виде напряжений, отрицательной полярности в отрицательной логике. (рис 14-15)

При отсутствии сигналов на входах схемы,  и

и заперты

положительным смещением

заперты

положительным смещением ,

тока нет и на выходе

,

тока нет и на выходе (то

есть «I»).Когда на входы

одновременно будут поданы

(то

есть «I»).Когда на входы

одновременно будут поданы (

то есть «I») и

(

то есть «I») и ,

тоV

,

тоV иV

иV откроются и на выходе

откроются и на выходе .Если

на ВхIподать «0», а на Вх2

–«1», то

.Если

на ВхIподать «0», а на Вх2

–«1», то будет заперт, а

будет заперт, а открыт, тока в цепи нет и

открыт, тока в цепи нет и (логическая «1»). Если на ВХ1 подать «1»,

а на ВХ2 – «0», то на выходе также

(логическая «1»). Если на ВХ1 подать «1»,

а на ВХ2 – «0», то на выходе также (логическая

«1»)

(логическая

«1»)

Логический элемент «ИЛИ-НЕ»(отрицание сложения элемент Пирса).

Условное обозначение в схемах (логического элемента «ИЛИ-НЕ»)

Таблица истинности логического элемента «ИЛИ-НЕ» :

X1

X2

Y

0

0

1

0

1

0

1

0

0

1

1

0

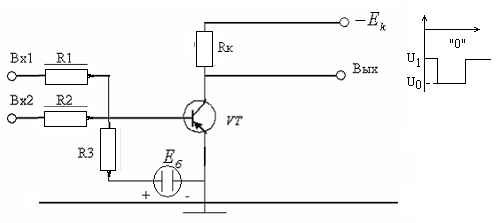

Рассмотрим схему элемента «ИЛИ-НЕ» (рис 14-16) :

Рис 14-16. . Электронная схема, реализующая логический элемент «ИЛИ-НЕ».

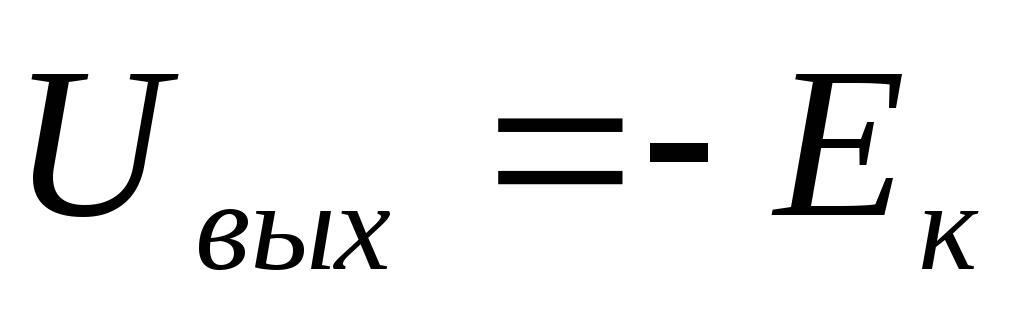

Схема (рис 14-16) работает от сигналов в виде напряжений отрицательной полярности в отрицательной логике. Схема выполнена на транзисторе и работает как логический элемент «НЕ» с несколькими входами (не менее двух).

При отсутствии на

входах сигналов транзистор заперт

положительным смещением +Еб

на базе,

тогда Iк=0

и Uвых

= -Ек (т.е. «I»).

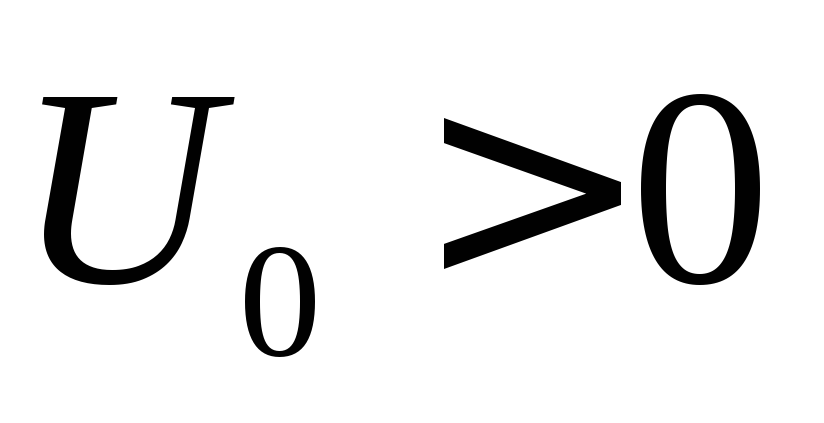

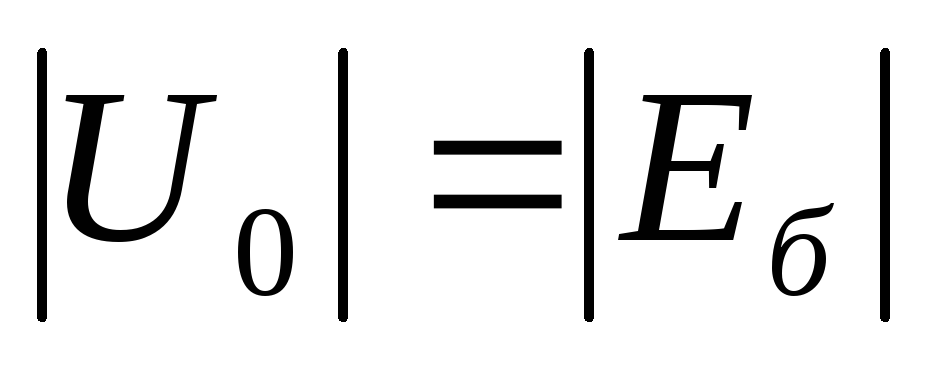

Когда на любой из входов поступит сигнал

Ubx

= Uo

(т.е. «I»),

то транзистор отпирается и Uвых 0

(т.е. «О») и т.д. Здесь чаще всего

используют МОП-транзисторы,

т.к. у них высокая степень интеграции и

повышенная помехоустойчивость.

0

(т.е. «О») и т.д. Здесь чаще всего

используют МОП-транзисторы,

т.к. у них высокая степень интеграции и

повышенная помехоустойчивость.

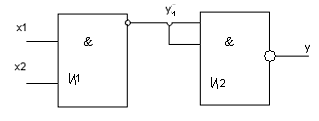

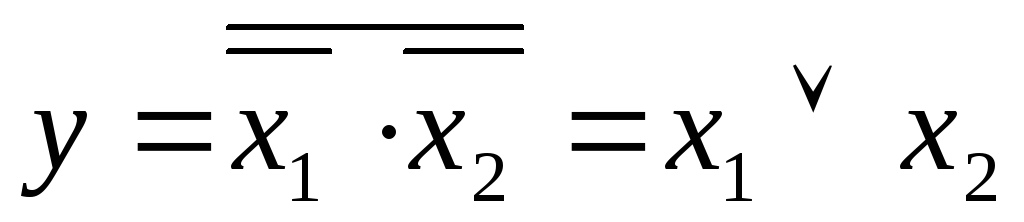

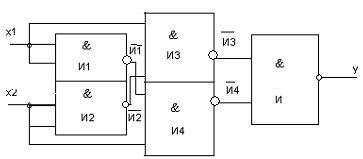

Основываясь на законах алгебры логики можно любой логический элемент заменить устройством, собранных только на двухходовых элементах И-НЕ.

1). Операция НЕ,  ,

,

Таблица истинности операции «НЕ».

у

0

0

1

1

1

0

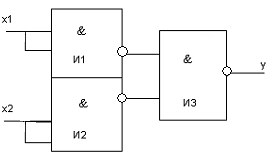

2). Операция И,

Таблица истинности операции «И».

Х1 | Х2 | И1 | НЕ(у1) | И2 | НЕ (у) |

0 | 0 | 0 | 1 | 1 | 0 |

0 | 1 | 0 | 1 | 1 | 0 |

1 | 0 | 0 | 1 | 1 | 0 |

1 | 1 | 1 | 0 | 0 | 1 |

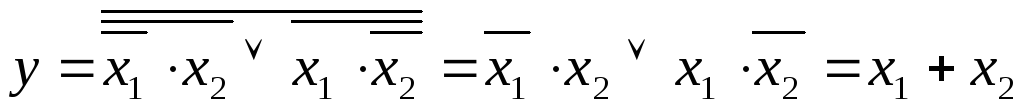

3). Операция «ИЛИ»,

Таблица истинности операции «ИЛИ».

Х1 | Х2 | И1 | И2 | И | И | И3 | У(или) |

0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

4). Операция сложения по модулю два (исключающее ИЛИ),

Таблица истинности операции «исключающее ИЛИ».

Х1 | Х2 | И1 | И2 | И1 | И2 | И3 | И4 | И3 | И4 | И | НЕ(У) |

0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

8.2. Логические элементы на диодах и биполярных транзисторах.

Логические элементы предназначены для выполнения различных логических (функциональных) операций над дискретными сигналами при двоичном способе их представления.

Преимущественное распространение получили логические элементы потенциального типа. В них используются дискретные сигналы, нулевому значению которых соответствует уровень низкого потенциала, а единичному значению – уровень высокого потенциала (положительного или отрицательного). Связь потенциального логического элемента с предыдущим или последующим узлами в системе осуществляется непосредственно без применения реактивных компонентов. Потенциальные логические элементы нашли применение в интегральном исполнении в виде микросхем.

Логические биполярные микросхемы чаще выполняют на транзисторах типа n-p-n с напряжением питания Ek > 0. Поэтому используемые в них сигналы имеют положительную полярность. Уровню высокого потенциала «1» соответствует закрытое состояние транзистора, а уровню низкого потенциала «0» — его открытое состояние. Процесс перехода транзистора из одного состояния в другой обычно принимается мгновенным.

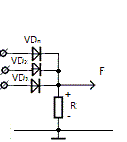

8.2.1. Логический элемент или.

X1 | X2 | F |

0 | 0 | 0 |

0 | 1 | 1 |

1 | 0 | 1 |

1 | 1 | 1 |

рисунок 8.3

Логический элемент ИЛИ имеет несколько входов и один общий выход и выполняет операцию логического сложения (дизъюнкции). F=х1+х2+х3+…+хn, где F – функция, х1+х2+х3+…+хn — аргументы. Здесь функция F=0 когда все аргументы равны 0 и F=1 при одном, нескольких или всех элементах равных единице (рисунок 8.3).

Наиболее просто элемент ИЛИ реализуется на диодах. Значение F=1 на выходе создаётся передачей входного сигнала вследствие отпирания соответствующего диода. К диодам, для которых входной сигнал равен «0», прикладывается обратное напряжение с резистора R и они находятся в закрытом состоянии.

На практике возможны случаи, когда число входов используемого элемента ИЛИ превышает количество входных сигналов. Тогда неиспользуемые входы заземляют, чем исключают возможность прохождения через них различных помех.

8.2.2. Логический элемент и.

X1 | X2 | F |

0 | 0 | 0 |

0 | 1 | 0 |

1 | 0 | 0 |

1 | 1 | 1 |

рисунок 8.4

Логический элемент И выполняет операцию логического умножения (конъюнкцию) F=х1·х2·х3·…·хn. Здесь F=0 когда хотя бы один из аргументов равен «0». F=1 когда все аргументы равны «1» (рисунок 8.4).

Схема

«И» на диодах работает следующим образом.

При всех входных сигналах равных «1» на

катодах диодов имеется положительный

потенциал относительно общей точки и

все диоды закрыты. На выходе схемы

создаётся напряжение  и F=1.

При нулевом значении сигнала, хотя бы

на одном из входов, соответствующий

диод будет проводить ток, и шунтировать

R2,

выполняющий роль нагрузки. Напряжение

на выходе при этом равно падению

напряжения на открытом диоде, то есть

близки к нулю. F=0.

и F=1.

При нулевом значении сигнала, хотя бы

на одном из входов, соответствующий

диод будет проводить ток, и шунтировать

R2,

выполняющий роль нагрузки. Напряжение

на выходе при этом равно падению

напряжения на открытом диоде, то есть

близки к нулю. F=0.

В случае применения логического элемента И, имеющее число входов больше количества входных сигналов, неиспользуемые входы элемента соединяют с плюсом источника питания (подают сигнал логической «1»).

50. Простейшие логические элементы на биполярных транзисторах.

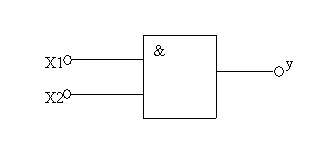

Принципиальная схема типового элемента 2И-НЕ диодно-транзисторной логики (ДТЛ) приведена на рис. 2. Если хотя бы на одном из входов (число которых может быть более двух) появляется уровень 0 (низкое напряжение), то соответствующий входной диод открывается и сигнал низкого напряжения практически закрывает транзистор Т1. При этом Т3 будет закрыт, а Т2 открыт и на выходе установится уровень 1 (высокий уровень). Для получения на выходе уровня 0 нужно, чтобы все входные диоды были закрыты, т.е. на входах должны быть уровни 1.

|

Рис. 2. Принципиальная схема ДТЛ

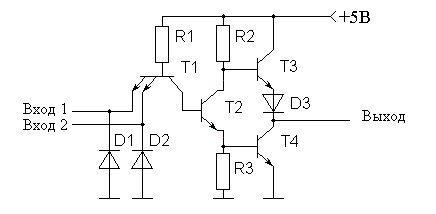

Принципиальная схема типового элемента 2И-НЕ транзисторно-транзисторной логики (ТТЛ) приведена на рис. 3. В отличие от схемы ДТЛ роль входных диодов выполняют эмиттерные переходы многоэмиттерного транзистора Т1.

|

Рис. 3. Принципиальная схема ТТЛ

Элемент ТТЛ со сложным инвертором.

Iб = 0

Т3=насыщения

Т4=отсечки

Uвых = 1

Iб = 1 (Uб = 1)

Т4=насыщения

Т3=отсечки

Uбз = 0,8 – 0,98

Uвых = 0

51.Ттл со сложным инвертором

Е сли

хотя бы на одном из входов будет

действовать логический ноль, соответствующий

эмиттерный переход будет открыт. В цепи

коллектора, а следовательно, и в цепи

базы ток будет отсутствовать, будет

находиться в режиме отсечки, ток через

транзистор, а значит, ток базы будут

близки к нулю. Транзистор также будет

находиться в режиме отсечки, и на выходе

будет высокий уровень напряжения

логической единицы. При этом напряжение

на коллекторе и на базе будет максимальным,

и будет находиться в полностью открытом

состоянии.При подаче на оба входа

логических единиц оба эмиттерных

перехода закрываются, и ток будет

протекать по цепи от плюса, через R1,

переход база-коллектор на базу. Транзистор

VT2 перейдёт в режим насыщения. Ток через

него, а следовательно, и ток базы будет

максимальным, и транзистор VT4 перейдёт

в режим насыщения. На выходе будет низкий

уровень логического нуля. При этом

напряжение на коллекторе VT2 и на базе

будет близко к нулю и перейдёт в полностью

закрытое состояние. Диод VD1 применяется

для более надёжного запирания транзистора

VT3

сли

хотя бы на одном из входов будет

действовать логический ноль, соответствующий

эмиттерный переход будет открыт. В цепи

коллектора, а следовательно, и в цепи

базы ток будет отсутствовать, будет

находиться в режиме отсечки, ток через

транзистор, а значит, ток базы будут

близки к нулю. Транзистор также будет

находиться в режиме отсечки, и на выходе

будет высокий уровень напряжения

логической единицы. При этом напряжение

на коллекторе и на базе будет максимальным,

и будет находиться в полностью открытом

состоянии.При подаче на оба входа

логических единиц оба эмиттерных

перехода закрываются, и ток будет

протекать по цепи от плюса, через R1,

переход база-коллектор на базу. Транзистор

VT2 перейдёт в режим насыщения. Ток через

него, а следовательно, и ток базы будет

максимальным, и транзистор VT4 перейдёт

в режим насыщения. На выходе будет низкий

уровень логического нуля. При этом

напряжение на коллекторе VT2 и на базе

будет близко к нулю и перейдёт в полностью

закрытое состояние. Диод VD1 применяется

для более надёжного запирания транзистора

VT3

52. N-моп логический элемент (типов и-не и или-не)

54. Кмоп логический элемент

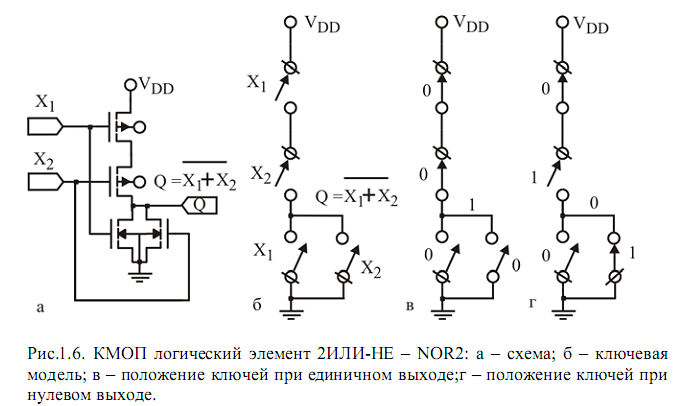

В технологии КМОП используются полевые транзисторы с изолированным затвором с каналами разной проводимости. Отличительной особенностью схем КМОП по сравнению с биполярными технологиями (ТТЛ, ЭСЛ и др.) является очень малое энергопотребление в статическом режиме (в большинстве случаев можно считать, что энергия потребляется только во время переключения состояний). Отличительной особенностью структуры КМОП по сравнению с другими МОП-структурами (N-МОП, P-МОП) является наличие как n-, так и p-канальных полевых транзисторов; как следствие, КМОП-схемы обладают более высоким быстродействием и меньшим энергопотреблением

КМОП-вентили достаточно просто реализуют функции ИЛИ-НЕ (NOR)и И-НЕ (NAND).

Выход Q двухвходового логического элемента 2ИЛИ-НЕ зависит от входов X1 и X2

Q = X1 + X2 (сумма под черточкой)

Рассмотрим КМОП-схему с двумя входами, в которой входные сигналы поступают на р-МОП, соединенные последовательно, и на n-МОП, соединенные параллельно

Элементная база различных логик: схемы, ТТЛ, ТТЛШ, КМОП

Для конкретной серии микросхем характерно использование типового электронного узла — базового логического элемента. Этот элемент является основой построения самых разнообразных цифровых электронных устройств.

Для конкретной серии микросхем характерно использование типового электронного узла — базового логического элемента. Этот элемент является основой построения самых разнообразных цифровых электронных устройств.

Ниже рассмотрим особенности базовых логических элементов различных логик.

Элементы транзисторно-транзисторной логики

Характерной особенностью ТТЛ является использование многоэмиттерных транзисторов. Эти транзисторы сконструированы таким образом, что отдельные эмиттеры не оказывают влияния друг на друга. Каждому эмиттеру соответствует свой p-n-переход. В первом приближении многоэмиттерный транзисторможет моделироваться схемой на диодах (см. пунктир на рис. 3.27).

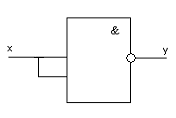

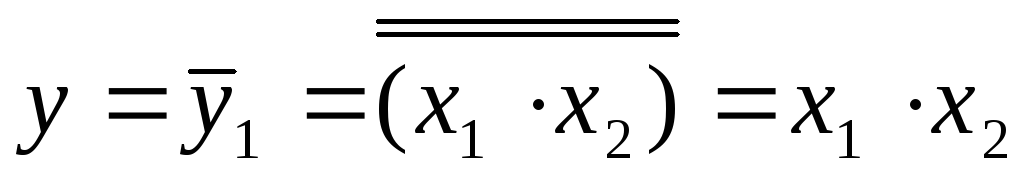

Упрощенная схема ТТЛ-элемента приведена на рис. 3.27. При мысленной замене многоэмиттерного транзистора диодами получаем элемент диодно-транзисторной логики «И-НЕ». Из анализа схемы можно сделать вывод, что если на один из входов или на оба входа подать низкий уровень напряжения, то ток базы транзистора Т2 будет равен нулю, и на коллекторе транзистора Т2 будет высокий уровень напряжения. Если на оба входа подать высокий уровень напряжения, то через базу Т2 транзистора будет протекать большой базовый ток и на коллекторе транзистора Т2 будет низкий уровень напряжения, т. е. данный элемент реализует функцию И-НЕ:

uвых= u1· u2. Базовый элемент ТТЛ содержит многоэмиттерный транзистор, выполняющий логическую операцию И, и сложный инвертор (рис. 3.28).

Если на один или оба входа одновременно подан низкий уровень напряжения, то многоэмиттерный транзистор находится в состоянии насыщения и транзистор Т2 закрыт, а следовательно, закрыт и транзистор Т4, т. е. на выходе будет высокий уровень напряжения. Если на обоих входах одновременно действует высокий уровень напряжения, то транзистор Т2 открывается и входит в режим насыщения, что приводит к открытию и насыщению транзистора Т4 и запиранию транзистора Т3, т. е. реализуется функция И-НЕ.

Для увеличения быстродействия элементов ТТЛ используются транзисторы с диодами Шоттки (транзисторы Шоттки).

Базовый логический элемент ТТЛШ (на примере серии К555)

В качестве базового элемента серии микросхем К555 использован элемент И-НЕ. На рис. 3.29, а изображена схема этого элемента, а условное графическое обозначение транзистора Шоттки приведено на рис. 3.29, б.

Такой транзистор эквивалентен рассмотренной выше паре из обычного транзистора и диода Шоттки. ТранзисторVT4 — обычный биполярный транзистор.

Если оба входных напряжения uвх1и uвх2 имеют высокий уровень, то диодыVD3 и VD4 закрыты, транзисторы VT1,VT5 открыты и на выходе имеет место напряжение низкого уровня. Если хотя бы на одном входе имеется напряжение низкого уровня, то транзисторы VT1 и VT5 закрыты, а транзисторы VT3 и VT4 открыты, и на входе имеет место напряжение низкого уровня. Полезно отметить, что транзисторы VT3 и VT4 образуют так называемый составной транзистор (схему Дарлингтона).

Микросхемы ТТЛШ

Микросхемы ТТЛШ серии К555 характеризуются следующими параметрами:

● напряжение питания +5 В;

● выходное напряжение низкого уровня — не более 0,4 В;

● выходное напряжение высокого уровня — не менее 2,5 В;

● помехоустойчивость — не менее 0,3 В;

● среднее время задержки распространения сигнала — 20 нс;

● максимальная рабочая частота — 25 МГц.

Микросхемы ТТЛШ обычно совместимы по логическим уровням, помехоустойчивости и напряжению питания с микросхемами ТТЛ. Время задержки распространения сигнала элементов ТТЛШ в среднем в два раза меньше по сравнению с аналогичными элементами ТТЛ.

Особенности других логик

Основой базового логического элемента ЭСЛ является токовый ключ. Схема токового ключа (рис. 3.30) подобна схеме дифференциального усилителя.

Необходимо обратить внимание на то, что микросхемы ЭСЛ питаются отрицательным напряжением (к примеру, −4,5 В для серии К1500). На базу транзистора VT2 подано отрицательное постоянное опорное напряжение Uоп. Изменение входного напряжения uвх1 приводит к перераспределению постоянного тока iэ0, заданного сопротивлением Rэ между транзисторами, что имеет следствием изменение напряжений на их коллекторах. Транзисторы не входят в режим насыщения, и это является одной из причин высокого быстродействия элементов ЭСЛ.

Микросхемы серий 100, 500 имеют следующие параметры:

● напряжение питания −5,2 В;

● потребляемая мощность — 100 мВт;

● коэффициент разветвления по выходу — 15;

● задержка распространения сигнала — 2,9 нс.

В микросхемах n-МОП и p-МОП используются ключи соответственно на МОП-транзисторах с n-каналом и динамической нагрузкой (рассмотрены выше) и на МОП-транзисторах с p-каналом.

В качестве примера рассмотрим элемент логики n-МОП, реализующий функцию ИЛИ-НЕ (рис. 3.31).

Он состоит из нагрузочного транзистора Т3 и двух управляющих транзисторов Т1 и Т2. Если оба транзистора Т1 и Т2 закрыты, то на выходе устанавливается высокий уровень напряжения. Если одно или оба напряжения u1и u2 имеют высокий уровень, то открывается один или оба транзистора Т1 и Т2 и на выходе устанавливается низкий уровень напряжения, т. е. реализуется функция uвых= u1 + u2.

Для исключения потребления мощности логическим элементом в статическом состоянии используются комплементарные МДП — логические элементы (КМДП или КМОП-логика). В микросхемах КМОП используются комплементарные ключи на МОП-транзисторах. Они отличаются высокой помехоустойчивостью. Логика КМОП является очень перспективной. Рассмотренный ранее комплементарный ключ фактически является элементом НЕ (инвертором).

КМОП — логический элемент

Рассмотрим КМОП — логический элемент, реализующий функцию ИЛИ-НЕ (рис. 3.32).

Если входные напряжения имеют низкие уровни (u1и u2меньше порогового напряжения n-МОП-транзистора Uзи.порог.n), то транзисторы Т1 и Т2 закрыты, транзисторы Т3 и Т4 открыты и выходное напряжение имеет высокий уровень. Если одно или оба входных напряжения u1и u2 имеют высокий уровень, превышающий Uзи.порог.n, то открывается один или оба транзистора Т1 и Т2, а между истоком и затвором одного или обоих транзисторов Т3 и Т4 устанавливается низкое напряжение, что приводит к запиранию одного или обоих транзисторов Т3 и Т4, а следовательно, на выходе устанавливается низкое напряжение. Таким образом, этот элемент реализует функцию uвых= u1+u2 и потребляет мощность от источника питания лишь в короткие промежутки времени, когда происходит его переключение.

Интегральная инжекционная логика (ИИЛ или И2Л) построена на использовании биполярных транзисторов и применении оригинальных схемотехнических и технологических решений. Для нее характерно очень экономичное использование площади кристалла полупроводника. Элементы И2Л могут быть реализованы только в интегральном исполнении и не имеют аналогов в дискретной схемотехнике.  Структура такого элемента и его эквивалентная схема приведены на рис. 3.33, из которого видно, что транзистор T1 (p-n-p) расположен горизонтально, а многоколлекторный транзистор Т2 (n-p n) расположен вертикально. Транзистор T1 выполняет роль инжектора, обеспечивающего поступление дырок из эмиттера транзистора T1 (при подаче на него положительного напряжения через ограничивающий резистор) в базу транзистора Т2. Если u1 соответствует логическому «0», то инжекционный ток не протекает по базе многоколлекторного транзистора Т2 и токи в цепях коллекторов транзистора Т2 не протекают, т. е. на выходах транзистора Т2 устанавливаются логические «1». При напряжении u1 соответствующем логической «1», инжекционный ток протекает по базе транзистора Т2 и на выходах транзистора Т2 — логические нули.

Структура такого элемента и его эквивалентная схема приведены на рис. 3.33, из которого видно, что транзистор T1 (p-n-p) расположен горизонтально, а многоколлекторный транзистор Т2 (n-p n) расположен вертикально. Транзистор T1 выполняет роль инжектора, обеспечивающего поступление дырок из эмиттера транзистора T1 (при подаче на него положительного напряжения через ограничивающий резистор) в базу транзистора Т2. Если u1 соответствует логическому «0», то инжекционный ток не протекает по базе многоколлекторного транзистора Т2 и токи в цепях коллекторов транзистора Т2 не протекают, т. е. на выходах транзистора Т2 устанавливаются логические «1». При напряжении u1 соответствующем логической «1», инжекционный ток протекает по базе транзистора Т2 и на выходах транзистора Т2 — логические нули.

Рассмотрим реализацию элемента ИЛИ-НЕ на основе элемента, представленного на рис. 3.34 (для упрощения другие коллекторы многоколлекторных транзисторов Т3 и Т4 на рисунке не показаны). Когда на один или оба входа подается логический сигнал «1», то напряжение uвых соответствует логическому нулю. Если на обоих входах логические сигналы «0», то напряжение uвых соответствует логической единице.

Логика на основе полупроводника из арсенида галлия GaAs характеризуется наиболее высоким быстродействием, что является следствием высокой подвижности электронов (в 3…6 раз больше по сравнению с кремнием). Микросхемы на основе GaAs могут работать на частотах порядка 10 ГГц и более.

2.1.3. Основные логические элементы в интегральном исполнении

Логические элементы в интегральном исполнении предназначают для работы с сигналами в потенциальной форме. Они могут выполняться в логике разных типов. Тип логики влияет на характеристики элемента. В интегральных микросхемах чаще всего применяют кремниевые транзисторы. Применение интегральных схем позволяет изготавливать компактные элементы, узлы и целые комплексы, выполняющие разнообразные логические операции, запоминание информации и другие функции.

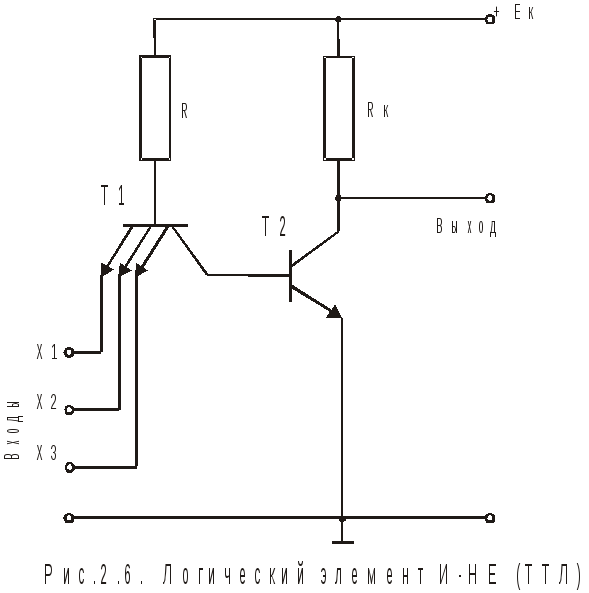

Логический элемент И — НЕ транзисторно-транзисторной логики (ТТЛ). Простейший элемент И — НЕ показан на рис.2.6. Он состоит из двух частей: элемента И на многоэмиттерном транзисторе Т1 и элемента НЕ на транзисторе Т2. Связь непосредственная: коллектор Т1 соединен с базой транзистора Т2. Смещение в цепи базы транзистора Т2 выполняет коллекторный переход Т1. Три эмиттерных перехода Т1, подключенных к входу элемента, выполняют функции входных диодов в схеме И на диодах.

П о

сравнению с ДТЛ-элементами элементы

ТТЛ обладают более высоким быстродействием.

Элемент выполнен по технологии

интегральных микросхем, поэтому он не

содержит реактивных элементов и работает

от сигналов в виде напряжений положительной

полярности.

о

сравнению с ДТЛ-элементами элементы

ТТЛ обладают более высоким быстродействием.

Элемент выполнен по технологии

интегральных микросхем, поэтому он не

содержит реактивных элементов и работает

от сигналов в виде напряжений положительной

полярности.

Рассмотрим принцип работы подобных элементов. Если на все входы подать напряжение U1, то все эмиттерные переходы сместятся в обратном направлении. Потенциал коллектора транзистора Т2, окажется близким нулю, переход база — коллектор смещен в прямом направлении за счет источника +Ек. Транзистор T1 будет в инверсном режиме, транзистор Т2, — в режиме насыщения. Коллекторный ток транзистора T1 втекает в базу транзистора Т2, оставляя последний в режиме насыщения. Таким образом, на выходе будет напряжение низкого уровня, т.е. логический 0.

Е сли

на один из входов подано напряжение U°,

то потенциал базы транзистора T1 станет выше потенциалов эмиттера и

коллектора, поэтому T1 окажется в режиме насыщения и ток базы

замкнется через эмиттерные переходы

T1 и не поступит в его коллектор, а

следовательно, и в базу Т2.

Поэтому транзистор Т2,

будет закрыт, а на его выходе — напряжение

высокого уровня (логическая 1). Таким

образом, элемент выполняет операцию И

— НЕ, так как

сигнал логического нуля на выходе может

быть только тогда, когда на все входы

будет подан сигнал логической единицы.

сли

на один из входов подано напряжение U°,

то потенциал базы транзистора T1 станет выше потенциалов эмиттера и

коллектора, поэтому T1 окажется в режиме насыщения и ток базы

замкнется через эмиттерные переходы

T1 и не поступит в его коллектор, а

следовательно, и в базу Т2.

Поэтому транзистор Т2,

будет закрыт, а на его выходе — напряжение

высокого уровня (логическая 1). Таким

образом, элемент выполняет операцию И

— НЕ, так как

сигнал логического нуля на выходе может

быть только тогда, когда на все входы

будет подан сигнал логической единицы.

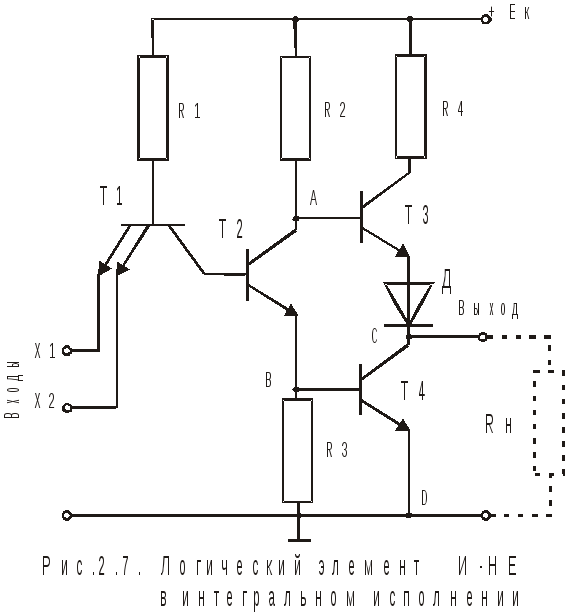

В промышленности для повышения нагрузочной способности логических элементов ДТЛ и ТТЛ используют схемы со сложным инвертором. На рис.2.7 изображена схема универсального логического элемента И_- НЕ со сложным инвертором на выходе в интегральном исполнении. Операция И выполняется входным многоэмиттерным транзистором T1. Инвертирование фазы сигнала осуществляется сложным инвертором на транзисторах Т2, Т3, Т4. Питание элемента – от источника постоянного напряжения 5В. Элемент работает от входных импульсов напряжения прямоугольной формы с уровнями U1= 3,3 В (логическая 1), U° = 0,1 В (логический 0).

Транзисторы Т2 и Т4 находятся в режиме насыщения. Ток проходит по цепи +Ек, R1, открытый коллекторный р-n-переход транзистора Т1, эмиттерно-базовые переходы насыщенных транзисторов Т2 и Т4, 0. Многоэмиттерный транзистор Т1 находится в инверсном режиме включения. Так как транзистор Т2 открыт и находится в насыщении, между точками А и В элемента имеется малый перепад напряжения, из которого вычитается падение напряжения на диоде Д. В силу этого транзистор Т3 надежно закрыт и находится в режиме отсечки. Насыщенный транзистор Т4, представляя собой в этом режиме эквипотенциальную точку, подсоединяет узел С схемы к заземленной точке D, закорачивая тем самым сопротивление нагрузки Rн. Таким образом, на выходе напряжение равно логическому нулю. Появление хотя бы на одном входе Т1 импульса напряжения низкого уровня приводит к открытию соответствующего эмиттерного перехода Т1. Транзистор Т1 выходит из инверсного режима, а транзисторы Т2 и Т4 закрываются, так как их базовые токи становятся равными нулю. В это время входит в насыщение транзистор Т3 и на выходе появляется сигнал логической 1.

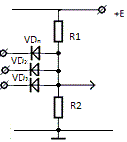

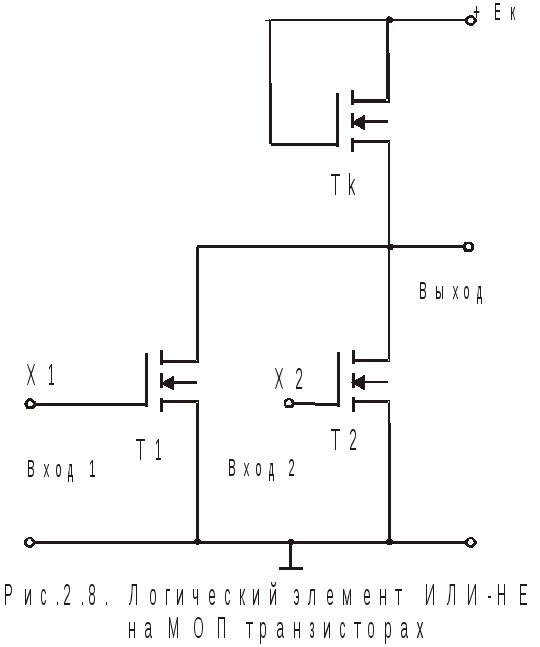

Логический элемент ИЛИ — НЕ n-канальной МОП-транзисторной логики (МОПТЛ). В логических схемах на полевых транзисторах используют только МОП-транзисторы с диэлектриком SiO2. Основные преимущества схем на МОП-транзисторах по сравнению с другими схемами — высокая степень интеграции и повышенная помехоустойчивость.

Р ассмотрим

схемуИЛИ —

HЕ на

МОП-транзисторах с индуцированным

n-каналом

(рис. 2.8). Для уменьшения площади схемы

вместо нагрузочного резистора используется

МОП-транзистор Тк.

Логические транзисторы Т1 и Т2 включены параллельно. Напряжение питания

обычно выбирают в три раза большим

порогового Uпор (Uпор — напряжение на затворе, при котором

образуется канал).

ассмотрим

схемуИЛИ —

HЕ на

МОП-транзисторах с индуцированным

n-каналом

(рис. 2.8). Для уменьшения площади схемы

вместо нагрузочного резистора используется

МОП-транзистор Тк.

Логические транзисторы Т1 и Т2 включены параллельно. Напряжение питания

обычно выбирают в три раза большим

порогового Uпор (Uпор — напряжение на затворе, при котором

образуется канал).

Если Unop = 2,0 В, то логический перепад (разность между входным и пороговым напряжениями) составляет 4 В. Логические уровни соответствуют выходным напряжениям открытого и закрытого транзистора. Если на оба входа подать напряжение меньше порогового (соответствующее логическому нулю), то транзисторы T1 и Т2 окажутся закрытыми, а ток стока — практически равным нулю. При этом ток стока нагрузочного транзистора Тк тоже будет равен нулю. Поэтому на выходе установится напряжение, близкое к напряжению источника питания Ес и соответствующее логической 1.

Если на вход хотя бы одного транзистора подать напряжение, превышающее пороговое (соответствующее логической 1), то этот транзистор откроется и появится ток стока. Тогда на выходе схемы будет остаточное напряжение, значительно меньшее порогового, что соответствует логическому 0.

Следует отметить, что схемы на МОП-транзисторах менее быстродействующие, чем на биполярных. Это связано со скоростью перезарядки выходной емкости, которая весьма значительна. Все способы повышения быстродействия ведут к появлению других существенных недостатков.

Аналогично работает (с учетом полярностей) схема ИЛИ-НЕс р-канальными МОП-транзисторами. Тип схемы влияет на характеристики (потребляемая мощность, быстродействие и др.), но принцип работы схемы остается неизменным. Кроме рассмотренных выше, существуют и другие типы логик.

МОП-транзисторная логика на комплементарных транзисторах (КМОП). Схема строится на комплементарных МОП-транзисторах. В качестве логических используются два транзистора, один из которых сn-каналом, а другой — с р-каналом. Логические ИМС на их основе являются наиболее перспективными. Однако технология изготовления транзисторов с р- и n-каналами на одном кристалле сложна и трудоемка.

Эмиттерно-связанная логика (ЭСЛ). Основу этой группы ИМС составляет переключатель тока, представляющий собой ключевой элементна транзисторах с объединенным эмиттером. Такие логические ИМС наиболее быстродействующие.

Интегральная инжекционная логика (И2Л). Эта логика не имеет аналогов в дискретном исполнении и является новым направлением, которое способствует миниатюризации цифровых приборов. В основе построения микросхем на И2Л используется базовая структура, состоящая из комплементарной пары биполярных транзисторов.

1

1 2

2