Составные транзисторы. Схемы включения. | HomeElectronics

Транзисторы как силовые элементы многих радиоэлектронных устройств для нормальной работы должны выполнять следующие функции:

1. Обеспечивать управление заданным током нагрузки при большом усилении по мощности.

2. Обладать достаточной (с учётом заданной выходной мощности и диапазонов изменения входного и выходного напряжений) рассеиваемой мощностью.

Для сборки радиоэлектронного устройства можно преобрески DIY KIT набор по ссылке.

3. Иметь максимально допустимое напряжение коллектор – эмиттер, позволяющее без опасности пробоя обеспечивать необходимое падение напряжение на переходе коллектор – эмиттер при возможных значениях входного и выходного напряжений.

В некоторых случаях имеющиеся в наличии транзисторы не позволяют выполнить одно или несколько вышеописанных условий, тогда прибегают к помощи так называемых составных транзисторов. Схем составных транзисторов существует великое множество, но основных схем существует всего три.

Тандемное включение транзисторов (схемы Дарлингтона и Шиклаи)

Довольно часто возникает ситуация, когда необходимого коэффициента усиления одного транзистора не хватает. В этом случае транзисторы соединяют тандемно (то есть выходной ток первого транзистора является входным током для второго). Существует две схемы такого включения: схема Дарлингтона и схема Шиклаи. Отличие заключается лишь в том, что в схеме Дарлингтона используются транзисторы одинакового типа проводимости, а в схеме Шиклаи – разного типа проводимости.

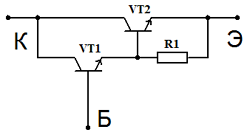

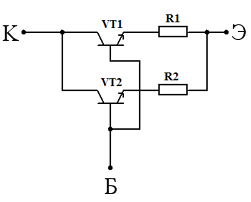

Схема Дарлингтона

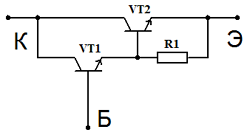

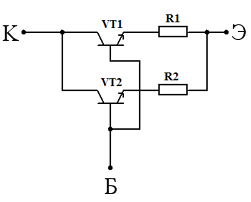

Схема Шиклаи

Данные пары – это просто два каскада эмиттерного повторителя. Иногда данные составные схемы транзисторов называют «супер-β» пары, так как они функционируют как один транзистор с высоким коэффициентом усиления.

Общий коэффициент передачи тока будет равен:

h21e(ОБЩ) = h21e(VT1)*h21e(VT2)

При использовании данных схем вполне возможна такая ситуация, когда нагрузка уменьшится до нуля (или некоторого минимального значения, близкого к нулю) или при повышении температуры базовый ток транзистора VT1 может стать равным нулю или даже переменить направление за счёт неуправляемого обратного тока коллектора. Во избежание запирания транзистора VT2 его режим следует стабилизировать с помощью резистора R1.

Величину сопротивления R1 можно определить по формуле:

R1 ≤ UE min/ICBO(VT1)

Параллельное включение транзисторов

Современные транзисторы позволяют реализовать электронные схемы расчитаные на широкие диапазоны изменений токов и напряжений, но в отдельных случаях для увеличения допустимой мощности рассеивания применяется параллельное включение транзисторов.

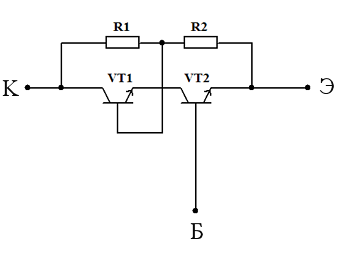

Схема параллельного включения транзисторов

Максимально допустимый ток протекающий через такой составной транзистор равен:

IKmax(общ) = IKmax(VT1) + IKmax(VT2)

При такой схеме включения транзисторов следует учитывать, что вследствие разброса параметров параллельно включённых транзисторов токи между ними распределяются неравномерно. Большая часть тока будет протекать через транзистор, имеющий больший коэффициент усиления. Рассеиваемые транзисторами мощности можно выровнять включением в их эмиттерные цепи дополнительных симметрирующих резисторов с небольшими сопротивлениями. Так как на практике трудно подбирать такие сопротивление для каждого транзистора, в практических схемах в эмиттеры всех транзисторов ставят резисторы одного сопротивления. Сопротивление симметрирующих резисторов R1 и R2 можно определить по формуле

R1 = R2 ≈ 0,5n/IK,

где n – число параллельно соединенных транзисторов

IK — ток проходящий через коллектор.

Такой способ связан с ухудшением усилительных свойств транзисторов, однако его достоинством является возможность получения мощного силового элемента при использовании относительно маломощных транзисторов.

Последовательное включение транзисторов

Во время работы силового транзистора на его переходе коллектор – эмиттер падает напряжение, представляющее собой разность входного и выходного напряжений. В отдельных случаях эта разность может превышать максимально допустимое напряжений коллектор – эмиттер транзистора, имеющегося в распоряжении. В этом случае необходимо использовать последовательное соединение нескольких транзисторов.

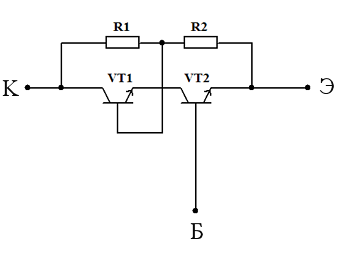

Схема последовательного включения транзисторов

Эквивалентный транзистор будет иметь следующие параметры:

UCEmax(общ) = UCEmax(VT1) + UCEmax(VT2)

Для симметрирования напряжений, которые будут падать на переходе коллектор – эмиттер транзисторов вводят симметрирующие резисторы R1 и R2 сопротивление, которых можно определить по формуле

R1 = R2 < UCEmax/2IB,

где IB – ток базы составного регулирующего транзистора.

Теория это хорошо, но без практического применения это просто слова.Здесь можно всё сделать своими руками.

Последовательное соединение — транзистор — Большая Энциклопедия Нефти и Газа, статья, страница 1

Последовательное соединение — транзистор

Cтраница 1

Последовательное соединение транзисторов, управляемых сигналами, выдаваемыми триггерами, позволяет использовать один и тот же транзистор, чтобы получить два произведения двух переменных, в которых одна переменная входит общим множителем. Это свойство позволяет экономить элементы. [1]

Применение последовательного соединения транзисторов в первую очередь позволяет значительно снизить проводимость внутренней обратной связи ( Л12, у12) между входом и выходом схемы, что особенно существенно в области повышенных частот, когда начинает сказываться влияние емкости перехода коллектор-база. [3]

При последовательном соединении транзисторов в запертом состоянии схемы через сопротивление RK проходит только ток / к обр в отличие от схемы с параллельным включением сопротивления транзисторов, где через RK проходит m токов / к. [5]

Так как непосредственное последовательное соединение транзисторов представляет определенные трудности ( подробнее — см. § 11 — 4), при повышенных напряжениях питания предпочтительней применение мостовой или полумостовой схемы. [6]

В случае последовательного соединения транзисторов ток, определяемый выражением ( 1), течет при включении только в базу одного транзистора. [7]

Следовательно, схема с последовательным соединением транзисторов в зависимости от системы задания логических переменных обеспечивает реализацию двух операций. [9]

На рис. 6.52 показан трюк с последовательным соединением транзисторов для увеличения напряжения пробоя. Транзистор 7 — i управляет последовательно соединенными транзисторами Т2 — Т4, которые делят между собой большое напряжение между коллектором Т2 и выходом. Одинаковые базовые резисторы выбираются достаточно мальгми, чтобы обеспечить полный выходной ток транзисторов. Заметьте, что резисторы смещения дают некоторый выходной ток, даже когда транзисторы выключены, поэтому должна быть минимальная нагрузка на землю для того, чтобы предотвратить подъем выходного напряжения выше стабилизированного уровня. [11]

Инвертор выполнен по трехфазной мостовой схеме с последовательным соединением транзисторов по четыре в одном плече моста. Для равномерного распределения напряжения между транзисторами при их закрытом состоянии каждый из них шунтирован сопротивлением Rm; величина Rm принимается равной. [12]

Логическая схема ИЛИ может быть также построена с последовательным соединением транзисторов. [13]

ВВА-схемы так же, как и однотактной АПН-схемы, позволяет исключить последовательное соединение транзисторов

Страницы: 1 2 3

Параллельное включение транзисторов | Все своими руками

Опубликовал admin | Дата 19 ноября, 2013Одним из наиболее распространенных требований при разработке или доработке источников питания является увеличение его выходного тока.

В таких источниках простое соединение одноименных выводов транзисторов обычно не дает практических результатов из-за неравномерного распределения тока между транзисторами. При повышении рабочей температуры неравномерное распределение тока между транзисторами становится еще большим до тех пор, пока практически весь ток нагрузки не потечет через один из транзисторов.

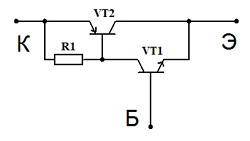

Предложенный вариант на рисунке 1 может быть реализован при условии, что параллельно соединенные транзисторы имеют совершенно идентичные характеристики и работают при одинаковой температуре. Такое условие практически не реализуемо из-за относительно больших разбросов характеристик биполярных транзисторов. Рис. 2 показывает, как осуществлять параллельное включение транзисторов в линейном источнике питания. При таком включении нужно стремиться использовать транзисторы с близкими параметрами Вст. Транзисторы большой мощности при этом должны устанавливаться на один теплоотвод. Для дополнительного выравнивания токов в данной схеме в цепях эмиттеров применены резисторы R1 и R2. Сопротивление резисторов следует выбирать исходя из падения напряжения на них в интервале рабочих токов, около 1 вольта или, по крайней мере, — не менее 0,7 вольта. Данная схема должна применяться с большой осторожностью, так как даже транзисторы одного типа и из одной партии выпуска имеют очень большой разброс по параметрам. Выход из строя одного из транзисторов неизбежно приведет к выходу из строя и других транзисторов в цепочке. При параллельном включении двух транзисторов максимальный суммарный ток коллектора не должен превышать 150 процентов от предельного тока коллектора одного из транзисторов! Количество транзисторов, включенных по этой схеме, может быть сколько угодно большим — все зависит от степени необходимой надежности устройств, в которых применяется такое включение транзисторов и допустимого КПД всего устройства, так как на резисторах выделяется отнюдь не маленькая тепловая мощность. На схемах нарисованы р-n-p транзисторы, естественно все сказанное будет справедливо и для n-p-n транзисторов.

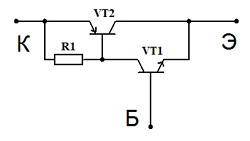

Статический коэффициент усиления по току такого каскада равен коэффициенту усиления одного транзистора, так как общий ток управления равномерно распределяется между базами транзисторов. Значительно большее усиление можно получить, если включить транзисторы по схеме, показанной на рис. 3. Такое включение транзисторов напоминает известный составной транзистор, но отличается от него наличием резистора R, подбираемого экспериментально. Правильно выбранное сопротивление R обеспечивает равномерное распределение общего тока коллектора между транзисторами при одновременном увеличении общего коэффициента усиления. Увеличение коэффициента усиления объясняется тем, что весь ток управления сначала усиливается транзистором VT1, а затем часть тока эмиттера этого транзистора дополнительно усиливается транзистором VT2. Преимущества включения двух транзисторов по схеме рис. 3 были выявлены при сравнительной экспериментальной проверке обоих вариантов схем. Обе схемы были поочередно собраны на одних и тех же экземплярах транзисторов П217В. Общий ток коллектора устанавливался равным 2 А в обоих случаях. В случае параллельного включения транзисторов, (рис. 2) равномерное распределение тока между транзисторами, было достигнуто при сопротивление резисторов R1 и R2 равном 0,69 Ом. При этом ток базы равнялся 44 мА, напряжение между эмиттером и коллектором — 4В. Во втором случае (рис. 3) равномерное распределение тока между транзисторами удалось получить при сопротивлении резистора R, равное 0,2 Ом, а то же напряжение между эмиттером и коллектором (4В) — при токе базы 20 мА. Таким образом, схема рис. 3 имеет вдвое больший статический коэффициент усиления и обладает более высоким КПД. Такая схема может быть использована и для соединения транзисторов с различными видами приводимости (рис. 4), что невозможно осуществить при включении транзисторов по схеме рис. 2. Усилитель по схеме рис. 4 был собран на транзисторах П306 и П701. Общий ток устанавливался равным 0.4 а. Сопротивление резистора R равно 8 ОМ. При токе базы, равном 7 мА, напряжение между эмиттером и коллектором составило 7В.

1. http://radiocon-net.narod.ru/page16.htm

Обсудить эту статью на — форуме «Радиоэлектроника, вопросы и ответы».

Просмотров:34 278

Схема последовательного соединения птуп-транзисторов

Изобретение относится к области электронной схемотехники, в частности к переключающему устройству с последовательным соединением ПТУП-транзисторов. Техническим результатом является повышение надежности переключающего устройства за счет обеспечения одинаковой нагрузки выводов затворов, влияющей на динамическое распределение запирающего напряжения. Устройство содержит, по меньшей мере, два последовательно подсоединенных ПТУП-транзистора (J1-J

Данное изобретение относится к области электронной схемотехники, в частности к переключающему устройству с последовательным соединением ПТУП-транзисторов (полевых транзисторов с управляющим p-n-переходом), тип которого указан в ограничительной части пункта 1 формулы изобретения.

Уровень техники

В качестве силовых выключателей или переключающих устройств, рассчитанных на работу при высоких напряжениях, можно использовать электронные коммутационные устройства с каскадным или последовательным включением транзисторов. В патентных документах, например, US 6822842 и DE 19926109 такие переключающие устройства называют каскодными схемами. Эти схемы основаны на особом соединении МОП-транзистора М и по меньшей мере одного ПТУП-транзистора Ji (см. фиг.1). Переключатели подсоединяются между первым выводом 1 и вторым выводом 2 и управляются через управляющий вывод 7 МОП-транзистора М. В таком переключающем устройстве, рассчитанном на работу при высоких напряжениях и основанном на каскодной схеме, предусматривают использование нескольких последовательно включенных ПТУП-транзисторов J2…Jj, чтобы за счет этого достичь высокого запирающего напряжения. При этом чтобы обеспечить защиту указанных ПТУП-транзисторов, к выводам затворов этих транзисторов подсоединяют диоды, а именно защитные диоды D1-D5, работающие в запирающем режиме. Защитные диоды соединяют между собой выводы затворов ПТУП-транзисторов, или говоря другими словами, каждый из них подсоединен между соответствующим выводом затвора и общим выводом 1, имеющим потенциал земли, с которым также соединен МОП-транзистор. Принцип действия защитных диодов D1-D5 для защиты ПТУП-транзисторов раскрыт в патенте US 6822842.

Из-за разной или слишком высокой емкости перехода защитных диодов D1-D5 на ПТУП-транзисторах может возникнуть неравномерное распределение запирающего напряжения. В частности, на самом верхнем ПТУП-транзисторе J6 (см. фиг.1) присутствует емкость, отличающаяся от емкостей, имеющихся на выводах затворов нижних ПТУП-транзисторов. Такая неодинаковая нагрузка выводов затворов может сильно повлиять на динамическое распределение запирающего напряжения и привести к тому, что самый верхний транзистор возьмет на себя все напряжение между выводами, и в самом неблагоприятном случае он даже может разрушиться.

Сущность изобретения

В связи с вышесказанным задача данного изобретения заключается в том, чтобы создать такое переключающее устройство с последовательным соединением ПТУП-транзисторов вышеназванного типа, которое лишено перечисленных недостатков.

Эта задача решена путем разработки переключающего устройства с последовательным включением ПТУП-транзисторов, характеризующегося признаками пункта 1 формулы изобретения.

Предложенное переключающее устройство для переключения тока между первым выводом и вторым выводом содержит по меньшей мере два последовательно соединенных ПТУП-транзистора, из которых самый нижний ПТУП-транзистор соединен с первым выводом или соединен с первым выводом через последовательно включенные управляющие выключатели. Имеется по меньшей мере один дополнительный ПТУП-транзистор, последовательно соединенный с самым нижним ПТУП-транзистором, причем ПТУП-транзистор, наиболее удаленный от самого нижнего ПТУП-транзистора и называемый самым верхним ПТУП-транзистором, через свой вывод стока соединен с указанным вторым выводом. Между выводами затворов ПТУП-транзисторов и первым выводом подключена стабилизирующая схема для стабилизации напряжения затворов ПТУП-транзисторов. При этом между выводом затвора самого верхнего ПТУП-транзистора и вторым выводом подключена дополнительная схема, которая подтягивает потенциал на выводе затвора самого верхнего ПТУП-транзистора к потенциалу на выводе стока этого транзистора и уменьшает разность потенциалов.

Благодаря этому при включенном самом верхнем ПТУП-транзисторе напряжение на затворе поддерживается на уровне, немного превышающем или предпочтительно равном напряжению на выводе истока. В результате, при выключении самый верхний ПТУП-транзистор остается во включенном состоянии дольше, чем без дополнительной схемы. Благодаря этому обстоятельству предотвращается ситуация, при которой все напряжение между первым и вторым выводом приходится на самый верхний ПТУП-транзистор.

При помощи цепи, содержащей стабилизирующую схему и дополнительную схему, вышерасположенные ПТУП-транзисторы при выключении выключаются медленнее, а включаются быстрее, чем нижерасположенные ПТУП-транзисторы, и предпочтительно имеют синхронные моменты включения.

Таким образом, благодаря всей цепи, состоящей из стабилизирующей схемы и дополнительной схемы, балансируется и стабилизируется динамическое распределение запирающего напряжения силового выключателя, основанного на последовательно включенных транзисторах.

Вообще говоря, стабилизирующая схема может для каждого ПТУП-транзистора сама по себе отводить задаваемый ток между выводом его затвора и первым выводом. Дополнительная схема вместе со стабилизирующей схемой создает симметричную нагрузку по напряжению для выводов затворов последовательно включенных ПТУП-транзисторов.

Схему последовательного соединения ПТУП-транзисторов можно реализовать с обеспечением управления самого нижнего ПТУП-транзистора по каскодной схеме. При этом схема последовательного соединения содержит управляющий выключатель, например, МОП-транзистор, подключенный между первым выводом и самым нижним ПТУП-транзистором. В альтернативном случае ПТУП-транзисторами можно управлять по-другому, например, при помощи схемы управления, воздействующей непосредственно на вывод затвора самого нижнего ПТУП-транзистора.

Временную характеристику пассивного управления самым верхним ПТУП-транзистором, если управление осуществляется посредством одного или нескольких дополнительных диодов, можно регулировать, изменяя общую емкость переходов этих последовательно включенных дополнительных диодов. Емкость переходов можно регулировать, меняя количество последовательно включенных дополнительных диодов и/или параметры отдельных дополнительных диодов. Общее запирающее напряжение или напряжение пробоя одного или нескольких диодов между стоком и затвором самого верхнего ПТУП-транзистора выбирают так, чтобы оно было по меньшей мере приблизительно равно соответствующим значениям для остальных ПТУП-транзисторов.

В еще одном предпочтительном варианте изобретения емкость переходов дополнительных диодов поддерживают небольшой, вместо этого посредством отдельных элементов, например конденсаторов, регулируют емкость между вторым выводом и затвором самого верхнего ПТУП-транзистора (а также остальных ПТУП-транзисторов). Благодаря такой дополнительной симметризирующей схеме можно оптимизировать и ускорить переходные процессы при переключении. Соответственно, симметризирующая схема имеет RC-цепочку, расположенную между затворами ПТУП-транзисторов и первым выводом. Например, затворы каждых следующих друг за другом ПТУП-транзисторов соединены через последовательно включенный резистор и дополнительный конденсатор, а затвор самого верхнего ПТУП-транзистора посредством дополнительной RC-цепочки, предпочтительно той же структуры, соединен со вторым выводом.

В другом предпочтительном варианте изобретения затвор каждого ПТУП-транзистора, за исключением самого нижнего ПТУП-транзистора, посредством последовательно подключенных резистора и конденсатора соединен с первым выводом, при этом затвор самого верхнего ПТУП-транзистора соединен со вторым выводом посредством дополнительной схемы, предпочтительно дополнительной RC-цепочки, состоящей из последовательно соединенных резистора и дополнительного конденсатора.

В еще одном предпочтительном варианте изобретения затвор каждого ПТУП-транзистора, за исключением самого нижнего ПТУП-транзистора, посредством последовательно включенных резистора и конденсатора соединен с первым выводом, при этом затворы ПТУП-транзисторов посредством одного или нескольких диодов соединены со вторым выводом. Кроме того, затвор самого верхнего ПТУП-транзистора соединен со вторым выводом посредством дополнительной схемы, предпочтительно дополнительной RC-цепочки, состоящей из последовательно соединенных резистора и дополнительного конденсатора.

В других предпочтительных вариантах изобретения предусмотрен резистор для демпфирования, который используется не для каждого из конденсаторов (или для дополнительного конденсатора), а только для одного или нескольких конденсаторов, предпочтительно в вышерасположенных ПТУП-транзисторах.

В принципе в симметризирующей схеме возможно также параллельное включение резисторов и конденсаторов, однако такая конфигурация сопряжена со статическими потерями вследствие возникающего статичного делителя напряжения.

Симметризирующая схема предпочтительно выполнена таким образом, что переходные процессы, возникающие в этой схеме при переключении, в самом верхнем ПТУП-транзисторе имеют наименьшую постоянную времени, а в самом нижнем ПТУП-транзисторе имеют наибольшую постоянную времени. Соответственно емкость дополнительной RC-цепочки (или дополнительной емкостной цепочки) меньше емкости самой нижней RC-цепочки (или дополнительной емкостной цепочки), соединенной с затвором самого нижнего ПТУП-транзистора. Предпочтительно емкость промежуточных RC-цепочек или емкостных цепочек постепенно уменьшается сверху вниз. Благодаря взаимодействию симметризирующей схемы со стабилизирующей схемой переходные процессы в затворах ПТУП-транзисторов имеют сбалансированные постоянные времени.

В результате по сравнению со схемой без симметризирующей цепи при выключении транзисторов или ПТУП-транзисторов потенциал вывода затвора в вышерасположенных ПТУП-транзисторов достигает напряжения отсечки относительно соответствующего вывода истока в течение более длительного времени. Вследствие этого верхние ПТУП-транзисторы остаются включенными в течение более длительного времени, чем нижние ПТУП-транзисторы, и соответственно, верхние ПТУП-транзисторы выключаются медленнее. Наоборот, при включении верхние ПТУП-транзисторы включаются быстрее, чем без дополнительной схемы и симметризирующей схемы. В идеальном случае обеспечивается совершенно синхронное включение и выключение всех ПТУП-транзисторов.

Благодаря соответствующему выполнению симметризирующей схемы временные характеристики процессов, протекающих в отдельных переключателях, согласованы друг с другом, так что рассматриваемое переключающее устройство в целом обладает максимально сбалансированными характеристиками, то есть оно обеспечивает как можно более одновременное переключение отдельных ПТУП-транзисторов.

В еще одном варианте изобретения управляющий выключатель, например, МОП-транзистор, работает в линейном режиме. В результате обеспечивается демпфирование колебаний, возникающих из-за емкости перехода.

Таким образом, вместе с дополнительной схемой и симметризирующей схемой стабилизирующая схема образует между первым и вторым выводом динамический делитель напряжения, который при коммутационных процессах выравнивает нагрузку ПТУП-транзисторов по напряжению. По сравнению с известными силовыми выключателями или переключающими устройствами, предназначенными для переключения высоких рабочих напряжений, балансировка динамичной нагрузки транзисторов по запирающему напряжению существенно улучшается благодаря добавлению дополнительной схемы, например, дополнительных диодов. Кроме того, в предпочтительном варианте изобретения ее можно целенаправленно оптимизировать при помощи RC-цепей.

Остальные предпочтительные варианты изобретения раскрыты в зависимых пунктах формулы изобретения.

Краткое описание чертежей

Ниже изобретение описано более подробно на примере предпочтительных вариантов его осуществления, проиллюстрированных приложенными чертежами, из которых:

фиг.1 изображает схему последовательного соединения ПТУП-транзисторов, соответствующую известному уровню техники;

фиг.2 иллюстрирует первый вариант изобретения;

фиг.3 иллюстрирует второй вариант изобретения;

фиг.4 иллюстрирует еще один вариант изобретения.

Номера позиций, используемых на чертежах, и соответствующие им значения указаны в перечне ссылочных обозначений. При этом одинаковые элементы обозначены на чертежах одинаковыми номерами позиций.

Варианты изобретения

На фиг.1 представлено переключающее устройство высокого рабочего напряжения. Оно содержит каскодную схему соединения МОП-транзистора М с первым или самым нижним ПТУП-транзистором J1 и подключенными последовательно с этим первым ПТУП-транзистором J1 одним или несколькими дополнительными ПТУП-транзисторами J2-J6. Таким образом, самый нижний или первый ПТУП-транзистор управляется в данной каскодной схеме МОП-транзистором, действующим как управляющий выключатель. Последний ПТУП-транзистор из последовательно включенных ПТУП-транзисторов, т.е. транзистор, наиболее удаленный от первого ПТУП-транзистора, также называют самым верхним ПТУП-транзистором J6. На этом чертеже в качестве примера показаны шесть ПТУП-транзисторов, однако согласно другим вариантам изобретения их может быть два или больше. Для стабилизации напряжения на затворах ПТУП-транзисторов предусмотрена стабилизирующая схема 3. В этой схеме между затворами каждой пары следующих друг за другом ПТУП-транзисторов имеется последовательное подключение защитных диодов D11-D13, D21-D23,…D51-D53, действующих в запирающем направлении. Количество защитных диодов D11-D53, подсоединенных последовательно друг другу, зависит от требуемого запирающего напряжения этих защитных диодов D11-D53. Говоря в общем, между затворами каждых двух следующих друг за другом ПТУП-транзисторов может иметься один или несколько защитных диодов D11-D53. В других вариантах изобретения используются не диоды, а иные коммутирующие элементы.

Между затвором и истоком каждого ПТУП-транзистора J2-J6, за исключением первого ПТУП-транзистора, подключены полупроводниковые стабилитроны (на фиг.1: ZGS,2-ZGS,6) или резисторы (на фиг.2: ZGS,2-ZGS,6). Эти стабилитроны и резисторы стабилизируют напряжение соответствующего затвора в стационарном состоянии.

Для выравнивания напряжения нагрузки ПТУП-транзисторов между затвором и выводом стока самого верхнего ПТУП-транзистора подключена дополнительная схема 4. В соответствии с фиг.2 эта схема содержит последовательное включение трех дополнительных диодов D61, D62, D63, действующих в запирающем направлении. Благодаря указанным диодам потенциал вывода затвора самого верхнего ПТУП-транзистора подтягивается к потенциалу на выводе стока этого транзистора. В результате, напряжение, приложенное между выводом стока и выводом затвора, уменьшается. Дополнительные диоды D61, D62, D63 обеспечивают симметричную нагрузку на выводах затворов и стабилизируют распределение запирающего напряжения. Кроме того, эти диоды действуют в качестве защитного элемента для самого верхнего ПТУП-транзистора J6, защищая его от перенапряжения между стоком и затвором.

Вместо дополнительных диодов в дополнительной схеме можно использовать другие коммутирующие элементы, приводящие к тому же результату, например, один, два или большее число последовательно включенных диодов, резистор, конденсатор или RC-цепочку.

В предпочтительном варианте изобретения между затворами каждой пары следующих друг за другом ПТУП-транзисторов параллельно одному или нескольким защитным диодам D11-D53 подключена RC-цепочка, состоящая из последовательно подсоединенных резистора или демпфирующего резистора RSt,1-RSt,5 и конденсатора СTu,1-СTu,5. В этом случае параллельно дополнительной схеме 4 между затвором и выводом стока самого верхнего ПТУП-транзистора подключена аналоговая цепь, предпочтительно RC-цепочка той же структуры. Вместе все вышеназванные RC-цепочки образуют симметризирующую схему 5.

В этом случае вся схема имеет от 1 до n дополнительных диодов D61, D62, D63 и пассивную RC-цепочку из демпфирующих резисторов RSt,1-RSt,6 и конденсаторов СTu,1-СTu,6.

Благодаря последовательному включению диодов можно сохранить небольшую общую емкость перехода, добавляемую между каждыми выводами затворов. Этот дает возможность, благодаря дополнительным конденсаторам СTu,1…СTu,6 оптимизировать динамическое распределение запирающего напряжения или регулировать его независимо от емкостей перехода. При этом дополнительные демпфирующие резисторы Rst,1…Rst,6 позволяют демпфировать колебания, вызванные дополнительными конденсаторами СTu,1…СTu,6.

На фиг.3 показан альтернативный предпочтительный вариант изобретения, при котором затворы ПТУП-транзисторов J1-J6 друг с другом не соединены, но каждый из них по отдельности посредством своей цепи, состоящей из защитных диодов D11-D53 и RC-цепочки, соединен с первым выводом 1. Как и в варианте изобретения, показанном на фиг.2, вывод затвора G6 самого верхнего ПТУП-транзистора J6 соединен через дополнительную цепь 4 со вторым выводом 2. И в этом случае дополнительная цепь 4 может содержать один или несколько последовательно включенных дополнительных диодов D61-D63 или другие коммутирующие элементы, или дополнительные диоды D61-D63, скомбинированные с последовательной RC-цепочкой RSt,6, CTu,6. И в этом случае оптимальные сами по себе и примененные для оптимизации RC-цепочки RSt,1…RSt,6 и СTu,1…СTu,6 вместе образуют симметризирующую схему 5.

На фиг.4 показан еще один вариант изобретения, при котором затворы ПТУП-транзисторов J1-J6 друг с другом не соединены, но каждый из них по отдельности соединен со своей цепью, состоящей из защитных диодов D11-D23, и с одним или несколькими дополнительными диодами 6, которые соединяют соответствующий вывод затвора со вторым выводом, кроме того они соединены с первым выводом 1 через RC-цепочку. Защитные диоды D11-D23 и дополнительные диоды 6 образуют для каждого напряжения затвора делитель напряжения, отдельно параметризируемый в отношении уровня напряжения и динамических свойств (постоянных времени). Вместо показанных на чертеже отдельных дополнительных диодов 6 можно использовать несколько последовательно включенных диодов. Как и в варианте, показанном на фиг.3, в этом случае дополнительная цепь 4 также может содержать один или несколько последовательно включенных дополнительных диодов D61-D63 или другие коммутирующие элементы, или дополнительные диоды D61-D63, скомбинированные с последовательной RC-цепочкой RSt,6, СTu,6. И в этом случае оптимальные сами по себе и примененные для оптимизации RC-цепочки RSt,1…RSt,6 и CTu,1…СTu,6 вместе образуют симметризирующую схему 5.

Предложенную схему, описанную в настоящем изобретении в целом, а также в конкретных примерах его выполнения, можно применять не только для рассмотренных здесь n-канальных ПТУП-транзисторов, но также при соответствующих изменениях, и для p-канальных ПТУП-транзисторов.

1. Переключающее устройство для переключения тока между первым выводом (1) и вторым выводом (2), содержащее по меньшей мере два последовательно подсоединенных ПТУП-транзистора (J1-J6) (полевых транзистора с управляющим р-n-переходом),

из которых самый нижний ПТУП-транзистор (J1) соединен с первым выводом (1), или этот самый нижний ПТУП-транзистор (J1) соединен по каскодной схеме с первым выводом (1) через управляющий выключатель (М),

и по меньшей мере один дополнительный ПТУП-транзистор (J2-J5), последовательно соединенный с указанным самым нижним ПТУП-транзистором (J1), причем ПТУП-транзистор (J6), наиболее удаленный от самого нижнего ПТУП-транзистора (J1) и называемый самым верхним ПТУП-транзистором (J6), через свой вывод стока соединен со вторым выводом (2),

при этом между выводами затворов ПТУП-транзисторов (J1-J6) и первым выводом (1) подключена стабилизирующая схема (D11-D53), обеспечивающая стабилизацию напряжения затворов ПТУП-транзисторов (J1-J6),

причем между выводом затвора (G6) самого верхнего ПТУП-транзистора (J6) и вторым выводом (2) подсоединена дополнительная схема (4), которая подтягивает потенциал на выводе затвора (G6) самого верхнего ПТУП-транзистора (J6) к потенциалу на выводе стока (D6) этого транзистора (J6),

при этом между затворами ПТУП-транзисторов (J1-J6) и первым выводом предусмотрена симметризирующая схема (5), содержащая RC-цепочку,

причем симметризирующая схема (5) выполнена таким образом, что переходные процессы, возникающие в этой схеме при переключении, в самом верхнем ПТУП-транзисторе (J6) имеют наименьшую постоянную времени, а в самом нижнем ПТУП-транзисторе (J1) имеют наибольшую постоянную времени.

2. Устройство по п.1, в котором указанная стабилизирующая схема (3) отводит задаваемый ток от вывода затвора каждого из ПТУП-транзисторов (J1-J6) к первому выводу (1), в частности, посредством действующих в запирающем направлении защитных диодов (D11-D53), каждый из которых расположен между выводами затворов соответствующих следующих друг за другом ПТУП-транзисторов (J1-J6) или между выводом затвора соответствующего ПТУП-транзистора (J1-J6) и первым выводом (1).

3. Устройство по п.1 или 2, в котором дополнительная схема (4) вместе со стабилизирующей схемой (3) создает симметричную нагрузку по напряжению для выводов затворов ПТУП-транзисторов (J1-J6).

4. Устройство по п.1 или 2, в котором дополнительная схема (4) содержит один или несколько дополнительных диодов (D61, D62, D63), которые последовательно подсоединены между выводом затвора (G6) самого верхнего ПТУП-транзистора (J6) и вторым выводом (2) и действуют в запирающем направлении.

5. Устройство по п.1 или 2, в котором дополнительная схема (4) представляет собой пассивную цепь, в частности резистор, причем эта пассивная цепь, в частности резистор, подключена между выводом затвора (G6) самого верхнего ПТУП-транзистора (J6) и вторым выводом (2).

6. Устройство по п.1 или 2, в котором стабилизирующая схема (3) между выводами затворов каждых следующих друг за другом ПТУП-транзисторов содержит по меньшей мере один диод с первым общим запирающим напряжением, действующий в запирающем направлении, при этом дополнительная схема (4) содержит по меньшей мере один дополнительный диод (D61, D62, D63) со вторым общим запирающим напряжением, действующий в запирающем направлении, причем второе общее запирающее напряжение по меньшей мере приблизительно равно первому общему запирающему напряжению.

7. Устройство по п.1, в котором указанная симметризирующая схема (5) между выводами затворов каждых следующих друг за другом ПТУП-транзисторов (J1-J6) содержит конденсатор (CTu,1-CTu,5), а также содержит дополнительный конденсатор (CTu,6), установленный параллельно дополнительной схеме (4), при этом последовательно по меньшей мере с одним из конденсаторов (CTu,1-CTu,5) и/или к указанному дополнительному конденсатору (CTu,6) подсоединен демпфирующий резистор (RSt,1-RSt,5,RSt,6).

8. Устройство по п.1, в котором симметризирующая схема (5) между выводами затворов каждых следующих друг за другом ПТУП-транзисторов (J2-J6), за исключением самого нижнего ПТУП-транзистора (J1) и первого вывода (1), содержит RC-цепочку (RSt,1-RSt,5 и CTu,1-CTu,5), а также содержит дополнительную RC-цепочку (RSt,6, CTu,6), установленную параллельно указанной дополнительной схеме (4).

9. Устройство по п.8, содержащее схему управления, регулирующую управляющий выключатель (М) таким образом, что он работает в линейном режиме.

Увеличение мощности стабилизированных источников | Техника и Программы

Одним из наиболее распространенных требований при доработке источников питания является увеличение выходного тока или мощности. Часто это может быть связано со стоимостью и трудностями при проектировании и изготовлении нового источника. Рассмотрим несколько способов увеличения выходной мощности существующих источников.

Первое, что вообще приходит на ум, — параллельное включение мощных транзисторов. В линейном стабилизаторе это относилось бы к проходным транзисторам или, в некоторых случаях, к параллельным стабилизирующим транзисторам. В таких источниках простое соединение одноименных выводов транзисторов обычно не дает практических результатов из-за неравномерного распределения тока между транзисторами. При повышении рабочей температуры неравномерное распределение нагрузки становится еще большим до тех пор, пока практически весь ток нафузки не потечет через один из транзисторов. Предложенный вариант может быть реализован при условии, что параллельно соединенные транзисторы имеют совершенно идентичные характеристики и работают при одинаковой температуре. Такое условие практически не реализуемо из-за относительно больших разбросов в характеристиках биполярных транзисторов.

С другой стороны, если в линейном стабилизаторе используются мощные МОП-транзисторы, простое их запараллеливание работать будет, потому что эти устройства имеют температурные коэффициенты другого знака по сравнению с мощными биполярными транзисторами и не будут подвергаться сильному нафеву или перераспределению тока. Но МОП-транзисторы использовались чаще в ИИП, чем в линейных стабилизаторах (наше рассмотрение этих не импульсных стабилизаторов дает некоторое понимание проблем параллельного включения транзисторов и в импульсных стабилизаторах).

Рис. 17.24 показывает, как осуществлять параллельное включение транзисторов в линейном или импульсном источнике питания. Резисторы с небольшим сопротивлением, включенные в цепи эмиттеров биполярных транзисторов, обеспечивают индивидуальное смещение между базой и эмиттером, что препятствует возможности увеличения доли тока, протекающего через какой-либо из транзисторов. Хотя применение этих так называемых балластных эмиттерных резисторов очень эффективно при опасном перераспределении токов или повышении температуры, следует использовать самое минимальное сопротивление резисторов, которое достаточно для этой цели. В противном случае будет рассеиваться заметная мощность, что особенно нежелательно в импульсных стабилизаторах, где основным достоинством является высокий к.п.д. Не удивительно поэтому, что балластные эмиттерные резисторы имеют сопротивления порядка 0,1 Ома, 0,05 Ома или меньше, а фактическая величина будет, конечно, зависеть прежде всего от тока эмиттера конкретного источника. В качестве оценки можно принять величину 1//, где / – максимальный ток эмиттер (или коллектора).

Вместо эмиттерных резисторов, иногда можно выравнить распределение тока в параллельно соединенных биполярных транзисторах, включая несколько более высокоомные резисторы в цепь базы. Они обычно имеют сопротивление от 1 до 10 Ом. Хотя полное рассеяние мощности в этом случае меньше, но эффективность ниже, чем при использовании эмиттерных резисторов.

Рис. 17.24. Способ параллельного включения мощных биполярных транзисторов. Любая попытка отдельного транзистора пропускать больший ток или перегреться предотвращается благодаря напряжению смещения на его эмиттерном резисторе.

В импульсном стабилизаторе недостаточно просто позаботиться о распределении тока в описанных статических условиях; во внимание необходимо также принять динамику процесса переключения. Это требует большего внимания к согласованности транзисторных характеристик. Практически обнаружено, что два мощных транзистора одного и того же типа и названия могут вести себя при переключении по-разному, один из них может быть несколько медленнее, чем другой. Хотя опасность такого расхождения можно свести на нет введением балластных эмиттерных резисторов, их сопротивления, возможно, придется выбирать достаточно высокими по сравнению со случаем, когда характеристики транзисторов близки. Однако даже если динамические характеристики отдельных транзисторов в параллельном соединении достаточно близки.

влияние неравной длины проводников или неидентичная разводка могут вызывать существенные различия в рассеиваемой мощности.

Чаще всего оказывается, что можно удвоить выходную мощность, соединив параллельно два биполярных транзистора и, скорее всего, не потребуется модернизировать задающий каскад. Однако в других случаях, вероятно, будет необходим больший ток от задающего устройства. Таким образом, при трех, четырех или большем числе выходных транзисторов в задающем каскаде также потребуется параллельное соединение транзисторов. Иногда оказывается, что в задающем устройстве целесообразнее применить транзистор с большей номинальной мощностью.

Мощные МОП-транзисторы можно включать параллельно без балластных резисторов. Часто четыре или больше таких транзисторов могут работать от задающего каскада, который работал с одним транзистором. Однако метод, показанный на рис. 17.25, рекомендуется для предупреждения паразитных колебаний в диапазоне метровых и дециметровых волн. С феррито-выми бусинками может потребоваться некоторое экспериментирование. Часто эффективное затухание обеспечивается введением двух или трех витков провода. Другой метод предлагает использовать небольшие пленочные рези-стсфы с сопротивлением от 100 до 1000 Ом в цепи затвора. Стабилитроны, показанные на рис. 17.25, включены в структуры специально разработанных МОП-транзисторов. Другие МОП-транзисторы не имеют такой защиты затвора, но метод параллельного включения остается тем же самым.

Рис. 17.25. Способ параллельного включения мощных МОП-транзисторов. Это простой путь увеличить нагрузочную способность по току как импульсных, так и линейных стабилизаторов. Ферритовая бусинка в цепи затвора подавляет высокочастотную паразитную генерацию. Стабилитроны находятся внутри транзисторов. Siliconix.

Мощный импульсный каскад на МОП-транзисторе может применяться также в последовательной схеме, чтобы обеспечить более высокое напряжение на выходе. Схема такого устройства изображена на рис. 17.26 для двух транзисторов, но их количество может быть и больше. Интересной чертой этого метода является то, что входной сигнал подается только на один МОП-транзистор. Происходит это потому, что на затворе другого

МОП-траНзистора имеется напряжение +15 В относительно земли; этот МОП-транзистор готов проводить, как только цепь его истока оказывается замкнутой запускаемым МОП-транзистором. Такая конструкция позволяет удвоить мощность, подводимую к нагрузке по сравнению с той которую можно получить от одного МОП-Транзистора; в то же самое время каждый МОП-транзистор работает в пределах номинального напряжения между стоком и истоком. /?С-цепь в цепи затвора верхнего МОП-транзистора осуществляет динамическую балансировку напряжений на затворах двух МОП-транзисторов. В первом приближении R\C\ должно равняться В2С2,

Рис. 17.26. Последовательное соединение мощных МОП-транзисторов для удвоенного рабочего напряжения. Этот метод можно распространить на большее число мощных МОП-транзисторов. Обратите внимание, что сигнал запуска поступает только на один затвор. Хотя показанный специализированный мощный МОП-транзистор имеет внутренний стабилитрон, большинство других его не имеют. Siliconex.

Поскольку появились мощные высоковольтные МОП-транзисторы, последовательная конфигурация не используется как раньше, когда эти транзисторы только стали конкурентоспособными с биполярными транзисторами. Кроме того, свойственная им легкость работы в параллельном режиме исключает трудности при расчете схем. Параллельная конфигурация проще в реализации, потому что легче обеспечить одинаковые температурные условия, которые требуется в обеих схемах для оптимальной работы. Последовательный вариант может быть выбран в системах, где постоянное рабочее напряжение превышает номинальное значение для одного МОП-транзистора.

Мало того, что некоторые мощные МОП-транзисторы содержат во входной цепи эквивалент стабилитрона для защиты затвора, изготовители этих устройств могут включить в выходную цепь «фиксирующий» диод. По этой причине во многих ИИП и схемах управления двигателями, использующих мощные МОП-транзисторы не включают обычный фиксирующий диод, который используется в схеме с биполярным транзистором. Это можно отнести к дополнительным достоинствам, так как уменьшается число используемых компонент и снижается стоимость. Когда для увеличения допустимой мощности применяется параллельное соединение, это может быть особенно существенно, потому что не требуется рассчитанного на большие токи, дорогого «внешнего» диода. Однако следует изучить технические условия изготовителя, чтобы установить, подходит ли для конкретного применения используемое устройство. В некоторых случаях может понадобиться внешний диод Шотки или диод с малым временем восстановления, чтобы обеспечить очень высокую скорость переключения индуктивных нагрузок.

Способ повышения выходной мощности с использованием комплементарных транзисторов уже упоминался на примере биполярных транзисторов (рис. 2.8 и 2.12). До недавнего времени простые схемы и хорошие характеристики этого метода были доступны только при использовании биполярных мощных транзисторов, где имелись согласованные пары прп и рпр транзисторов. Однако теперь несколько изготовителей разместили на рынке /^-канальные МОП-транзисторы, имеющие характеристики, зеркальные по отношению к л-канальным, поэтому можно создавать схемы на мощных комплементарных МОП-транзисторах. Хотя схемы на биполярных транзисторах, изображенные на рис. 2.8 и рис. 2.12, являются генераторами с насыщаемым сердечником, стоит отметить, что лишь небольшие изменения необходимы в схеме и режиме работы, чтобы получить инверторы или преобразователи с внешним возбуждением. Кроме того, используя цепи обратной связи и управления, подобные тем, что применялись в других стабилизаторах, можно реализовать стабилизированные источники.

В настоящее время имеется несколько полупроводниковых фирм, таких как International Rectifier, Intersil, Supertex и Westinghouse, которые производят мощные МОП-транзисторы, подходящие для применения в комплементарных схемах. Препятствия, которые задержали появление кремниевых рпр мощных транзисторов, не столь серьезны при производстве /^-канальных МОП-транзисторов. Поэтому можно ожидать, что другие компании скоро будут торговать устройствами, содержащими пару комплементарных МОП-транзисторов для импульсных применений.

Еще одна схема, в которой складываются мощности, показана на рис. 17.27. Здесь выходы идентичных выходных каскадов соединены последовательно, что позволяет эффективно объединять возможности транзисторов без применения балластных резисторов. Это прекрасный способ обойтись без мощных транзисторов, работающих с более высокими напряжениями или номинальными токами, – такие устройства могут быть или недоступны или очень дороги. Это устройство лучше рассмотреть на начальном этапе конструирования инвертора или стабилизированного источника, тогда будет легко определить входные и выходные обмотки трансформаторов. Фазирование вторичных обмоток выходных трансформаторов должно быть таким, чтобы выходные напряжения складывались. Относительно легко получить равный вклад токов от мощных транзисторов и хорошо, если все транзисторы работают при одной и той же температуре. Обычно это достигается путем применения общего радиатора. В этом отношении схема с общим коллектором, а не показанная на рисунке схема с общим эмиттером, более предпочтительна, поскольку не требуется никакой изоляции между корпусом транзистора и радиатором.

Рис. 17.27. Схема удвоения выходной мощности инвертора или импульсного стабилизатора. Этот метод не требует дорогих или недоступных высоковольтных или предназначенных для работы при больших токах транзисторов. В отличие от схем с параллельным включением транзисторов здесь не требуются балластные резисторы, рассеивающие мощность.

К недостаткам этого метода можно отнести высокую стоимость, а также увеличенные габариты и вес. Это справедливо потому, что два трансформатора дороже, чем один, имеющий вдвое большую номинальную мощность. Габариты двух трансформаторов будут, как правило, превышать размеры одного трансформатора той же мощности. Существенны или нет эти факторы зависит, конечно, от конкретных обстоятельств, связанных с особенностями системы.

Хотя на рис. 17.27 показаны два выходных каскада, объединять можно и большее число каскадов. Но основную идею, предлагаемую здесь, не следует путать с вариантом, показанным на рис. 2.10, где используется один выходной трансформатор, а пары выходных транзисторов соединены последовательно по отношению к источнику постоянного напряжения. Схема на рис. 17.27 предпочтительнее для инверторов с внешним возбуждением и ИИП, а схема на рис. 2-10 лучше подходит для реализации инвертора с насыщаемым сердечником. В схеме, приведенной на рис. 17.27, можно использовать один сердечник для всех входных трансформаторов и один для выходных. Конечно, это так, однако использование отдельных трансформаторов, как показано на рисунке, представляется наиболее разумным для испытаний, оценки возможностей, измерения и эксплуатации.

Примером гибкости схемы на рис. 17.27 является возможность использовать в качестве одной из пар мощные /?/7/?-транзисторы. Хотя это не приводит к схеме с комплементарными транзисторами в обычном смысле, но в некоторых случаях оказывается проще получить требуемую суммарную мощность. По переменному току функционирование схемы не изменилось.

Интересный способ удвоить выходной ток и, поэтому, выходную мощность одно-транзисторного импульсного стабилизатора, показан на рис. 17.28. Сигнал на дополнительный переключающий транзистор Q2 поступает со сдвигом на 180** по отношению к сигналу, поступающему на основной транзистор Q\. Этот сдвиг фазы осуществляется с помощью трансформатора 71. Хотя отношение числа витков первичной и вторичной обмоток можно взять равным 1, низкие входные сопротивления транзисторов обычно требуют для получения оптимальных результатов использовать понижающий трансформатор. В этом случае вторичная обмотка с отводом от середины обеспечит более низкое напряжение на базе каждого транзистора, чем имеющееся на первичной обмотке. (Это, кроме того, снижает вероятность обратного пробоя эмиттерных переходов транзисторов. Полезным может оказаться включение в цепь базы (на рисунке не показано) резистора с малым сопротивлением.)

Потребуется также катушка индуктивности L2 аналогичная катушке L\, Дополнительный «фиксирующий» диод D2 идентичен диоду D\. Удвоение выходного тока стабилизатора не единственное, что дает дополнительный переключающий транзистор. В этой схеме удваивается частота пульсаций и вдвое уменьшается их амплитуда. Таким образом, с прежней емкостью выходного конденсатора С1 на выходе стабилизатора имеем более чистое постоянное напряжение. Другой вариант состоит в том, чтобы сохранить характеристики одно-транзисторной схемы, уменьшая емкость конденсатора С1. Этот вариант позволяет несколько сократить габариты и стоимость. Если следовать этой методике на начальной стадии проектирования, то можно выбрать менее дорогие переключающие транзисторы, потому что каждый должен будет переключаться с частотой, равной половине частоты пульсаций на выходе.

Рис. 17.28. Метод удвоения выходного тока импульсного стабилизатора. Этот метод обеспечивает не только увеличение выходной мощности, но и уменьшает пульсации выходного напряжения. (А) Упрощенная схема обычного импульсного стабилизатора. (В) Модифицированная схема для удвоения выходного тока.

Чтобы воспользоваться достоинствами этой схемы, нестабилизированный источник постоянного напряжения должен, конечно, обеспечивать ток, вдвое больший требуемого для одно-транзисторного стабилизатора. Схемы на рис. 17.28 А и В представляют собой стабилизаторы с внешним возбуждающим сигналом, имеющим фиксированную частоту. Если применять этот метод в автоколебательном стабилизаторе, то могут встретиться некоторые трудности и, естественно, потребуется экспериментальная доводка. Связано это с тем, что частота пульсаций, используемых в цепи обратной связи, вдвое выше частоты переключений.