Полупроводниковая схемотехника

Полупроводниковая схемотехника

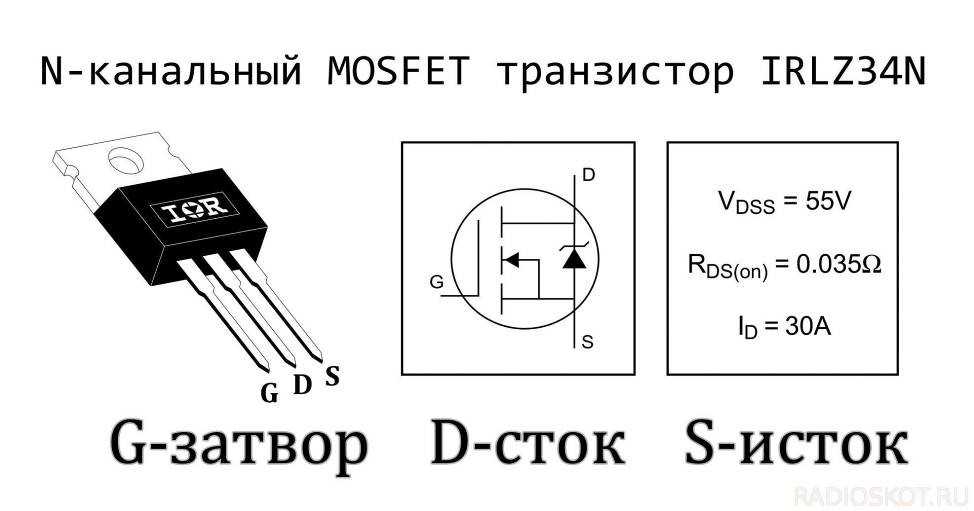

ОглавлениеПредисловие редактора переводаЧасть I. Основные положения 1. Пояснение применяемых величин 2.  2.1. ФИЛЬТР НИЖНИХ ЧАСТОТ 2.1.3. ДЛИТЕЛЬНОСТЬ ФРОНТА ИМПУЛЬСА И ЧАСТОТА СРЕЗА ФИЛЬТРА 2.2. ФИЛЬТР ВЕРХНИХ ЧАСТОТ 2.3. КОМПЕНСИРОВАННЫЙ ДЕЛИТЕЛЬ НАПРЯЖЕНИЯ 2.4. ПАССИВНЫЙ ПОЛОСОВОЙ RC-ФИЛЬТР 2.5. МОСТ ВИНА-РОБИНСОНА 2.6. ДВОЙНОЙ Т-ОБРАЗНЫЙ ФИЛЬТР 2.7. КОЛЕБАТЕЛЬНЫЙ КОНТУР 3. Диоды 3.2. СТАБИЛИТРОНЫ 3.3. ВАРИКАПЫ 4. Транзистор и схемы на его основе 4.2. СХЕМА С ОБЩИМ ЭМИТТЕРОМ 4.2.2. НЕЛИНЕЙНЫЕ ИСКАЖЕНИЯ 4.2.3. СХЕМА С ОБЩИМ ЭМИТТЕРОМ И ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО ТОКУ 4.2.4. ОТРИЦАТЕЛЬНАЯ ОБРАТНАЯ СВЯЗЬ ПО НАПРЯЖЕНИЮ 4.2.5. УСТАНОВКА РАБОЧЕЙ ТОЧКИ 4.3. СХЕМА С ОБЩЕЙ БАЗОЙ 4.4. СХЕМА С ОБЩИМ КОЛЛЕКТОРОМ, ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ 4.5.2. БИПОЛЯРНЫЙ ИСТОЧНИК ПИТАНИЯ 4.5.3. СХЕМА «ТОКОВОГО ЗЕРКАЛА» 4.6. СХЕМА ДАРЛИНГТОНА 4.7. ДИФФЕРЕНЦИАЛЬНЫЕ УСИЛИТЕЛИ 4.7.2. РЕЖИМ БОЛЬШОГО СИГНАЛА 4.7.3. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО ТОКУ 4.  7.4. НАПРЯЖЕНИЕ РАЗБАЛАНСА 7.4. НАПРЯЖЕНИЕ РАЗБАЛАНСА4.8. ИЗМЕРЕНИЕ НЕКОТОРЫХ ПАРАМЕТРОВ ПРИ МАЛОМ СИГНАЛЕ 4.9. ШУМЫ ТРАНЗИСТОРА 4.10. ПРЕДЕЛЬНЫЕ ПАРАМЕТРЫ 5. Полевые транзисторы 5.2. ХАРАКТЕРИСТИКИ И ПАРАМЕТРЫ МАЛЫХ СИГНАЛОВ 5.3. ПРЕДЕЛЬНЫЕ ЭЛЕКТРИЧЕСКИЕ ПАРАМЕТРЫ 5.4. ОСНОВНЫЕ СХЕМЫ ВКЛЮЧЕНИЯ 5.4.2. СХЕМА С ОБЩИМ ЗАТВОРОМ 5.4.3. СХЕМА С ОБЩИМ СТОКОМ, ИСТОКОВЫЙ ПОВТОРИТЕЛЬ 5.5. ПОЛЕВОЙ ТРАНЗИСТОР КАК СТАБИЛИЗАТОР ТОКА 5.6. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ 5.7. ПОЛЕВОЙ ТРАНЗИСТОР В КАЧЕСТВЕ УПРАВЛЯЕМОГО СОПРОТИВЛЕНИЯ 6. Операционный усилитель 6.1. СВОЙСТВА ОПЕРАЦИОННОГО УСИЛИТЕЛЯ 6.2. ПРИНЦИП ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗИ 6.3. НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ 6.4. ИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ 7. Внутренняя структура операционных усилителей 7.2. ПРОСТЕЙШИЕ СХЕМЫ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 7.3. СТАНДАРТНАЯ СХЕМА ИНТЕГРАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ 7.4. КОРРЕКЦИЯ ЧАСТОТНОЙ ХАРАКТЕРИСТИКИ  2. ПОЛНАЯ ЧАСТОТНАЯ КОРРЕКЦИЯ 2. ПОЛНАЯ ЧАСТОТНАЯ КОРРЕКЦИЯ7.4.3. ПОДСТРАИВАЕМАЯ ЧАСТОТНАЯ КОРРЕКЦИЯ 7.4.4. СКОРОСТЬ НАРАСТАНИЯ 7.4.5. КОМПЕНСАЦИЯ ЕМКОСТНОЙ НАГРУЗКИ 7.5. ИЗМЕРЕНИЕ ПАРАМЕТРОВ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 8. Простейшие переключающие схемы 8.1. ТРАНЗИСТОРНЫЙ КЛЮЧ 8.2. БИСТАБИЛЬНЫЕ РЕЛАКСАЦИОННЫЕ СХЕМЫ 8.2.2. ТРИГГЕР ШМИТТА 8.3. МОНОСТАБИЛЬНАЯ РЕЛАКСАЦИОННАЯ СХЕМА 8.4. НЕСТАБИЛЬНАЯ РЕЛАКСАЦИОННАЯ СХЕМА 9. Базовые логические схемы 9.1. ОСНОВНЫЕ ЛОГИЧЕСКИЕ ФУНКЦИИ 9.2. СОСТАВЛЕНИЕ ЛОГИЧЕСКИХ ФУНКЦИЙ 9.3. ПРОИЗВОДНЫЕ ОСНОВНЫХ ЛОГИЧЕСКИХ ФУНКЦИЙ 9.4. СХЕМОТЕХНИЧЕСКАЯ РЕАЛИЗАЦИЯ ОСНОВНЫХ ЛОГИЧЕСКИХ ФУНКЦИЙ 9.4.1. РЕЗИСТИВНО-ТРАНЗИСТОРНАЯ ЛОГИКА (РТЛ) 9.4.2. ДИОДНО-ТРАНЗИСТОРНАЯ ЛОГИКА (ДТЛ) 9.4.3. ТРАНЗИСТОРНО-ТРАНЗИСТОРНАЯ ЛОГИКА (ТТЛ) 9.4.4. ИНТЕГРАЛЬНАЯ ИНЖЕКЦИОННАЯ ЛОГИКА 9.4.5. ЭМИТТЕРНО-СВЯЗАННАЯ ЛОГИКА (ЭСЛ) 9.4.6. n-КАНАЛЬНАЯ МОП-ЛОГИКА 9.4.7. КОМПЛЕМЕНТАРНАЯ МОП-ЛОГИКА (КМОП) 9.4.8. ОБЗОР 9.  4.9. СПЕЦИАЛЬНЫЕ СХЕМЫ ВЫХОДНЫХ КАСКАДОВ 4.9. СПЕЦИАЛЬНЫЕ СХЕМЫ ВЫХОДНЫХ КАСКАДОВ9.5. ИНТЕГРАЛЬНЫЕ ТРИГГЕРЫ 9.5.2. ТРИГГЕРЫ ТИПА M-S (MASTER-SLAVE) 9.5.3. ДИНАМИЧЕСКИЙ ТРИГГЕР 9.6.2. ПОСТОЯННЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА (ПЗУ) 9.6.3. ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ МАТРИЦЫ (ПЛМ) 10. Оптоэлектронные приборы 10.1. ОСНОВНЫЕ ПОНЯТИЯ ФОТОМЕТРИИ 10.2. ФОТОРЕЗИСТОР 10.3. ФОТОДИОДЫ 10.4. ФОТОТРАНЗИСТОРЫ 10.5. СВЕТОДИОДЫ 10.6. ОПТРОНЫ Часть II. Применения 11. Линейные и нелинейные аналоговые вычислительные схемы 11.1. СХЕМА СУММИРОВАНИЯ 11.2. СХЕМЫ ВЫЧИТАНИЯ 11.2.2. СХЕМА ВЫЧИТАНИЯ НА ОПЕРАЦИОННОМ УСИЛИТЕЛЕ 11.3. БИПОЛЯРНОЕ УСИЛИТЕЛЬНОЕ ЗВЕНО 11.4. СХЕМЫ ИНТЕГРИРОВАНИЯ 11.4.1. ИНВЕРТИРУЮЩИЙ ИНТЕГРАТОР 11.4.2. ЗАДАНИЕ НАЧАЛЬНЫХ УСЛОВИЙ 11.4.3. СУММИРУЮЩИЙ ИНТЕГРАТОР 11.4.4. НЕИНВЕРТИРУЮЩИЙ ИНТЕГРАТОР 11.5.3. СХЕМА ДИФФЕРЕНЦИРОВАНИЯ С ВЫСОКИМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ 11.  6. РЕШЕНИЕ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ 6. РЕШЕНИЕ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ11.7. ФУНКЦИОНАЛЬНЫЕ ПРЕОБРАЗОВАТЕЛИ 11.7.2. ЭКСПОНЕНТА 11.7.3. ВЫЧИСЛЕНИЕ СТЕПЕННЫХ ФУНКЦИЙ С ПОМОЩЬЮ ЛОГАРИФМОВ 11.7.4. ФУНКЦИИ SIN X И COS X 11.7.5. ПЕРЕСТРАИВАЕМЫЕ ФУНКЦИОНАЛЬНЫЕ СХЕМЫ 11.8. АНАЛОГОВЫЕ СХЕМЫ УМНОЖЕНИЯ 11.8.2. УМНОЖЕНИЕ С ПОМОЩЬЮ ЛОГАРИФМИЧЕСКИХ ФУНКЦИОНАЛЬНЫХ ГЕНЕРАТОРОВ 11.8.3. СХЕМА УМНОЖЕНИЯ, ИСПОЛЬЗУЮЩАЯ ИЗМЕНЕНИЕ КРУТИЗНЫ ХАРАКТЕРИСТИКИ ТРАНЗИСТОРОВ 11.8.4. СХЕМА УМНОЖЕНИЯ С ИЗОЛИРОВАННЫМИ ЗВЕНЬЯМИ 11.8.6. СХЕМЫ ЧЕТЫРЕХКВАДРАНТНОГО УМНОЖЕНИЯ 11.8.7. ПРИМЕНЕНИЕ СХЕМЫ УМНОЖЕНИЯ ДЛЯ ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНЫХ КОРНЕЙ 11.9. ПРЕОБРАЗОВАНИЕ КООРДИНАТ 11.9.2. ПРЕОБРАЗОВАНИЕ ДЕКАРТОВЫХ КООРДИНАТ В ПОЛЯРНЫЕ 12. Управляемые источники и схемы преобразования полного сопротивления 12.1. ИСТОЧНИКИ НАПРЯЖЕНИЯ, УПРАВЛЯЕМЫЕ НАПРЯЖЕНИЕМ 12.2. ИСТОЧНИКИ НАПРЯЖЕНИЯ, УПРАВЛЯЕМЫЕ ТОКОМ 12.3. ИСТОЧНИКИ ТОКА, УПРАВЛЯЕМЫЕ НАПРЯЖЕНИЕМ 12.  3.2. ИСТОЧНИКИ ТОКА С ЗАЗЕМЛЕННОЙ НАГРУЗКОЙ 3.2. ИСТОЧНИКИ ТОКА С ЗАЗЕМЛЕННОЙ НАГРУЗКОЙ12.3.4. ПЛАВАЮЩИЕ ИСТОЧНИКИ ТОКА 12.4. ИСТОЧНИКИ ТОКА, УПРАВЛЯЕМЫЕ ТОКОМ 12.5. ПРЕОБРАЗОВАТЕЛЬ ОТРИЦАТЕЛЬНОГО СОПРОТИВЛЕНИЯ (NIC) 12.6. ГИРАТОР 12.7. ЦИРКУЛЯТОР 13. Активные фильтры 13.1. ТЕОРЕТИЧЕСКОЕ ОПИСАНИЕ ФИЛЬТРОВ НИЖНИХ ЧАСТОТ 13.1.1. ФИЛЬТР БАТТЕРВОРТА 13.1.2. ФИЛЬТР ЧЕБЫШЕВА 13.1.3. ФИЛЬТРЫ БЕССЕЛЯ 13.1.4. ОБОБЩЕННОЕ ОПИСАНИЕ ФИЛЬТРОВ 13.2. ПРЕОБРАЗОВАНИЕ НИЖНИХ ЧАСТОТ В ВЕРХНИЕ 13.3. РЕАЛИЗАЦИЯ ФИЛЬТРОВ НИЖНИХ И ВЕРХНИХ ЧАСТОТ ПЕРВОГО ПОРЯДКА 13.4. РЕАЛИЗАЦИЯ ФИЛЬТРОВ НИЖНИХ И ВЕРХНИХ ЧАСТОТ ВТОРОГО ПОРЯДКА 13.4.2. ФИЛЬТР СО СЛОЖНОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.4.3. ФИЛЬТР С ПОЛОЖИТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.5. РЕАЛИЗАЦИЯ ФИЛЬТРОВ ВЕРХНИХ И НИЖНИХ ЧАСТОТ БОЛЕЕ ВЫСОКОГО ПОРЯДКА 13.6. ПРЕОБРАЗОВАНИЕ ФИЛЬТРА НИЖНИХ ЧАСТОТ В ПОЛОСОВОЙ ФИЛЬТР 13.  6.1. ПОЛОСОВОЙ ФИЛЬТР ВТОРОГО ПОРЯДКА 6.1. ПОЛОСОВОЙ ФИЛЬТР ВТОРОГО ПОРЯДКА13.6.2. ПОЛОСОВОЙ ФИЛЬТР ЧЕТВЕРТОГО ПОРЯДКА 13.7. РЕАЛИЗАЦИЯ ПОЛОСОВЫХ ФИЛЬТРОВ ВТОРОГО ПОРЯДКА 13.7.2. ПОЛОСОВОЙ ФИЛЬТР СО СЛОЖНОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.7.3. ПОЛОСОВОЙ ФИЛЬТР С ПОЛОЖИТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.7.4. ПОЛОСОВОЙ ФИЛЬТР С ОМИЧЕСКОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.9. РЕАЛИЗАЦИЯ ЗАГРАЖДАЮЩИХ ФИЛЬТРОВ ВТОРОГО ПОРЯДКА 13.9.1. ЗАГРАЖДАЮЩИЙ LRC-ФИЛЬТР 13.9.2. АКТИВНЫЙ ЗАГРАЖДАЮЩИЙ ФИЛЬТР С ДВОЙНЫМ Т-ОБРАЗНЫМ МОСТОМ 13.9.3. АКТИВНЫЙ ЗАГРАЖДАЮЩИЙ ФИЛЬТР С МОСТОМ ВИНА-РОБИНСОНА 13.10. ФАЗОВЫЙ ФИЛЬТР 13.10.2. РЕАЛИЗАЦИЯ ФАЗОВОГО ФИЛЬТРА ПЕРВОГО ПОРЯДКА 13.10.3. РЕАЛИЗАЦИЯ ФАЗОВОГО ФИЛЬТРА ВТОРОГО ПОРЯДКА 13.11. ПЕРЕСТРАИВАЕМЫЙ УНИВЕРСАЛЬНЫЙ ФИЛЬТР 14. Широкополосные усилители 14.1. ЗАВИСИМОСТЬ КОЭФФИЦИЕНТА УСИЛЕНИЯ ПО ТОКУ ОТ ЧАСТОТЫ 14.2. ВЛИЯНИЕ ВНУТРЕННИХ ЕМКОСТЕЙ ТРАНЗИСТОРА И ЕМКОСТЕЙ МОНТАЖА 14.  14.4. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ КАК ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ 14.5. СИММЕТРИЧНЫЙ ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ 14.5.2. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ИНВЕРТОРОМ 14.5.3. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С КОМПЛЕМЕНТАРНОЙ КАСКОДНОЙ СХЕМОЙ 14.5.4. ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ 14.6. ШИРОКОПОЛОСНЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ 14.6.2. ДВУХТАКТНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ 14.7. ШИРОКОПОЛОСНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ 15. Усилители мощности 15.1. ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ КАК УСИЛИТЕЛЬ МОЩНОСТИ 15.2. КОМПЛЕМЕНТАРНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ 15.2.2. КОМПЛЕМЕНТАРНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ В РЕЖИМЕ AB 15.2.3. СПОСОБЫ ЗАДАНИЯ НАПРЯЖЕНИЯ СМЕЩЕНИЯ 15.4. КОМПЛЕМЕНТАРНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ ПО СХЕМЕ ДАРЛИНГТОНА 15.5. РАСЧЕТ МОЩНОГО ОКОНЕЧНОГО КАСКАДА 15.6. СХЕМЫ ПРЕДВАРИТЕЛЬНЫХ УСИЛИТЕЛЕЙ НАПРЯЖЕНИЯ 15.7. ПОВЫШЕНИЕ НАГРУЗОЧНОЙ СПОСОБНОСТИ ИНТЕГРАЛЬНЫХ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 16. Источники питания 16.  1. СВОЙСТВА СЕТЕВЫХ ТРАНСФОРМАТОРОВ 1. СВОЙСТВА СЕТЕВЫХ ТРАНСФОРМАТОРОВ16.2. ВЫПРЯМИТЕЛИ 16.2.1. ОДНОПОЛУПЕРИОДНЫЙ ВЫПРЯМИТЕЛЬ 16.2.2. МОСТОВОЙ ВЫПРЯМИТЕЛЬ 16.2.3. МОСТОВОЙ ВЫПРЯМИТЕЛЬ ДЛЯ ДВУХ СИММЕТРИЧНЫХ ОТНОСИТЕЛЬНО ЗЕМЛИ ВЫХОДНЫХ НАПРЯЖЕНИЙ 16.3. ПОСЛЕДОВАТЕЛЬНАЯ СТАБИЛИЗАЦИЯ НАПРЯЖЕНИЯ 16.3.2. СХЕМА С РЕГУЛИРУЮЩИМ УСИЛИТЕЛЕМ 16.3.3. ИНТЕГРАЛЬНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ 16.3.4. СТАБИЛИЗАТОР С МАЛЫМ НАПРЯЖЕНИЕМ ПОТЕРЬ 16.3.5. СТАБИЛИЗАЦИЯ НАПРЯЖЕНИЙ, СИММЕТРИЧНЫХ ОТНОСИТЕЛЬНО ЗЕМЛИ 16.3.6. СТАБИЛИЗАТОР НАПРЯЖЕНИЯ С ИЗМЕРИТЕЛЬНЫМИ ВЫВОДАМИ 16.3.7. ЛАБОРАТОРНЫЕ ИСТОЧНИКИ ПИТАНИЯ 16.3.8. ОКОНЕЧНЫЙ КАСКАД ЛАБОРАТОРНОГО ИСТОЧНИКА ПИТАНИЯ С БОЛЬШОЙ ВЫХОДНОЙ МОЩНОСТЬЮ 16.4. ПОЛУЧЕНИЕ ОПОРНОГО НАПРЯЖЕНИЯ 16.4.2. ПОЛУЧЕНИЕ МАЛЫХ ОПОРНЫХ НАПРЯЖЕНИЙ 16.5. ИМПУЛЬСНЫЕ РЕГУЛЯТОРЫ НАПРЯЖЕНИЯ 16.5.2. ПЕРВИЧНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ 17. Аналоговые коммутаторы и компараторы 17.2. ЭЛЕКТРОННЫЕ КОММУТАТОРЫ 17.2.2. ДИОДНЫЙ КОММУТАТОР 17.2.3. КОММУТАТОР НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ 17.  3. АНАЛОГОВЫЕ КОММУТАТОРЫ НА БАЗЕ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 3. АНАЛОГОВЫЕ КОММУТАТОРЫ НА БАЗЕ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ17.3.2. КОММУТАТОР НА ПОЛЕВОМ ТРАНЗИСТОРЕ С ПЕРЕМЕНОЙ ЗНАКА ВЫХОДНОГО НАПРЯЖЕНИЯ 17.3.3. КОММУТАТОР НА БАЗЕ ДИФФЕРЕНЦИАЛЬНОГО УСИЛИТЕЛЯ 17.4. АНАЛОГОВЫЕ КОММУТАТОРЫ С ПАМЯТЬЮ 17.5. КОМПАРАТОРЫ 17.5.2. КОМПАРАТОР С ПРЕЦИЗИОННЫМ ВЫХОДНЫМ НАПРЯЖЕНИЕМ 17.5.3. ДВУХПОРОГОВЫЙ КОМПАРАТОР 17.6. ТРИГГЕР ШМИТТА 17.6.1. ИНВЕРТИРУЮЩИЙ ТРИГГЕР ШМИТТА 17.6.2. НЕИНВЕРТИРУЮЩИЙ ТРИГГЕР ШМИТТА 17.6.3. ПРЕЦИЗИОННЫЙ ТРИГГЕР ШМИТТА 18. Генераторы сигналов 18.1. LC-ГЕНЕРАТОРЫ 18.1.2. ГЕНЕРАТОР С ТРАНСФОРМАТОРНОЙ СВЯЗЬЮ (СХЕМА МАЙССНЕРА) 18.1.3. ТРЕХТОЧЕЧНАЯ СХЕМА С ИНДУKТИВНОЙ ОБРАТНОЙ СВЯЗЬЮ (СХЕМА ХАРТЛИ) 18.1.4. ТРЕХТОЧЕЧНАЯ СХЕМА С ЕМКОСТНОЙ ОБРАТНОЙ СВЯЗЬЮ (СХЕМА КОЛПИТЦА) 18.1.5. LC-ГЕНЕРАТОР С ЭМИТТЕРНОЙ СВЯЗЬЮ 18.1.6. ДВУХТАКТНЫЕ ГЕНЕРАТОРЫ 18.2. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ 18.2.1. ЭЛЕКТРИЧЕСКИЕ СВОЙСТВА КВАРЦЕВОГО РЕЗОНАТОРА 18.2.2. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ С LC-КОЛЕБАТЕЛЬНЫМ КОНТУРОМ 18.  2.3. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ БЕЗ LC-КОНТУРА 2.3. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ БЕЗ LC-КОНТУРА18.3. СИНУСОИДАЛЬНЫЕ RC-ГЕНЕРАТОРЫ 18.3.2. МОДЕЛИРОВАНИЕ ДИФФЕРЕНЦИАЛЬНОГО УРАВНЕНИЯ СИНУСОИДАЛЬНЫХ КОЛЕБАНИЙ 18.4. ГЕНЕРАТОРЫ СИГНАЛОВ СПЕЦИАЛЬНОЙ ФОРМЫ (ФУНКЦИОНАЛЬНЫЕ ГЕНЕРАТОРЫ) 18.4.2. ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР С УПРАВЛЯЕМОЙ ЧАСТОТОЙ ВЫХОДНОГО СИГНАЛА 18.4.3. ВЫСОКОЧАСТОТНЫЙ ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР 18.5. МУЛЬТИВИБРАТОРЫ 18.5.1. НИЗКОЧАСТОТНЫЕ МУЛЬТИВИБРАТОРЫ 18.5.2. ВЫСОКОЧАСТОТНЫЕ МУЛЬТИВИБРАТОРЫ 19. Комбинационные логические схемы 19.1. ПРЕОБРАЗОВАТЕЛИ КОДОВ 19.1.2. ДВОИЧНО-ДЕСЯТИЧНЫЕ КОДЫ 19.1.3. КОД ГРЕЯ 19.2. МУЛЬТИПЛЕКСОР И ДЕМУЛЬТИПЛЕКСОР 19.3. КОМБИНАЦИОННОЕ УСТРОЙСТВО СДВИГА 19.4. КОМПАРАТОРЫ 19.5. СУММАТОРЫ 19.5.1. ПОЛУСУММАТОР 19.5.2. ПОЛНЫЙ СУММАТОР 19.5.3. СУММАТОРЫ С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ 19.5.4. СЛОЖЕНИЕ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ 19.5.5. ВЫЧИТАНИЕ 19.5.6. СЛОЖЕНИЕ ЧИСЕЛ С ЛЮБЫМИ ЗНАКАМИ 19.6. УМНОЖИТЕЛИ 19.7. ЦИФРОВЫЕ ФУНКЦИОНАЛЬНЫЕ ПРЕОБРАЗОВАТЕЛИ 20.  Интегральные схемы со структурами последовательностного типа Интегральные схемы со структурами последовательностного типа20.1. ДВОИЧНЫЕ СЧЕТЧИКИ 20.1.1. АСИНХРОННЫЙ (ПОСЛЕДОВАТЕЛЬНЫЙ) СЧЕТЧИК 20.1.2. СИНХРОННЫЙ (ПАРАЛЛЕЛЬНЫЙ) СЧЕТЧИК 20.2. ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК В КОДЕ 8421 20.2.1. АСИНХРОННЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК 20.2.2. СИНХРОННЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК 20.3. СЧЕТЧИК С ПРЕДВАРИТЕЛЬНОЙ УСТАНОВКОЙ 20.4. РЕГИСТРЫ СДВИГА 20.4.2. КОЛЬЦЕВОЙ РЕГИСТР 20.4.3. РЕГИСТР СДВИГА С ПАРАЛЛЕЛЬНЫМ ВВОДОМ 20.4.4. РЕГИСТР СДВИГА С ПЕРЕКЛЮЧАЕМЫМ НАПРАВЛЕНИЕМ СДВИГА 20.5. ПОЛУЧЕНИЕ ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ 20.6. ПЕРВОНАЧАЛЬНАЯ ОБРАБОТКА АСИНХРОННОГО СИГНАЛА 20.6.2. СИНХРОНИЗАЦИЯ ИМПУЛЬСОВ 20.6.3. СИНХРОННЫЙ ОДНОВИБРАТОР 20.6.4. СИНХРОННЫЙ ДЕТЕКТОР ИЗМЕНЕНИЙ 20.6.5. СИНХРОННЫЙ ТАКТОВЫЙ ПЕРЕКЛЮЧАТЕЛЬ 20.7. СИСТЕМАТИЧЕСКИЙ СИНТЕЗ ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМ 20.7.2. ПРИМЕР СИНТЕЗА ПЕРЕКЛЮЧАЕМОГО СЧЕТЧИКА 20.7.3. СОКРАЩЕНИЕ ЕМКОСТИ ПАМЯТИ 21. Микро-ЭВМ 21.1. ОСНОВНАЯ СТРУКТУРА МИКРО-ЭВМ 21.  2. ПРИНЦИП ДЕЙСТВИЯ МИКРОПРОЦЕССОРА 2. ПРИНЦИП ДЕЙСТВИЯ МИКРОПРОЦЕССОРА21.3. НАБОР КОМАНД 21.4. ОТЛАДОЧНЫЕ СРЕДСТВА 21.5. ОБЗОР МИКРОПРОЦЕССОРОВ РАЗЛИЧНОГО ТИПА 21.6. МОДУЛЬНОЕ ПОСТРОЕНИЕ МИКРО-ЭВМ 21.7. ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА 21.7.1. ПАРАЛЛЕЛЬНЫЙ ИНТЕРФЕЙС 21.7.2. ПОСЛЕДОВАТЕЛЬНЫЙ ИНТЕРФЕЙС 21.7.3. ИНТЕРФЕЙС МАГИСТРАЛИ «ОБЩАЯ ШИНА» 21.7.4. ПРОГРАММИРУЕМЫЙ СЧЕТЧИК 21.7.5. ПОДКЛЮЧЕНИЕ ПЕРИФЕРИЙНЫХ МОДУЛЕЙ СЕМЕЙСТВА 8080 К МАГИСТРАЛЯМ СЕМЕЙСТВА 6800 21.7.6. ОБЗОР ПЕРИФЕРИЙНЫХ УСТРОЙСТВ 21.8. МИНИМАЛЬНЫЕ СИСТЕМЫ 21.8.2. ОДНОКРИСТАЛЬНАЯ МИКРО-ЭВМ 22. Цифровые фильтры 22.1. ТЕОРЕМА О ДИСКРЕТИЗАЦИИ (ТЕОРЕМА О ВЫБОРКАХ) 22.1.2. ПРАКТИЧЕСКИЕ СООБРАЖЕНИЯ 22.2. ЦИФРОВАЯ ФУНКЦИЯ ПЕРЕДАЧИ ФИЛЬТРА 22.3. БИЛИНЕЙНОЕ ПРЕОБРАЗОВАНИЕ 22.4. РЕАЛИЗАЦИЯ ЦИФРОВЫХ ФИЛЬТРОВ 22.4.2. СТРУКТУРА ЦИФРОВЫХ ФИЛЬТРОВ ВТОРОГО ПОРЯДКА 22.4.3. ПРАКТИЧЕСКИЕ СООБРАЖЕНИЯ 23. Передача данных и индикация 23.1. СОЕДИНИТЕЛЬНЫЕ ЛИНИИ 23.2. ЗАЩИТА ДАННЫХ 23.2.2. КОД ХЕММИНГА 23.  3. СТАТИЧЕСКИЕ ЦИФРОВЫЕ ИНДИКАТОРЫ 3. СТАТИЧЕСКИЕ ЦИФРОВЫЕ ИНДИКАТОРЫ23.3.1. ДВОИЧНЫЕ ИНДИКАТОРЫ НА СВЕТОДИОДАХ 23.3.2. ДЕКАДНЫЕ ИНДИКАТОРЫ 23.3.3. ИНДИКАЦИЯ В ШЕСТНАДЦАТЕРИЧНОМ КОДЕ 23.4. МУЛЬТИПЛЕКСНЫЕ ИНДИКАТОРЫ 23.4.1. МНОГОРАЗРЯДНЫЕ 7-СЕГМЕНТНЫЕ ИНДИКАТОРЫ 23.4.2. МАТРИЦА ТОЧЕК 24. Цифро-аналоговые и аналого-цифровые преобразователи 24.1. СХЕМОТЕХНИЧЕСКИЕ ПРИНЦИПЫ ЦА-ПРЕОБРАЗОВАТЕЛЕЙ 24.1.2. ЦА-ПРЕОБРАЗОВАТЕЛЬ С ПЕРЕКИДНЫМИ КЛЮЧАМИ 24.1.3. РЕЗИСТИВНАЯ МАТРИЦА ПОСТОЯННОГО ИМПЕДАНСА (МАТРИЦА ТИПА R-2R) 24.1.4. РЕЗИСТИВНАЯ МАТРИЦА ДЛЯ ДЕКАДНЫХ ПРЕОБРАЗОВАТЕЛЕЙ 24.2. ПОСТРОЕНИЕ ЦА-ПРЕОБРАЗОВАТЕЛЕЙ С ЭЛЕКТРОННЫМИ КЛЮЧАМИ 24.2.2. ЦА-ПРЕОБРАЗОВАТЕЛЬ С ТОКОВЫМИ КЛЮЧАМИ 24.3. ЦА-ПРЕОБРАЮВАТЕЛИ ДЛЯ СПЕЦИАЛЬНЫХ ПРИМЕНЕНИЙ 24.3.2. ЦА-ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ДЕЛЕНИЯ 24.3.3. ЦА-ПРЕОБРАЗОВАТЕЛЬ КАК ГЕНЕРАТОР ФУНКЦИЙ 24.4. ОСНОВНЫЕ ПРИНЦИПЫ АЦ-ПРЕОБРАЗОВАНИЯ 24.5. ТОЧНОСТЬ АЦ-ПРЕОБРАЗОВАТЕЛЕЙ 24.6. ПОСТРОЕНИЕ АЦ-ПРЕОБРАЗОВАТЕЛЕЙ 25. Измерительные схемы 25.  1. ИЗМЕРЕНИЕ НАПРЯЖЕНИЙ 1. ИЗМЕРЕНИЕ НАПРЯЖЕНИЙ25.1.2. ИЗМЕРЕНИЕ РАЗНОСТИ ПОТЕНЦИАЛОВ 25.1.3. ИЗОЛИРОВАННЫЙ УСИЛИТЕЛЬ 25.2. ИЗМЕРЕНИЕ ТОКА 25.2.1. ИЗОЛИРОВАННЫЕ ОТ ЗЕМЛИ АМПЕРМЕТРЫ С МАЛЫМ ПАДЕНИЕМ НАПРЯЖЕНИЯ 25.2.2. ИЗМЕРЕНИЕ ТОКА ПРИ ВЫСОКОМ ПОТЕНЦИАЛЕ 25.3. ИЗМЕРИТЕЛЬНЫЙ ВЫПРЯМИТЕЛЬ 25.3.2. ИЗМЕРЕНИЕ ЭФФЕКТИВНОГО ЗНАЧЕНИЯ 25.3.3. ИЗМЕРЕНИЕ АМПЛИТУДНЫХ ЗНАЧЕНИЙ 25.3.4. СИНХРОННЫЙ ДЕТЕКТОР 26. Электронные регуляторы 26.2. ТИПЫ РЕГУЛЯТОРОВ 26.2.1. П-РЕГУЛЯТОР 26.2.2. ПИ-РЕГУЛЯТОР 26.2.3. ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР 26.2.4. НАСТРАИВАЕМЫЕ ПИД-РЕГУЛЯТОРЫ 26.3. УПРАВЛЕНИЕ НЕЛИНЕЙНЫМИ ОБЪЕКТАМИ 26.4. ОТСЛЕЖИВАЮЩАЯ СИНХРОНИЗАЦИЯ (АВТОПОДСТРОЙКА) 26.4.1. ЭЛЕМЕНТЫ ВЫБОРКИ-ХРАНЕНИЯ В КАЧЕСТВЕ ФАЗОВОГО ДЕТЕКТОРА 26.4.2. СИНХРОННЫЙ ВЫПРЯМИТЕЛЬ В КАЧЕСТВЕ ФАЗОВОГО ДЕТЕКТОРА 26.4.3. ЧАСТОТНО-ЧУВСТВИТЕЛЬНЫЙ ФАЗОВЫЙ ДЕТЕКТОР 26.4.4. ФАЗОВЫЙ ДЕТЕКТОР С ПРОИЗВОЛЬНО УВЕЛИЧИВАЕМЫМ ДИАПАЗОНОМ ИЗМЕРЕНИЙ 26.4.5. ФАЗОРЕГУЛЯТОР В КАЧЕСТВЕ ПЕРЕМНОЖИТЕЛЯ ЧАСТОТ |

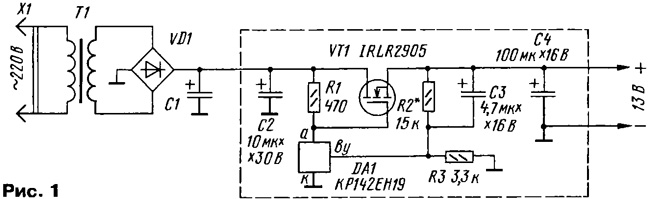

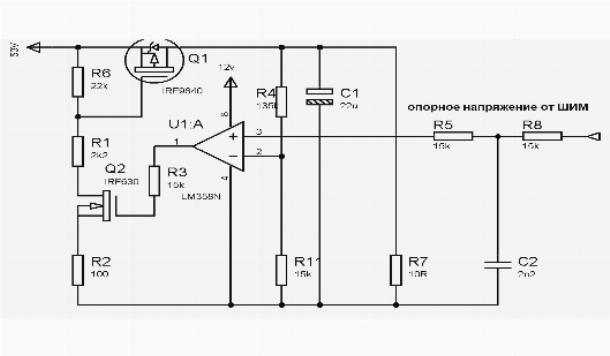

Стабилизатор напряжения на ОУ и полевом транзисторе

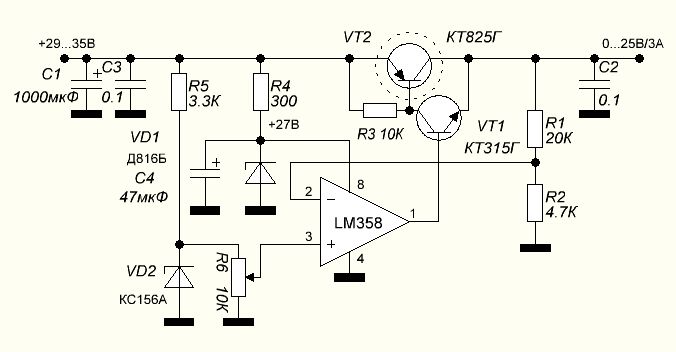

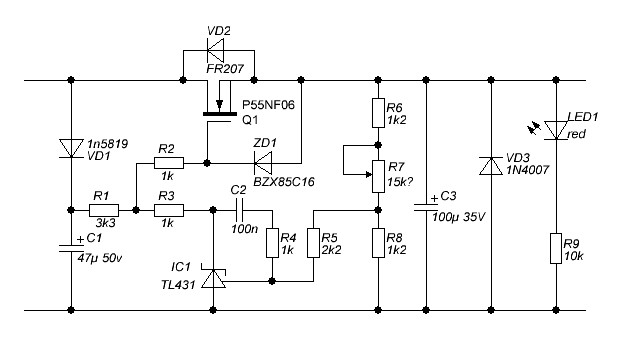

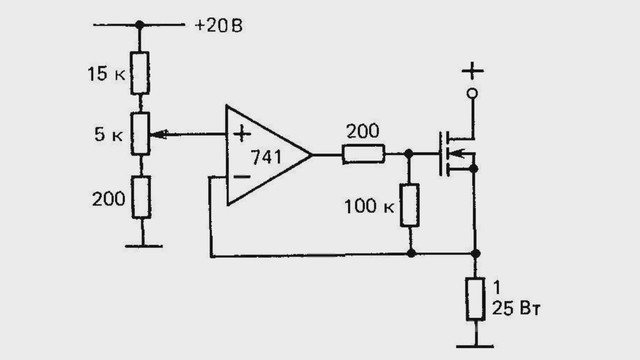

Всем доброго времени суток! В прошлой статье я рассматривал RC генераторы синусоидальных (гармонических) колебаний на ОУ. В данной статье я рассмотрю стабилизаторы напряжения, в основе которых лежат операционные усилители. Основное преимущество ОУ при использовании их в стабилизаторах напряжения является то, что ОУ обладает большим коэффициентом усиления (несколько десятков тысяч). Поэтому они позволяют получить нестабильность выходного напряжения порядка 0,001 %.

В данной статье я рассмотрю стабилизаторы напряжения, в основе которых лежат операционные усилители. Основное преимущество ОУ при использовании их в стабилизаторах напряжения является то, что ОУ обладает большим коэффициентом усиления (несколько десятков тысяч). Поэтому они позволяют получить нестабильность выходного напряжения порядка 0,001 %.

Для сборки радиоэлектронного устройства можно преобрески DIY KIT набор по ссылке.

Основная схема компенсационного стабилизатора напряжения

Большинство современной силовой электроники представлено импульсными источниками питания, которые обладают высоким КПД и небольшими габаритными размерами. Однако линейные стабилизаторы напряжения также находят своё применение, прежде всего в устройствах небольшой мощности, а также в схемах, где не желательны импульсные помехи.

Как известно линейные источники питания разделяются на последовательные и параллельные в зависимости от схемы подсоединения регулирующего элемента относительно выхода. Наибольшее распространение получили последовательные стабилизаторы, так как могут обеспечить КПД и стабилизацию больше чем параллельные, из основных достоинств которых является возможность перегрузки по току и способность выдерживать короткое замыкание.

Наибольшее распространение получили последовательные стабилизаторы, так как могут обеспечить КПД и стабилизацию больше чем параллельные, из основных достоинств которых является возможность перегрузки по току и способность выдерживать короткое замыкание.

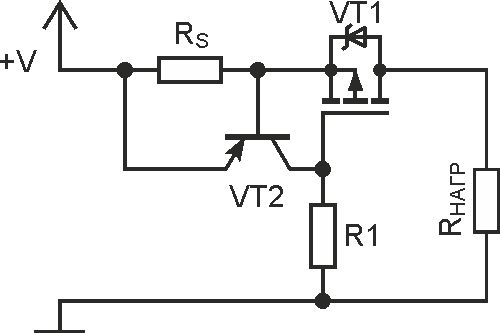

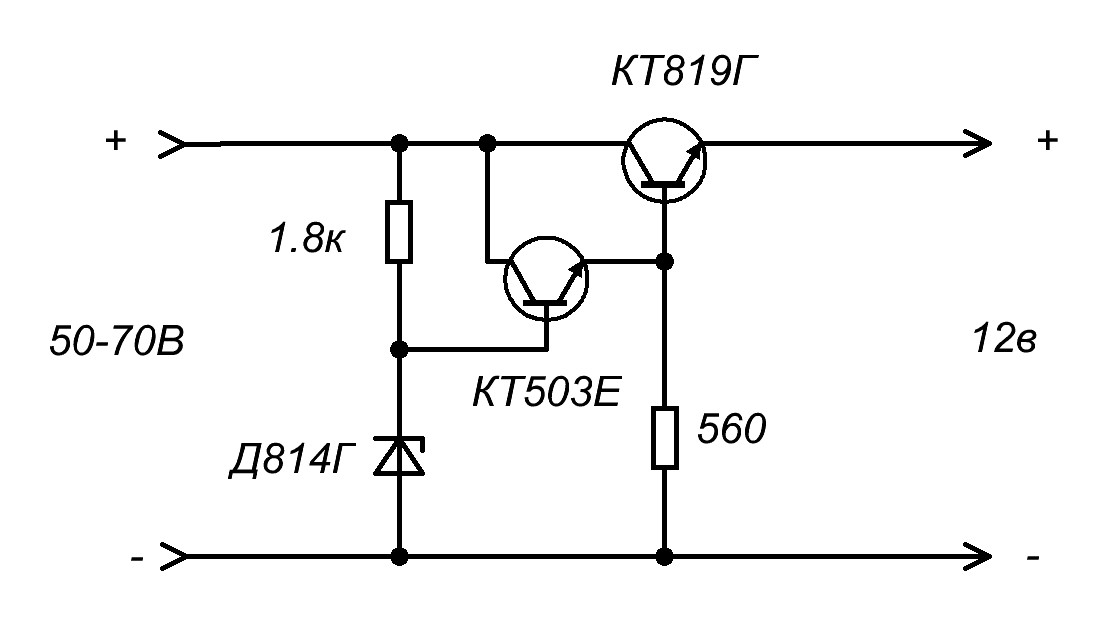

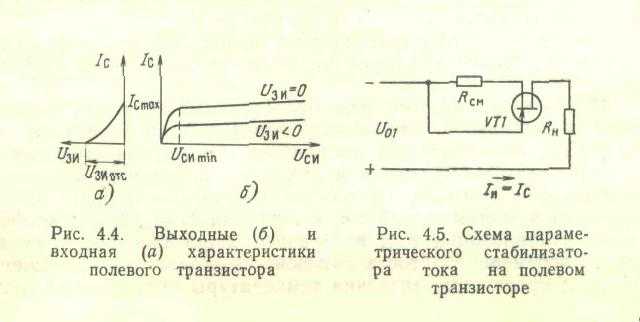

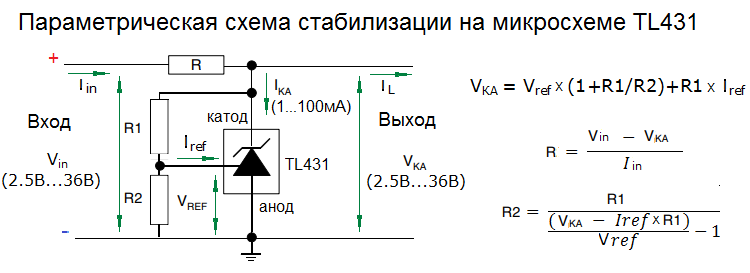

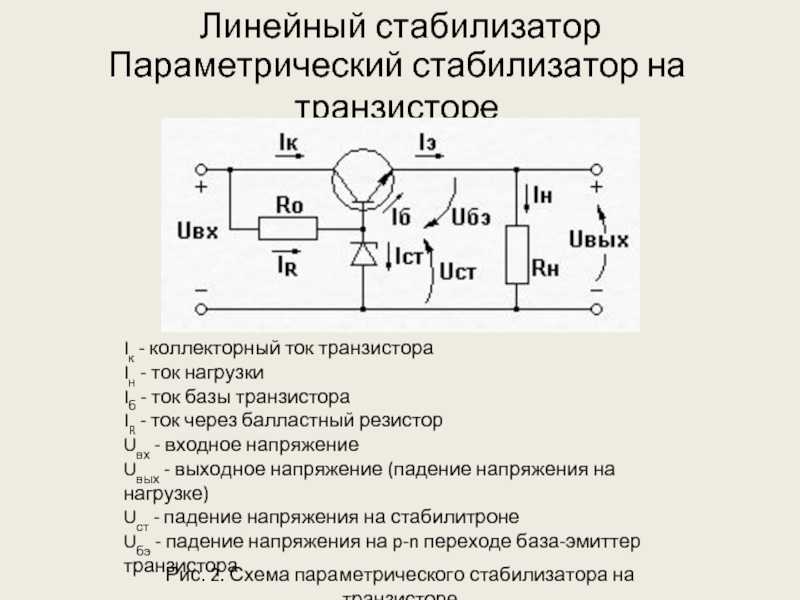

Кроме схемы подключения регулирующего элемента, стабилизаторы напряжения классифицируются по способу регулирования выходного напряжения: параметрические и компенсационные. Работа параметрических стабилизаторов основана на нелинейных свойствах регулирующих элементах, то есть при значительном изменении тока протекающего через него падение напряжения на регулирующем элементе мало изменяется. Такие стабилизаторы применяются в схемах небольшой мощности до нескольких ватт. Наибольшее распространение получили схемы последовательных стабилизаторов компенсационного типа, структурная схема, которого представлена ниже

Структурная схема компенсационного стабилизатора последовательного типа.

В одной из статей я рассказывал о компенсационных стабилизаторах напряжения, выполненных на транзисторах, поэтому напомню принцип его работы. Схема состоит из чётырёх основных частей: источник образцового напряжения И, элемента сравнения ЭС, усилительного элемента У и регулирующего элемента Р. Элемент сравнения сравнивает выходное напряжение U1 с напряжение вырабатываемым источником образцового напряжения и выдаёт ошибку сравнения на усилительный элемент, где происходит усиление ошибки сравнения и вырабатывается управляющий сигнал для регулирующего элемента.

Схема состоит из чётырёх основных частей: источник образцового напряжения И, элемента сравнения ЭС, усилительного элемента У и регулирующего элемента Р. Элемент сравнения сравнивает выходное напряжение U1 с напряжение вырабатываемым источником образцового напряжения и выдаёт ошибку сравнения на усилительный элемент, где происходит усиление ошибки сравнения и вырабатывается управляющий сигнал для регулирующего элемента.

Довольно часто в простых схемах происходит объединение элемента сравнения и усилителя (а иногда и регулирующего элемента в слаботочных схемах) в одно устройство. В современных схемах функции элемента сравнения и усилителя выполняют на ОУ.

Основы работы источника тока с двумя операционными усилителями

Чтобы проанализировать источник тока на двух операционных усилителях, мы будем использовать его реализацию в LTspice.

youtube.com/embed/Rs1R7lnpW3E?feature=oembed» frameborder=»0″ allow=»accelerometer; autoplay; clipboard-write; encrypted-media; gyroscope; picture-in-picture» allowfullscreen=»»>Удвойте выходной ток с помощью параллельных регуляторов напряжения

Для повышения эффективности в приложениях большой мощности регуляторы напряжения можно использовать параллельно для удвоения выходного тока, если предусмотрены средства принудительного распределения тока.

В одном схемном подходе используются чувствительные резисторы, включенные последовательно с нагрузкой, и он применим к регуляторам любого типа. С небольшой модификацией его можно разместить перед регуляторами, измеряющими входной ток. Другой метод наиболее применим к синхронным переключателям, поскольку он требует наличия чувствительных элементов нижнего плеча, которые могут быть резисторами или полевыми транзисторами.

Иногда разработчики могут захотеть соединить регуляторы параллельно, чтобы удвоить ток или повысить эффективность. К ним относятся случаи, когда:

К ним относятся случаи, когда:

1. Требуется использовать линейный стабилизатор или ИС-переключатель со встроенными силовыми полевыми транзисторами, но превышен максимальный номинальный ток.

2. Повышение температуры отдельной ИС больше допустимого для поверхностного монтажа.

3. Повышение эффективности оправдано снижением общей стоимости или увеличением срока службы батареи.

4. Требование к высокому выходному току диктует двухфазную конструкцию. Преимущества двухфазных переключателей для сильноточных приложений широко известны. Но многие двухфазные IC-контроллеры не позволяют легко запараллелить выходы. Это особенно верно для контроллеров режима напряжения.

На рисунках 1а и 1б показаны блоки регулируемых регуляторов, соединенные параллельно. Напряжения обратной связи (FB) для рис. 1a относятся к Gnd, а на рис. 1b показаны устройства с тремя клеммами, в которых FB привязан к V OUT . На данном этапе обсуждения блоки регуляторов могут быть как линейными, так и переключателями.

В большинстве регуляторов напряжения используется контур обратной связи с высоким коэффициентом усиления для подчинения V OUT внутреннему опорному напряжению, так что сигнал ошибки на выводе обратной связи всего в несколько милливольт вызовет полномасштабное изменение на V ВЫХОД . Отрицательная обратная связь с высоким коэффициентом усиления V OUT должна быть линейной функцией V REF и отношением резисторов обратной связи, как определено: (R F2 /R F1 + 1), где v Ref Equals V FB (напряжение при FB) (1)

(для рис. 1B)

V OUT (для рис. = V REF (R F1 /R F2 + 1) где V REF равно V OUT V FB (2)

Ошибки постоянного тока в основном определяются точностью и допуском резисторов обратной связи V REF . Когда два одинаковых регулятора соединены параллельно, небольшая разница в V REF приведет к тому, что один регулятор будет подавать почти весь ток нагрузки, пока не будет достигнуто предельное значение тока. Тогда его V OUT будет падать до второго регулятора, с чуть более низким V REF , начинает подавать остаточный ток нагрузки. Работа таким образом может быть приемлемой, если тепловыделение и температура устройства остаются достаточно низкими, чтобы избежать термоциклирования.

Тогда его V OUT будет падать до второго регулятора, с чуть более низким V REF , начинает подавать остаточный ток нагрузки. Работа таким образом может быть приемлемой, если тепловыделение и температура устройства остаются достаточно низкими, чтобы избежать термоциклирования.

По мере увеличения тока нагрузки и рассеяния регулятора регуляторы должны разделять ток, поэтому для этого необходимо добавить некоторые схемы. На рисунках 2a и 2b показаны резисторы R SHARE , включенные последовательно с каждым выходом для обеспечения предсказуемого разделения при максимальном токе нагрузки. R SHARE выбран так, чтобы падение напряжения на нем при полной нагрузке в несколько раз превышало максимальную разность напряжений между стабилизаторами. Тогда:

V OUT = V REG1 (I REG1 × R Share ) = V REG2 (I REG2 × R Акция ) (3)

Полнолетная разница. V REG1 V REG2 )/R SHARE (4)

V REG1 V REG2 )/R SHARE (4)

Путем выбора дифференциального тока при полной нагрузке I OUT × 10%, определения допуска = T и установки максимума (V REG18 V REG2 ) значение 2×T×V REG , получаем: R Share = (V REG1 V REG2 ) /(I OUT × 10%) = 20 × T × V REG /I OUT (5) Пример 1: Пример 1: Пример 1:. Для I OUT = 2 A с использованием двух регуляторов 1-A с допуском ±3% и V REG = 5 В, R SHARE = 10 × 0,3 В/2 A = 1,5O. Совместное использование — это хорошо, но падение напряжения при полной нагрузке составляет 1,5 В или 30%, что слишком много для большинства нагрузок. При параллельном подключении стабилизаторов напряжения главные цели хорошего регулирования и предсказуемого разделения тока могут быть достигнуты путем добавления последовательного резистора для измерения тока в каждом канале, а также операционного усилителя для усиления и интегрирования сигнала ошибки. Цепь, выделенная серым цветом на обоих рисунках, состоит из чувствительных резисторов R S1 , R S2 и дифференциального интегратора. Для регуляторов без функции стока тока, которые должны работать при небольшой нагрузке, добавлен R OS , чтобы обеспечить небольшое смещение холостого хода для интегратора. Без R OS , когда ток нагрузки падает настолько, что напряжение на R S1 или R S2 становится меньше напряжения смещения операционного усилителя, ведомое устройство V REG2 Напряжение может повышаться. Выбор номинала чувствительного резистора является компромиссом между эффективностью и увеличением стоимости операционного усилителя с малым смещением. Выберите U1, чтобы получить низкое напряжение смещения и возможность работы от сети к сети. На рисунке 3а операционный усилитель может быть LMV931M5 и питаться от V OUT в диапазоне от 1,5 до 5,5 В. Или это может быть деталь, как LM7301M5 в V OUT диапазон от 2,2 до 30 В. Оба доступны в корпусах SOT23-5 с V OS IN, при условии, что V IN V OUT больше 1,5 В. На рис. от V IN и должен иметь входной синфазный диапазон, активный на положительной шине, как и LMV931M5, LM7301M5, LMC7101M5 и LMC8101M5. Выберите R OS , чтобы обеспечить небольшое падение напряжения на входном резисторе интегратора, равное напряжению смещения операционного усилителя. R S = 4 × (Мощность, рассеиваемая в каждом R S ) / I OUT2 (6) R S = 2 × V RS / I OUT , где V RS — падение напряжения на каждом R S (7) V OSmax = I D / × R (8) Минимальное значение для каждого R S основано на точности, необходимой для текущего совпадения. Максимальное значение для R S определяется либо доступным падением напряжения, либо рассеиваемой мощностью. Пример 2: Для I OUT = 2 A с использованием двух регуляторов 1-A с допуском ±3% и V REG = 5 В, выберем R S с рассеиваемой мощностью 100 мВт. Тогда R S = 4 × 0,1 Вт/4 = 0,1 (омега). А, V OSmax = 2/10 × 0,1/2 = 10 мВ. Для схемы на рис. 1а выбран R OS , обеспечивающий ток, достаточный для падения 10 мВ на резисторе 1 кОм или 10 мкА. Таким образом, его значение равно 5 В/10 мкА = 500 кОм. р F3 должен обеспечить достаточно большой диапазон управления, чтобы заставить V REG2 работать в полном диапазоне выходного тока. Выберите его значение с нулевым выходом U1 и его током больше, чем (V OUT × 2 × допуск %)/(R F1 + R F2 ), в результате чего: R F3 >= V FB (R F1 + R F2 )/(2 × V OUT × допуск %), где V FB — напряжение на FB (9) На рис. Пример 3: Для I OUT = 10 A с использованием двух регуляторов на 5 A с допуском ± 3% и V REG = 5 В выберем R S диссипация при 250 мОм. Тогда R S = 4 × 0,25 Вт/100 = 10 мОм и V OS max = 10/10 × 0,01 = 10 мВ. Потери можно дополнительно уменьшить в три раза, выбрав лучший операционный усилитель, такой как LMV711M5, который имеет максимальное напряжение 3 мВ V OS , уменьшая минимальные значения R S до 3 мОм. Например, при более высоком токе 33 А даже 1 мВт последовательного сопротивления добавляет 1 Вт рассеяния. Измерение небольших падений напряжения на R DS(ON) нижних полевых транзисторов при наличии амплитуды импульса переключения, которая в 100–1000 раз больше, на первый взгляд кажется сложной задачей. Схема на Рисунке 5 показывает один из способов сделать это относительно точно с недорогими деталями. Измерения не требуют абсолютной точности, так как в качестве сигнала ошибки используется интегральная разность напряжений. Серая схема измерения тока на рис. Диоды D1 и D2 на Рисунке 5 предотвращают перегрузку входов операционного усилителя большим размахом сигнала в каждом узле коммутации. Это позволяет использовать U1 в качестве низковольтного двойного усилителя с однополярным питанием. Его наиболее важными характеристиками являются низкое напряжение смещения и широкая полоса пропускания, поскольку он измеряет сигналы Выбранный компонент, LMV722MM, обеспечивает полосу пропускания 10 МГц с максимальным смещением 3 мВ. Он может питаться от самых разных источников, часто включая выход регулятора, если он попадает в необходимый диапазон питания от 2,2 до 5,5 В. В этом примере он легко питается от 5-вольтового источника питания драйвера затвора. U2 используется для интегрирования разностного напряжения с выходов U1 для формирования сигнала ошибки с очень высоким коэффициентом усиления по постоянному току. На рис. 5 показан сигнал ошибки, суммированный в узле обратной связи ведомого канала с помощью резистора R 9 .0017 Ф3  Сигнал ошибки используется для подчинения одного канала другому путем регулировки напряжения обратной связи подчиненного устройства до тех пор, пока напряжения на каждом чувствительном резисторе не сравняются. Этот метод, как показано на рисунках 3а и 3б, прост и относительно эффективен для токов в диапазоне от нуля до нескольких ампер. И он одинаково хорошо работает для синхронных и несинхронных переключателей и линейных регуляторов.

Сигнал ошибки используется для подчинения одного канала другому путем регулировки напряжения обратной связи подчиненного устройства до тех пор, пока напряжения на каждом чувствительном резисторе не сравняются. Этот метод, как показано на рисунках 3а и 3б, прост и относительно эффективен для токов в диапазоне от нуля до нескольких ампер. И он одинаково хорошо работает для синхронных и несинхронных переключателей и линейных регуляторов. R F3 устанавливает диапазон управления V REG2 . Конфигурация совместного использования, показанная на рисунке 3b, работает со всеми типами регуляторов, включая регуляторы с тремя терминалами.

R F3 устанавливает диапазон управления V REG2 . Конфигурация совместного использования, показанная на рисунке 3b, работает со всеми типами регуляторов, включая регуляторы с тремя терминалами. Уравнения 6 и 7 используются для выбора R S для каждого регулятора на основе наименьшей из максимальной мощности, которую он готов рассеивать при полном токе в каждом R S . Или максимально допустимое падение напряжения на каждом R S . Уравнение 8 используется для выбора максимального напряжения смещения, допустимого для операционного усилителя, выбранного для допустимого I OUT дифференциального тока, ID, при полной нагрузке:

Уравнения 6 и 7 используются для выбора R S для каждого регулятора на основе наименьшей из максимальной мощности, которую он готов рассеивать при полном токе в каждом R S . Или максимально допустимое падение напряжения на каждом R S . Уравнение 8 используется для выбора максимального напряжения смещения, допустимого для операционного усилителя, выбранного для допустимого I OUT дифференциального тока, ID, при полной нагрузке: Желаемая разница тока 10 % или менее (I D ¾ I OUTMAX /10) требуется V RS , по крайней мере, в 10 раз превышающее напряжение смещения U1.

Желаемая разница тока 10 % или менее (I D ¾ I OUTMAX /10) требуется V RS , по крайней мере, в 10 раз превышающее напряжение смещения U1. 4 более детально показан рисунок 3a. с В REG1 и V REG2 нарисованы как синхронные переключатели. Поскольку синхронные переключатели потребляют и отдают ток, R OS можно не использовать, а требования V OS к операционному усилителю можно уменьшить на 50%. Тогда уравнение 8 принимает вид V OSmax = I D × R S .

4 более детально показан рисунок 3a. с В REG1 и V REG2 нарисованы как синхронные переключатели. Поскольку синхронные переключатели потребляют и отдают ток, R OS можно не использовать, а требования V OS к операционному усилителю можно уменьшить на 50%. Тогда уравнение 8 принимает вид V OSmax = I D × R S . Здесь последовательные резисторы имеют тенденцию быть относительно большими и дорогими, вносить значительные потери и вызывать нежелательное повышение температуры. С помощью R DS(ON) полевых транзисторов нижнего плеча в качестве токоизмерительных резисторов дополнительные потери не требуются. Точность разделения тока будет несколько отличаться из-за несоответствия R DS(ON) . Но это будет в пределах приемлемого диапазона, если полевые транзисторы установлены на одном и том же медном участке радиатора или печатной платы.

Здесь последовательные резисторы имеют тенденцию быть относительно большими и дорогими, вносить значительные потери и вызывать нежелательное повышение температуры. С помощью R DS(ON) полевых транзисторов нижнего плеча в качестве токоизмерительных резисторов дополнительные потери не требуются. Точность разделения тока будет несколько отличаться из-за несоответствия R DS(ON) . Но это будет в пределах приемлемого диапазона, если полевые транзисторы установлены на одном и том же медном участке радиатора или печатной платы. 5 использует двойной операционный усилитель U1 для измерения и усиления (× 10) небольшого отрицательного напряжения, присутствующего на каждом нижнем полевом транзисторе в течение периода его проводимости. Для этого метода измерения требуется полевой транзистор нижнего плеча, что делает его применимым к синхронным переключателям.

5 использует двойной операционный усилитель U1 для измерения и усиления (× 10) небольшого отрицательного напряжения, присутствующего на каждом нижнем полевом транзисторе в течение периода его проводимости. Для этого метода измерения требуется полевой транзистор нижнего плеча, что делает его применимым к синхронным переключателям.

Для четвертого примера, который объясняет, как схема на рисунке 5 может комбинировать 30-A, 1,2-V каналы в один выходной ток 60 А, см. «Удвоение выходного тока с помощью параллельных регуляторов напряжения (часть 2)» по адресу www.elecdesign.com , Drill Deeper 9279 ED Online 9270 .

Стабильный источник тока смещения — Texas Instruments Incorporated

ОБЛАСТЬ ТЕХНИКИ ИЗОБРЕТЕНИЯ

Настоящее изобретение в целом относится к области интегрированных электронных устройств. Более конкретно, настоящее изобретение относится к способу и устройству для подачи стабильного тока смещения на устройство с интегральной схемой.

ПРЕДПОСЫЛКИ ИЗОБРЕТЕНИЯ

Различные устройства на интегральных схемах требуют генерирования стабильного тока смещения частью устройства. Ток смещения используется для установки величины токов, используемых для питания различных компонентов устройства. Очень важно, чтобы ток смещения оставался как можно ближе к заданному уровню, чтобы гарантировать, что общий ток, требуемый интегральной схемой, является постоянным и, следовательно, предсказуемым.

Различные силы, действующие на интегральную схему, могут вызывать колебания уровня тока смещения. Двумя наиболее значительными силами являются температура окружающей среды, в которой работает устройство, вызывающая флуктуации тока смещения, и изменения, вносимые в устройство при его конструировании и влияющие на величину тока смещения.

Типичным примером устройства на интегральной схеме, для которого требуется стабильный источник тока смещения, является маломощный операционный усилитель. Поскольку эти усилители используются в условиях малой мощности, для них требуются относительно простые цепи смещения с небольшим количеством компонентов и минимальными требованиями к току. Цепи питания током смещения для высокоточных операционных усилителей, как правило, включают большое количество компонентов для обеспечения стабильного выходного тока. Однако для этих цепей требуется больший ток, чем было бы приемлемо для маломощной конструкции.

Цепи питания током смещения для высокоточных операционных усилителей, как правило, включают большое количество компонентов для обеспечения стабильного выходного тока. Однако для этих цепей требуется больший ток, чем было бы приемлемо для маломощной конструкции.

Более простые схемы подачи тока смещения, используемые в маломощных конструкциях, потребляют меньше тока, но они более чувствительны к изменениям процесса и изменениям температуры окружающей среды. В результате страдает производительность маломощного операционного усилителя. Следовательно, используемые в настоящее время цепи питания током смещения удовлетворяют требованиям простой конструкции с низкими требованиями к току. Хотя эти схемы обычно включают элементарную температурную компенсацию за счет использования обычных резисторов, они не обеспечивают защиты от изменений процесса. Кроме того, из-за того, что технологические отклонения в резисторах особенно трудно контролировать, добавление этих резисторов к обычным схемам подачи тока смещения усугубляет проблему технологических отклонений.

Таким образом, возникла потребность в простой схеме подачи тока смещения, использующей относительно небольшое количество компонентов и имеющей, соответственно, небольшие требования по току, которая может обеспечить выходной ток, стабильный по отношению как к изменениям температуры окружающей среды, так и к изменениям процесса.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

В соответствии с идеями настоящего изобретения предложена маломощная схема подачи тока смещения, которая существенно устраняет или уменьшает недостатки и проблемы, связанные со схемами предшествующего уровня техники. Более конкретно, настоящее изобретение обеспечивает маломощную схему подачи тока смещения, которую можно использовать для подачи стабильного тока смещения на множество устройств на интегральных схемах. Схема по настоящему изобретению демонстрирует большую стабильность уровня выходного тока, чем схемы предшествующего уровня техники, в отношении изменений температуры окружающей среды и изменений процесса.

В одном варианте осуществления настоящего изобретения первоначальный источник тока соединен с зеркалом тока. Токовое зеркало включает в себя активный резистивный элемент, содержащий транзистор. Силам, изменяющим выходной ток начального источника тока, частично противодействует активный резистивный элемент. Таким образом, маломощная схема смещения по настоящему изобретению демонстрирует большую стабильность по отношению к изменениям температуры окружающей среды и изменениям процесса.

В другом варианте осуществления изобретения предусмотрена схема маломощного дифференциального усилителя, которая включает в себя схему подачи стабильного тока смещения. Схема подачи тока смещения включает в себя источник начального тока и токовое зеркало. Внутри токового зеркала полевой транзистор включен в качестве активного резистивного элемента для обеспечения стабильности выходного тока схемы смещения по отношению к температуре окружающей среды и технологическим изменениям. Из-за дополнительной стабильности выходного тока схемы подачи тока смещения схема маломощного дифференциального усилителя демонстрирует меньшие колебания в своих общих потребностях в токе подачи.

Важным техническим преимуществом настоящего изобретения является то, что оно обеспечивает стабильный источник тока смещения с небольшим количеством компонентов. Стабильность обеспечивается как при изменении температуры процесса, так и при изменении температуры окружающей среды без больших требований к току более сложных стабилизирующих схем.

Еще одно техническое преимущество настоящего изобретения заключается в том, что оно обеспечивает стабилизацию подачи тока смещения без использования обычных резисторов. Изменения процесса в обычных резисторах чрезвычайно трудно контролировать, и они могут еще больше усложнить любую схему стабилизации. Схема, построенная в соответствии с настоящим изобретением, не требует обычных резисторов и, таким образом, позволяет избежать этих широких вариаций процесса.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Более полное понимание настоящего изобретения может быть получено при обращении к подробному описанию изобретения и формуле изобретения при рассмотрении их в связи с прилагаемыми чертежами, на которых одинаковые ссылочные позиции указывают на одинаковые признаки, на которых:

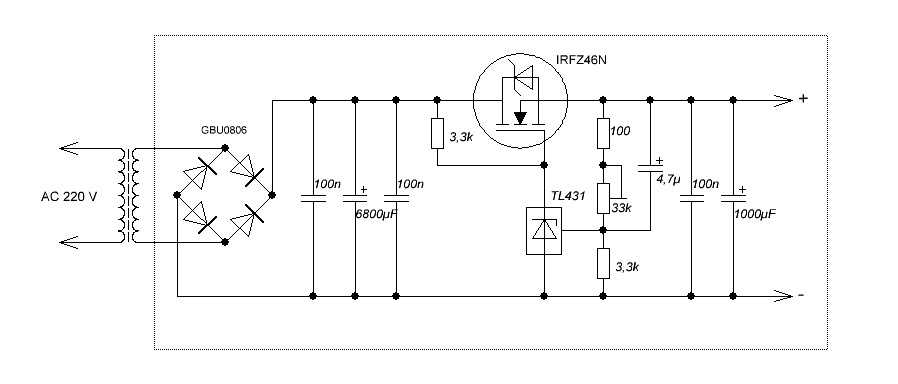

РИС. 1 представляет собой схематическое изображение известной схемы подачи тока смещения;

1 представляет собой схематическое изображение известной схемы подачи тока смещения;

РИС. 2 представляет собой схематическое изображение схемы подачи тока смещения, выполненной в соответствии с настоящим изобретением;

РИС. 3а представляет собой графическое представление работы схемы подачи тока смещения предшествующего уровня техники и схемы подачи тока смещения, сконструированной согласно настоящему изобретению, при номинальных параметрах процесса по отношению к изменениям температуры окружающей среды;

РИС. 3b представляет собой графическое представление характеристик схемы подачи тока смещения предшествующего уровня техники и схемы подачи тока смещения, сконструированной в соответствии с настоящим изобретением, по отношению как к температуре окружающей среды, так и к изменениям процесса;

РИС. 4 представляет собой принципиальную схему операционного усилителя, построенного в соответствии с настоящим изобретением; и

РИС. 5 представляет собой графическое сравнение требований к общему току операционного усилителя предшествующего уровня техники и операционного усилителя, сконструированного в соответствии с настоящим изобретением, в зависимости от изменений температуры окружающей среды.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

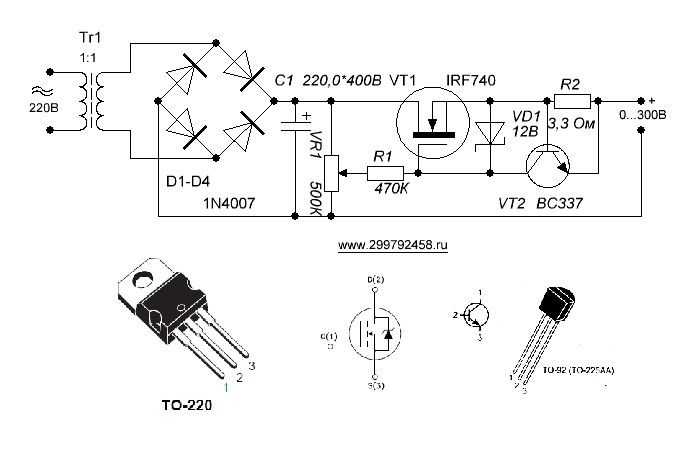

РИС. 1 представляет собой схематическое изображение типичной схемы подачи тока смещения предшествующего уровня техники, обозначенной в целом позицией 10. Схема 10 содержит полевой транзистор с первым переходом (JFET) 12. Исток и затвор JFET 12 соединены с источником напряжения V+. Начальный ток I D показан на фиг. 1, который генерируется из стока JFET 12. Сток JFET 12 соединен с одним концом резистора 14 и с базой первого биполярного переходного транзистора (BJT) 16. Противоположный конец резистора 14 соединен с коллектор BJT 16. Эмиттер BJT 16 соединен с источником напряжения V-. Коллектор BJT 16 также соединен с базой второго BJT 18. Эмиттер BJT 18 соединен с источником напряжения V-. Выходной ток I O генерируется в коллекторе биполярного транзистора 18.

Схематическое представление схемы подачи тока смещения, построенной в соответствии с настоящим изобретением, в целом обозначено позицией 20 на фиг. 2. Схема 20 содержит первый полевой транзистор 22, затвор и исток которого соединены с источником напряжения V+. Полевой транзистор 22 генерирует начальный ток I D в своем стоке. Сток первого полевого транзистора 22 соединен с затвором и истоком второго полевого транзистора 24, а также с основанием биполярного транзистора 26. Сток полевого транзистора 24 соединен с коллектором биполярного транзистора 26 и с основанием биполярного транзистора. BJT 28. Эмиттер BJT 26 соединен с эмиттером BJT 28 и источником напряжения V-. Выходной ток I O генерируется схемой 20 в коллекторе биполярного транзистора 28.

Схема 20 содержит первый полевой транзистор 22, затвор и исток которого соединены с источником напряжения V+. Полевой транзистор 22 генерирует начальный ток I D в своем стоке. Сток первого полевого транзистора 22 соединен с затвором и истоком второго полевого транзистора 24, а также с основанием биполярного транзистора 26. Сток полевого транзистора 24 соединен с коллектором биполярного транзистора 26 и с основанием биполярного транзистора. BJT 28. Эмиттер BJT 26 соединен с эмиттером BJT 28 и источником напряжения V-. Выходной ток I O генерируется схемой 20 в коллекторе биполярного транзистора 28.

В предпочтительном варианте полевые транзисторы 22 и 24 содержат полевые транзисторы с p-каналом. Однако аналогичная схема может быть спроектирована с использованием n-канальных JFET или n-канальных или p-канальных полевых МОП-транзисторов с режимом истощения.

Рассчитав значение I O в зависимости от параметров устройства в каждой цепи, можно продемонстрировать важные технические преимущества цепи 20. Как для схемы 10, так и для схемы 20 можно сделать некоторые упрощающие предположения. Во-первых, все базовые токи будут считаться пренебрежимо малыми. Во-вторых, транзисторы 16, 18, 26 и 28 BJT будут считаться эквивалентными транзисторами. Другими словами, токи насыщения и площади для каждого из этих транзисторов будут считаться равными. При этих разумных допущениях можно вывести следующие уравнения для обоих контуров 10 и 20: I D = I C (1)

Как для схемы 10, так и для схемы 20 можно сделать некоторые упрощающие предположения. Во-первых, все базовые токи будут считаться пренебрежимо малыми. Во-вторых, транзисторы 16, 18, 26 и 28 BJT будут считаться эквивалентными транзисторами. Другими словами, токи насыщения и площади для каждого из этих транзисторов будут считаться равными. При этих разумных допущениях можно вывести следующие уравнения для обоих контуров 10 и 20: I D = I C (1)

, где I C определяется как ток, протекающий в коллекторе BJT 16 и BJT 26, как показано на фиг. 1 и 2. I O =I D (exp[-(I D R eq )/V t ]) (2)

, где V t =kT/q ## EQU1## Для схемы 10 R eq равно значению резистора 14. Для схемы 12 R eq определяется как напряжение стока истока на полевом транзисторе 24, деленное на ток через полевой транзистор 24. Это можно записать как: р eq =V DS /I D

Уравнение 2, показанное выше, получено путем суммирования напряжений вокруг контура. Уравнение для выходного тока может быть получено следующим образом:

Уравнение для выходного тока может быть получено следующим образом:

Вывод ##EQU2## где A — площадь биполярных транзисторов 12, 16, 26 и 28, а I s — константа, представляющая ток насыщения для каждого этих транзисторов.

Чтобы лучше продемонстрировать преимущества схемы 20 по сравнению с схемой 10, в уравнение 2 можно добавить математические термины, чтобы проиллюстрировать изменения процесса во всех зависящих от процесса условиях. Для схемы 10, показанной на фиг. 1, это приводит к следующему уравнению: (P 1 I O )=(P 2 I D ) exp [-[(P 2 I D ) (P 3 R)3]/V )

, где P 1 , P 2 и P 3 — процентильные коэффициенты. Эти факторы представляют дробный уровень конкретного параметра по отношению к оптимальному уровню этого параметра. Другими словами, значение 0,90 для P 3 будет означать, что из-за обработки ниже оптимальной значение резистора 14 составляет только девяносто процентов от его оптимального значения. Если уравнение 2 применить к схеме 20, показанной на фиг. 2, и добавляются аналогичные термины процесса, можно вывести следующее уравнение: ##EQU3##

Если уравнение 2 применить к схеме 20, показанной на фиг. 2, и добавляются аналогичные термины процесса, можно вывести следующее уравнение: ##EQU3##

Когда для построения цепей 10 и 20 используются обычные технологические процессы, значение стандартного базового резистора может варьироваться на двадцать пять процентов выше или ниже его оптимального значения. Кроме того, значение тока насыщения JFET также может варьироваться на двадцать пять процентов выше или ниже его оптимального значения. Таким образом, эти вариации также включены в полученные уравнения.

Для определения изменения V DS при двадцатипятипроцентном изменении I D используется уравнение для JFET, работающего в линейной области. Это уравнение выглядит следующим образом: I D =Площадь×β×V DS [2(V GS -V TO )-V DS ][1+λ×V DS ] (5 )

λ можно пренебречь в уравнении 5, поскольку полевой транзистор JFET 24 имеет очень малое напряжение сток-исток. Решение уравнения 5 для V DS приводит к следующему уравнению: V DS =V P -SQRT[V P 2 -I D /Area×β)](6)

Решение уравнения 5 для V DS приводит к следующему уравнению: V DS =V P -SQRT[V P 2 -I D /Area×β)](6)

где Площадь определяется как ширина, деленная на длину области канала полевого транзистора JFET 24, а V P и β — другие параметры устройства JFET 24.

Путем подстановки характеристических данных для JFET 24 в уравнение 6 можно определить, что если I D составляет семьдесят пять процентов от его номинального значения, V DS составляет восемьдесят процентов от его номинального значения. ценить.

Чтобы проиллюстрировать разницу между двумя схемами, I D будет считаться равным семидесяти пяти процентам от его номинальной стоимости. Для этого примера будут предположены следующие условия:

Допущения

I D = 14 мкл

REQ = R = 1700 Ом

V T = 0,0258V

I O = 5,56 μ

I O = 5,566. A

A

Подставив эти значения в уравнение 3 для схемы 10 и предполагая, что базовый резистор 14 составляет семьдесят пять процентов от его номинального значения, можно получить следующее значение погрешности процесса, связанной с выходным током. ##EQU4##

Выполняя аналогичный расчет с использованием уравнения (4), полученного из схемы 20, можно получить следующее значение отклонения выходного тока из-за изменений процесса: ##EQU5##

Этот пример демонстрирует, что при при наихудших возможных отклонениях процесса выходной ток схемы 10 изменится на двадцать пять процентов, в то время как выходной ток схемы 20, показанный на фиг. 2 изменится только на десять процентов.

Превосходные характеристики схемы 20 являются результатом того факта, что полевой транзистор 24 сконструирован так же, как полевой транзистор 22. Эти устройства, например, могут быть сконструированы рядом друг с другом на микросхеме интегральной схемы, так что они будут демонстрировать почти идентичные технологические изменения и подвергаться аналогичным колебаниям температуры. Из-за согласованности полевых транзисторов 22 и 24 любое отклонение начального тока I D , вызванный силами, действующими на полевой транзистор 22, противодействует полевому транзистору 24, который имеет такую же дисперсию, вызывающую силы, действующие на него.

Из-за согласованности полевых транзисторов 22 и 24 любое отклонение начального тока I D , вызванный силами, действующими на полевой транзистор 22, противодействует полевому транзистору 24, который имеет такую же дисперсию, вызывающую силы, действующие на него.

В схеме полевого транзистора 24 сопротивление истока и стока должно быть минимальным. Этого можно достичь, обеспечив относительно короткие диффузии истока и стока и контактируя исток и сток более чем в одном месте.

Обратимся теперь к фиг. 3а показано графическое представление работы схемы 10 и схемы 20. Температура в градусах Цельсия показана на оси ординат графика на фиг. 3а, а выходной ток I O показано в микроамперах на оси координат. Кривая 30 иллюстрирует работу схемы 10 при номинальных условиях процесса и при переменных температурах окружающей среды. Кривая 32 иллюстрирует работу схемы 20 при номинальных условиях процесса и переменных условиях температуры окружающей среды.

Несмотря на то, что при номинальных условиях процентное изменение производительности двух схем одинаково, схема 20 по настоящему изобретению обеспечивает несколько явных преимуществ. Изменение выходного тока при изменении температуры окружающей среды является достаточно линейным для схемы 20, как показано на кривой 32. Такое линейное изменение в зависимости от температуры гораздо легче компенсировать, чем нелинейные изменения, связанные со схемой 10, показанные на кривой 30.

Изменение выходного тока при изменении температуры окружающей среды является достаточно линейным для схемы 20, как показано на кривой 32. Такое линейное изменение в зависимости от температуры гораздо легче компенсировать, чем нелинейные изменения, связанные со схемой 10, показанные на кривой 30.

Еще одним техническим преимуществом контура 20 является то, что он имеет отрицательный температурный коэффициент. Если схема 20 используется со схемой, которая имеет слегка положительный температурный коэффициент, уменьшение тока, подаваемого схемой 20, с повышением температуры помогает свести к минимуму изменение общего тока питания рассматриваемой схемы при изменении температуры.

РИС. 3b представляет собой графическое представление характеристик схем 10 и 20 в отношении как изменений температуры окружающей среды, так и изменений процесса. Кривая 36 и кривая 42 иллюстрируют характеристики, показанные на фиг. 3а контуров 10 и 20, соответственно, при номинальных условиях процесса и при различных температурах окружающей среды. Кривая 34 иллюстрирует работу схемы 10 при различных температурах окружающей среды с полевым транзистором JFET 12 в схеме 10, имеющим значение на двадцать пять процентов выше номинального, и резистором 14, имеющим значение на двадцать пять процентов меньше номинального. Как обсуждалось ранее, при использовании современной технологии обработки возможны отклонения процесса ± двадцать пять процентов. Из-за конфигурации компонентов схемы 10 два наихудших сценария изменения выходного тока I O возникают, когда JFET 12 и резистор 14 находятся на противоположных концах возможных спектров изменения процесса.

Кривая 34 иллюстрирует работу схемы 10 при различных температурах окружающей среды с полевым транзистором JFET 12 в схеме 10, имеющим значение на двадцать пять процентов выше номинального, и резистором 14, имеющим значение на двадцать пять процентов меньше номинального. Как обсуждалось ранее, при использовании современной технологии обработки возможны отклонения процесса ± двадцать пять процентов. Из-за конфигурации компонентов схемы 10 два наихудших сценария изменения выходного тока I O возникают, когда JFET 12 и резистор 14 находятся на противоположных концах возможных спектров изменения процесса.

Кривая 38 представляет противоположный наихудший сценарий для контура 10 из-за изменений процесса. Кривая 38 иллюстрирует работу схемы 10 при различных температурах окружающей среды, когда JFET 12 на двадцать пять процентов меньше номинального значения, а резистор 14 на двадцать пять процентов больше своего номинального значения. Таким образом, кривые 34 и 38 представляют возможные крайние значения производительности контура 10 из-за изменений процесса и изменений температуры окружающей среды. Таким образом, фактическая производительность контура 10 будет находиться в пределах диапазона, созданного кривыми 34 и 38.

Таким образом, фактическая производительность контура 10 будет находиться в пределах диапазона, созданного кривыми 34 и 38.

Кривая 42, показанная на РИС. 3b представляет работу схемы 20 при колебаниях температуры окружающей среды при номинальных условиях процесса. Возможные наихудшие случаи для схемы 20 возникают, когда рабочие параметры JFET 22 и JFET 24 на двадцать пять процентов выше их номинальных значений, и когда эти параметры обоих JFET 22 и 24 на двадцать пять процентов ниже их номинальных значений. . Варианты процесса для JFET 22 и 24 обычно не являются независимыми. JFET 22 и 24 могут быть размещены в схемной схеме так, что они будут демонстрировать почти идентичные технологические изменения. Таким образом, нет необходимости рассматривать сценарий, в котором JFET 22 демонстрирует изменение процесса, отличное от JFET 24. Кривая 40 иллюстрирует работу схемы 20 в различных условиях температуры окружающей среды, когда рабочие параметры JFET 22 и 24 равны двадцати пяти. процентов выше их номинальной стоимости. Кривая 44 иллюстрирует работу схемы 20 в различных условиях температуры окружающей среды, когда рабочие параметры обоих полевых транзисторов JFET 22 и 24 на двадцать пять процентов меньше их номинальных значений из-за изменений процесса.

Кривая 44 иллюстрирует работу схемы 20 в различных условиях температуры окружающей среды, когда рабочие параметры обоих полевых транзисторов JFET 22 и 24 на двадцать пять процентов меньше их номинальных значений из-за изменений процесса.

Огибающая, созданная кривыми 40 и 44 возможной характеристики выходного тока для схемы 20, явно уже, чем показанная на фиг. 3b для схемы 10. Фиг. Таким образом, фиг.3b иллюстрирует важное техническое преимущество, которое схема 20 имеет по сравнению с схемой 10 благодаря ее стабильности как при изменении температуры, так и при изменении процесса.

Еще один вариант осуществления настоящего изобретения показан на фиг. 4. Важность стабильности выходного тока I O схемы 20 лучше всего проиллюстрировать, когда цепь смещения 20 исследуется в сочетании с конкретной схемой, для которой она подает ток смещения. ИНЖИР. 4 представляет собой принципиальную схему дифференциального усилителя 46, использующего схему 20 для подачи тока смещения для различных каскадов усилителя.

Цепь смещения 20 обеспечивает выходной ток смещения I O , который подается через биполярный транзистор 48. Коллектор биполярного транзистора 48 соединен с коллектором биполярного транзистора 28 в цепи смещения 20, а его эмиттер соединен с источником напряжения V+. BJT 48 функционирует как часть токового зеркала, которое управляет величиной тока, подводимого к каждому из каскадов операционного усилителя 46. BJT 49 имеет базу, соединенную с коллектором BJT 48, эмиттер, соединенный с базой BJT 48, и коллектор, подключенный к источнику напряжения V-. Это текущее зеркало включает BJT 48, BJT 50, BJT 52, BJT 54, BJT 56 и BJT 58. BJT 49.обеспечивает базовый ток для BJT 48 и 50-58.

Каждый из BJT с 50 по 58 имеет размер, пропорциональный BJT 48, как показано на РИС. 4. Например, как показано на фиг. 4, BJT 50 в 1,5 раза больше BJT 48. Каждый BJT 50 и 52 имеет свои базы, соединенные с базой BJT 48. Оба BJT 50 и 52 имеют свои эмиттеры, соединенные с источником напряжения V+. BJT 50 имеет два выхода коллектора, которые соединены с входным каскадом 60. BJT 52 имеет один выход коллектора, соединенный с входным каскадом 60. Входной каскад 60 имеет неинвертирующий вход 62 и инвертирующий вход 64. Сигнальный вход на не- инвертирующий вход 62 усиливается усилителем 46 без инвертирования сигнала. Сигнал, поступающий на инвертирующий вход 64, усиливается усилителем 46 и также инвертируется перед выходом. Входной каскад 60 также подключен к источнику напряжения V-V.

BJT 50 имеет два выхода коллектора, которые соединены с входным каскадом 60. BJT 52 имеет один выход коллектора, соединенный с входным каскадом 60. Входной каскад 60 имеет неинвертирующий вход 62 и инвертирующий вход 64. Сигнальный вход на не- инвертирующий вход 62 усиливается усилителем 46 без инвертирования сигнала. Сигнал, поступающий на инвертирующий вход 64, усиливается усилителем 46 и также инвертируется перед выходом. Входной каскад 60 также подключен к источнику напряжения V-V.

База BJT 54 соединена с BJT 48, а эмиттер соединен с источником напряжения V+. BJT 54 имеет два выхода коллектора, которые подключены ко второму каскаду 66. BJT 54 в 1,5 раза больше по размеру, чем BJT 48, и поэтому проводит примерно в 1,5 раза больше тока, чем BJT 48. Второй каскад 66 подключен непосредственно к источнику напряжения V+. Второй каскад 66 также подключен через инвертирующий вход 67 и неинвертирующий вход 69 к входному каскаду 60. Второй каскад 66 подключен непосредственно к источнику напряжения V и также подключен к коллектору npn BJT 68. Эмиттер BJT 68 подключен к источнику напряжения V-. База BJT 68 подключена к npn BJT 70. Эмиттер BJT 70 подключен к источнику напряжения V-V. Коллектор и база BJT 70 соединены с коллектором BJT 56. Эмиттер BJT 56 соединен с источником напряжения V+. Основание BJT 56 соединено с основанием BJT 48.

Эмиттер BJT 68 подключен к источнику напряжения V-. База BJT 68 подключена к npn BJT 70. Эмиттер BJT 70 подключен к источнику напряжения V-V. Коллектор и база BJT 70 соединены с коллектором BJT 56. Эмиттер BJT 56 соединен с источником напряжения V+. Основание BJT 56 соединено с основанием BJT 48.

Эмиттер BJT 58 соединен с источником напряжения V+, его база соединена с базой BJT 48, а его коллектор соединен с базой и коллектором npn BJT 72. Эмиттер BJT 72 соединен с источником напряжения V- . База и коллектор BJT 72 подключены к базе npn BJT 74. Эмиттер BJT 74 подключен к источнику напряжения V, а коллектор BJT 74 подключен к выходному каскаду 76.

Выходной каскад 76 подключен непосредственно ко второй ступени 66, источнику напряжения V+ и источнику напряжения V-. Выходной каскад 76 формирует выходной сигнал усилителя 46 через выходной узел 78.

Размеры npn BJT 68, 70, 72 и 74 не зависят от размеров pnp BJT 48, 50, 52, 54, 56 и 58. Соотношение размеров npn BJT не зависит от соотношения размеров pnp BJT. Ток в npn BJT 70 и в npn BJT 72 задается pnp BJT 56 и 58 соответственно. Этот ток через токовое зеркало, образованное биполярными транзисторами 48, 56 и 58, устанавливается равным удвоенному выходному току I O схемы смещения 20. Таким образом, ток, протекающий через биполярный транзистор 68, за счет работы токового зеркала устанавливается в три раза больше. ток, протекающий через npn BJT 70. Таким образом, ток, протекающий через npn BJT 68, примерно в шесть раз превышает выходной ток I O цепи смещения 20. Точно так же ток, протекающий через npn BJT 74, примерно в шесть раз превышает выходной ток I O , генерируемый схемой 20.

Ток в npn BJT 70 и в npn BJT 72 задается pnp BJT 56 и 58 соответственно. Этот ток через токовое зеркало, образованное биполярными транзисторами 48, 56 и 58, устанавливается равным удвоенному выходному току I O схемы смещения 20. Таким образом, ток, протекающий через биполярный транзистор 68, за счет работы токового зеркала устанавливается в три раза больше. ток, протекающий через npn BJT 70. Таким образом, ток, протекающий через npn BJT 68, примерно в шесть раз превышает выходной ток I O цепи смещения 20. Точно так же ток, протекающий через npn BJT 74, примерно в шесть раз превышает выходной ток I O , генерируемый схемой 20.

При работе токи, протекающие в каждом каскаде усилителя 46, по существу пропорциональны к выходному току I O , генерируемому схемой смещения 20. Таким образом, любое изменение выходного тока I O геометрически увеличивается и может привести к резким изменениям общего тока, потребляемого усилителем 46. Из-за этих геометрических взаимосвязей токи питания различных каскадов усилителя 46, небольшой разброс выходного тока I O умножается примерно в 36 раз на общий ток питания усилителя 46.

Из-за этих геометрических взаимосвязей токи питания различных каскадов усилителя 46, небольшой разброс выходного тока I O умножается примерно в 36 раз на общий ток питания усилителя 46.

РИС. 5 графически иллюстрирует улучшенные характеристики схемы 20 по сравнению со схемой 10 при использовании в усилителе 46. На фиг. 5 представляет собой графическое представление полного тока питания усилителя 46 при изменении температуры окружающей среды. Кривая 82 иллюстрирует изменения общего тока питания в диапазоне температур окружающей среды для усилителя, подобного усилителю 46, но использующего схему 10, показанную на фиг. 1 в качестве цепи подачи тока смещения. Кривая 80 иллюстрирует характеристики усилителя 46, использующего схему 20 в качестве схемы подачи тока смещения. В диапазоне 170°, показанном на фиг. 5 кривая 82 показывает изменение общего тока питания на девяносто микроампер. Кривая 80, однако, для того же температурного диапазона показывает лишь изменение общего тока питания всего на тридцать микроампер.

РИС. 5 также показывает, что кривая 80 является гораздо более линейной, чем кривая 82. Этот факт показывает, что температурная зависимость полного тока питания операционного усилителя, использующего схему питания током смещения, построенную в соответствии с настоящим изобретением, имеет приблизительно линейную температурную зависимость. Как обсуждалось ранее, линейную температурную зависимость кривой 80 гораздо проще спроектировать, чем нелинейную температурную зависимость, показанную на кривой 82.

Схема 20 подачи тока смещения, показанная на ФИГ. 2 и 4 применимы к большому количеству цепей. Усилитель 46, показанный на фиг. 4 представляет собой только один возможный вариант осуществления настоящего изобретения и использовался исключительно для демонстрации важных технических преимуществ настоящего изобретения. Цепь подачи тока, выполненная в соответствии с настоящим изобретением, может использоваться везде, где требуется ток, который должен оставаться постоянным при изменении температуры окружающей среды и технологических изменений.