Эмиттерный и истоковый повторители | Основы электроакустики

Главная » Элементы усилителей

Эмиттерный и истоковый повторители

Эмиттерный и истоковый повторители представляют собой усилители тока и мощности, выполненные на транзисторах по схеме с ОК (ОС), охваченные 100%-ной последовательной ООС.

Основные свойства этих каскадов близки, а существующие отличия обусловлены несовпадением характеристик используемых транзисторов. Pассмотрим схему эмиттерного повторителя (ЭП), отмечая для истокового повторителя только его характерные особенности. Сопротивление нагрузки включается в эмиттерную цепь транзистора. ЭП обладает повышенным входными и пониженным выходным сопротивлениями. Его входное и выходные напряжения совпадают по фазе и незначительно отличаются по величине. Отмеченные свойства ЭП позволяют использовать его для согласования (разделения) высокоомного источника сигнала и низкоомной нагрузки.

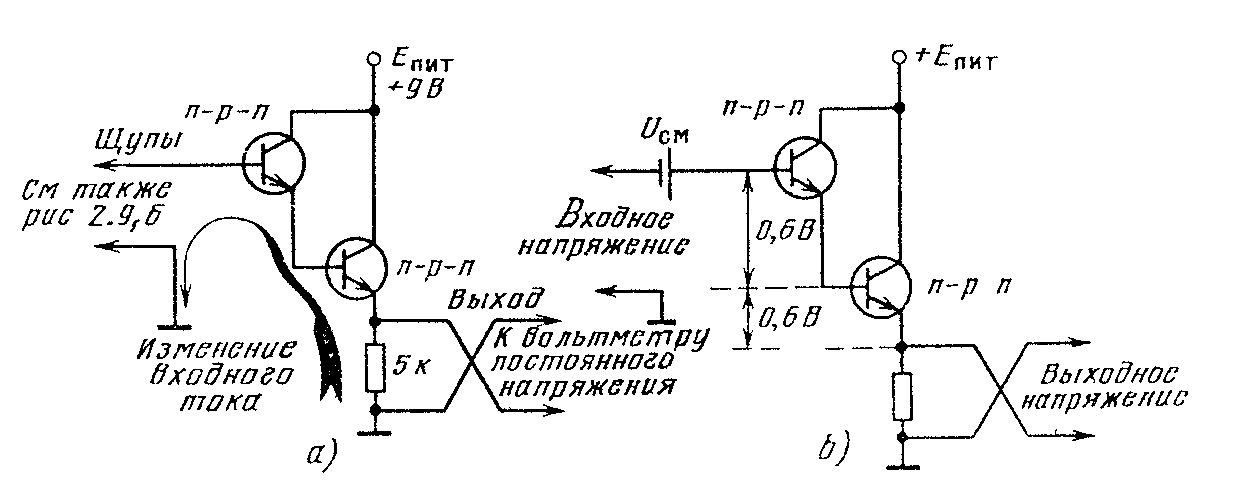

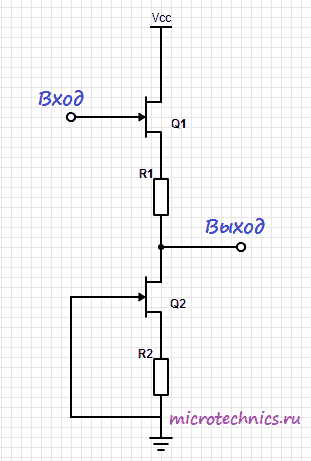

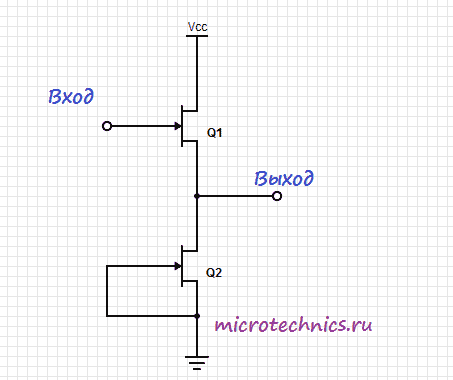

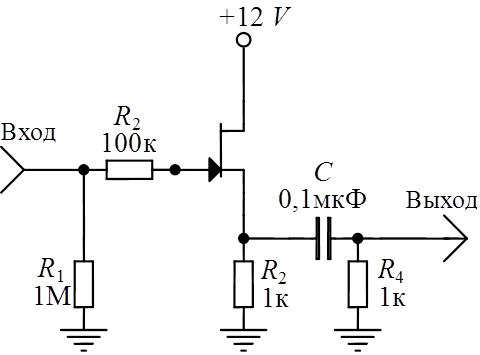

Рис.11.14. Схемы эмиттерного (а) и стокового (б) повторителейЭП можно рассматривать как усилительный каскад с ОЭ, у которого RК = 0, а резистор в цепи эмиттера не зашунтирован конденсатором. В этом случае все выходное напряжение, выделяемое на сопротивлении в цепи эмиттера, последовательно вводится во входную цепь усилителя, где вычитается из напряжения входного сигнала UВХ, снижая его. В схеме действует 100%-ая последовательная ООС по напряжению, увеличивающая входное и уменьшающая выходное сопротивление ЭП. В отличие от усилителя с общим эмиттером, ЭП не инвертирует входной сигнал. Действительно, если к входу эмиттерного повторителя приложить увеличивающееся по уровню напряжение, то это приведет к увеличению эмиттерного тока транзистора и соответствующему увеличению его выходного напряжения. Поэтому входной и выходной сигналы в схеме будут изменяться в одинаковой фазе.

В этом случае все выходное напряжение, выделяемое на сопротивлении в цепи эмиттера, последовательно вводится во входную цепь усилителя, где вычитается из напряжения входного сигнала UВХ, снижая его. В схеме действует 100%-ая последовательная ООС по напряжению, увеличивающая входное и уменьшающая выходное сопротивление ЭП. В отличие от усилителя с общим эмиттером, ЭП не инвертирует входной сигнал. Действительно, если к входу эмиттерного повторителя приложить увеличивающееся по уровню напряжение, то это приведет к увеличению эмиттерного тока транзистора и соответствующему увеличению его выходного напряжения. Поэтому входной и выходной сигналы в схеме будут изменяться в одинаковой фазе.

Oсновные характеристики каскада. Для определения коэффициента усиления по напряжению воспользуемся основным выражением для коэффициента передачи усилителя с цепью ООС. Тогда, имея коэффициент обратной связи βU = 1, получим КUЭП = КU / (1 + КU βU) = КU / (1 + KU) < 1. Для реальных схем входное сопротивление каскада RВХ = β RЭ, где β – коэффициент усиления транзистора по току. Не обладая усилением по напряжению, ЭП обладает значительным усилением по току: КIЭП = β + 1. Следствием этого является значительное усиление по мощности (КР ≈ КI). Частотные свойства ЭП (как и каскада с общим эмиттером) полностью определяются частотными свойствами применяемого транзистора. Однако на практике данный каскад является более высокочастотным, что является следствием 100%-ой ООС.Основные свойства истокового повторителя аналогичны свойствам ЭП: КUИП < 1; RВХ≈ RЗ – велико; RВЫХ ≈1 / S – мало. Частотные свойства истокового повторителя сущетвенно лучше частотных свойств каскада с общим истоком. Причина этого та же, что и в схеме ЭП – 100%-ная ООС. Следует отметить, что цепь затвора в схеме на рис. 11.14, б шунтирована резистором, поэтому не удается реализовать свойственное полевому транзистору большое входное сопротивление. Для реализации этой возможности необходимо применять МОП транзисторы со встроенным каналом, имеющие возможность работать без смещения.

Не обладая усилением по напряжению, ЭП обладает значительным усилением по току: КIЭП = β + 1. Следствием этого является значительное усиление по мощности (КР ≈ КI). Частотные свойства ЭП (как и каскада с общим эмиттером) полностью определяются частотными свойствами применяемого транзистора. Однако на практике данный каскад является более высокочастотным, что является следствием 100%-ой ООС.Основные свойства истокового повторителя аналогичны свойствам ЭП: КUИП < 1; RВХ≈ RЗ – велико; RВЫХ ≈1 / S – мало. Частотные свойства истокового повторителя сущетвенно лучше частотных свойств каскада с общим истоком. Причина этого та же, что и в схеме ЭП – 100%-ная ООС. Следует отметить, что цепь затвора в схеме на рис. 11.14, б шунтирована резистором, поэтому не удается реализовать свойственное полевому транзистору большое входное сопротивление. Для реализации этой возможности необходимо применять МОП транзисторы со встроенным каналом, имеющие возможность работать без смещения.

Режим работы транзистора в схеме усилительного каскада

Усиление сигналов с помощью транзистора

Каскад с общим эмиттером

Эмиттерные повторители и фазоинверсные усилители

Усилитель на биполярном транзисторе с общим эмиттером

Методы задания начального режима работы транзистора

Влияние Обратной Связи на параметры усилителей

Основные схемы включения и параметры транзисторов

Полупроводниковая схемотехника

Полупроводниковая схемотехника

ОглавлениеПредисловие редактора перевода1. Пояснение применяемых величин 2. Пассивные RC- и LRC- цепи 2.1. ФИЛЬТР НИЖНИХ ЧАСТОТ 2.1.3. ДЛИТЕЛЬНОСТЬ ФРОНТА ИМПУЛЬСА И ЧАСТОТА СРЕЗА ФИЛЬТРА 2.2. ФИЛЬТР ВЕРХНИХ ЧАСТОТ 2.3. КОМПЕНСИРОВАННЫЙ ДЕЛИТЕЛЬ НАПРЯЖЕНИЯ 2.4. ПАССИВНЫЙ ПОЛОСОВОЙ RC-ФИЛЬТР 2.5. МОСТ ВИНА-РОБИНСОНА 2.6.  ДВОЙНОЙ Т-ОБРАЗНЫЙ ФИЛЬТР ДВОЙНОЙ Т-ОБРАЗНЫЙ ФИЛЬТР2.7. КОЛЕБАТЕЛЬНЫЙ КОНТУР 3. Диоды 3.2. СТАБИЛИТРОНЫ 3.3. ВАРИКАПЫ 4. Транзистор и схемы на его основе 4.2. СХЕМА С ОБЩИМ ЭМИТТЕРОМ 4.2.2. НЕЛИНЕЙНЫЕ ИСКАЖЕНИЯ 4.2.3. СХЕМА С ОБЩИМ ЭМИТТЕРОМ И ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО ТОКУ 4.2.5. УСТАНОВКА РАБОЧЕЙ ТОЧКИ 4.3. СХЕМА С ОБЩЕЙ БАЗОЙ 4.4. СХЕМА С ОБЩИМ КОЛЛЕКТОРОМ, ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ 4.5. ТРАНЗИСТОР КАК ИСТОЧНИК СТАБИЛЬНОГО ТОКА 4.5.2. БИПОЛЯРНЫЙ ИСТОЧНИК ПИТАНИЯ 4.5.3. СХЕМА «ТОКОВОГО ЗЕРКАЛА» 4.6. СХЕМА ДАРЛИНГТОНА 4.7. ДИФФЕРЕНЦИАЛЬНЫЕ УСИЛИТЕЛИ 4.7.2. РЕЖИМ БОЛЬШОГО СИГНАЛА 4.7.3. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО ТОКУ 4.7.4. НАПРЯЖЕНИЕ РАЗБАЛАНСА 4.8. ИЗМЕРЕНИЕ НЕКОТОРЫХ ПАРАМЕТРОВ ПРИ МАЛОМ СИГНАЛЕ 4.9. ШУМЫ ТРАНЗИСТОРА 4.10. ПРЕДЕЛЬНЫЕ ПАРАМЕТРЫ 5. Полевые транзисторы 5.2. ХАРАКТЕРИСТИКИ И ПАРАМЕТРЫ МАЛЫХ СИГНАЛОВ  ПРЕДЕЛЬНЫЕ ЭЛЕКТРИЧЕСКИЕ ПАРАМЕТРЫ ПРЕДЕЛЬНЫЕ ЭЛЕКТРИЧЕСКИЕ ПАРАМЕТРЫ5.4. ОСНОВНЫЕ СХЕМЫ ВКЛЮЧЕНИЯ 5.4.1. СХЕМА С ОБЩИМ ИСТОКОМ 5.4.2. СХЕМА С ОБЩИМ ЗАТВОРОМ 5.4.3. СХЕМА С ОБЩИМ СТОКОМ, ИСТОКОВЫЙ ПОВТОРИТЕЛЬ 5.5. ПОЛЕВОЙ ТРАНЗИСТОР КАК СТАБИЛИЗАТОР ТОКА 5.6. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ 5.7. ПОЛЕВОЙ ТРАНЗИСТОР В КАЧЕСТВЕ УПРАВЛЯЕМОГО СОПРОТИВЛЕНИЯ 6. Операционный усилитель 6.1. СВОЙСТВА ОПЕРАЦИОННОГО УСИЛИТЕЛЯ 6.2. ПРИНЦИП ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗИ 6.3. НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ 6.4. ИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ 7.2. ПРОСТЕЙШИЕ СХЕМЫ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 7.3. СТАНДАРТНАЯ СХЕМА ИНТЕГРАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ 7.4. КОРРЕКЦИЯ ЧАСТОТНОЙ ХАРАКТЕРИСТИКИ 7.4.2. ПОЛНАЯ ЧАСТОТНАЯ КОРРЕКЦИЯ 7.4.3. ПОДСТРАИВАЕМАЯ ЧАСТОТНАЯ КОРРЕКЦИЯ 7.4.4. СКОРОСТЬ НАРАСТАНИЯ 7.4.5. КОМПЕНСАЦИЯ ЕМКОСТНОЙ НАГРУЗКИ 7.5. ИЗМЕРЕНИЕ ПАРАМЕТРОВ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 8. Простейшие переключающие схемы 8.  1. ТРАНЗИСТОРНЫЙ КЛЮЧ 1. ТРАНЗИСТОРНЫЙ КЛЮЧ8.2. БИСТАБИЛЬНЫЕ РЕЛАКСАЦИОННЫЕ СХЕМЫ 8.2.2. ТРИГГЕР ШМИТТА 8.3. МОНОСТАБИЛЬНАЯ РЕЛАКСАЦИОННАЯ СХЕМА 9. Базовые логические схемы 9.1. ОСНОВНЫЕ ЛОГИЧЕСКИЕ ФУНКЦИИ 9.2. СОСТАВЛЕНИЕ ЛОГИЧЕСКИХ ФУНКЦИЙ 9.2.1. ТАБЛИЦА КАРНО 9.3. ПРОИЗВОДНЫЕ ОСНОВНЫХ ЛОГИЧЕСКИХ ФУНКЦИЙ 9.4. СХЕМОТЕХНИЧЕСКАЯ РЕАЛИЗАЦИЯ ОСНОВНЫХ ЛОГИЧЕСКИХ ФУНКЦИЙ 9.4.1. РЕЗИСТИВНО-ТРАНЗИСТОРНАЯ ЛОГИКА (РТЛ) 9.4.2. ДИОДНО-ТРАНЗИСТОРНАЯ ЛОГИКА (ДТЛ) 9.4.3. ТРАНЗИСТОРНО-ТРАНЗИСТОРНАЯ ЛОГИКА (ТТЛ) 9.4.4. ИНТЕГРАЛЬНАЯ ИНЖЕКЦИОННАЯ ЛОГИКА 9.4.5. ЭМИТТЕРНО-СВЯЗАННАЯ ЛОГИКА (ЭСЛ) 9.4.6. n-КАНАЛЬНАЯ МОП-ЛОГИКА 9.4.7. КОМПЛЕМЕНТАРНАЯ МОП-ЛОГИКА (КМОП) 9.4.8. ОБЗОР 9.4.9. СПЕЦИАЛЬНЫЕ СХЕМЫ ВЫХОДНЫХ КАСКАДОВ 9.5. ИНТЕГРАЛЬНЫЕ ТРИГГЕРЫ 9.5.2. ТРИГГЕРЫ ТИПА M-S (MASTER-SLAVE) 9.6. ПОЛУПРОВОДНИКОВЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА 9.6.2. ПОСТОЯННЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА (ПЗУ) 9.  6.3. ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ МАТРИЦЫ (ПЛМ) 6.3. ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ МАТРИЦЫ (ПЛМ)10. Оптоэлектронные приборы 10.1. ОСНОВНЫЕ ПОНЯТИЯ ФОТОМЕТРИИ 10.2. ФОТОРЕЗИСТОР 10.3. ФОТОДИОДЫ 10.4. ФОТОТРАНЗИСТОРЫ 10.5. СВЕТОДИОДЫ 10.6. ОПТРОНЫ Часть II. Применения 11. Линейные и нелинейные аналоговые вычислительные схемы 11.1. СХЕМА СУММИРОВАНИЯ 11.2. СХЕМЫ ВЫЧИТАНИЯ 11.2.2. СХЕМА ВЫЧИТАНИЯ НА ОПЕРАЦИОННОМ УСИЛИТЕЛЕ 11.3. БИПОЛЯРНОЕ УСИЛИТЕЛЬНОЕ ЗВЕНО 11.4.1. ИНВЕРТИРУЮЩИЙ ИНТЕГРАТОР 11.4.2. ЗАДАНИЕ НАЧАЛЬНЫХ УСЛОВИЙ 11.4.3. СУММИРУЮЩИЙ ИНТЕГРАТОР 11.4.4. НЕИНВЕРТИРУЮЩИЙ ИНТЕГРАТОР 11.5. СХЕМЫ ДИФФЕРЕНЦИРОВАНИЯ 11.5.3. СХЕМА ДИФФЕРЕНЦИРОВАНИЯ С ВЫСОКИМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ 11.6. РЕШЕНИЕ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ 11.7. ФУНКЦИОНАЛЬНЫЕ ПРЕОБРАЗОВАТЕЛИ 11.7.2. ЭКСПОНЕНТА 11.7.3. ВЫЧИСЛЕНИЕ СТЕПЕННЫХ ФУНКЦИЙ С ПОМОЩЬЮ ЛОГАРИФМОВ 11.7.4. ФУНКЦИИ SIN X И COS X 11.7.5. ПЕРЕСТРАИВАЕМЫЕ ФУНКЦИОНАЛЬНЫЕ СХЕМЫ 11.  8. АНАЛОГОВЫЕ СХЕМЫ УМНОЖЕНИЯ 8. АНАЛОГОВЫЕ СХЕМЫ УМНОЖЕНИЯ11.8.2. УМНОЖЕНИЕ С ПОМОЩЬЮ ЛОГАРИФМИЧЕСКИХ ФУНКЦИОНАЛЬНЫХ ГЕНЕРАТОРОВ 11.8.4. СХЕМА УМНОЖЕНИЯ С ИЗОЛИРОВАННЫМИ ЗВЕНЬЯМИ 11.8.5. БАЛАНСИРОВКА СХЕМ УМНОЖЕНИЯ 11.8.6. СХЕМЫ ЧЕТЫРЕХКВАДРАНТНОГО УМНОЖЕНИЯ 11.8.7. ПРИМЕНЕНИЕ СХЕМЫ УМНОЖЕНИЯ ДЛЯ ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНЫХ КОРНЕЙ 11.9. ПРЕОБРАЗОВАНИЕ КООРДИНАТ 11.9.2. ПРЕОБРАЗОВАНИЕ ДЕКАРТОВЫХ КООРДИНАТ В ПОЛЯРНЫЕ 12. Управляемые источники и схемы преобразования полного сопротивления 12.1. ИСТОЧНИКИ НАПРЯЖЕНИЯ, УПРАВЛЯЕМЫЕ НАПРЯЖЕНИЕМ 12.2. ИСТОЧНИКИ НАПРЯЖЕНИЯ, УПРАВЛЯЕМЫЕ ТОКОМ 12.3. ИСТОЧНИКИ ТОКА, УПРАВЛЯЕМЫЕ НАПРЯЖЕНИЕМ 12.3.2. ИСТОЧНИКИ ТОКА С ЗАЗЕМЛЕННОЙ НАГРУЗКОЙ 12.3.4. ПЛАВАЮЩИЕ ИСТОЧНИКИ ТОКА 12.4. ИСТОЧНИКИ ТОКА, УПРАВЛЯЕМЫЕ ТОКОМ 12.5. ПРЕОБРАЗОВАТЕЛЬ ОТРИЦАТЕЛЬНОГО СОПРОТИВЛЕНИЯ (NIC) 12.6. ГИРАТОР 12.  7. ЦИРКУЛЯТОР 7. ЦИРКУЛЯТОР13. Активные фильтры 13.1. ТЕОРЕТИЧЕСКОЕ ОПИСАНИЕ ФИЛЬТРОВ НИЖНИХ ЧАСТОТ 13.1.1. ФИЛЬТР БАТТЕРВОРТА 13.1.2. ФИЛЬТР ЧЕБЫШЕВА 13.1.3. ФИЛЬТРЫ БЕССЕЛЯ 13.1.4. ОБОБЩЕННОЕ ОПИСАНИЕ ФИЛЬТРОВ 13.2. ПРЕОБРАЗОВАНИЕ НИЖНИХ ЧАСТОТ В ВЕРХНИЕ 13.3. РЕАЛИЗАЦИЯ ФИЛЬТРОВ НИЖНИХ И ВЕРХНИХ ЧАСТОТ ПЕРВОГО ПОРЯДКА 13.4. РЕАЛИЗАЦИЯ ФИЛЬТРОВ НИЖНИХ И ВЕРХНИХ ЧАСТОТ ВТОРОГО ПОРЯДКА 13.4.3. ФИЛЬТР С ПОЛОЖИТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.4.4. ФИЛЬТР НИЖНИХ ЧАСТОТ С ОМИЧЕСКОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.5. РЕАЛИЗАЦИЯ ФИЛЬТРОВ ВЕРХНИХ И НИЖНИХ ЧАСТОТ БОЛЕЕ ВЫСОКОГО ПОРЯДКА 13.6. ПРЕОБРАЗОВАНИЕ ФИЛЬТРА НИЖНИХ ЧАСТОТ В ПОЛОСОВОЙ ФИЛЬТР 13.6.1. ПОЛОСОВОЙ ФИЛЬТР ВТОРОГО ПОРЯДКА 13.6.2. ПОЛОСОВОЙ ФИЛЬТР ЧЕТВЕРТОГО ПОРЯДКА 13.7. РЕАЛИЗАЦИЯ ПОЛОСОВЫХ ФИЛЬТРОВ ВТОРОГО ПОРЯДКА 13.7.2. ПОЛОСОВОЙ ФИЛЬТР СО СЛОЖНОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.7.3. ПОЛОСОВОЙ ФИЛЬТР С ПОЛОЖИТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.  13.8. ПРЕОБРАЗОВАНИЕ ФИЛЬТРОВ НИЖНИХ ЧАСТОТ В ЗАГРАЖДАЮЩИЕ ПОЛОСОВЫЕ ФИЛЬТРЫ 13.9. РЕАЛИЗАЦИЯ ЗАГРАЖДАЮЩИХ ФИЛЬТРОВ ВТОРОГО ПОРЯДКА 13.9.1. ЗАГРАЖДАЮЩИЙ LRC-ФИЛЬТР 13.9.2. АКТИВНЫЙ ЗАГРАЖДАЮЩИЙ ФИЛЬТР С ДВОЙНЫМ Т-ОБРАЗНЫМ МОСТОМ 13.9.3. АКТИВНЫЙ ЗАГРАЖДАЮЩИЙ ФИЛЬТР С МОСТОМ ВИНА-РОБИНСОНА 13.10. ФАЗОВЫЙ ФИЛЬТР 13.10.2. РЕАЛИЗАЦИЯ ФАЗОВОГО ФИЛЬТРА ПЕРВОГО ПОРЯДКА 13.10.3. РЕАЛИЗАЦИЯ ФАЗОВОГО ФИЛЬТРА ВТОРОГО ПОРЯДКА 13.11. ПЕРЕСТРАИВАЕМЫЙ УНИВЕРСАЛЬНЫЙ ФИЛЬТР 14. Широкополосные усилители 14.1. ЗАВИСИМОСТЬ КОЭФФИЦИЕНТА УСИЛЕНИЯ ПО ТОКУ ОТ ЧАСТОТЫ 14.2. ВЛИЯНИЕ ВНУТРЕННИХ ЕМКОСТЕЙ ТРАНЗИСТОРА И ЕМКОСТЕЙ МОНТАЖА 14.4. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ КАК ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ 14.5. СИММЕТРИЧНЫЙ ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ 14.5.2. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ИНВЕРТОРОМ 14.5.3. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С КОМПЛЕМЕНТАРНОЙ КАСКОДНОЙ СХЕМОЙ 14.5.  4. ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ 4. ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ14.6. ШИРОКОПОЛОСНЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ 14.6.2. ДВУХТАКТНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ 14.7. ШИРОКОПОЛОСНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ 15. Усилители мощности 15.1. ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ КАК УСИЛИТЕЛЬ МОЩНОСТИ 15.2. КОМПЛЕМЕНТАРНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ 15.2.2. КОМПЛЕМЕНТАРНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ В РЕЖИМЕ AB 15.3. СХЕМЫ ОГРАНИЧЕНИЯ ТОКА 15.4. КОМПЛЕМЕНТАРНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ ПО СХЕМЕ ДАРЛИНГТОНА 15.5. РАСЧЕТ МОЩНОГО ОКОНЕЧНОГО КАСКАДА 15.6. СХЕМЫ ПРЕДВАРИТЕЛЬНЫХ УСИЛИТЕЛЕЙ НАПРЯЖЕНИЯ 15.7. ПОВЫШЕНИЕ НАГРУЗОЧНОЙ СПОСОБНОСТИ ИНТЕГРАЛЬНЫХ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 16. Источники питания 16.1. СВОЙСТВА СЕТЕВЫХ ТРАНСФОРМАТОРОВ 16.2. ВЫПРЯМИТЕЛИ 16.2.1. ОДНОПОЛУПЕРИОДНЫЙ ВЫПРЯМИТЕЛЬ 16.2.2. МОСТОВОЙ ВЫПРЯМИТЕЛЬ 16.2.3. МОСТОВОЙ ВЫПРЯМИТЕЛЬ ДЛЯ ДВУХ СИММЕТРИЧНЫХ ОТНОСИТЕЛЬНО ЗЕМЛИ ВЫХОДНЫХ НАПРЯЖЕНИЙ 16.3. ПОСЛЕДОВАТЕЛЬНАЯ СТАБИЛИЗАЦИЯ НАПРЯЖЕНИЯ 16.  3.2. СХЕМА С РЕГУЛИРУЮЩИМ УСИЛИТЕЛЕМ 3.2. СХЕМА С РЕГУЛИРУЮЩИМ УСИЛИТЕЛЕМ16.3.3. ИНТЕГРАЛЬНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ 16.3.4. СТАБИЛИЗАТОР С МАЛЫМ НАПРЯЖЕНИЕМ ПОТЕРЬ 16.3.5. СТАБИЛИЗАЦИЯ НАПРЯЖЕНИЙ, СИММЕТРИЧНЫХ ОТНОСИТЕЛЬНО ЗЕМЛИ 16.3.6. СТАБИЛИЗАТОР НАПРЯЖЕНИЯ С ИЗМЕРИТЕЛЬНЫМИ ВЫВОДАМИ 16.3.7. ЛАБОРАТОРНЫЕ ИСТОЧНИКИ ПИТАНИЯ 16.3.8. ОКОНЕЧНЫЙ КАСКАД ЛАБОРАТОРНОГО ИСТОЧНИКА ПИТАНИЯ С БОЛЬШОЙ ВЫХОДНОЙ МОЩНОСТЬЮ 16.4. ПОЛУЧЕНИЕ ОПОРНОГО НАПРЯЖЕНИЯ 16.4.2. ПОЛУЧЕНИЕ МАЛЫХ ОПОРНЫХ НАПРЯЖЕНИЙ 16.5. ИМПУЛЬСНЫЕ РЕГУЛЯТОРЫ НАПРЯЖЕНИЯ 16.5.2. ПЕРВИЧНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ 17. Аналоговые коммутаторы и компараторы 17.2. ЭЛЕКТРОННЫЕ КОММУТАТОРЫ 17.2.2. ДИОДНЫЙ КОММУТАТОР 17.2.3. КОММУТАТОР НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ 17.3. АНАЛОГОВЫЕ КОММУТАТОРЫ НА БАЗЕ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 17.3.2. КОММУТАТОР НА ПОЛЕВОМ ТРАНЗИСТОРЕ С ПЕРЕМЕНОЙ ЗНАКА ВЫХОДНОГО НАПРЯЖЕНИЯ 17.3.3. КОММУТАТОР НА БАЗЕ ДИФФЕРЕНЦИАЛЬНОГО УСИЛИТЕЛЯ 17.4. АНАЛОГОВЫЕ КОММУТАТОРЫ С ПАМЯТЬЮ 17.5. КОМПАРАТОРЫ 17.  5.2. КОМПАРАТОР С ПРЕЦИЗИОННЫМ ВЫХОДНЫМ НАПРЯЖЕНИЕМ 5.2. КОМПАРАТОР С ПРЕЦИЗИОННЫМ ВЫХОДНЫМ НАПРЯЖЕНИЕМ17.5.3. ДВУХПОРОГОВЫЙ КОМПАРАТОР 17.6. ТРИГГЕР ШМИТТА 17.6.1. ИНВЕРТИРУЮЩИЙ ТРИГГЕР ШМИТТА 17.6.2. НЕИНВЕРТИРУЮЩИЙ ТРИГГЕР ШМИТТА 17.6.3. ПРЕЦИЗИОННЫЙ ТРИГГЕР ШМИТТА 18. Генераторы сигналов 18.1. LC-ГЕНЕРАТОРЫ 18.1.2. ГЕНЕРАТОР С ТРАНСФОРМАТОРНОЙ СВЯЗЬЮ (СХЕМА МАЙССНЕРА) 18.1.3. ТРЕХТОЧЕЧНАЯ СХЕМА С ИНДУKТИВНОЙ ОБРАТНОЙ СВЯЗЬЮ (СХЕМА ХАРТЛИ) 18.1.4. ТРЕХТОЧЕЧНАЯ СХЕМА С ЕМКОСТНОЙ ОБРАТНОЙ СВЯЗЬЮ (СХЕМА КОЛПИТЦА) 18.1.5. LC-ГЕНЕРАТОР С ЭМИТТЕРНОЙ СВЯЗЬЮ 18.1.6. ДВУХТАКТНЫЕ ГЕНЕРАТОРЫ 18.2. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ 18.2.1. ЭЛЕКТРИЧЕСКИЕ СВОЙСТВА КВАРЦЕВОГО РЕЗОНАТОРА 18.2.2. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ С LC-КОЛЕБАТЕЛЬНЫМ КОНТУРОМ 18.2.3. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ БЕЗ LC-КОНТУРА 18.3. СИНУСОИДАЛЬНЫЕ RC-ГЕНЕРАТОРЫ 18.3.2. МОДЕЛИРОВАНИЕ ДИФФЕРЕНЦИАЛЬНОГО УРАВНЕНИЯ СИНУСОИДАЛЬНЫХ КОЛЕБАНИЙ 18.4. ГЕНЕРАТОРЫ СИГНАЛОВ СПЕЦИАЛЬНОЙ ФОРМЫ (ФУНКЦИОНАЛЬНЫЕ ГЕНЕРАТОРЫ) 18.4.2. ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР С УПРАВЛЯЕМОЙ ЧАСТОТОЙ ВЫХОДНОГО СИГНАЛА 18.  4.3. ВЫСОКОЧАСТОТНЫЙ ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР 4.3. ВЫСОКОЧАСТОТНЫЙ ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР18.5. МУЛЬТИВИБРАТОРЫ 18.5.1. НИЗКОЧАСТОТНЫЕ МУЛЬТИВИБРАТОРЫ 18.5.2. ВЫСОКОЧАСТОТНЫЕ МУЛЬТИВИБРАТОРЫ 19. Комбинационные логические схемы 19.1. ПРЕОБРАЗОВАТЕЛИ КОДОВ 19.1.2. ДВОИЧНО-ДЕСЯТИЧНЫЕ КОДЫ 19.1.3. КОД ГРЕЯ 19.2. МУЛЬТИПЛЕКСОР И ДЕМУЛЬТИПЛЕКСОР 19.3. КОМБИНАЦИОННОЕ УСТРОЙСТВО СДВИГА 19.4. КОМПАРАТОРЫ 19.5. СУММАТОРЫ 19.5.1. ПОЛУСУММАТОР 19.5.2. ПОЛНЫЙ СУММАТОР 19.5.3. СУММАТОРЫ С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ 19.5.4. СЛОЖЕНИЕ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ 19.5.5. ВЫЧИТАНИЕ 19.5.6. СЛОЖЕНИЕ ЧИСЕЛ С ЛЮБЫМИ ЗНАКАМИ 19.6. УМНОЖИТЕЛИ 19.7. ЦИФРОВЫЕ ФУНКЦИОНАЛЬНЫЕ ПРЕОБРАЗОВАТЕЛИ 20. Интегральные схемы со структурами последовательностного типа 20.1. ДВОИЧНЫЕ СЧЕТЧИКИ 20.1.1. АСИНХРОННЫЙ (ПОСЛЕДОВАТЕЛЬНЫЙ) СЧЕТЧИК 20.1.2. СИНХРОННЫЙ (ПАРАЛЛЕЛЬНЫЙ) СЧЕТЧИК 20.2. ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК В КОДЕ 8421 20.2.1. АСИНХРОННЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК 20.2.  2. СИНХРОННЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК 2. СИНХРОННЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК20.3. СЧЕТЧИК С ПРЕДВАРИТЕЛЬНОЙ УСТАНОВКОЙ 20.4. РЕГИСТРЫ СДВИГА 20.4.2. КОЛЬЦЕВОЙ РЕГИСТР 20.4.3. РЕГИСТР СДВИГА С ПАРАЛЛЕЛЬНЫМ ВВОДОМ 20.4.4. РЕГИСТР СДВИГА С ПЕРЕКЛЮЧАЕМЫМ НАПРАВЛЕНИЕМ СДВИГА 20.5. ПОЛУЧЕНИЕ ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ 20.6. ПЕРВОНАЧАЛЬНАЯ ОБРАБОТКА АСИНХРОННОГО СИГНАЛА 20.6.2. СИНХРОНИЗАЦИЯ ИМПУЛЬСОВ 20.6.3. СИНХРОННЫЙ ОДНОВИБРАТОР 20.6.4. СИНХРОННЫЙ ДЕТЕКТОР ИЗМЕНЕНИЙ 20.6.5. СИНХРОННЫЙ ТАКТОВЫЙ ПЕРЕКЛЮЧАТЕЛЬ 20.7. СИСТЕМАТИЧЕСКИЙ СИНТЕЗ ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМ 20.7.2. ПРИМЕР СИНТЕЗА ПЕРЕКЛЮЧАЕМОГО СЧЕТЧИКА 20.7.3. СОКРАЩЕНИЕ ЕМКОСТИ ПАМЯТИ 21. Микро-ЭВМ 21.1. ОСНОВНАЯ СТРУКТУРА МИКРО-ЭВМ 21.2. ПРИНЦИП ДЕЙСТВИЯ МИКРОПРОЦЕССОРА 21.3. НАБОР КОМАНД 21.4. ОТЛАДОЧНЫЕ СРЕДСТВА 21.5. ОБЗОР МИКРОПРОЦЕССОРОВ РАЗЛИЧНОГО ТИПА 21.6. МОДУЛЬНОЕ ПОСТРОЕНИЕ МИКРО-ЭВМ 21.7. ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА 21.7.1. ПАРАЛЛЕЛЬНЫЙ ИНТЕРФЕЙС 21.7.2. ПОСЛЕДОВАТЕЛЬНЫЙ ИНТЕРФЕЙС 21.  7.3. ИНТЕРФЕЙС МАГИСТРАЛИ «ОБЩАЯ ШИНА» 7.3. ИНТЕРФЕЙС МАГИСТРАЛИ «ОБЩАЯ ШИНА»21.7.4. ПРОГРАММИРУЕМЫЙ СЧЕТЧИК 21.7.5. ПОДКЛЮЧЕНИЕ ПЕРИФЕРИЙНЫХ МОДУЛЕЙ СЕМЕЙСТВА 8080 К МАГИСТРАЛЯМ СЕМЕЙСТВА 6800 21.7.6. ОБЗОР ПЕРИФЕРИЙНЫХ УСТРОЙСТВ 21.8. МИНИМАЛЬНЫЕ СИСТЕМЫ 21.8.2. ОДНОКРИСТАЛЬНАЯ МИКРО-ЭВМ 22. Цифровые фильтры 22.1. ТЕОРЕМА О ДИСКРЕТИЗАЦИИ (ТЕОРЕМА О ВЫБОРКАХ) 22.1.2. ПРАКТИЧЕСКИЕ СООБРАЖЕНИЯ 22.2. ЦИФРОВАЯ ФУНКЦИЯ ПЕРЕДАЧИ ФИЛЬТРА 22.3. БИЛИНЕЙНОЕ ПРЕОБРАЗОВАНИЕ 22.4. РЕАЛИЗАЦИЯ ЦИФРОВЫХ ФИЛЬТРОВ 22.4.2. СТРУКТУРА ЦИФРОВЫХ ФИЛЬТРОВ ВТОРОГО ПОРЯДКА 22.4.3. ПРАКТИЧЕСКИЕ СООБРАЖЕНИЯ 23. Передача данных и индикация 23.1. СОЕДИНИТЕЛЬНЫЕ ЛИНИИ 23.2. ЗАЩИТА ДАННЫХ 23.2.2. КОД ХЕММИНГА 23.3. СТАТИЧЕСКИЕ ЦИФРОВЫЕ ИНДИКАТОРЫ 23.3.1. ДВОИЧНЫЕ ИНДИКАТОРЫ НА СВЕТОДИОДАХ 23.3.2. ДЕКАДНЫЕ ИНДИКАТОРЫ 23.3.3. ИНДИКАЦИЯ В ШЕСТНАДЦАТЕРИЧНОМ КОДЕ 23.4. МУЛЬТИПЛЕКСНЫЕ ИНДИКАТОРЫ 23.4.1. МНОГОРАЗРЯДНЫЕ 7-СЕГМЕНТНЫЕ ИНДИКАТОРЫ 23.4.2. МАТРИЦА ТОЧЕК 24.  Цифро-аналоговые и аналого-цифровые преобразователи Цифро-аналоговые и аналого-цифровые преобразователи24.1. СХЕМОТЕХНИЧЕСКИЕ ПРИНЦИПЫ ЦА-ПРЕОБРАЗОВАТЕЛЕЙ 24.1.2. ЦА-ПРЕОБРАЗОВАТЕЛЬ С ПЕРЕКИДНЫМИ КЛЮЧАМИ 24.1.3. РЕЗИСТИВНАЯ МАТРИЦА ПОСТОЯННОГО ИМПЕДАНСА (МАТРИЦА ТИПА R-2R) 24.1.4. РЕЗИСТИВНАЯ МАТРИЦА ДЛЯ ДЕКАДНЫХ ПРЕОБРАЗОВАТЕЛЕЙ 24.2. ПОСТРОЕНИЕ ЦА-ПРЕОБРАЗОВАТЕЛЕЙ С ЭЛЕКТРОННЫМИ КЛЮЧАМИ 24.2.2. ЦА-ПРЕОБРАЗОВАТЕЛЬ С ТОКОВЫМИ КЛЮЧАМИ 24.3. ЦА-ПРЕОБРАЮВАТЕЛИ ДЛЯ СПЕЦИАЛЬНЫХ ПРИМЕНЕНИЙ 24.3.2. ЦА-ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ДЕЛЕНИЯ 24.3.3. ЦА-ПРЕОБРАЗОВАТЕЛЬ КАК ГЕНЕРАТОР ФУНКЦИЙ 24.4. ОСНОВНЫЕ ПРИНЦИПЫ АЦ-ПРЕОБРАЗОВАНИЯ 24.5. ТОЧНОСТЬ АЦ-ПРЕОБРАЗОВАТЕЛЕЙ 24.6. ПОСТРОЕНИЕ АЦ-ПРЕОБРАЗОВАТЕЛЕЙ 25. Измерительные схемы 25.1. ИЗМЕРЕНИЕ НАПРЯЖЕНИЙ 25.1.2. ИЗМЕРЕНИЕ РАЗНОСТИ ПОТЕНЦИАЛОВ 25.1.3. ИЗОЛИРОВАННЫЙ УСИЛИТЕЛЬ 25.2. ИЗМЕРЕНИЕ ТОКА 25.2.1. ИЗОЛИРОВАННЫЕ ОТ ЗЕМЛИ АМПЕРМЕТРЫ С МАЛЫМ ПАДЕНИЕМ НАПРЯЖЕНИЯ 25.2.2. ИЗМЕРЕНИЕ ТОКА ПРИ ВЫСОКОМ ПОТЕНЦИАЛЕ 25.3. ИЗМЕРИТЕЛЬНЫЙ ВЫПРЯМИТЕЛЬ 25.  3.2. ИЗМЕРЕНИЕ ЭФФЕКТИВНОГО ЗНАЧЕНИЯ 3.2. ИЗМЕРЕНИЕ ЭФФЕКТИВНОГО ЗНАЧЕНИЯ25.3.3. ИЗМЕРЕНИЕ АМПЛИТУДНЫХ ЗНАЧЕНИЙ 25.3.4. СИНХРОННЫЙ ДЕТЕКТОР 26. Электронные регуляторы 26.2. ТИПЫ РЕГУЛЯТОРОВ 26.2.1. П-РЕГУЛЯТОР 26.2.2. ПИ-РЕГУЛЯТОР 26.2.3. ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР 26.2.4. НАСТРАИВАЕМЫЕ ПИД-РЕГУЛЯТОРЫ 26.3. УПРАВЛЕНИЕ НЕЛИНЕЙНЫМИ ОБЪЕКТАМИ 26.4. ОТСЛЕЖИВАЮЩАЯ СИНХРОНИЗАЦИЯ (АВТОПОДСТРОЙКА) 26.4.1. ЭЛЕМЕНТЫ ВЫБОРКИ-ХРАНЕНИЯ В КАЧЕСТВЕ ФАЗОВОГО ДЕТЕКТОРА 26.4.2. СИНХРОННЫЙ ВЫПРЯМИТЕЛЬ В КАЧЕСТВЕ ФАЗОВОГО ДЕТЕКТОРА 26.4.3. ЧАСТОТНО-ЧУВСТВИТЕЛЬНЫЙ ФАЗОВЫЙ ДЕТЕКТОР 26.4.4. ФАЗОВЫЙ ДЕТЕКТОР С ПРОИЗВОЛЬНО УВЕЛИЧИВАЕМЫМ ДИАПАЗОНОМ ИЗМЕРЕНИЙ 26.4.5. ФАЗОРЕГУЛЯТОР В КАЧЕСТВЕ ПЕРЕМНОЖИТЕЛЯ ЧАСТОТ |

FET — часть 2

» Перейти к дополнительным материалам

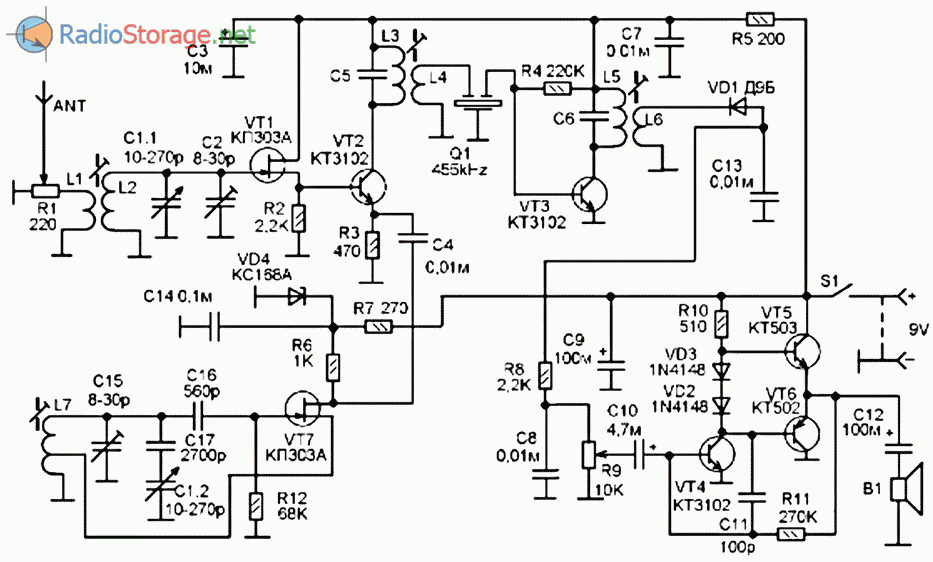

В первом выпуске прошлого месяца объяснялись (среди прочего) основные принципы работы JFET. JFET представляют собой маломощные устройства с очень высоким входным сопротивлением и неизменно работают в режиме истощения, т. Е. Они пропускают максимальный ток, когда смещение затвора равно нулю, и ток уменьшается («истощается») за счет обратного смещения клеммы затвора. .

JFET представляют собой маломощные устройства с очень высоким входным сопротивлением и неизменно работают в режиме истощения, т. Е. Они пропускают максимальный ток, когда смещение затвора равно нулю, и ток уменьшается («истощается») за счет обратного смещения клеммы затвора. .

| РИСУНОК 1. Схема и соединения полевых транзисторов 2N3819 и MPF102. | ||

| Параметр | 2N3918 | MPF102 |

| В DS макс. (= макс. напряжение сток-исток) | 25В | 25В |

| В DG макс. (= макс. напряжение сток-затвор) | 25В | 25В |

| В GS макс. (= макс. напряжение затвор-исток) | 25В | 25В |

| I DSS (= ток сток-исток при V GS = 0 В) | 2-20 мА | 2-20 мА |

I GSS макс. (= ток утечки затвора при 25°C) (= ток утечки затвора при 25°C) | 2 нА | 2 нА |

| P T max (= макс. рассеиваемая мощность, на открытом воздухе) | 200 мВт | 310 мВт |

| Рис. 2. Основные характеристики n-канальных полевых транзисторов 2N3819 и MPF102. | ||

Большинство JFET являются n-канальными (а не p-канальными) устройствами. Двумя старейшими и наиболее известными n-канальными полевыми транзисторами являются 2N3819 и MPF102, которые обычно размещаются в пластиковых корпусах TO92 с соединениями, показанными на рис. 1 ; На рис. 2 перечислены основные характеристики этих двух устройств.

В статье этого месяца рассматривается основная информация об использовании и применении JFET. Все практические схемы, показанные здесь, специально разработаны для 2N3819., но будет одинаково хорошо работать при использовании MPF102.

JFET BIASING

JFET может использоваться в качестве линейного усилителя путем обратного смещения его затвора относительно вывода истока, таким образом переводя его в линейную область. Обычно используются три основных метода смещения JFET. Простейшей из них является система с «самосмещением», показанная на рис.

Обычно используются три основных метода смещения JFET. Простейшей из них является система с «самосмещением», показанная на рис.

| РИСУНОК 3. Базовая система JFET с «самосмещением». |

Предположим, что требуется ток I D , равный 1 мА, и что для установки этого условия требуется смещение V GS , равное -2 В2; правильное смещение, очевидно, можно получить, задав Rs значение 2k2; если I D по какой-либо причине имеет тенденцию к уменьшению, то V GS , естественно, также падает и, таким образом, заставляет I D увеличиваться и противодействовать первоначальному изменению; таким образом, смещение саморегулируется посредством отрицательной обратной связи.

На практике значение V GS , необходимое для установки заданного значения I D , сильно различается между отдельными JFETS, и единственный надежный способ получить точное значение I D в этой системе — сделать Rs переменным резистором. ; однако эта система достаточно точна для многих приложений и является наиболее широко используемым из трех методов смещения.

; однако эта система достаточно точна для многих приложений и является наиболее широко используемым из трех методов смещения.

| РИСУНОК 4. Базовая система JFET со смещением смещения. |

Более точным способом смещения JFET является система «смещения» Рис. 4(a) , в которой делитель R1-R2 подает фиксированное положительное смещение на затвор через Rg, а напряжение источника это напряжение минус В GS . Если напряжение затвора велико по сравнению с V GS , I D устанавливается в основном Rs и не сильно зависит от изменений V GS . Таким образом, эта система позволяет устанавливать значения I D с хорошей точностью и без необходимости выбора отдельных компонентов. Подобные результаты можно получить, заземлив затвор и подведя низ Rs к большому отрицательному напряжению, как в Рисунок 4(b) .

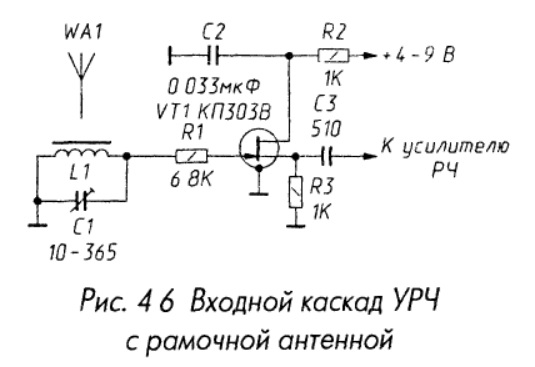

Третий тип системы смещения показан на рис. 5 , в котором генератор постоянного тока Q2 устанавливает I D , независимо от характеристик JFET. Эта система обеспечивает превосходную стабильность смещения, но за счет увеличения сложности и стоимости схемы.

В трех описанных системах смещения Rg может иметь любое значение вплоть до 10M, причем верхний предел определяется падением напряжения на Rg, вызванным токами утечки затвора, которые могут нарушить смещение затвора.

| РИСУНОК 5. Базовая система смещения постоянного тока на JFET. | РИСУНОК 6. Истоковый повторитель с автоматическим смещением. Зин = 10М. | РИСУНОК 7. Истоковый повторитель со смещенным смещением. Зин = 44М. |

ЦЕПИ ИСТОЧКОВОГО ПОВТОРИТЕЛЯ

При использовании в качестве линейных усилителей JFET обычно используются либо в режиме истокового повторителя (общий сток), либо в режиме с общим истоком. Истоковый повторитель обеспечивает очень высокий входной импеданс и коэффициент усиления по напряжению, близкий к единице (отсюда и альтернативное название «повторитель напряжения»).

Истоковый повторитель обеспечивает очень высокий входной импеданс и коэффициент усиления по напряжению, близкий к единице (отсюда и альтернативное название «повторитель напряжения»).

На рис. 6 показан простой истоковой повторитель с автосмещением (через RV1); RV1 используется для установки падения напряжения R2 в состоянии покоя 5V6. Фактический коэффициент усиления входного/выходного напряжения схемы составляет 0,95. К резистору R3 применяется некоторая степень самонастройки, что увеличивает его эффективное сопротивление; фактический входной импеданс схемы составляет 10 МОм, шунтированный на 10 пФ, т. е. он равен 10 МОм на очень низких частотах, падает до 1 МОм примерно на 16 кГц и 100 кОм на 160 кГц и т. д.

На рис. Общий коэффициент усиления по напряжению составляет около 0,95. Конденсатор C2 является пусковым конденсатором и увеличивает входное сопротивление до 44 МОм, шунтированное на 10 пФ.

РИСУНОК 8. Гибридный истоковый повторитель. Зин = 500М. Гибридный истоковый повторитель. Зин = 500М. |

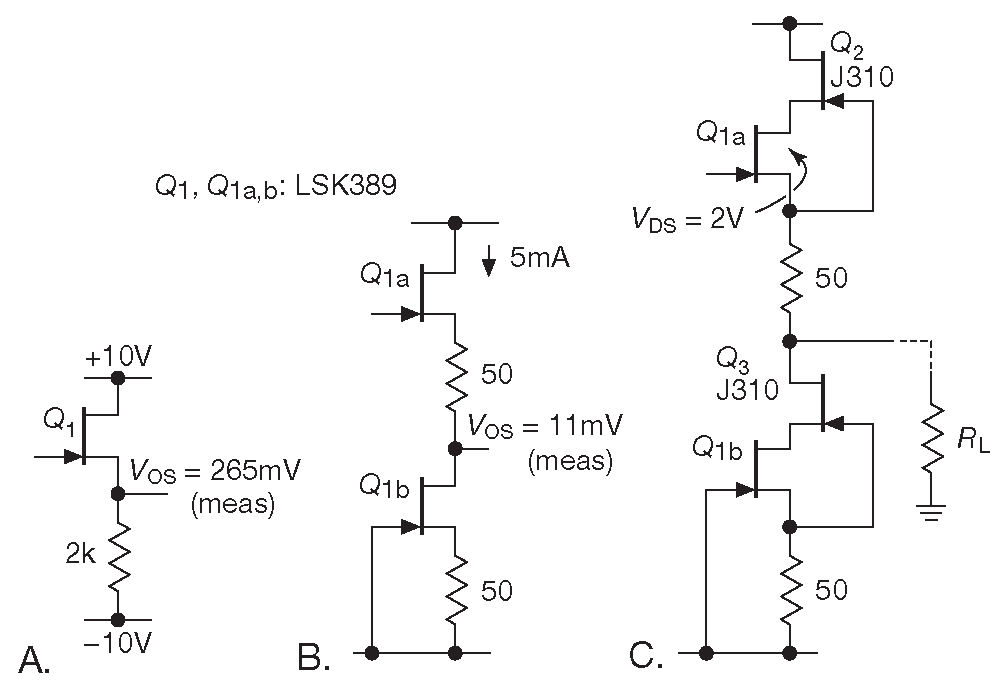

На рис. 8 показан гибридный (JFET плюс биполярный) истоковый повторитель. Смещение смещения применяется через резисторы R1-R2, а генератор постоянного тока Q2 действует как источник нагрузки с очень высоким импедансом, что дает схеме общий коэффициент усиления по напряжению 0,99. C2 увеличивает эффективный импеданс R3 до 1000 МОм, который шунтируется импедансом затвора JFET; входное сопротивление всей цепи 500 МОм, шунтированное 10 пФ.

Обратите внимание, что если необходимо поддерживать высокое эффективное значение входного импеданса этой цепи, выход должен быть либо подключен к внешним нагрузкам через дополнительный каскад эмиттерного повторителя (как показано пунктиром на схеме), либо должен быть подключен только к достаточному высокоимпедансные нагрузки.

УСИЛИТЕЛИ С ОБЩИМ ИСТОЧНИКОМ

На рис. 9 показан простой усилитель с общим истоком с автоматическим смещением; RV1 используется для установки покоя 5V6 на R3. Сеть смещения RV1-R2 развязана по переменному току через C2, и схема дает усиление по напряжению 21 дБ (= x12) и имеет частотную характеристику ± 3 дБ, которая охватывает диапазон от 15 Гц до 250 кГц, и входное сопротивление 2 МОм2, шунтированное 50 пФ. (Это высокое значение шунта связано с обратной связью Миллера, которая умножает эффективную емкость затвор-сток полевого транзистора на значение x12 Av схемы.)

Сеть смещения RV1-R2 развязана по переменному току через C2, и схема дает усиление по напряжению 21 дБ (= x12) и имеет частотную характеристику ± 3 дБ, которая охватывает диапазон от 15 Гц до 250 кГц, и входное сопротивление 2 МОм2, шунтированное 50 пФ. (Это высокое значение шунта связано с обратной связью Миллера, которая умножает эффективную емкость затвор-сток полевого транзистора на значение x12 Av схемы.)

| РИСУНОК 9. Простой усилитель с общим истоком и самосмещением. | РИСУНОК 10. Простой усилитель для наушников. |

На рис. 10 показан простой усилитель для наушников с автоматическим смещением, который можно использовать с импедансом наушников 1 кОм или выше. Он имеет встроенный регулятор громкости (RV1), имеет входное сопротивление 2 МОм и может использовать любой источник питания в диапазоне от 9 до 18 В.

| РИСУНОК 11. Дополнительный предварительный усилитель общего назначения. | РИСУНОК 12. Усилитель с общим истоком со смещенным затвором. |

| РИСУНОК 13. «Гибридный» усилитель с общим истоком. |

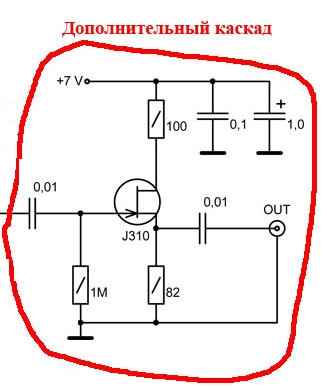

На рис. 11 показан дополнительный предварительный усилитель с автоматическим смещением, обеспечивающий коэффициент усиления по напряжению более 20 дБ, полосу пропускания, превышающую 100 кГц, и входное сопротивление 2 МОм2. Его можно использовать с любым усилителем, который может обеспечить 9Источник питания от В до 18В.

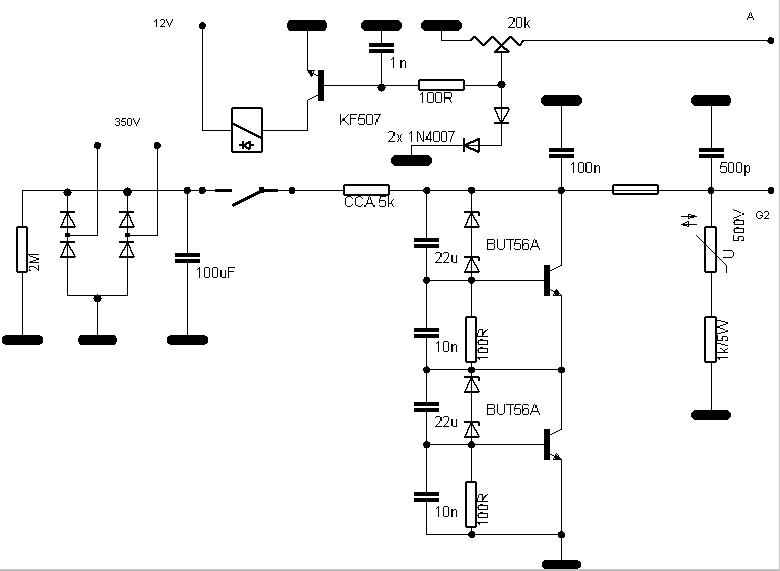

Усилители с общим истоком на полевых транзисторах JFET могут — когда требуется очень высокая точность смещения — быть спроектированы с использованием метода смещения «смещения» или «постоянного тока». На рисунках 12 и 13 показаны схемы этих типов. Обратите внимание, что «офсетная» схема , рис. 1, 2, может использоваться только с источниками питания в диапазоне от 16 В до 20 В, а гибридная схема , рис. 13, , может использоваться с любым источником питания в диапазоне от 12 до 20 В. Обе схемы обеспечивают усиление по напряжению 21 дБ, полосу частот ±3 дБ от 15 Гц до 250 кГц и входное сопротивление 2 МОм2.

На рисунках 12 и 13 показаны схемы этих типов. Обратите внимание, что «офсетная» схема , рис. 1, 2, может использоваться только с источниками питания в диапазоне от 16 В до 20 В, а гибридная схема , рис. 13, , может использоваться с любым источником питания в диапазоне от 12 до 20 В. Обе схемы обеспечивают усиление по напряжению 21 дБ, полосу частот ±3 дБ от 15 Гц до 250 кГц и входное сопротивление 2 МОм2.

ВОЛЬТМЕТРЫ ПОСТОЯННОГО ТОКА

На рис. 14 показан полевой транзистор JFET, используемый для создания очень простого трехдиапазонного вольтметра постоянного тока с максимальной чувствительностью FSD 0,5 В и входным сопротивлением 11 МОм. Здесь R6-RV2 и R7 образуют делитель напряжения на источнике питания 12 В и, если соединение R7-RV2 используется в качестве точки нулевого напряжения цепи, устанавливает верхнюю часть R6 на +8 В, а нижнюю часть R7 на -4 В. Q1 используется в качестве истокового повторителя, его затвор заземлен через сеть R1-R4, и смещено смещением за счет подключения его истока к -4 В через R5; он потребляет около 1 мА тока стока.

| РИСУНОК 14. Простой трехдиапазонный вольтметр постоянного тока. |

В Рис. 14 , R6-RV2 и Q1-R5 действуют как сеть моста Уитстона, а RV2 настроен так, чтобы мост был сбалансирован и в счетчике протекал нулевой ток при отсутствии входного напряжения на Q1 ворота. Любое напряжение, подаваемое на затвор Q1, выводит мост из баланса на пропорциональную величину, которая может быть считана непосредственно на измерителе.

R1-R3 образуют сеть множителя диапазона, которая — при правильной настройке RV1 — дает диапазоны FSD 0,5 В, 5 В и 50 В. R4 защищает затвор Q1 от повреждения, если на схему подается избыточное входное напряжение.

Чтобы использовать схему Рисунок 14 , сначала подстройте RV2, чтобы получить нулевое показание счетчика при отсутствии входного напряжения, а затем подключите ко входу точное напряжение 0,5 В постоянного тока и подстройте RV1, чтобы получить точное полное показание счетчика. . Повторяйте эти регулировки до тех пор, пока не будут получены согласованные показания нуля и полной шкалы; после этого устройство готово к использованию.

. Повторяйте эти регулировки до тех пор, пока не будут получены согласованные показания нуля и полной шкалы; после этого устройство готово к использованию.

| РИСУНОК 15. Трехдиапазонный вольтметр постоянного тока с малым дрейфом. |

На практике эта очень простая схема имеет тенденцию к дрейфу при изменении напряжения питания и температуры, и требуется довольно частая подстройка нуля. Дрейф можно значительно уменьшить, используя стабилизированный стабилитроном источник питания 12 В.

На рис. 15 показана улучшенная версия вольтметра JFET с малым дрейфом. Q1 и Q2 подключены как дифференциальный усилитель, поэтому любой дрейф, возникающий на одной стороне цепи, автоматически противодействует аналогичному дрейфу на другой стороне, и достигается хорошая стабильность. В схеме используется принцип «моста», где Q1-R5 образуют одну сторону моста, а Q2-R6 — другую. Q1 и Q2 в идеале должны быть согласованной парой JFET со значениями IDSS, совпадающими в пределах 10%. Схема устроена так же, как и у 9.0019 Рисунок 14 .

Q1 и Q2 в идеале должны быть согласованной парой JFET со значениями IDSS, совпадающими в пределах 10%. Схема устроена так же, как и у 9.0019 Рисунок 14 .

РАЗНЫЕ ЦЕПИ JFET

| РИСУНОК 16. Нестабильный мультивибратор VLF. |

| РИСУНОК 17. Усилитель/аттенюатор, управляемый напряжением. |

В заключение статьи этого месяца, На рисунках с 16 по 19 показан разнообразный набор полезных схем JFET. Модель Рисунок 16 представляет собой очень низкочастотный (VLF) нестабильный или автономный мультивибратор; его периоды включения и выключения контролируются C1-R4 и C2-R3, а R3 и R4 могут иметь значения до 10M.

При показанных значениях схема работает со скоростью один раз в 20 секунд, т. е. с частотой 0,05 Гц; кнопку запуска S1 необходимо удерживать в закрытом положении не менее одной секунды, чтобы инициировать нестабильное действие.

На рис. 17 в базовой форме показано, как можно использовать JFET и операционный усилитель 741 для создания усилителя/аттенюатора, управляемого напряжением. Операционный усилитель используется в инвертирующем режиме, коэффициент усиления по напряжению задается соотношением R2/R3, а резистор R1 и JFET используются в качестве входного аттенюатора, управляемого напряжением.

Когда на затвор Q1 подается большое отрицательное управляющее напряжение, JFET действует как почти бесконечное сопротивление и вызывает нулевое затухание сигнала, поэтому схема дает высокий общий коэффициент усиления, но когда смещение затвора равно нулю, FET действует как низкое сопротивление и вызывает сильное затухание сигнала, поэтому схема дает общую потерю сигнала.

Промежуточные значения затухания сигнала и общего усиления или ослабления можно получить, изменяя значение управляющего напряжения.

РИСУНОК 18. Усилитель постоянной громкости. Усилитель постоянной громкости. |

На рис. 18 показано, как этот метод аттенюатора, управляемого напряжением, можно использовать для создания усилителя «постоянной громкости», который обеспечивает изменение уровня выходного сигнала всего на 7,5 дБ при изменении уровня входного сигнала в диапазоне 40 дБ ( от 3 мВ до 300 мВ RMS).

Схема может принимать входные сигналы с уровнями среднеквадратичного значения до 500 мВ. Q1 и R4 соединены последовательно, образуя управляемый напряжением аттенюатор, который регулирует уровень входного сигнала для усилителя с общим эмиттером Q2, выход которого буферизуется через эмиттерный повторитель. Q3.

Выход Q3 используется для генерирования (через C5-R9-D1-D2-C4-R5) управляющего напряжения постоянного тока, которое подается обратно на затвор Q1, образуя, таким образом, контур отрицательной обратной связи по постоянному току, который автоматически регулирует общий коэффициент усиления по напряжению, чтобы что уровень выходного сигнала имеет тенденцию оставаться постоянным при изменении уровня входного сигнала следующим образом.

Когда на схему подается очень слабый входной сигнал, выходной сигнал Q3 также мал, поэтому на затвор Q1 подается незначительное управляющее напряжение постоянного тока; Таким образом, Q1 действует как низкоомное сопротивление в этих условиях, так что почти весь входной сигнал подается на базу Q2, и схема дает высокий общий коэффициент усиления.

Когда на схему подается большой входной сигнал, выходной сигнал Q3 имеет тенденцию быть большим, поэтому на затвор Q1 подается большое отрицательное управляющее напряжение постоянного тока; Таким образом, Q1 действует как высокое сопротивление в этих условиях, поэтому только небольшая часть входного сигнала подается на базу Q2, и схема дает низкий общий коэффициент усиления.

Таким образом, выходной уровень остается практически постоянным в широком диапазоне уровней входного сигнала; эта характеристика полезна в кассетных магнитофонах, переговорных устройствах, телефонных усилителях и т. д.

РИСУНОК 19. Преобразователь постоянного тока в переменный или схема прерывателя. Преобразователь постоянного тока в переменный или схема прерывателя. |

Наконец, На рис. 19 показан JFET, используемый для создания преобразователя постоянного тока в переменный или «прерывателя», который создает прямоугольный выходной сигнал с пиковой амплитудой, равной амплитуде входного напряжения постоянного тока.

В этом случае Q1 действует как электронный переключатель, который подключен последовательно с R1 и включается и выключается с частотой 1 кГц через нестабильную цепь Q2-Q3, таким образом обеспечивая преобразование постоянного тока в переменный. Обратите внимание, что амплитуда сигнала управления затвором Q1 может изменяться с помощью RV1; если используется слишком большой привод, переход затвор-исток Q1 начинает лавинообразно работать, вызывая небольшой скачок напряжения, пробивающийся через сток и дающий выходной сигнал даже при отсутствии входа постоянного тока.

Чтобы предотвратить это, подключите вход постоянного тока, а затем подстройте RV1, пока выход не станет на грани уменьшения; однажды настроенная таким образом, схема может быть надежно использована для прерывания напряжения до доли милливольта. NV

NV

Другие детали из серии «Принципы и схемы полевых транзисторов» — выходит еженедельно

Полевые транзисторы (FET) — основы. (Часть 1 из 4)

Практические схемы JFET. (Часть 2 из 4)

Практические схемы MOSFET и CMOS. (часть 3 из 4)

13.3: MOSFET Повторители с общим стоком

- Последнее обновление

- Сохранить как PDF

- Идентификатор страницы

- 25335

- Джеймс М. Фиоре

- Муниципальный колледж Mohawk Valley

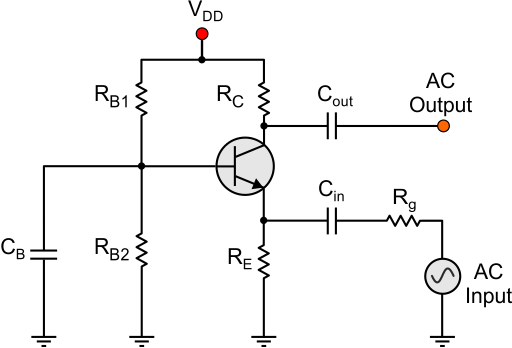

Как обсуждалось в разделе, посвященном JFET, усилитель с общим стоком также известен как истоковый повторитель. Схема усилителя-прототипа с моделью устройства показана на рисунке \(\PageIndex{1}\). Как и во всех повторителях напряжения, мы ожидаем коэффициента усиления неинвертирующего напряжения, близкого к единице, с высоким \(Z_{in}\) и низким \(Z_{out}\).

Схема усилителя-прототипа с моделью устройства показана на рисунке \(\PageIndex{1}\). Как и во всех повторителях напряжения, мы ожидаем коэффициента усиления неинвертирующего напряжения, близкого к единице, с высоким \(Z_{in}\) и низким \(Z_{out}\).

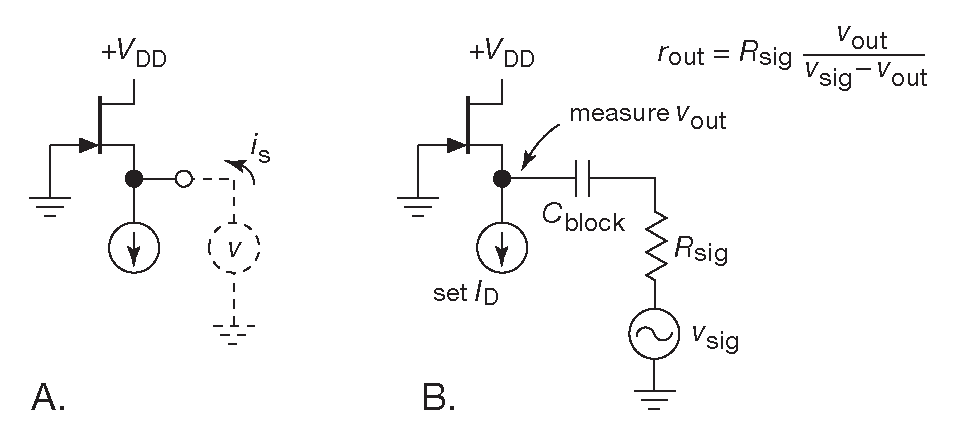

Рисунок \(\PageIndex{1}\): Прототип общего стока (исходного повторителя).

Как обычно, входной сигнал подается на клемму затвора, а выходной сигнал берется из источника. Поскольку выход находится в источнике, нельзя использовать схемы смещения, в которых клемма источника заземлена, например, нулевое смещение и смещение делителя напряжения.

13.3.1: Коэффициент усиления по напряжению

Уравнение усиления по напряжению для повторителя с общим стоком составляется следующим образом: }\), и выразим эти напряжения через их эквиваленты по закону Ома. Нагрузка теперь находится в истоке MOSFET, поэтому ее можно обозначить как \(r_L\) или \(r_S\).

\[A_v = \frac{v_{out}}{v_{i n}} = \frac{v_S}{v_G} = \frac{v_L}{v_G} \\ A_v = \frac{i_D r_L}{i_D r_L+v_{GS}} \\ A_v = \frac{g_m v_{GS} r_L}{g_m v_{GS} r_L+v_{GS}} \\ A_v = \frac{g_m r_L}{g_m r_L+1} \метка{13. 5} \]

5} \]

или, если предпочтительнее,

\[A_v = \frac{g_m r_S}{g_m r_S+1} \label{13.5b} \]

Если \(g_mr_S \gg 1\), усиление по напряжению будет очень близко к единице; желаемый результат.

13.3.2: Входной импеданс

Анализ входного импеданса истокового повторителя практически идентичен анализу для усилителя с общим истоком. Тот же комментарий относится к упрощению резисторов смещения затвора, чтобы получить значение \(r_G\).

\[Z_{in} = r_G || r_{GS} \ приблизительно r_G \label{13.6} \]

13.3.3: Выходное сопротивление

Чтобы определить выходное сопротивление, мы модифицируем схему на рисунке \(\PageIndex{1}\), отделив сопротивление нагрузки от резистора смещения истока. Это показано на рисунке \(\PageIndex{2}\).

Рисунок \(\PageIndex{2}\): Анализ выходного импеданса истокового повторителя.

Оглядываясь назад на источник с точки зрения нагрузки, мы обнаруживаем, что резистор смещения источника \(R_S\) параллелен импедансу, обращенному назад к клемме источника.

\[Z_{выход} = R_S || Z_{источник} \nonumber \]

Чтобы найти \(Z_{источник}\), обратите внимание, что напряжение в источнике равно \(v_{GS}\), а ток, поступающий в этот узел, равен \(i_D\). Соотношение двух даст импеданс, если смотреть назад в источник.

\[Z_{источник} = \frac{v_{GS}}{i_D} \\ Z_{источник} = \frac{v_{GS}}{g_m v_{GS}} \\ Z_{источник} = \ frac{1}{g_m} \label{13.7} \]

Следовательно, выходное сопротивление равно

\[Z_{out} = R_S || \frac{1}{g_m} \label{13.8} \]

Глядя на уравнение \ref{13.8} становится очевидным, что чем выше крутизна, тем ниже выходной импеданс. Как отмечалось ранее, большая крутизна также означает, что коэффициент усиления по напряжению будет близок к единице. Как правило, для истокового повторителя желательна большая крутизна.

Пришло время привести несколько наглядных примеров.

Пример \(\PageIndex{1}\)

Для схемы на рисунке \(\PageIndex{3}\) определите коэффициент усиления по напряжению и входное сопротивление. Предположим, что \(V_{GS(off)}\) = -0,8 В и \(I_{DSS}\) = 30 мА.

Предположим, что \(V_{GS(off)}\) = -0,8 В и \(I_{DSS}\) = 30 мА.

Рисунок \(\PageIndex{3}\): Схема для примера \(\PageIndex{1}\).

Этот усилитель использует самосмещение, поэтому нам нужно определить \(g_{m0}R_S\).

\[g_{m0} =- \frac{2 I_{DSS}}{V_{GS (off)}} \nonumber \]

\[g_{m0} =- \frac{2 \times 30mA} {−0,8 В} \номер \]

\[g_{m0} = 75 мс \номер \]

) = 16,2. Из уравнения или графика самосмещения получается, что ток стока составляет 2,61 мА.

\[g_m = g_{m0} \sqrt{\frac{I_D}{I_{DSS}}} \nonumber \]

\[g_m = 75 мСм \sqrt{\frac{2,61 мА} {30 мА} } \nonumber \]

\[g_m = 22,1 мс \nonumber \]

Коэффициент усиления по напряжению равен

\[A_v = \frac{g_m r_S}{g_m r_S+1} \nonumber \]

\[A_v = \frac{22,1 мСм(270\Омега || 150 \Омега )}{22,1 мСм \times (270 \Омега || 150\Омега ) +1} \номер \]

\[A_v = 0,68 \неномер \]

Наконец, для входного импеданса имеем

\[Z_{in} = 1,2 МОм\Омега || Z_{in(gate)} \примерно 1,2 M\Omega \nonumber \]

Пример \(\PageIndex{2}\)

Для схемы на рисунке \(\PageIndex{4}\) определите усиление по напряжению и входное сопротивление. Предположим, что \(V_{GS(off)}\) = -2,5 В и \(I_{DSS}\) = 80 мА.

Предположим, что \(V_{GS(off)}\) = -2,5 В и \(I_{DSS}\) = 80 мА.

Рисунок \(\PageIndex{4}\): Схема для примера \(\PageIndex{2}\).

В этом повторителе используется P-канальное устройство с комбинированным смещением. Обратите внимание, что клемма источника находится вверху схемы. Сначала определите \(g_{m0}R_S\) и коэффициент смещения, \(k\). Затем можно использовать комбинированное уравнение смещения для определения тока стока.

\[g_{m0} =- \frac{2 I_{DSS}}{V_{GS (off )}} \nonumber \]

\[g_{m0} =- \frac{2 \times 80 мА }{−2,5 В} \nonumber \]

\[g_{m0} = 64 мСм \nonumber \]

} R_S\) = 115,2. Коэффициент смещения равен \(V_{SS}/V_{GS(off)}\) или 4. Комбинированное уравнение смещения (уравнение 10.9) дает \(I_D\) = 6,67 мА.

Теперь мы можем найти крутизну и коэффициент усиления по напряжению.

\[g_m = g_{m0} \sqrt{\frac{I_D}{I_{DSS}}} \nonumber \]

\[g_m = 64 мСм \sqrt{\frac{6,67 мА}{80 мА}} \nonnumber \]

\[g_m = 18,5 мСм \nonnumber \]

Коэффициент усиления по напряжению равен

\[A_v = \frac {g_m r_S}{g_m r_S+1} \nonumber \]

\[A_v = \frac{18,5 мСм(1,8k \Omega || 800\Omega )}{18,5 мСм \times (1,8 k\Omega || 800 \Omega ) +1} \nonumber \]

\[A_v = 0,91 \nonumber \]

Наконец, входное сопротивление равно

\[Z_{in} = 560 k\Omega || Z_{in(gate)} \примерно 560 k\Omega\nonumber\]

Эта страница под названием 13.

, Шенк К. Полупроводниковая схемотехника: Справочное руководство. Пер. с нем. М.: Мир, 1982. — 512 с.

, Шенк К. Полупроводниковая схемотехника: Справочное руководство. Пер. с нем. М.: Мир, 1982. — 512 с.