Микросхемы серии 130- 139 |

|||

| Тип/Серия | Аналог | Производитель аналога | Назначение |

| 130ЛА1 | SN74h30 | TI | Два логических элемента 4И-НЕ. |

| 130ЛА2 | SN74h40 | TI | Логический элемент 8И-НЕ. |

| 130ЛА3 | SN74H00 | TI | Четыре логических элемента 2И-НЕ. |

| 130ЛА4 | SN74h20 | TI | Три логических элемента 3И-НЕ. |

| 130ЛА6 | SN74h50 | TI | Два логических элемента 4И-НЕ с большим коэффициентом разветвления по выходу. |

| 130ЛА13 | . | ||

| 130ЛД1 | SN74H60 | TI | Два четырехвходовых расширителя по ИЛИ. |

| 130ЛЛ4 | . | ||

| 130ЛН1 | SN74H04 | TI | Шесть логических элементов НЕ. |

| 130ЛР1 | SN74H50 | TI | Два логических элемента 2-2И-2ИЛИ-НЕ, один расширяемый по ИЛИ. |

| 130ЛР3 | SN74H53 | TI | Логический элемент 2-2-2-3И-4ИЛИ-НЕ с возможностью расширения по ИЛИ. |

| 130ЛР4 | SN74H55 | TI | Логический элемент 4-4И-2ИЛИ-НЕ с возможностью расширения по ИЛИ. |

| 130ТВ1 | SN74H72 | TI | JK-триггер с логикой 3И на входе. |

| 130ТМ2 | SN74H74 | TI | Два D-триггера. |

| 131ЛА1 | SN74h30 | TI | Два логических элемента 4И-НЕ. |

| 131ЛА2 | SN74h40 | TI | Логический элемент 8И-НЕ. |

| 131ЛА3 | SN74H00 | TI | Четыре логических элемента 2И-НЕ. |

| 131ЛА4 | SN74h20 | TI | Три логических элемента 3И-НЕ. |

| 131ЛА6 | SN74h50 | TI | Два логических элемента 4И-НЕ с большим коэффициентом разветвления по выходу. |

| 131ЛВ3 | SN74H00 | TI | Четыре логических элемента 2И-НЕ. |

| 131ЛД1 | SN74H60 | TI | Два четырехвходовых расширителя по ИЛИ. |

| 131ЛН1 | SN74H04 | TI | Шесть логических элементов НЕ. |

| 131ЛР1 | SN74H50 | TI | Два логических элемента 2-2И-2ИЛИ-НЕ, один расширяемый по ИЛИ. |

| 131ЛР3 | SN74H53 | TI | Логический элемент 2-2-2-3И-4ИЛИ-НЕ с возможностью расширения по ИЛИ. |

| 131ЛР4 | SN74H55 | TI | Логический элемент 4-4И-2ИЛИ-НЕ с возможностью расширения по ИЛИ. |

| 131ТВ1 | SN74H72 | TI | JK-триггер с логикой 3И на входе. |

| 131ТМ2 | SN74H74 | TI | Два D-триггера. |

| 132РУ1 | 2101А-4 | INTEL | Статическое ОЗУ (1k x 1). |

| 132РУ2 | 2102А | INTEL | Статическое ОЗУ (1k х 1). |

| 132РУ3 | 2125 | INTEL | Статическое ОЗУ (1k х 1). |

| 132РУ4 | 2125AL | INTEL | Статическое ОЗУ (1k х 1). |

| 132РУ5 | 2147 | INTEL | Статическое ОЗУ (4k х 1). |

| 132РУ6 | IMS1400 | INMOS | Статическое ОЗУ (16k x1). |

| 132РУ7 | ~TMS4016 | TI | Статическое ОЗУ (2k х 8). |

| 132РУ8 | 2148Н | INTEL | Статическое ОЗУ (1k х 4). |

| 132РУ9 | 2149Н | INTEL | Статическое ОЗУ(1k х 4). |

| 132РУ10 | MB81C71-55 | FUJITSU | Статическое ОЗУ (64k x 1). |

| 132РУ11 | TMM2016P | TOSHIBA | Статическое ОЗУ (2k х 8). |

| 132РУ12 | IMS1420-55 | INMOS | Статическое ОЗУ (4k x 1). |

| 132РУ13 | TMM2016P | TOSHIBA | Статическое ОЗУ (2k х 8). |

| 132РУ14 | 2148Н | INTEL | Статическое ОЗУ (1k x 4). |

| 132РУ15 | 2149Н | INTEL | Статическое ОЗУ (1k х 4). |

| 132РУ16 | 2147Н | INTEL | Статическое ОЗУ (8k х 8). |

| 133АГ1 | SN54121 | Одновибратор с логическим элементом на входе. | |

| 133АГ3 | SN54123 | TI | Два одновибратора с повторным запуском. |

| 133ИВ1 | SN54148 | TI | Приоритетный шифратор 8 x 3. |

| 133ИE8 | SN5497 | TI | Делитель частоты с переменным коэффициентом деления. |

| 133ИД1 | SN54141 | TI | Двоично-десятичный дешифратор с высоковольтным выходом. |

| 133ИД3 | SN54154 | TI | Дешифратор-демультиплексор 4 x 16. |

| 133ИД4 | SN54155 | TI | Сдвоенный дешифратор мультиплексор 2 x 4. |

| 133ИД10 | SN54145 | TI | Двоично-десятичный дешифратор. |

| 133ИД15 | б/а | Дешифратор 3 в 8 для управления шкалой линейной красного цвета. | |

| 133ИД16 | б/а | Дешифратор для управления линейной шкалой зеленого цвета. | |

| 133ИД20 | б/а | ||

| 133ИД21 | б/а | Управление сборкой из линейных светодиодных шкал желтого и зеленого цветов свечения или знакосинтезирующих индикаторов. | |

| 133ИЕ2 | SN5490 | TI | Двоично-десятичный счетчик (4 р). |

| 133ИЕ4 | SN5492 | TI | Счетчик-делитель на 12. |

| 133ИЕ5 | SN5493 | TI | Двоичный счетчик (4 р). |

| 133ИЕ6 | TI | Синхронный реверсивный десятичный счетчик с параллельной загрузкой (4 р). | |

| 133ИЕ7 | SN54193 | TI | Синхронный реверсивный двоичный счетчик с параллельной загрузкой (4 р). |

| 133ИЕ8 | SN5497 | TI | Делитель частоты с переменным коэффициентом деления. |

| 133ИЕ9 | SN54160 | TI | 4-разрядный синхронный счетчик. |

| 133ИЕ14 | SN54196 | TI | Асинхронный десятичный счетчик (4 р). |

| 133ИМ1 | SN5480 | TI | Одноразрядный полный сумматор. |

| 133ИМ2 | SN5482 | TI | Двухразрядный двоичный сумматор. |

| 133ИМ3 | SN5483 | TI | Четырехразрядный двоичный сумматор. |

| 133ИП2 | SN54180 | TI | Восьмиразрядная схема контроля четности. |

| 133ИП3 | SN54181 | TI | Арифметическо-логическое устройство (4 р). |

| 133ИП4 | SN54182 | TI | Схема ускоренного переноса. |

| 133ИР1 | SN5495 | TI | Универсальный сдвиговый регистр (4 р). |

| 133ИР13 | SN54198 | TI | Реверсивный регистр сдвига (8 р). |

| 133ИР17 | Am2504 | AMD | Регистр последовательного приближения (12 р). |

| 133ИР32 | SN54170 | TI | Регистровый файл 4 x 4. |

| 133КП1 | SN54150 | TI | Селектор-мультиплексор данных на 16 каналов со стробированием. |

| 133КП2 | SN54153 | TI | Сдвоенный цифровой селектор-мультиплексор 4 х 1. |

| 133КП5 | SN54152 | TI | Селектор-мультиплексор данных на 8 каналов. |

| 133КП7 | SN54151 | TI | Селектор-мультиплексор данных на 8 каналов со стробированием. |

| 133ЛА1 | SN5420 | TI | Два логических элемента 4И-НЕ. |

| 133ЛА2 | SN5430 | TI | Логический элемент 8И-НЕ. |

| 133ЛА3 | SN5400 | TI | Четыре логических элемента 2И-НЕ. |

| 133ЛА4 | SN5410 | TI | Три логических элемента 3И-НЕ. |

| 133ЛА6 | SN5440 | TI | Два логических элемента 4И-НЕ с большим коэффициентом разветвления по выходу. |

| 133ЛА7 | SN5422 | TI | Два логических элемента 4И-НЕ с открытым коллекторным выходом. |

| 133ЛА8 | SN5401 | TI | Четыре логических элемента 2И-НЕ с открытым коллекторным выходом. |

| 133ЛА10 | SN5412 | TI | Три логических элемента 3И-НЕ с открытым коллекторным выходом. |

| 133ЛА11 | SN5426 | TI | Четыре высоковольтных логических элемента 2И-НЕ с открытым коллектором. |

| 133ЛА12 | SN5437 | TI | Четыре логических элемента 2И-НЕ с высокой нагрузочной способностью. |

| 133ЛА15 | Четыре логических элемента 2И-НЕ (сопряжение МОП ЗУ — ТТЛ). | ||

| 133ЛД1 | SN5460 | TI | Два четырехвходовых расширителя по ИЛИ. |

| 133ЛД3 | Восьмивходовый расширитель по ИЛИ. | ||

| 133ЛЕ1 | SN5402 | TI | Четыре логических элемента 2ИЛИ-НЕ. |

| 133ЛЕ3 | SN5425 | TI | Два логических элемента 4ИЛИ-НЕ со стробированием. |

| 133ЛЕ5 | SN5428 | TI | Четыре буферных логических элемента 2ИЛИ-НЕ. |

| 133ЛЕ6 | SN54128 | TI | Четыре логических элемента 2ИЛИ-НЕ (магистральный усилитель). |

| 133ЛИ1 | SN5408 | TI | Четыре логических элемента 2И. |

| 133ЛИ3 | SN5411 | TI | Три логических элемента 3И. |

| 133ЛИ5 | SN55451A | TI | Два логических элемента 2И с мощным открытым коллекторным выходом. |

| 133ЛЛ1 | SN5432 | TI | Четыре логических элемента 2ИЛИ. |

| 133ЛН1 | SN5404 | TI | Шесть логических элементов НЕ. |

| 133ЛН2 | SN5405 | TI | Шесть логических элементов НЕ с открытым коллекторным выходом. |

| 133ЛН3 | SN5406 | TI | Шесть буферных логических элементов НЕ с повышенным коллекторным напряжением. |

| 133ЛН5 | SN5416 | TI | Шесть буферных инверторов. |

| 133ЛП4 | SN5417 | TI | 6 повторителей мощных с открытым коллектором. |

| 133ЛП5 | SN5486 | TI | Четыре двухвходовых логических элемента исключающее ИЛИ. |

| 133ЛП7 | SN55450 | TI | Два логических элемента 2И-НЕ с общим входом и двумя мощными транзисторами. |

| 133ЛП8 | SN54125 | TI | Четыре буферных элемента с тремя состояниями и общей шиной. |

| 133ЛП9 | SN5407 | TI | Шесть буферных логических элементов НЕ с повышенным коллекторным напряжением. |

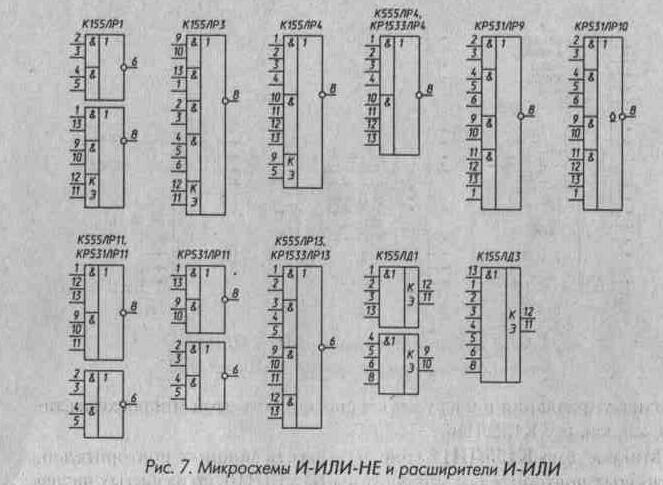

| 133ЛР1 | SN5450 | TI | Два логических элемента 2-2И-2ИЛИ-НЕ, один расширяемый по ИЛИ. |

| 133ЛР3 | SN5453 | TI | Логический элемент 2-2-2-3И-4ИЛИ-НЕ с возможностью расширения по ИЛИ. |

| 133ЛР4 | SN5455 | TI | Логический элемент 4-4И-2ИЛИ-НЕ с возможностью расширения по ИЛИ. |

| 133ПП4 | SN5449 | TI | Дешифратор двоично-десятичный/семисегментный код. |

| 133ПР6 | SN54184 | TI | Преобразователь двоично-десятичного кода в двоичный. |

| 133ПР7 | SN54185 | TI | Преобразователь двоичного кода в двоично-десятичный. |

| 133РП3 | SN54172 | TI | Регистровый файл на 16 бит с выходом 3 состояния. |

| 133РУ1 | SN5481 | TI | Статическое ОЗУ со схемами управления (16 x 1). |

| 133РУ5 | 93410 | FAIRCHILD | Статическое ОЗУ со схемами управления (256 х 1 ). |

| 133РУ7 | 93425 | FAIRCHILD | Статическое ОЗУ со схемами управления (1k х 1 ). |

| 133ТВ1 | SN5472 | TI | JK-триггер с логикой 3И на входе. |

| 133ТВ15 | SN54109 | TI | Два JК-триггера. |

| 133ТЛ1 | SN5413 | TI | Два триггера Шмитта с логическим элементом на входе 4И-НЕ. |

| 133ТЛ2 | SN5414 | TI | Шесть триггеров Шмитта с инверсией. |

| 133ТЛ3 | SN54132 | TI | 4 триггера Шмитта с логикой 2И-НЕ. |

| 133ТМ2 | SN5474 | TI | Два D-триггера. |

| 133ТМ5 | SN5477 | TI | Четыре D-триггера. |

| 133ТМ7 | SN5475 | TI | Четыре D-триггера с прямыми и инверсными выходами. |

| 134ИД3 | SN74L154 | TI | Дешифратор-демультиплексор 4 x 16. |

| 134ИД6 | SN54L82 | TI | Дешифратор 4×10. |

| 134ИЕ2 | SN74L90 | TI | Двоично-десятичный счетчик (4 р). |

| 134ИЕ5 | SN54L93 | TI | Двоичный счетчик (4 р). |

| 134ИЕ8 | SN54L97 | TI | Делитель частоты с переменным коэффициентом деления. |

| 134ИМ4 | SN54LS83 | TI | Полный сумматор (4 р). |

| 134ИМ5 | SN74L183 | TI | Два сумматора (1р). |

| 134ИП2 | SN74L180 | TI | Восьмиразрядная схема контроля четности. |

| 134ИП3 | SN54L181 | TI | Арифметическо-логическое устройство (4 р). |

| 134ИП4 | SN54L182 | TI | Схема ускоренного переноса. |

| 134ИР1 | SN54L95 | TI | Универсальный сдвиговый регистр (4 р). |

| 134ИР2 | SN54L91 | TI | Регистр сдвига (8 р). |

| 134ИР5 | SN74L98 | TI | Селективный накопительный регистр (4 р). |

| 134ИР8 | SN74L164 | TI | Регистр сдвига с параллельным выводом (8 р). |

| 134КП8 | б/а | Три переключателя. | |

| 134КП9 | SN54L153 | TI | Сдвоенный цифровой селектор-мультиплексор 4 х 1. |

| 134КП10 | SN54L152 | TI | Селектор-мультиплексор данных на 8 каналов. |

| 134ЛА2 | SN74L30 | TI | Логический элемент 8И-НЕ. |

| 134ЛА8 | SN74L01 | TI | Четыре логических элемента 2И-НЕ с открытым коллекторным выходом. |

| 134ЛА13 | SN54L38 | TI | Четыре логических элемента 2И-НЕ с открытым коллектором. |

| 134ЛБ1 | ~SN54L00 | TI | Четыре логических элемента 2И-НЕ, 2ИЛИ-НЕ. |

| 134ЛБ2 | ~SN54L20 | TI | Два логических элемента 4И-НЕ, 4ИЛИ-НЕ. |

| 134ЛП3 | б/а | Мажоритарный элемент. | |

| 134ЛР1 | SN54L50 | TI | Два логических элемента 2-2И-2ИЛИ-НЕ, один расширяемый по ИЛИ. |

| 134ЛР2 | SN54L54 | TI | Логический элемент 2И-2И-3И-4И-4ИЛИ-НЕ. |

| 134ЛР4 | SN74L55 | TI | Логический элемент 4-4И-2ИЛИ-НЕ с возможностью расширения по ИЛИ. |

| 134РМ1 | б/а | Четыре накопительных элемента. | |

| 134РУ5 | 93410FM | FAIRCHILD | Статическое O3У (256 x 1). |

| 134РУ6 | SN54S209 | TI | Статическое O3У (1k x 1). |

| 134СП1 | SN74L85 | TI | Схема сравнения 2-х чисел (4 р). |

| 134ТВ1 | SN54L72 | TI | JK-триггер с логикой 3И на входе. |

| 134ТВ14 | SN54L78 | TI | Два JK-триггера. |

| 134ТМ2 | SN74L74 | TI | Два D-триггера. |

| 134ХЛ2 | б/а | Многоцелевой элемент (МЭЦС-2). |

|

| 134ХЛ3 | б/а | Многоцелевой элемент (МЭЦС-1). | |

| 136ЛА1 | SN54L20 | TI | Два логических элемента 4И-НЕ. |

| 136ЛА2 | SN54L30 | TI | Логический элемент 8И-НЕ. |

| 136ЛА3 | SN54L00 | TI | Четыре логических элемента 2И-НЕ. |

| 136ЛА4 | SN54L10 | TI | Три логических элемента 3И-НЕ. |

| 136ЛН1 | SN54L04 | TI | Шесть логических элементов НЕ. |

| 136ЛР1 | SN54L50 | TI | Два логических элемента 2-2И-2ИЛИ-НЕ, один расширяемый по ИЛИ. |

| 136ЛР3 | SN54L53 | TI | Логический элемент 2-2-2-3И-4ИЛИ-НЕ с возможностью расширения по ИЛИ. |

| 136ЛР4 | SN54L55 | TI | Логический элемент 4-4И-2ИЛИ-НЕ с возможностью расширения по ИЛИ. |

| 136ТВ1 | SN54L72 | TI | JK-триггер с логикой 3И на входе. |

| 136ТМ2 | SN54L74 | TI | Два D-триггера. |

| 136ТР1 | RS-триггер с логикой 3И на входе. | ||

| 137ИЛ1 | Полусумматор с нагрузочными резисторами на выходах. | ||

| 137ИЛ2 | Полусумматор с нагрузочными резисторами на выходах. | ||

| 137ИЛ3 | Полусумматор. | ||

| 137ЛД1 | Два трехвходовых расширителя по ИЛИ. | ||

| 137ЛД2 | Два трехвходовых расширителя по ИЛИ. | ||

| 137ЛЕ1 | Два логических элемента 3ИЛИ-НЕ с нагрузочными резисторами на выходах. |

||

| 137ЛЕ2 | Два логических элемента 3ИЛИ-НЕ с нагрузочными резисторами на выходах. | ||

| 137ЛЕ3 | Два логических элемента 3ИЛИ-НЕ. | ||

| 137ЛМ1 | Логический элемент 3ИЛИ-НЕ/3ИЛИ с возможностью расширения по ИЛИ и нагрузочными резисторами на выходах. | ||

| 137ЛМ2 | Логический элемент 3ИЛИ-НЕ/3ИЛИ с возможностью расширения по ИЛИ и нагрузочными резисторами на выходах. | ||

| 137ЛМ3 | Логический элемент 3ИЛИ-НЕ/3ИЛИ с повышенным коэффициентом разветвления и нагрузочными резисторами на выходах. | ||

| 137ЛМ4 | Логический элемент 5ИЛИ-НЕ/5ИЛИ с нагрузочными резисторами на выходах. | ||

| 137ЛМ5 | Логический элемент 5ИЛИ-НЕ/5ИЛИ с нагрузочными резисторами на выходах. |

||

| 137ЛМ6 | Логический элемент 3ИЛИ-НЕ/3ИЛИ с возможностью расширения по ИЛИ. | ||

| 137ЛМ7 | Логический элемент 3ИЛИ-НЕ/3ИЛИ с повышенным коэффициентом разветвления. | ||

| 137ЛМ8 | Логический элемент 5ИЛИ-НЕ/5ИЛИ. | ||

| 137ТМ1 | Синхронный D-триггер. | ||

| 137ТР1 | Синхронный RS-триггер с нагрузочными резисторами на выходах. | ||

| 137ТР2 | Синхронный RS-триггер. | ||

| 138ЛЕ1 | Четыре логических элемента 2ИЛИ-НЕ. | ||

| 138ЛК1 | Два логических элемента 2-2ИЛИ-2И/2И-2ИЛИ-2И-НЕ. | ||

| 138ЛЛ1 | Четыре логических элемента 2ИЛИ. |

||

| 138ЛМ1 | Логический элемент 8ИЛИ-НЕ/8ИЛИ. | ||

| 138ЛМ2 | Два логических элемента 4ИЛИ-НЕ/4ИЛИ. | ||

| 138ЛП1 | Дифференциальный приемник сигнала с линии. | ||

| 138ЛС1 | Логический элемент 4-3-3-3ИЛИ-4И. | ||

| 138ЛС2 | Два логических элемента 2-3ИЛИ-2И. | ||

| 138ТМ1 | D-триггер. | ||

| 138ТМ2 | Два D-триггера. | ||

| 138ТР1 | RS-триггер. | ||

| 138ХЛ1 | Два логических элемента «исключающее» ИЛИ/И-НЕ/ИЛИ. | ||

| 139РВ1 | . |

||

Популярные цифровые микросхемы: Схемотехника — DJVU (83)

DJVU-файл из архива «Популярные цифровые микросхемы», который расположен в категории «». Всё это находится в предмете «схемотехника» из 5 семестр, которые можно найти в файловом архиве НИУ «МЭИ» . Не смотря на прямую связь этого архива с НИУ «МЭИ» , его также можно найти и в других разделах. Архив можно найти в разделе «книги и методические указания», в предмете «схемотехника» в общих файлах.

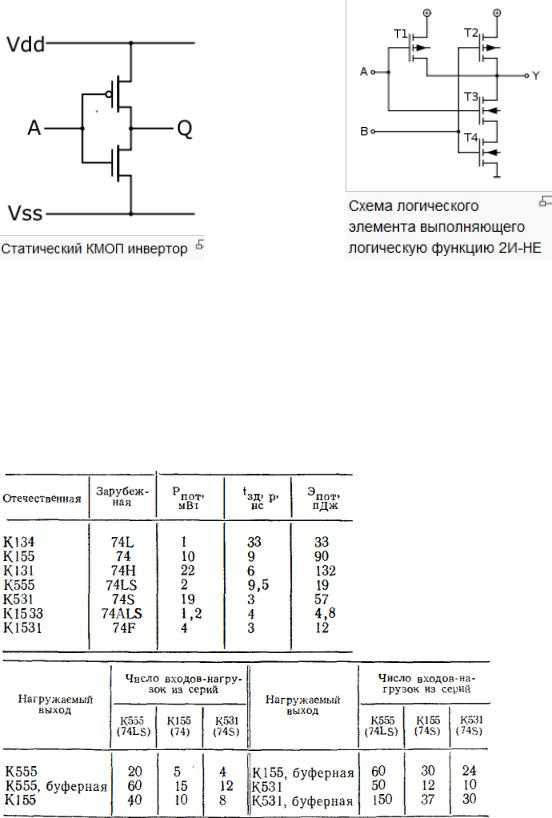

И Массова н радио библиотека Основана в 1947 году Выпуск 1111 Ясап Р~га1 Справочник Моснва «Радио и свнзы 1987 Ц,Л.Шило Популярные цифроеые МИКРОСХВМ Ы ОГЛАВЛЕНИЕ 163 174 184 193 194 204 21! 217 221 224 229 234 248 261 266 278 291 301 308 316 330 336 340 344 Приложение Список литературы 351 352 Предисловие !. циюровые микросхемы ттл 1,1. Общие сведении об элементах ТТЛ . 1.2. Схемотехника элементов ТТЛ !.3. Традиционные серпп ТТЛ 1.4. Перспективныс серии ТТЛ 1.5.

Буферные и разрешающие элементы ТТЛ 1. 6. Схемотехника элементов Й, ЙЛИ, ИУИЛИ 1.7. Микросхемы ТТЛ: И,И, ИЛИ, И/ИЛИ, расширители 1.8. Автогенераторы иа элементах ТТЛ . 1.9. Логическпе элементы — триггеры Шмнтта 1.10. Исключающее ИЛИ 1.11. Триггерные схемы 1.12, К5- и О-триггеры 1.! 3. Ж-триггеры 1.14. Счетчики ТТЛ 1.15. Регистры ТТЛ 1.!6. Лешифраторы и шифраторы ТТЛ . 1.17. Мультиплексоры ТТЛ 1.18.

6. Схемотехника элементов Й, ЙЛИ, ИУИЛИ 1.7. Микросхемы ТТЛ: И,И, ИЛИ, И/ИЛИ, расширители 1.8. Автогенераторы иа элементах ТТЛ . 1.9. Логическпе элементы — триггеры Шмнтта 1.10. Исключающее ИЛИ 1.11. Триггерные схемы 1.12, К5- и О-триггеры 1.! 3. Ж-триггеры 1.14. Счетчики ТТЛ 1.15. Регистры ТТЛ 1.!6. Лешифраторы и шифраторы ТТЛ . 1.17. Мультиплексоры ТТЛ 1.18.

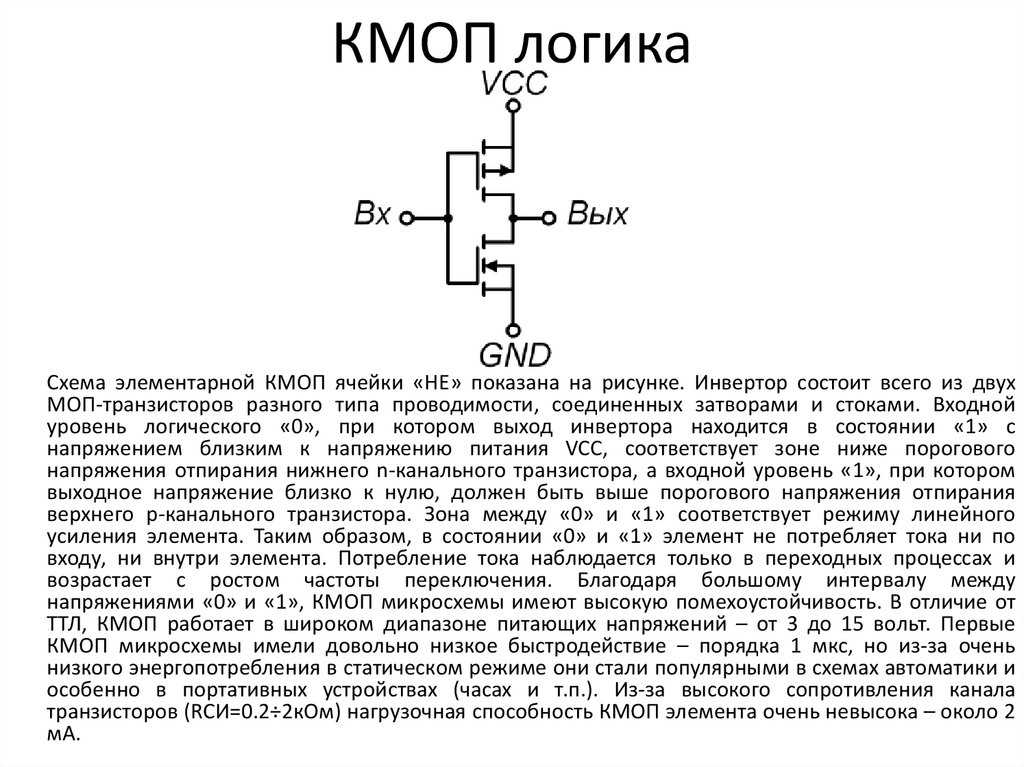

Сумматоры ТТЛ . 1.!9. Оперативныс и постоянные запоминающие устройства ТТЛ 1.20. Узлы вычислительных устройств 1.21. Ждущие мультивибраторы и автогенераторы , ЦИФРОВЫЕ МИКРОСХЕМЫ КМОП 2.1, Устройство и свойства логического элемента КМОП 2.2. Основвые логические элементы Й, ИЛИ, 2 2.3.

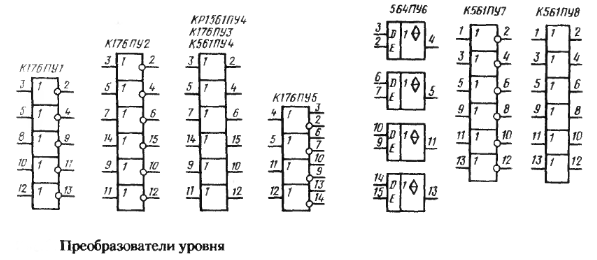

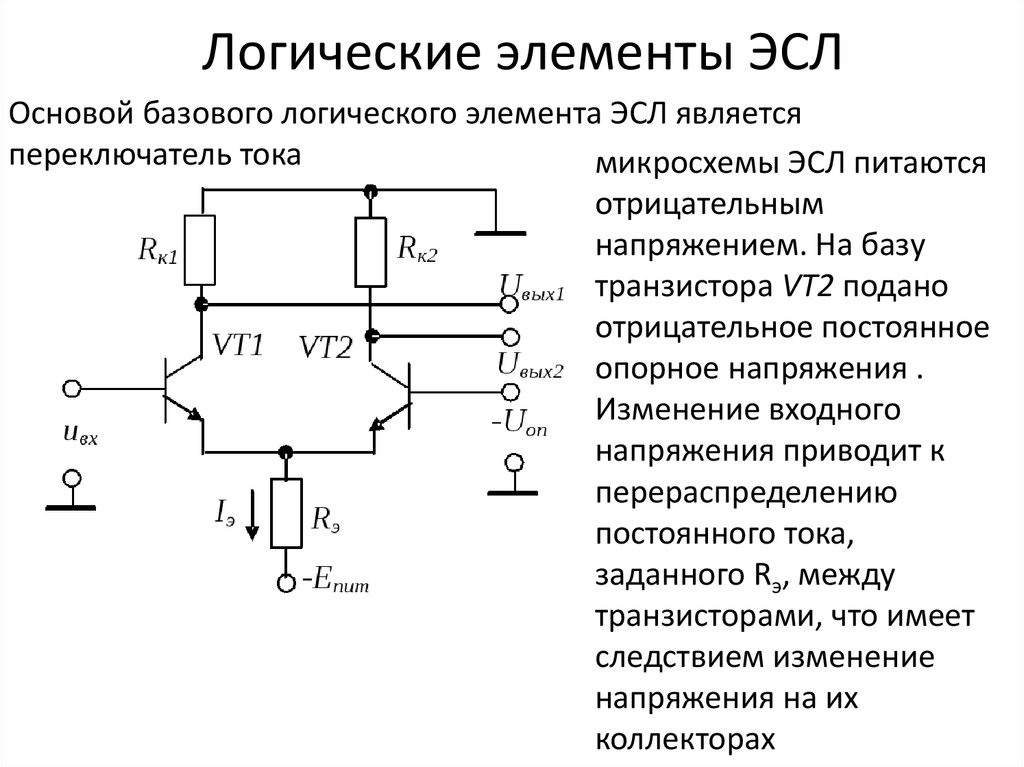

Микросхемы с инвертореми и их применение 2,4, Схемы генераторов и преобразователей 2.5. Преобразователи уровней логических сигналов 2.6. Коммутаторы цифровых и аналоговых сигналов 2.7. Триггерные микросхемы КМОП 2.8. Счетчики-делители КМОП 2.9. Регистры КМОП 2.10. Лешифраторы КМОП 2.11. Арифметические схемы КМОП . 2.12. Микросхемы ФАП и мультнвибраторы ЦИФРОВЫЕ МИКРОСХЕМЫ ЭСЛ 3,1, Схемотехника логических элементов 3. 2.

2.

Комбинаторные микросхемы серии К500 3.3. Триггеры, счетчики и регистры серии К500 3.4. Элементы вычислительных устройств из серии К500 3.5. Комбинаториые микросхемы серии К1500 36. Триггеры и регистры серии К!500 3.7. Узлы вычислительных устройств серии К1500 3 5 5 9 15 23 26 34 40 50 53 55 62 74 79 85 104 130 142 153 ББК 32,844 Ш 81 УДК 62!.397.62 — 619:64 Редакционная коллегия: Б. Г. Белкин, С. А.

Бирюков, В. Г. Борисов, В. М. Бондоренко. Е. Н. Геништп, А. В. Гороховский, С. А. Ельяшкевич, И. Н..%зрей!(ов, В, Г. Корольков, В. Г. Лоляков, А.Д. Смирнов, Ф, И. Торосов, О. П. Фролов, Ю. Л. Хотуняев, Н. И. Чистяков. Шило В. Д. Ш 81 Популярные цифровые микросхемы: Справочник. — Мл Радио и связь, 1987. — 362 сп ил.— (Массовая радиобиблиотека. Бып. 1111).

Приведены сведения а трех самых распространеняых и радиолюбительской практике видах цифровых микросхем: ТТЛ, КМОП и ЭСЛ. Кратко раесматрены основы их схемотехники, показаны структуры, цоиолевки и дена описание работы более 309 типов »»весовых цифровых микросхем: логических элементов, триггеров, регистров, счетчиков, мультиплексоров, арифметическик и др. Денм рекомендации по их прныенению.

Денм рекомендации по их прныенению.

Для подготовленных радиолюбителей и специалистов народного хазяй. ства, разрабатывающих и применяющих импульсно.цифровую аппаратуру 2403000000-170 Ш 100-87 040(01)-87 Р Е Ц Е Н 3 Е Н Т Л. С. ЧЕГЛАКОВ Научно-популярное яздэние ВАЛЕРИЙ ЛЕОНИДОВИЧ ШИЛО ПОПУЛЯРНЫЕ ЦИФРОВЫЕ МИКРОСХЕМЫ Руководитель груины МРБ И. Н.

С у с л о в з Редакторы Т. В. Жукова, 4!. Н. Суслова Художественный редактор Н. С. Ш е я н Переплет художника А. С. Д з у цен а Техничесннй редактор Л. А. Горшкова Корректор Л. С, Г л а г о л е в а ИБ 1598 Сдано в набор 0202.87. Подписано в печать 29.04.87. Т-10452. Формат 84Х(обчм. БУмага ки.-жУРн. № 35 ГаРиитУРа лнтеРатУРнаЯ, Печать высоУч.-изд. л.

22,03. Тираж 250 900 акз. (1-9 завод 1-100 000 зкз.! Изд. № 21955, Зак, № 788, Цена 2 р. 1О к. Издательства «Радио и сввзь». 101000 Москва, Почтамт, а(я 393 Владимирская типография Союзполиграфпрома при Государственном комитете СССР па делам издательств, полиграфии и кни’кной торговли 500000, г, Владимир, Октябрьский проспект. д. 7 © Издательстно «Радио и связь», 1987 ПРЕДИСЛОВИЕ Предлагаемая книга посвшцена схемотехнике самых массо.

д. 7 © Издательстно «Радио и связь», 1987 ПРЕДИСЛОВИЕ Предлагаемая книга посвшцена схемотехнике самых массо.

вых серий микросхем — цифровых малой и средней степени интеграции. Известно, что в 70-е — 80-е годы в аппаратуре доминируют три вида таких микросхем: ТТЛ, КМОП и ЭСЛ. Их выпускают сотнями миллионов штук в год. Возможно, многие из них будут изготавливать до конца столетия. В каждом из трех видов микросхем существуют преемственно развивающиеся серии. Имея описание микросхемы, можно реализовать ее свойства полностью. Каждая группа микросхем (к примеру, счетчиков, регистров) имеет сейчас много схемотехнических применений. Варианты схемотехники отображают как ход развития микросхем, так и расширение запросов потребителей.

Вдумчивый читатель мозкет проследить путь развития схемотехники от простейших микросхем до современных и перспективных. Кроме того, полезно сравнить, как исходные устройства оптимизируются и трансформируются под схемотехнику ТТЛ, КМОП и ЭСЛ. Автор надеется, что книга будет полезна и начинающим, и опытным радиолюбителям, а также студентам и молодым специалистам.

Они смогут осваивать цифровую электронику на практике: познакомившись с отдельными узлами и с параметрами крупносерийяых микросхем, легче изучить теорию логических преобразований. Книга состоит из трех глав. Глава первая — наибольшая по объе. му, поскольку посвящена микросхемам ТТЛ. В ней рассмотрена не только их номенклатура, по и даны некоторые теоретические сведении (например, о триггерах), общие и для двух других глав. Во второй главе описаны самые экономичные массовые микросхемы логики КМОП. Отметим, что микросхемы КМОП разрабатывалн после внедреняя в аппаратуру первых серий ТТЛ, поэтому во многом копировали их структуру, Микросхемы КМОП почти не потребляют энергию от источника питания, когда сигналы не поступают, т.е.

во время ожидания. При обработке сигналов ток потребления микросхем тем больше, чем выше скорость работы устройства. Микросхемы ТТЛ потребляют статический ток, сравнимый по силе с динамическим. Отметим, что на предельных скростях работы токи потребления как для микросхем КМОП, так и для ТТЛР сопоставимы по уровням. Читателю, по-видимому, будет интересно по материалам первой и второй глав самостоятельно сравнить устройство однотипных микросхем ТТЛ и КМОП. Следует подчеркнуть, что в ряде стран парашина. ется выпуск особых серий микросхем КМОП с шифром 74С (здесь цифра 74 заимствуется от названия массовых серий ТТЛ, буква С вЂ” от сокращения СМОБ, в русском варианте — КМОП).

Читателю, по-видимому, будет интересно по материалам первой и второй глав самостоятельно сравнить устройство однотипных микросхем ТТЛ и КМОП. Следует подчеркнуть, что в ряде стран парашина. ется выпуск особых серий микросхем КМОП с шифром 74С (здесь цифра 74 заимствуется от названия массовых серий ТТЛ, буква С вЂ” от сокращения СМОБ, в русском варианте — КМОП).

Микросхемы серии 74С по уровннм электрических сигналов, напряжению питания, структуре и цоколевке в точности соответствуют ыш’росхемам ТТЛ серна 7455 (т. е. отечественной серии К555). Более ‘ новыс, высококачественные варианты, называемые 74НС (Н вЂ” й)йй), соответствуют серии 7455 и но быстродействию, они постепенно вытесняют ее из многих видов цифровой аппаратуры. В последние годы разработаны микросхемы КМОП с условным названием ЕАСТ (фирма Ра~гсй(16), скорость переключения которых сопоставима с перспективными микросхемами ТТЛ типа 74АБ5 (серия КР1533).

В третьей главе рассмотрены микросхемы ЭСЛ. Это самая скоростная логика является, пожалуй, самой спорной. Потребителей отпугивает очень большая рассеиваемая мощность. Однако разработчики ЭСЛ много рзз «спасали» эту логику от наступления ТТЛ, открывая с ее помощью новые возможности увеличения быстродействия цифровых устройств.

Потребителей отпугивает очень большая рассеиваемая мощность. Однако разработчики ЭСЛ много рзз «спасали» эту логику от наступления ТТЛ, открывая с ее помощью новые возможности увеличения быстродействия цифровых устройств.

В настоящее время быстродействие ЭСЛ достигло субнаносекундного диапазона (серия К1500), а перспективные серии ТТЛ работают пока еще со скоростью в 3 …4 раза меньшей. В книге используются таблицы номенклатуры и таблицы состояний. В таблицах номенклатуры перечисяяются отечественные микросхемы, приводятся нх зарубежные аналоги.

В каждую таблнцу сводятся микросхемы определенного типа для нескольких сходных серий. Наличие микросхемы в серии отмечается крестиком. По мере появления новых микросхем читатель может самостоятельно сделать отметки в этвх таблицах. Таблицы состояний отображают логические функции микросхем. Здесь, как и на принципиальных схемах, использованы мнемонические обозначения, которые сведены в табл. П.1, приведенную в Приложении. Зная буквенно-цифровое обозначение, с помощью табл. П.2 мож. ио найти в этой книге интересующую микросхему ТТЛ серий К155, К555, К531, КР1533 и КР(53!. В таблице микросхемы перечислены в алфавитном порядке букв, входящих в их обозначение.

П.2 мож. ио найти в этой книге интересующую микросхему ТТЛ серий К155, К555, К531, КР1533 и КР(53!. В таблице микросхемы перечислены в алфавитном порядке букв, входящих в их обозначение.

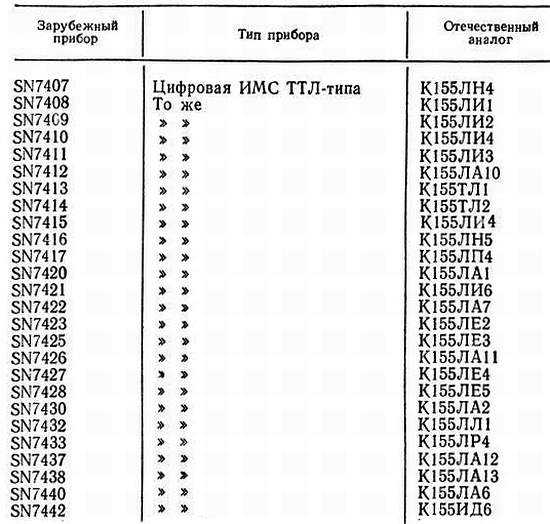

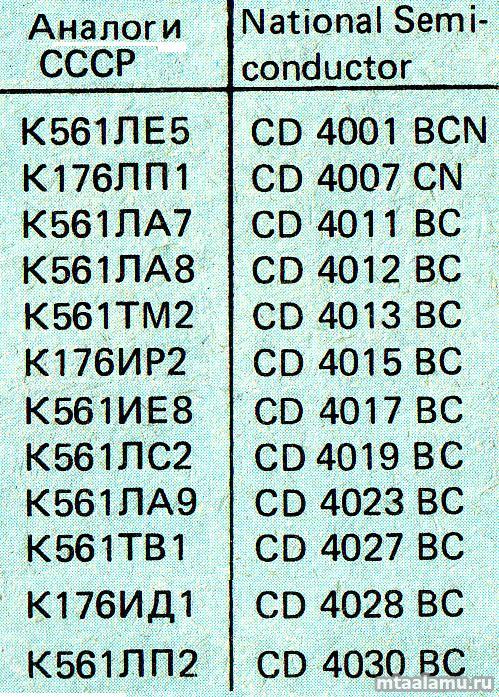

Наименования отечественных цифровых микросхем отличаются от соответствующих зарубежных. Вместе с теы в иностранных радиолю. бительских журналах, а также в переводных изданиях можно найти много полезных вариантов применения микросхем. С целью ориентнровки в зарубежных названиях микросхем ТТЛ в табл. П.З показана связь нх с отечественными аналогами. Таблица П.4 поможет найти в книге микросхемы КМОП серий К!76 и К561 по их буквенно-цифровому обозначению.

С соответствием наименований зарубежных и отечественных микросхем КМОП мохсно ознакомиться по табл. П,5. Микросхемы ЭСЛ наносекундной (К500) и субнаносекундной серий (К1500) можно отыскать по табл. П.6 и П.7, где они перечисляютсн в порядке возрастания их условных номеров 1. ЦИФРОВЫЕ МИКРОСХЕМЫ ТТЛ 1.!. ОБЩИЕ СВЕДЕНИЯ ОБ ЭЛЕМЕНТАХ ТТЛ В цифровой микросхеме простейшие логические операции осуществляются с помощью логическнх элементов. В начале развития микроэлектроники кахсдая микросхема содержала обычно всего один логический элемент, подобный тому, который показан на рис. 1.1, а. По мере развития технологии на кристалле микросхемы стали размещать наборы таких элементов, а затем соединять их в логические структуры.

В начале развития микроэлектроники кахсдая микросхема содержала обычно всего один логический элемент, подобный тому, который показан на рис. 1.1, а. По мере развития технологии на кристалле микросхемы стали размещать наборы таких элементов, а затем соединять их в логические структуры.

При этом прин!пзпиальная схема логического элемента ие менялась. Однако с течением времени импульсные параметры микросхемы оказывались нодостаточнымн и приходилось расширять диапазоны быстродействия, экономичность и помехоустойчивость микросхем за счет, новой принципиальной схемы логического элемента. За четверть века последовательно сменилось около десятка таких схем. Чтооы их можно было легко различать, им присвапвайи сокращенные условные обозначения. В обозначении, как правило, присутствует буква Л вЂ” начальная от слова логика. Этим словом в свое время условно назвалн цифровой ключ.

Логические ИС серии 74 | Electronics Club

Логические ИС серии 74 | Клуб электроникисемьи | Открытый коллектор | Характеристики | Логические ворота | Счетчики | Декодеры | Драйверы дисплея

См. также: Серия 4000 | ИС

также: Серия 4000 | ИС

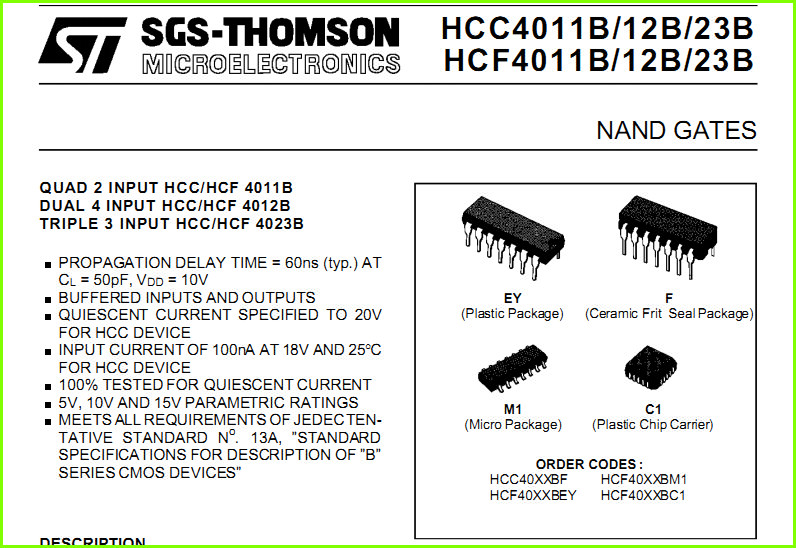

Существует несколько семейств логических ИС, пронумерованных от 74xx00 и далее с буквами (xx) в середине числа, чтобы указать тип схемы, например, 74LS00 и 74HC00. В исходном семействе (ныне устаревшем) не было букв, например 7400.

Rapid Electronics: микросхемы серии 74

На этой странице представлены многие микросхемы серии 74, в которых основное внимание уделяется на самых полезных воротах, прилавках, декодеры и драйверы дисплея. Для каждой микросхемы есть схема, показывающая расположение выводов, и краткие пояснения. функцию штифтов, где это необходимо. Для простоты буквы семейства после 74 опущены на диаграммах ниже, поскольку применяются штыревые соединения. ко всем ИС с одинаковым номером. Например, вентили NAND 7400 доступны как 74HC00, 74HCT00 и 74LS00.

Если вы используете другую ссылку, имейте в виду, что существуют некоторые различия в терминах, используемых для описания функций выводов.

например сброс также называется сброс . Некоторые входы имеют «активный низкий уровень», что означает, что они работают.

их функция при низком уровне. Если вы видите линию, нарисованную над меткой, это означает, что она активна на низком уровне, например:

(скажем «сброс-бар»).

На странице «Ссылки» перечислены веб-сайты с таблицами данных.

Некоторые входы имеют «активный низкий уровень», что означает, что они работают.

их функция при низком уровне. Если вы видите линию, нарисованную над меткой, это означает, что она активна на низком уровне, например:

(скажем «сброс-бар»).

На странице «Ссылки» перечислены веб-сайты с таблицами данных.

Рекомендуемая книга: Поваренная книга TTL

74 серии семейств

Семейство 74LS (с низким энергопотреблением Шоттки) (как и оригинал) использует схему TTL (транзисторно-транзисторная логика). что быстро, но требует больше энергии, чем более поздние семейства. Серию 74 часто до сих пор называют «серией TTL». даже несмотря на то, что последние ИС не используют TTL!

Семейство 74HC имеет высокоскоростную схему CMOS, сочетающую скорость TTL с очень низким энергопотреблением.

расход серии 4000. Это микросхемы CMOS с тем же расположением выводов, что и в старом семействе 74LS.

Обратите внимание, что входы 74HC не могут надежно управляться выходами 74LS, поскольку диапазоны напряжения, используемые для логического 0

не совсем совместимы, используйте вместо них 74HCT.

Семейство 74HCT представляет собой специальную версию 74HC с входами, совместимыми с 74LS TTL, поэтому 74HCT можно смело смешивается с 74LS в той же системе. Фактически 74HCT можно использовать в качестве прямой замены маломощных более старые микросхемы 74LS в большинстве схем. Небольшой недостаток 74HCT — меньшая помехоустойчивость, но это вряд ли будет проблемой в большинстве ситуаций.

Для большинства новых проектов лучшим выбором будет семейство 74HC. Семейства 74LS и 74HCT требуют питания 5 В, поэтому они не подходят для работы от батареи.

Выходы с открытым коллектором

Некоторые микросхемы серии 74 имеют выходы с открытым коллектором, это означает, что они могут погружаться. ток, но они не могут быть источником тока. Они ведут себя как NPN транзисторный переключатель.

На схеме показано, как выход с открытым коллектором может быть подключен к стоковому току от источника питания с

более высокое напряжение, чем питание логической ИС. Максимальное напряжение питания нагрузки составляет 15 В для большинства интегральных схем с открытым коллектором.

Максимальное напряжение питания нагрузки составляет 15 В для большинства интегральных схем с открытым коллектором.

Выходы с открытым коллектором можно безопасно соединить вместе для включения нагрузки при низком уровне любого из них; в отличие от обычных выходов, которые должны быть объединены с помощью диодов.

Характеристики семейств 74HC и 74HCT

Схема КМОП, используемая в микросхемах серий 74HC и 74HCT , чувствительны к статическому электричеству. Прикосновение к булавке, когда она заряжена статическим электричеством (например, от вашей одежды) может повредить микросхему. На самом деле большинство ИС при регулярном использовании вполне терпимы. достаточно заземлить руки, прикоснувшись к металлической водопроводной трубе или оконной раме, прежде чем прикасаться к ним. ИС следует оставлять в защитной упаковке до тех пор, пока вы не будете готовы их использовать.

- 74HC Питание: от 2 до 6 В, допустимы небольшие колебания.

- 74HCT Источник питания: 5 В ± 0,5 В, лучше всего использовать регулируемый источник питания.

- Входы имеют очень высокий импеданс (сопротивление), это хорошо, т.к.

они не повлияют на часть цепи, где они подключены. Однако это также означает, что несвязанные

входы могут легко улавливать электрические помехи и быстро переключаться между высоким и низким состоянием непредсказуемым образом.

Это, вероятно, приведет к хаотичному поведению микросхемы и значительно увеличит потребляемый ток.

Во избежание проблем все неиспользуемые входы ДОЛЖНЫ быть подключены к источнику питания (+Vs или 0V) ,

это применимо, даже если эта часть микросхемы не используется в схеме!

Обратите внимание, что входы 74HC не могут надежно управляться выходами 74LS , поскольку используемые диапазоны напряжения для логического 0 не совсем совместимы. Для надежности используйте 74HCT , если в системе есть микросхемы 74LS.

- Выходы могут потреблять и выдавать около 4 мА, если вы хотите сохранить правильное выходное напряжение для управления логическими входами, но если нет необходимости управлять какими-либо входами, максимальный ток составляет около 20 мА. Для переключения больших токов можно подключить транзистор.

- Разветвление: один выход может управлять несколькими входами (50+), за исключением входов 74LS, поскольку для них требуется более высокий ток, и можно управлять только 10.

- Время прохождения строба : около 10 нс для прохождения сигнала через строб.

- Частота : до 25 МГц.

- Потребляемая мощность (самой микросхемы) очень низкая, несколько мкВт. Он намного больше на высоких частотах, например, несколько мВт на частоте 1 МГц.

Семейство 74LS ТТЛ характеристики

- Питание: 5В ±0,25В, оно должно быть очень плавным, лучше всего отрегулированное питание*.

В дополнение к нормальному сглаживанию питания, конденсатор 0,1 мкФ должен быть подключен к источнику питания около

IC для удаления «пиков», возникающих при переключении состояния, требуется один конденсатор на каждые 4 IC.

В дополнение к нормальному сглаживанию питания, конденсатор 0,1 мкФ должен быть подключен к источнику питания около

IC для удаления «пиков», возникающих при переключении состояния, требуется один конденсатор на каждые 4 IC.

* По моему опыту, микросхемы 74LS обычно успешно работают с питанием от батареи 4,5 В в простых и нетребовательных низкочастотные цепи, но я, конечно, не рекомендую это для какой-либо схемы с серьезными целями. так как оно находится за пределами диапазона номинального напряжения. - Входы ‘высокий уровень с плавающей запятой до логической 1, если они не подключены, но не полагайтесь на это в постоянном (паяная) цепь, так как входы могут улавливать электрические помехи. 1 мА должен быть выведен, чтобы удерживать входы в состоянии логического 0. В постоянной цепи целесообразно подключать любые неиспользуемые входы к + V, чтобы обеспечить хорошую помехоустойчивость.

- Выходы могут потреблять до 16 мА (достаточно, чтобы зажечь светодиод),

но они могут подавать только около 2 мА.

Для переключения больших токов можно

подключить транзистор.

Для переключения больших токов можно

подключить транзистор. - Разветвление : один выход может управлять до 10 входов 74LS, но гораздо больше входов 74HCT.

- Время прохождения строба : около 10 нс для прохождения сигнала через строб.

- Частота : примерно до 35 МГц (при правильных условиях).

- Потребляемая мощность (самой ИС) составляет несколько мВт.

Для большинства новых проектов лучшим выбором будет семейство 74HC.

Семейства 74LS и 74HCT требуют питания 5 В, поэтому они не подходят для работы от батареи. Если вы привыкли использовать серию 74LS, помните, что входы 74HC и 74HCT не имеют высокого уровня, когда они не подключены. поэтому неиспользуемые входы должны быть подключены к +Vs или 0V для надежной работы.

Смешивание логических семейств

Лучше всего строить схему, используя только одно логическое семейство, но при необходимости можно использовать разные семейства. смешанные при условии, что источник питания подходит для всех из них. Например, для смешивания 4000 и 74HC требуется

напряжение питания должно быть в диапазоне от 3 до 6В. Схема, включающая микросхемы 74LS или 74HCT, должна иметь питание 5 В.

смешанные при условии, что источник питания подходит для всех из них. Например, для смешивания 4000 и 74HC требуется

напряжение питания должно быть в диапазоне от 3 до 6В. Схема, включающая микросхемы 74LS или 74HCT, должна иметь питание 5 В.

Выход 74LS не может надежно управлять входом 4000 или 74HC, если только не установлен нагрузочный резистор 2.2k подключено между источник питания +5 В и вход для коррекции немного отличающихся используемых диапазонов логического напряжения.

Обратите внимание, что выход серии 4000 может управлять только одним входом 74LS.

Таблицы с характеристиками логических семейств см. в разделе Логические ИС

Управление входами 4000 или 74HC от выхода

74LS с помощью подтягивающего резистора.

Счетверенные 2-входовые ворота

- 7400 счетверенный NAND с 2 входами

- 7403 Четыре входа NAND с двумя входами и выходами с открытым коллектором

- 7408 счетверенный 2 входа И

- 7409 счетверенный И с 2 входами и выходами с открытым коллектором

- 7432 счетверенный 2 входа ИЛИ

- 7486 счетверенный 2 входа EX-OR

- 74132 Четырехканальный И-НЕ с 2 входами и входами триггера Шмитта

Модель 74132 имеет входы триггера Шмитта для обеспечения хорошей помехоустойчивости. Они идеально подходят для медленно меняющихся или шумных сигналов.

Они идеально подходят для медленно меняющихся или шумных сигналов.

7402 quad 2-input NOR

Микросхема 7402 показана отдельно, так как имеет необычное расположение вентилей.

Тройные вентили с 3 входами

- 7410 Тройные вентили с 3 входами NAND

- 7411 тройной 3-х входной И

- 7412 Тройной NAND с 3 входами и выходами с открытым коллектором

- 7427 тройной 3 входа NOR

Обратите внимание, как ворота 1 распределены по двум сторонам упаковки.

Двойные вентили с 4 входами

- 7420 Двойные вентили с 4 входами NAND

- 7421 двойной 4 входа И

NC = нет соединения (неиспользуемый контакт).

7430 8-входовой логический элемент И-НЕ

NC = нет соединения (неиспользуемый контакт).

Шестигранные ворота НЕ

- 7404 шестнадцатеричный НЕ

- 7405 hex НЕ с выходами с открытым коллектором

- 7414 hex НЕ с входами триггера Шмитта

Модель 7414 имеет входы триггера Шмитта для обеспечения хорошей помехоустойчивости. Они идеально подходят для медленно меняющихся или шумных сигналов.

Они идеально подходят для медленно меняющихся или шумных сигналов.

7490 Декадный (0–9) счетчик пульсаций

7493 4-битный (0–15) счетчик пульсаций

Это счетчики пульсаций, поэтому будьте осторожны, так как в любых системах логических вентилей могут возникать сбои. подключены к их выходам из-за небольшой задержки перед тем, как более поздние выходы счетчика среагируют на тактовый импульс.

Счет увеличивается по мере того, как вход часов становится низким (по заднему фронту), это отображается по полосе над меткой часов. Это обычное поведение часов пульсирующих счетчиков, и это означает, что выход счетчика может напрямую управлять тактовым входом следующего счетчика в цепочке.

Счетчик состоит из двух секций: clockA-QA и clockB-QB-QC-QD. Для обычного использования подключите QA к clockB, чтобы связать две секции и подключите внешний тактовый сигнал к clockA.

Для нормальной работы хотя бы один вход reset0 должен иметь низкий уровень, при этом оба высоких уровня сбрасывают счетчик на ноль. (0000, QA-QD низкий). Обратите внимание, что 7490 имеет пару входов reset9 на контактах 6 и 7, они сбрасывают счетчик на

девять (1001), поэтому хотя бы одно из них должно быть низким, чтобы произошел подсчет.

(0000, QA-QD низкий). Обратите внимание, что 7490 имеет пару входов reset9 на контактах 6 и 7, они сбрасывают счетчик на

девять (1001), поэтому хотя бы одно из них должно быть низким, чтобы произошел подсчет.

Счет до максимального значения (9 или 15) может быть достигнут путем подключения соответствующих выходов к два входа reset0 . Если требуется только один вход сброса, два входа можно соединить вместе. Например: для счета от 0 до 8 подключите QA (1) и QD (8) к входам сброса.

NC = нет соединения (неиспользуемый контакт).

# на 7490 контакты 6 и 7 подключаются к

внутреннему вентилю И для сброса на 9.

Для нормального использования подключите QA к clockB, а

подключите внешний тактовый сигнал к clockA.

Соединение в цепочку

Подробную информацию о соединении счетчиков пульсаций, таких как 7490 и 7493, в цепочку см. ниже.

74390 Двойной декадный (0-9) счетчик пульсаций

74390 содержит два отдельных счетчика декад (от 0 до 9), по одному с каждой стороны микросхемы. Это счетчики пульсаций, поэтому будьте осторожны, так как в любом логическом элементе могут возникнуть сбои.

системы, подключенные к их выходам, из-за небольшой задержки перед тем, как более поздние выходы счетчика среагируют на тактовый импульс.

Это счетчики пульсаций, поэтому будьте осторожны, так как в любом логическом элементе могут возникнуть сбои.

системы, подключенные к их выходам, из-за небольшой задержки перед тем, как более поздние выходы счетчика среагируют на тактовый импульс.

Счет увеличивается по мере того, как вход часов становится низким (по заднему фронту), это отображается по полосе над меткой часов. Это обычное поведение часов пульсирующих счетчиков, и это означает, что выход счетчика может напрямую управлять тактовым входом следующего счетчика в цепочке.

Каждый счетчик состоит из двух секций: clockA-QA и clockB-QB-QC-QD. Для обычного использования подключите QA к clockB, чтобы связать две секции и подключите внешний тактовый сигнал к clockA.

Для нормальной работы вход сброса должен быть низким, установка высокого уровня сбрасывает счетчик на ноль. (0000, QA-QD низкий).

Счет до менее чем 9 может быть достигнут путем подключения соответствующего выхода(ов) к входу сброса,

используя вентиль И, если необходимо. Например: для счета от 0 до 7 подключите QD (8) для сброса, для счета от 0 до 8 подключите

QA (1) и QD (8) для сброса с использованием вентиля И.

Например: для счета от 0 до 7 подключите QD (8) для сброса, для счета от 0 до 8 подключите

QA (1) и QD (8) для сброса с использованием вентиля И.

Для нормального использования подключите QA к ClockB, а

подключите внешний тактовый сигнал к ClockA.

Соединение в цепочку

Подробную информацию о соединении счетчиков пульсаций, таких как 74390, в цепочку см. ниже.

74393 двойной 4-битный (0-15) счетчик пульсаций

74393 содержит два отдельных 4-битных (от 0 до 15) счетчика, по одному на каждой стороне микросхемы. Это счетчики пульсаций, поэтому будьте осторожны, так как в логических системах могут возникать сбои. подключены к их выходам из-за небольшой задержки перед тем, как более поздние выходы среагируют на тактовый импульс.

Счет идет как часы вход становится низким (по заднему фронту), на это указывает

по полосе над меткой часов. Это обычное поведение часов пульсирующих счетчиков, и это означает, что

означает, что выход счетчика может напрямую управлять тактовым входом следующего счетчика в цепочке.

Для нормальной работы вход сброса должен быть низким, установка высокого уровня сбрасывает счетчик на ноль (0000, QA-QD низкий).

Счет до менее чем 15 может быть достигнут путем подключения соответствующего выхода(ов) к входу сброса, используя вентиль И, если необходимо. Например, чтобы посчитать от 0 до 8, соедините QA (1) и QD (8) для сброса с помощью вентиля И.

Соединение в цепочку

Подробную информацию о соединении счетчиков пульсаций, таких как 74390, в цепочку см. ниже.

Соединение счетчиков импульсов в цепочку

На приведенной ниже диаграмме показано, как связать счетчики пульсаций в цепочку, обратите внимание, как наибольший выходной QD каждого счетчик управляет входом часов следующего счетчика.

74160-3 синхронных счетчика

- 74160 синхронный декадный счетчик (стандартный сброс)

- 74161 синхронный 4-битный счетчик (стандартный сброс)

- 74162 синхронный декадный счетчик (синхронный сброс)

- 74163 синхронный 4-битный счетчик (синхронный сброс)

Это синхронные счетчики , поэтому их выходы изменяются точно вместе при каждом тактовом импульсе. Это полезно, если вам нужно подключить их выходы к логическим элементам, потому что это позволяет избежать сбоев, которые

происходят со счетчиками пульсаций.

Это полезно, если вам нужно подключить их выходы к логическим элементам, потому что это позволяет избежать сбоев, которые

происходят со счетчиками пульсаций.

Счет продвигается по часам 9Вход 0016 становится высоким (по переднему фронту). Декадные счетчики считают от 0 до 9 (от 0000 до 1001 в двоичном формате). 4-битные счетчики считают от 0 до 15 (от 0000 до 1111 в двоичном формате).

Для нормальной работы (подсчета) сброс , предустановка , включение счета и в все входы должны быть высокими. Когда count enable имеет низкий уровень, вход часов игнорируется и подсчет останавливается.

Счетчик может быть предустановленным , поместив нужное двоичное число на входы AD , сделав

вход предустановки низкий, и подача положительного импульса на вход часов .

Входы AD можно оставить неподключенными, если они не требуются.

Вход сброса имеет активный низкий уровень, поэтому для нормальной работы (счета) он должен быть высоким (+Vs). При низком уровне счетчик сбрасывается на ноль (0000, низкий уровень QA-QD), это происходит сразу же с 74160 и 74161 ( стандартный сброс ), но с 74162 и 74163 ( синхронный сброс ) сброс происходит по переднему фронту тактового входа.

Счет до максимального значения (15 или 9) может быть достигнут путем подключения соответствующего выхода(ов) через логический элемент НЕ или И-НЕ на вход сброса. Для 74162 и 74163 (синхронный сброс ) вы должны использовать выходные данные, представляющие на единицу меньше . чем количество сбросов, которое вам требуется, например. для сброса на 7 (считая от 0 до 6) используйте QB (2) и QC (4).

* сброс и предустановка активны-низкий уровень

9Предварительная установка 0010 также известна как включение параллельного подключения (PE)

Соединение в цепочку

Подробная информация о соединении синхронных счетчиков, таких как микросхемы 74160-3, в цепочке приведена ниже.

Соединение синхронных счетчиков в цепочку

На схеме ниже показано, как связать синхронные счетчики, такие как 74160-3, обратите внимание, как все часы (СК) входы связаны. Вынос (CO) используется для подачи переноса (CI) следующего счетчика. Перенос (CI) первого счетчика 74160-3 должен быть высоким.

74192 Десятичный (0-9) прямой счетчик

74193 Прямой/нижний 4-битный (0-15) счетчик

Это синхронные счетчики , поэтому их выходы изменяются точно вместе при каждом тактовом импульсе. Это полезно, если вам нужно подключить их выходы к логическим элементам, потому что это позволяет избежать сбоев, которые происходят со счетчиками пульсаций.

Эти счетчики имеют отдельные входы часов для прямого и обратного счета.

Счет увеличивается как up clock Вход становится высоким (по переднему фронту).

Счетчик уменьшается по мере того, как на входе нисходящей частоты становится высоким уровень (по переднему фронту). В обоих случаях другой тактовый вход должен быть высоким.

В обоих случаях другой тактовый вход должен быть высоким.

Для нормальной работы (подсчета) на входе предварительной настройки должен быть высокий уровень, а на входе сброса — низкий уровень. Когда на входе reset высокий уровень, счетчик сбрасывается до нуля (0000, низкий уровень QA-QD).

Счетчик может быть предварительно задан путем помещения желаемого двоичного числа на вводит AD и кратковременно установка пресета на вход низкого уровня. Обратите внимание, что для предварительной настройки не требуется тактовый импульс, в отличие от счетчиков 74160-3. Входы AD можно оставить неподключенными, если они не требуются.

* предустановка активна-низкая

Соединение в цепочку

Подробнее о соединении этих счетчиков вверх/вниз в цепочку см. ниже.

Соединение счетчиков вверх/вниз в цепочку

На приведенной ниже схеме показано, как подключить 74192-3 счетчика прямого/обратного счета с отдельными входами прямого и обратного часов,

обратите внимание, как несут и заимствуют , подключены к up clock и down clock входы соответственно следующего счетчика.

74HC4017 Декадный счетчик (1 из 10)

74HC4020 14-битный счетчик пульсаций

74HC4040 12-разрядный счетчик пульсаций

74HC4060 14-разрядный счетчик пульсаций с внутренним генератором

Это эквиваленты 74HC счетчиков CMOS серии 4000. Как и все микросхемы 74HC, им требуется питание от 2 до 6 В. Контактные соединения и функции см.:

- 4017

- 4020

- 4040

- 4060

7442 Декодер BCD в десятичный (1 из 10)

Выходы 7442 имеют активный низкий уровень , что означает, что они становятся низкими при выборе, но имеют высокий уровень в другие времена. Они могут потреблять около 20 мА.

Соответствующий выход становится низким в ответ на ввод BCD (двоично-десятичный код). Например, ввод двоичного кода 0101 (=5) сделает выход Q5 низким, а все остальные выходы — высоким.

7442 представляет собой двоично-десятичный декодер, предназначенный для ввода значений от 0 до 9. (от 0000 до 1001 в двоичном формате). При входах от 10 до 15 (от 1010 до 1111 в двоичном формате) все выходы имеют высокий уровень.

(от 0000 до 1001 в двоичном формате). При входах от 10 до 15 (от 1010 до 1111 в двоичном формате) все выходы имеют высокий уровень.

Обратите внимание, что 7442 можно использовать в качестве декодера 1-из-8 , если на вход D подается низкий уровень.

См. также: 74HC4017 и 4017 оба являются счетчиком декад и декодером 1 из 10 в одной ИС.

7447 Драйвер BCD для 7-сегментного дисплея

Соответствующие выходы a-g становится низким для отображения BCD (двоично-десятичное) число, подаваемое на входы AD . Модель 7447 имеет открытый коллектор. выходы a-g, которые могут потреблять до 40 мА. Сегменты 7-сегментного дисплея должны быть подключены между +Vs и выходами с последовательным резистором. (330 с питанием 5В). Требуется дисплей с общим анодом .

Проверка дисплея и пустой ввод активны-низкий уровень, поэтому для нормальной работы они должны быть высокими. Когда отображает тест низкий, все сегменты дисплея должны светиться (показывая цифру 8).

Когда отображает тест низкий, все сегменты дисплея должны светиться (показывая цифру 8).

Если пустой ввод имеет низкий уровень, дисплей будет пустым, когда ввод счетчика равен нулю (0000). Это может быть использовано для удаления начальных нулей, когда несколько разрядов дисплея управляются цепочкой счетчиков. Для этого пустой выход должен быть подключен к пустому входу следующего отображать вниз по цепочке (следующая по значимости цифра).

Модель 7447 предназначена для BCD (двоично-десятичной системы), которая представляет собой входные значения от 0 до 9.(от 0000 до 1001 в двоичном формате). Вводы от 10 до 15 (от 1010 до 1111 в двоичном формате) будут освещать нечетные сегменты дисплея, но не причинят вреда.

74HC4511 Драйвер BCD для 7-сегментного дисплея

Это эквивалент 74HC драйвера дисплея CMOS 4511. Как и все микросхемы 74HC, ему требуется питание от 2 до 6 В.

Контактные соединения и функции см. 4511.

4511.

47. Таблица функций интегральной логики общего назначения < Серия 74 >|Chip One Stop

| Функциональное название | Функция | Номера контактов |

|---|---|---|

00 | Четырехканальный логический элемент И-НЕ с двумя входами | 14 |

02 | Четырехканальный логический элемент NOR с 2 входами | 14 |

03 | Quad 2-Input NAND GateOpen Drain | 14 |

04 | Шестигранный инвертор | 14 |

U04 | Шестигранный инвертор | 14 |

05 | Шестигранный инвертор с открытым сливом | 14 |

06 | Шестигранные инверторные буферы/драйверыОткрытый дренаж | 14 |

07 | Шестигранный буфер Открытый дренаж | 14 |

08 | Счетверенный вентиль И с 2 входами | 14 |

09 | Счетверенные вентили положительного И с 2 входами и выходами с открытым коллектором | 14 |

10 | Тройной логический элемент И-НЕ с 3 входами | 14 |

11 | Тройной вентиль И с 3 входами | 14 |

14 | Шестигранный инвертор Шмитта | 14 |

16 | Шестигранный инвертор | 14 |

20 | Двойной логический элемент И-НЕ с 4 входами | 14 |

21 | Двойной вентиль И с 4 входами | 14 |

27 | Тройной логический элемент NOR с 3 входами | 14 |

30 | Логический элемент И-НЕ с 8 входами | 14 |

32 | Счетверенный операционный вентиль с 2 входами | 14 |

33 | 13-входовой логический элемент И-НЕ | 14 |

38 | Четырехканальный логический элемент И-НЕ с двумя входами | 14 |

42 | Декодер BCD-to-Decimal | 16 |

45 | BCD в десятичный декодер | 16 |

47 | BCD К 7-СЕГМЕНТНОМУ ДЕКОДЕРУ/ДРАЙВЕРАМ | 16 |

73 | Двойной триггер J-K с предустановкой и очисткой | 14 |

74 | Двойной D-триггер с предустановкой и очисткой | 14 |

75 | 4-битная бистабильная защелка | 16 |

85 | 4-битный компаратор величин | 16 |

86 | Эксклюзивные ворота Quad OR | 14 |

93 | 4-БИТНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 14 |

107 | Двойной J-K триггер с прозрачным покрытием | 14 |

109 | Двойной триггер J-K с предустановкой и очисткой | 16 |

112 | Двойной триггер J-K с предустановкой и очисткой | 16 |

121 | Моностабильный мультивибратор | 14 |

122 | Моностабильный мультивибратор с перезапуском | 14 |

123А | Двойной моностабильный мультивибратор | 16 |

125 | Счетверенный буфер шины 3, состояние | 14 |

126 | Quad Bus Buffer3-State | 14 |

128 | Шестигранный линейный драйвер OR-Gate | 14 |

132 | Четырехканальный вентиль Schmitt NAND с двумя входами | 14 |

133 | Логический элемент И-НЕ с 13 входами | 16 |

137 | Декодер от 3 до 8 строк с защелкой адреса | 16 |

138 | Декодер 3-8 строк | 16 |

139 | Двойной декодер 2-4 строки | 16 |

145 | ДЕКОДЕРЫ/ДРАЙВЕРЫ BCD-TO-DECIMAL | 16 |

147 | Кодировщик с приоритетом от 10 до 4 строк | 16 |

148 | Кодер с приоритетом 8-3 линий | 16 |

151 | 8-канальный мультиплексор | 16 |

153 | Двойной 4-канальный мультиплексор | 16 |

154 | Декодер строк от 4 до 16 | 24 |

155 | Двойной декодер 2-4 строки | 16 |

157 | Счетверенный 2-канальный мультиплексор | 16 |

158 | Четверной 2-канальный инвертированный мультиплексор | 16 |

161 | Синхр. | 16 |

163 | Синхр. Двоичный счетчик с синхронизацией. Очистить | 16 |

164 | 8-битный сдвиговый регистр с последовательным вводом/выводом | 14 |

165 | 8-битный регистр сдвига с параллельным вводом/последовательным выводом | 16 |

166 | 8-битный регистр сдвига с параллельным вводом/последовательным выводом | 16 |

169 | СИНХРОННЫЕ 4-БИТНЫЕ ДВОИЧНЫЕ СЧЕТЧИКИ ВВЕРХ/ВНИЗ | 16 |

173 | Quad D-Type Register3-State | 16 |

174 | Шестигранный триггер D-типа с прозрачным покрытием | 16 |

175 | Счетверенный триггер D-типа с прозрачным покрытием | 16 |

191 | 4-битный двоичный счетчик прямого/обратного счета | 16 |

193 | Синхр. | 16 |

194 | 4-БИТНЫЕ ДВУНАПРАВЛЕННЫЕ УНИВЕРСАЛЬНЫЕ РЕГИСТРЫ Сдвига | 16 |

221А | Двойной моностабильный мультивибратор | 16 |

237 | Декодер/защелка 3-8 строк | 16 |

238 | Декодер 3-8 строк | 16 |

240 | Восьмеричный буфер шины, 3 состояния, инвертированный | 20 |

241 | Восьмеричный буфер шины 3, состояние | 20 |

244 | Восьмеричный буфер шины, 3 состояния | 20 |

245 | Приемопередатчик Octal Bus, 3 состояния | 20 |

251 | 8-канальный мультиплексор, 3 состояния | 16 |

253 | Двойной 4-канальный мультиплексор, 3 состояния | 16 |

257 | Счетверенный 2-канальный мультиплексор, 3 состояния | 16 |

259 | 8-битная адресная защелка | 16 |

273 | Восьмеричный триггер D-типа с прозрачным покрытием | 20 |

279 | Защелка Quad S-R | 16 |

280 | 9-битный генератор/контроллер четности | 14 |

283 | 4-битный полный сумматор | 16 |

294 | Программируемый делитель частоты/таймер | 16 |

297 | ЦИФРОВЫЕ ФИЛЬТРЫ С ФАЗОВОЙ АППАРАТУРОЙ | 16 |

299 | 8-битный регистр сдвига PIPO | 20 |

354 | 8-1-строчный переключатель даты/MultiPrexer | 20 |

365 | Шестнадцатеричный буфер шины, 3 состояния | 16 |

366 | Буфер шины Hex, 3 состояния, инвертированный | 16 |

367 | Шестнадцатеричный буфер шины, 3 состояния | 16 |

368 | Буфер шины Hex, 3 состояния, инвертированный | 16 |

373 | Восьмеричная защелка D-типа, 4 состояния | 20 |

374 | Восьмеричный триггер типа D, 3 состояния | 20 |

375 | Счетверенная защелка D-типа | 16 |

377 | Восьмеричный триггер D-типа | 20 |

378 | ШЕСТИГРАННЫЕ ШЛЕСТРЫ D-ТИПА | 16 |

390 | Двойной декадный счетчик | 16 |

393 | Двойной двоичный счетчик | 14 |

423А | Двойной моностабильный мультивибратор | 16 |

521 | 8-битный компаратор равенства | 20 |

534 | Восьмеричный триггер D-типа с 3 состояниями, перевернутый | 20 |

540 | Восьмеричный буфер шины, 3 состояния, инвертированный | 20 |

541 | Восьмеричный буфер шины, 3 состояния | 20 |

564 | Восьмеричный триггер D-типа с 3 состояниями, инвертированный | 20 |

573 | Восьмеричная защелка D-типа, 4 состояния | 20 |

574 | Восьмеричный триггер типа D, 3 состояния | 20 |

580 | Восьмеричная защелка D-типа, 4 состояния | 20 |

590 | 8-битный двоичный счетчик/состояние регистра 3 | 16 |

592 | 8-битный регистровый/двоичный счетчик | 16 |

594 | 8-битные сдвиговые регистры с выходными регистрами | 16 |

595 | 8-битный регистр сдвига/состояние Latch4 | 16 |

597 | 8-битный регистр-защелка/сдвиг | 16 |

624 | Одиночный генератор, управляемый напряжением | 14 |

640 | Приемопередатчик Octal Bus, 3 состояния, инвертированный | 20 |

645 | Приемопередатчик Octal Bus, 3 состояния | 20 |

646 | Octal Bus TransceiverRegister3-State | 24 |

652 | Octal Bus TransceiverRegister3-State | 24 |

670 | 4-словный x 4-битный регистр File3-state | 16 |

674 | 16-разрядный последовательный ввод/вывод, параллельный регистр хранения | 24 |

688 | 8-битный компаратор равенства | 20 |

697 | U/D 4-битный двоичный счетчик/состояние регистра 3 | 20 |

873 | Двойная 4-битная защелка типа D, 4 состояния | 24 |

2244 | Восьмеричный буфер шины, 3 состояния | 20 |

2245 | Приемопередатчик Octal Bus | 20 |

3245 | Приемопередатчик Octal Bus, 3 состояния | 24 |

С3245 | Приемопередатчик Octal Bus с двойным питанием, 3 состояния | 24 |

4002 | Двойной вентиль положительного ИЛИ-НЕ с 4 входами | 14 |

4017 | Счетчик декад/делитель | 16 |

4020 | 14-ступенчатый двоичный счетчик | 16 |

4024 | 7-ступенчатый двоичный счетчик | 14 |

4028 | Декодер BCD-to-Decimal | 16 |

4040 | 12-ступенчатый двоичный счетчик | 16 |

4046 | Контур фазовой автоподстройки частоты с ГУН | 16 |

4049 | Шестнадцатеричный инвертирующий буфер/преобразователь | 16 |

4050 | Шестнадцатеричный неинвертирующий буфер/преобразователь | 16 |

4051 | Одиночный 8-канальный аналоговый мультиплексор/демультиплексор | 16 |

4051А | Одиночный 8-канальный аналоговый мультиплексор/демультиплексор | 16 |

4052 | Двойной 4-канальный аналоговый мультиплексор/демультиплексор | 16 |

4052А | Двойной 4-канальный аналоговый мультиплексор/демультиплексор | 16 |

4053 | Тройной 2-канальный аналоговый мультиплексор/демультиплексор | 16 |

4053А | Тройной 2-канальный аналоговый мультиплексор/демультиплексор | 16 |

4060 | 14-ступенчатый двоичный счетчик/осциллятор | 16 |

4066 | Счетверенный двусторонний переключатель | 14 |

4072 | Двойной 4-входовой положительный логический элемент ИЛИ | 14 |

4075 | Тройной вентиль положительного ИЛИ с 3 входами | 14 |

4078 | 8-входовой положительный вентиль ИЛИ/НЕ | 14 |

4094 | 8-ступенчатый шинный регистр сдвига и сохранения | 16 |

4245 | Приемопередатчик Octal Bus с двойным питанием, 3 состояния | 24 |

4511 | Защелка/декодер/драйвер 7-сегментного двоично-десятичного кода | 16 |

4514 | 4-битная защелка Декодер строк от 5 до 16 | 24 |

4520 | Двойной двоичный счетчик прямого счета | 16 |

4538 | Моно-мультивибратор Dual Precision | 16 |

7046 | Контур фазовой автоподстройки частоты с ГУН | 16 |

7240 | Восьмеричный буфер шины, 3 состояния, инвертированный | 20 |

7244 | Восьмеричный буфер шины 3, состояние | 20 |

7266 | Quad Exclusive-NOR Gate | 14 |

7292 | Программируемый делитель/таймер | 16 |

16240 | 16-битный буфер шины, 3 состояния | 48 |

16241 | 16-битный буфер шины, 3 состояния | 48 |

16244 | 16-битный буфер шины, 3 состояния | 48 |

16245 | 16-битный трансивер шины 3-состояние | 48 |

16373 | 16-битная защелка D-типа с 4 состояниями | 48 |

16374 | 16-битный триггер D-типа с 3 состояниями | 48 |

16646 | 16-битный шинный трансиверRegister3-State | 56 |

16652 | 16-битный шинный трансиверRegister3-State | 56 |

40102 | Двойной двоично-десятичный программируемый обратный счетчик | 16 |

40103 | 8-битный двоичный программируемый обратный счетчик | 16 |

40105 | 4-битный регистр FIFO по 16 слов | 16 |

163245 | 16-битный шинный трансивер с двойным питанием и серийным разрешением | 48 |

164245 | 16-битный шинный трансивер с двойным питанием и серийным разрешением | 48 |

Примечание.

В дополнение к нормальному сглаживанию питания, конденсатор 0,1 мкФ должен быть подключен к источнику питания около

IC для удаления «пиков», возникающих при переключении состояния, требуется один конденсатор на каждые 4 IC.

В дополнение к нормальному сглаживанию питания, конденсатор 0,1 мкФ должен быть подключен к источнику питания около

IC для удаления «пиков», возникающих при переключении состояния, требуется один конденсатор на каждые 4 IC.  Для переключения больших токов можно

подключить транзистор.

Для переключения больших токов можно

подключить транзистор. Двоичный счетчик с асинхронностью. Очистить

Двоичный счетчик с асинхронностью. Очистить Двоичный счетчик вверх/вниз

Двоичный счетчик вверх/вниз