Простой металлоискатель на четырех транзисторах. Схема

Главная » Бытовая электроника » Простой металлоискатель на четырех транзисторах. Схема

Хотите стать охотником за сокровищами? За счет тонких изменений частоты эта конструкция транзисторного металлоискателя способна обнаруживать монеты на глубине до 10 сантиметров.

Устройство может обнаруживать банку из-под газировки на глубине до 15 см и металлические трубы на еще большем расстоянии.

Металлоискатель питается от двух последовательно соединенных батарей по 9 В. Схема достаточно экономичная в плане питания — потребляет примерно 9 мА при 18 В.

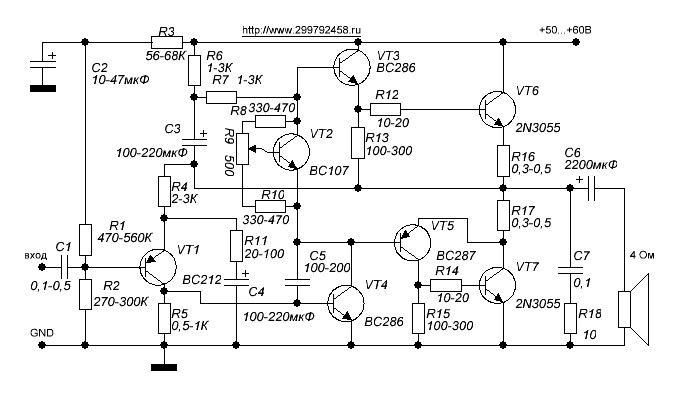

Конструкция транзисторного металлоискателя состоит из четырех частей:

- На транзисторе VT1 построен осциллятор, частота которого определяется индуктивностью катушки L1.

- На транзисторе VT2 выполнен опорный генератор, частота которого задается емкостью C6.

- На транзисторе VT3 собран микшер, который объединяет сигналы с выходов VT1 и VT2.

- На транзисторе VT4 построен простой усилитель.

Катушка L1 должна иметь индуктивность 100 мкГн. Катушка намотана на каркас диаметром 10 см и содержит 22 витка медного провода диаметром примерно 0,6мм.

Индуктивность поисковой катушкой вместе с кабелем составляет примерно126 мкГн. Для правильной работы необходимо использовать аудиокабель.

Резонансная частота:

F = 1 / (2π * SQR (L1 * C)).

Конденсатор 1 нФ (C3) соединенный последовательно с 10 нФ (C4) и плюс 56 пФ (C2) дает общую емкость 965 пФ. При такой емкости резонансная частота составит 456 кГц, когда рядом с поисковой катушкой L1 нет металлических предметов.

Генератор, построенный на транзисторе VT2, является опорным генератором. Его частоту можно подстроить, изменяя емкость конденсатора C6. Частота должна быть в пределах 2 кГц от выходной частоты VT1. Чтобы получить этот результат, вам, возможно, придется подобрать также емкость конденсатора C8.

Инвертор 12 В/ 220 В

Инвертор с чистой синусоидой, может обеспечивать питание переменно. ..

..

Подробнее

Обратите внимание, что частота колебаний VT1 очень чувствительна к паразитной емкости. Выходной сигнал генератора на VT1 будет изменяться примерно на 70 Гц при каждом изменение паразитной емкости на 1 пикофарад.

Микшер на транзисторе VT4 объединяет сигналы с обоих генераторов (на VT1 и VT2). Когда металлический объект приближается к поисковой катушке, индуктивность L1 уменьшается. Это приводит к увеличению частоты колебаний на VT1.

Выходной сигнал микшера представляет собой сумму и разность двух сигналов:

Fosc + Fref и | Fosc – Fref | ,

где «| x |» означает «абсолютное значение x»

Предположим, что если Fref = 500 кГц и Fosc = 501 кГц, то выход микшера будет 1 кГц и 1001 кГц. Если Fref = 500 кГц и Fosc = 499 кГц, то выходной сигнал составит 1 кГц и 999 кГц.

Частоты, выдаваемые микшером, поступают на транзисторный усилитель (VT3) с высоким входным сопротивлением. Выход с VT3 через разделительный конденсатор поступает на регулятор громкости R16.

Наушники, используемые в этом металлоискателе, должны иметь высокий импеданс. Здесь будут хорошо работать керамические наушники, имеющие импеданс около 20 МОм.

Обратите внимание, что в наушники отправляются обе частоты микшера: верхние и нижние. Наушники шунтирует более высокую частоту на землю, действуя как фильтр нижних частот.

Тестер транзисторов / ESR-метр / генератор

Многофункциональный прибор для проверки транзисторов, диодов, тиристоров…

Подробнее

Categories Бытовая электроника Tags Металлоискатель

Отправить сообщение об ошибке.

Распознавание цифровых схем. Асинхронный счётный триггер / Хабр

Борис Цирлин и Александр Кушнеров

30.10.2019

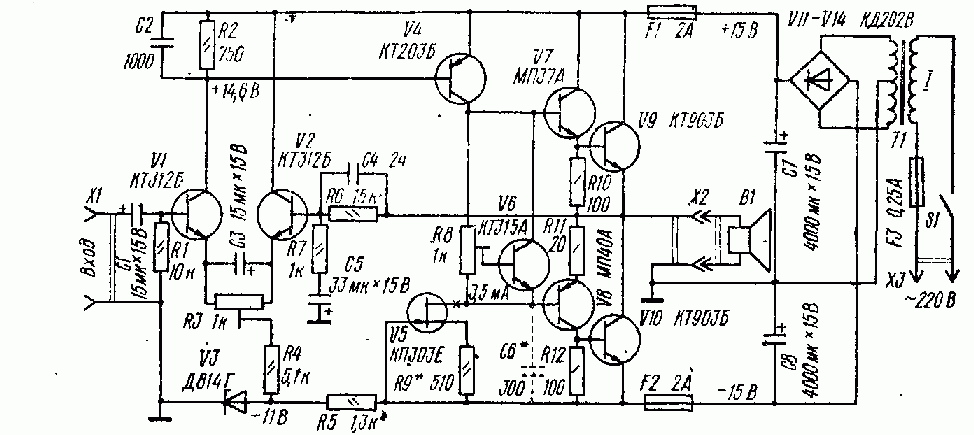

Для опытного разработчика схем не составляет большого труда узнать знакомую схему, в каком бы виде она не была нарисована. В этой статье мы покажем, что две транзисторные схемы из патентов являются вариантом асинхронного счётного триггера (АСТ). По сравнению со стандартной схемой, в схемах из патентов отсутствуют некоторые транзисторы. Это может рассматриваться как неисправность. Мы покажем, что, если такая же неисправность возникает в стандартной схеме, она продолжает работать правильно. АСТ, реализованный только на элементах ИЛИ-НЕ [1] или только на элементах И-НЕ известен как гарвардский триггер. Оба варианта схем показаны на Рис. 1, где g7 – это индикатор завершения переходных процессов. В дальнейшем мы его рассматривать не будем. На Рис. 1 показаны также графы сигнальных переходов (STG) [2] построенные в Workcraft [3].

По сравнению со стандартной схемой, в схемах из патентов отсутствуют некоторые транзисторы. Это может рассматриваться как неисправность. Мы покажем, что, если такая же неисправность возникает в стандартной схеме, она продолжает работать правильно. АСТ, реализованный только на элементах ИЛИ-НЕ [1] или только на элементах И-НЕ известен как гарвардский триггер. Оба варианта схем показаны на Рис. 1, где g7 – это индикатор завершения переходных процессов. В дальнейшем мы его рассматривать не будем. На Рис. 1 показаны также графы сигнальных переходов (STG) [2] построенные в Workcraft [3].

Рис. 1. Асинхронный счётный триггер (АСТ) и его STG.

Обратим внимание, что в обоих вариантах АСТ есть три пары элементов (g1, g2), (g4, g5) и (g3, g6), которые имеют общий вход. Транзисторные схемы элементов 2И-НЕ и 2ИЛИ-НЕ показаны на Рис. 2. Трёхвходовые элементы устроены аналогично и содержат 6 транзисторов.

Рис. 2. Транзисторные схемы элементов 2И-НЕ и 2ИЛИ-НЕ.

Возьмём два элемента 2ИЛИ-НЕ и выберем у каждого вход, где p-MOS транзистор подключён к Uпит. Соединим эти входы вместе и подключим к земле (лог. 0). Оба транзистора откроются и напряжение на их стоках будет равным Uпит. Достаточно ли этого чтобы безопасно соединить стоки и заменить два транзистора на один, как показано на Рис. 3? Нет. Нужно проверить что произойдёт если на общий вход подать лог. 1. Выходы обоих элементов соединятся с землёй, и мы будем иметь мостиковую схему из четырёх p-MOS транзисторов. Для оставшихся двух входов имеем четыре комбинации 0 и 1. Легко показать, что ни в одной из них не возникает короткого замыкания между Uпит и землёй.

Соединим эти входы вместе и подключим к земле (лог. 0). Оба транзистора откроются и напряжение на их стоках будет равным Uпит. Достаточно ли этого чтобы безопасно соединить стоки и заменить два транзистора на один, как показано на Рис. 3? Нет. Нужно проверить что произойдёт если на общий вход подать лог. 1. Выходы обоих элементов соединятся с землёй, и мы будем иметь мостиковую схему из четырёх p-MOS транзисторов. Для оставшихся двух входов имеем четыре комбинации 0 и 1. Легко показать, что ни в одной из них не возникает короткого замыкания между Uпит и землёй.

Рис. 3. Два элемента 2ИЛИ-НЕ, имеющие общий вход.

Рассмотрим теперь схему распределителя импульсов [4] на Рис. 4. Пользуясь Рис. 3, мы можем перерисовать эту схему как показано на Рис. 5. В ней уже можно узнать АСТ на Рис. 1, однако, там элементы g3 и g6 имеют 3 входа.

Рис. 4. Схема распределителя импульсов из [4].

Рис. 5. Вариант схемы на Рис. 4.

Затворы транзисторов 11 и 12 можно рассматривать как входы элементов 3ИЛИ-НЕ, в которых третий p-MOS транзистор закорочен.

Рис. 6. STG для ИЛИ-НЕ. Сигналы in, g2, g6 и g3.

Поскольку третий p-MOS транзистор закорочен, переключение g3+ может произойти после переключений in- и g6- (в любом порядке) без разрешающего переключения g2-. Однако, как видно из Рис. 6, на участке от g2+ до g2- есть только in- и g6+, поэтому запрещённого переключения g3+ не происходит. Перед переключением g2+ элемент g3 уже находится в 0, а на его входе g6 всё ещё 0, т.е. первый p-MOS транзистор открыт. Переключение g2+ открывает транзистор 11 и должно выключить закороченный p-MOS транзистор. Этого не происходит, более того, переключение in- открывает второй p-MOS транзистор. Таким образом, через два открытых p-MOS транзистора и открытый транзистор 11 начинает течь ток от Uпит к земле. Это продолжается короткое время, пока следующее переключение g6+ не закроет первый p-MOS транзистор.

Рис. 7. Схема счётного триггера из [5].

Рис. 8. Вариант схемы на Рис. 7.

Будут ли выходы g3 и g6 на Рис. 8 переключаться правильно, если третий p-MOS транзистор в параллель отсутствует? Это будет понятно после анализа STG на Рис. 9, который, как и в предыдущем случае, получен из соответствующего STG на Рис. 1 удалением всех сигналов, кроме in, g2, g6 и g3.

Рис. 9. STG для И-НЕ. Сигналы in, g2, g6 и g3.

Элемент g3 – это 3И-НЕ, поэтому после переключений in+, g6+ и g2+ (в любом порядке) произойдёт переключение g3-. Любое из обратных переключений in-, g6- или g2- должно вызвать переключение g3+. Однако, g2- не может открыть отсутствующий p-MOS транзистор, поэтому g3 останется в 0 и будет ждать переключения in- или g6-. Как видно из Рис. 9, на участке от g3- до g3+ переключения g2- нет и p-MOS транзистор здесь не нужен. С другой стороны, этот транзистор должен обеспечивать лог. 1 на g3, когда in и g6 переключаются произвольно. Рассмотрим на Рис. 9 участок от g3+ до g2+. Переключение g2- закрывает транзистор 19. Далее, переключение in+ закрывает транзистор 1 и открывает транзистор 15. Элемент g6 остаётся в 1, т.е. транзистор 17 открыт, а транзистор 3 закрыт. Таким образом, in+ отключает g3 и от земли, и от Uпит. Тем не менее, на g3 удерживается лог. 1, поскольку на практике между g3 и землёй есть паразитная ёмкость, которая заряжена до Uпит. Переключение g6- открывает транзистор 3 и подключает эту ёмкость к Uпит. Для второй половины схемы всё аналогично. Таким образом, задержки элементов g6 и g3 определяют время, в течении которого состояние запоминается на ёмкости. На практике важно чтобы ток утечки транзисторов 19 и 20 был маленьким, иначе за отведённое время ёмкость может разрядится ниже (1/2)Uпит.

Однако, g2- не может открыть отсутствующий p-MOS транзистор, поэтому g3 останется в 0 и будет ждать переключения in- или g6-. Как видно из Рис. 9, на участке от g3- до g3+ переключения g2- нет и p-MOS транзистор здесь не нужен. С другой стороны, этот транзистор должен обеспечивать лог. 1 на g3, когда in и g6 переключаются произвольно. Рассмотрим на Рис. 9 участок от g3+ до g2+. Переключение g2- закрывает транзистор 19. Далее, переключение in+ закрывает транзистор 1 и открывает транзистор 15. Элемент g6 остаётся в 1, т.е. транзистор 17 открыт, а транзистор 3 закрыт. Таким образом, in+ отключает g3 и от земли, и от Uпит. Тем не менее, на g3 удерживается лог. 1, поскольку на практике между g3 и землёй есть паразитная ёмкость, которая заряжена до Uпит. Переключение g6- открывает транзистор 3 и подключает эту ёмкость к Uпит. Для второй половины схемы всё аналогично. Таким образом, задержки элементов g6 и g3 определяют время, в течении которого состояние запоминается на ёмкости. На практике важно чтобы ток утечки транзисторов 19 и 20 был маленьким, иначе за отведённое время ёмкость может разрядится ниже (1/2)Uпит.

По сравнению со стандартным АСТ на Рис. 1, в схемах на Рис. 5 и на Рис. 8 функция установки в 1 элемента 3ИЛИ-НЕ и функция сброса в 0 элемента 3И-НЕ повреждена. Это означает, что стандартный АСТ продолжит работать правильно, даже если в элементах g6 и g3 возникнет соответствующая неисправность. Для стандартной схемы (без g7) нужно 28 транзисторов. Для схем на Рис. 4 и на Рис. 7 (без транзисторов 11, 12, 24, 23) нужно соответственно 23 и 22 транзистора. Если вернуть недостающие p-MOS транзисторы, эти схемы будут работать надёжнее. Минимальное количество транзисторов в схеме на Рис. 7 не обязательно говорит о том, что она лучше схемы на Рис. 4 и лучше схемы на Рис. 1. Помимо количества транзисторов и потребляемого тока есть другие важные параметры, например,

- сложность дополнительной схемы для установки начальных состояний

- нагрузочная способность (скорость перезарядки ёмкости нагрузки)

- скорость выхода из метастабильного состояния

- количество и значения паразитных ёмкостей

- количество и значения токов утечки

Сравнительный анализ этих параметров, как и обсуждение схем АСТ реализованных на других элементах, выходит за рамки этой статьи.

Литература

[1] G. T. Osborne, «Asynchronous binary counter register stage with flip-flop and gate utilizing plurality of interconnected NOR circuits». Patent US3139540, 30 Jun. 1964.

[2] Л. Я. Розенблюм и А. В. Яковлев, «О новой графической форме иллюстрации сущности изобретения,» Вопросы изобретательства, № 11, pp. 36-40, 1988.

[3] https://workcraft.org

[4] В. И. Горячев, Б. М. Мансуров, Я. Д. Мартыненко и Р. Г. Талибов, «Четырехфазовый распределитель импульсов». Авторское свидетельство SU342299, 14.06.1972.

[5] В. И. Варшавский, Н. М. Кравченко, В. Б. Мараховский и Б. С. Цирлин, «Счетный триггер на КМОП-транзисторах». Авторское свидетельство SU1398069, 23.05.1988.

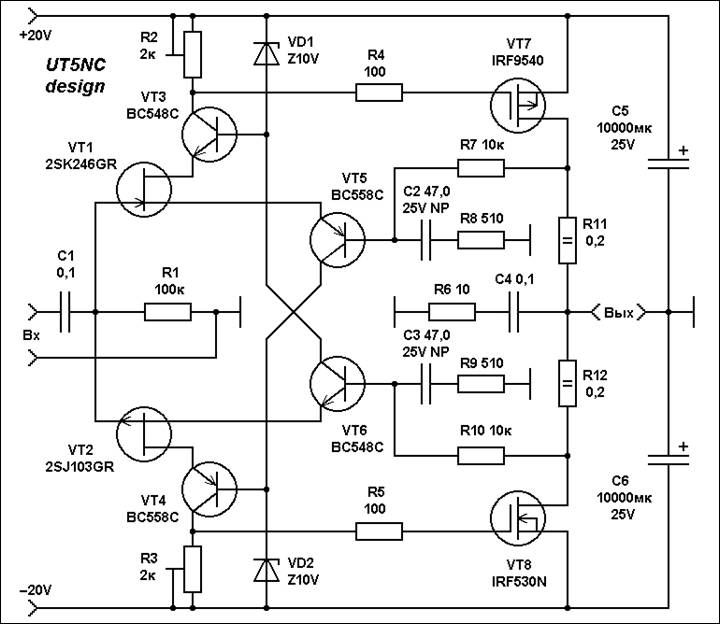

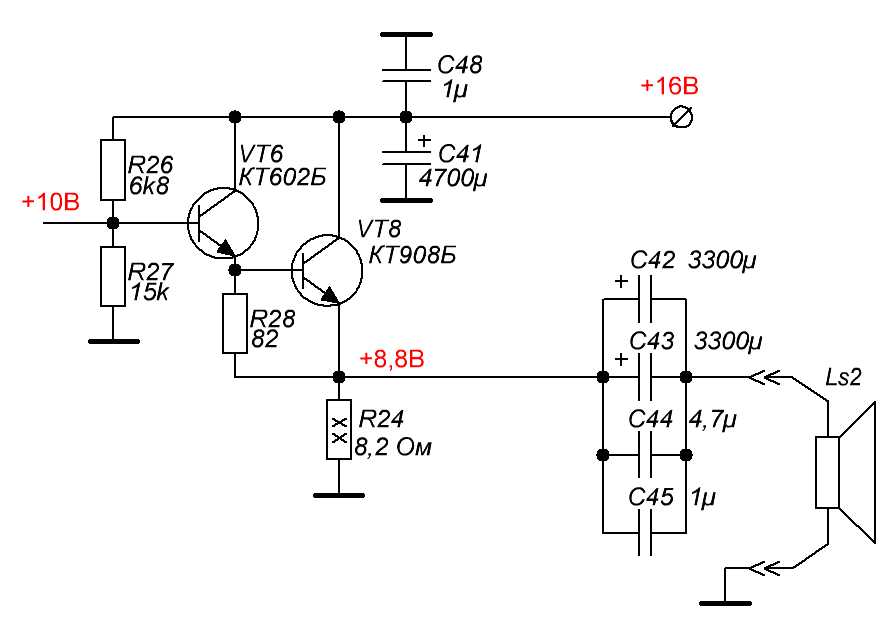

Схема комплементарной симметрии — усилители

Усилители

Переходные транзисторы доступны как типы PNP и NPN.

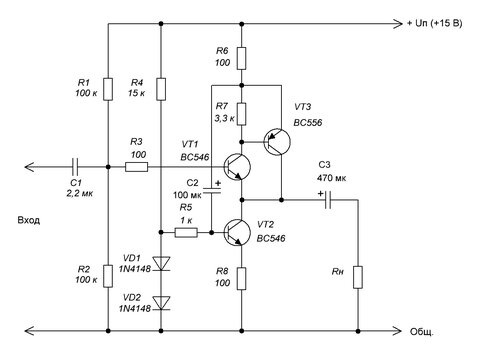

Если два типа транзисторов соединены в один каскад (рисунок ниже),

путь тока (указанный стрелками) в выходной цепи завершается через

коллекторно-эмиттерные переходы транзисторов. При подключении к этому

Таким образом, схема упоминается как схема комплементарной симметрии .

При подключении к этому

Таким образом, схема упоминается как схема комплементарной симметрии .

Схема дополнительной симметрии обеспечивает все преимущества обычной схемы. двухтактные усилители без необходимости в каскаде драйвера фазоинвертора или для входного трансформатора с отводом от средней точки. Параллельное подключение выхода цепь по отношению к нагрузке устраняет необходимость в отводной первичной обмотке. трансформатор в выходной цепи.

Схема комплементарной симметрии с нулевым смещением.

На рисунке выше показаны два транзистора в комплементарном соединении симметрии.

Транзистор Q 1 представляет собой транзистор PNP и транзистор Q 2 — NPN-транзистор. Отрицательный входной сигнал

смещает транзистор Q 1 в прямом направлении и заставляет его проводить.

Положительный входной сигнал смещает транзистор в прямом направлении Q 2 и заставляет его проводить. Поскольку один транзистор проводит, другой

непроводящие, потому что сигнал, который идет вперед, смещает один

транзистор, обратное смещение другого транзистора.

Результирующее действие в выходной цепи можно понять, рассмотрев схема рисунка ниже. Это упрощенная версия выходной схемы. Внутренняя цепь эмиттер-коллектор транзистора Q 1 представлен переменным резистором R 1 и транзистора Q 2 переменным резистором Р 2 .

Упрощенный вариант выходной схемы комплементарной схемы симметрии.

При отсутствии входного сигнала и работе класса B (нулевое смещение эмиттер-база)

переменные плечи переменных резисторов можно считать находящимися в выключенном состоянии

позиции (бесконечные сопротивления R 1 и Р 2 ). Ток через транзисторы не течет

ни через нагрузочный резистор R L . Когда входящий сигнал идет

положительный, транзисторный Q 2 проводящий и транзисторный Q 1 остается непроводящим. Переменный резистор Р 1 остается в выключенном состоянии. Переменное плечо резистора R 2 движется к точке 3 и ток проходит через последовательную цепь

состоит из батареи В CC2 , переменного резистора R 2 и резистор R L . Величина текущего потока

зависит от величины входящего сигнала, регулируемый рычаг перемещается

к точке 3 для увеличения прямого смещения и к точке 4 для уменьшения

смещение вперед. Ток течет в направлении пунктирной стрелки,

выдает напряжение указанной полярности. Когда входной сигнал проходит

минус, транзистор Q 1 проводники и транзистор Q 2 становится непроводящим. То же действие повторяется с

переменный резистор R 1 . Ток течет через батарею В CC1 , нагрузочный резистор R L и

переменный резистор R 1 в направлении, указанном

сплошная стрелка и создает напряжение на резисторе R L с указанием полярности.

Переменное плечо резистора R 2 движется к точке 3 и ток проходит через последовательную цепь

состоит из батареи В CC2 , переменного резистора R 2 и резистор R L . Величина текущего потока

зависит от величины входящего сигнала, регулируемый рычаг перемещается

к точке 3 для увеличения прямого смещения и к точке 4 для уменьшения

смещение вперед. Ток течет в направлении пунктирной стрелки,

выдает напряжение указанной полярности. Когда входной сигнал проходит

минус, транзистор Q 1 проводники и транзистор Q 2 становится непроводящим. То же действие повторяется с

переменный резистор R 1 . Ток течет через батарею В CC1 , нагрузочный резистор R L и

переменный резистор R 1 в направлении, указанном

сплошная стрелка и создает напряжение на резисторе R L с указанием полярности.

Для работы класса А схемы дополнительной симметрии напряжение

Сеть делителя (не показана) используется для подачи прямого смещения на два

транзисторы, чтобы коллекторный ток не отключался в любое время.

В упрощенной схеме (рисунок выше) переменных резисторов не будет.

положение Off в любое время. Постоянный ток смещения в выходной цепи протекает

от плюсовой клеммы аккумулятора В CC2 , через

переменный резистор R 2 , переменный резистор Р 1 ,

и к отрицательной клемме аккумулятора В CC1 .

Через резистор R L ток не течет. Под этим

условиях, выходную цепь можно считать балансным мостом, плечи

моста из резисторов R 1 и R 2 и батареи V CC1 и В СС2 . Когда входной сигнал становится положительным, транзистор Вопрос 2 проводник и транзистор Q 1 проводит меньше. В упрощенной схеме переменное плечо резистора R 1 перемещается к точке 1 и к точке резистора R 2 перемещается к точке 3. Это действие приводит к дисбалансу

мост и ток течет через резистор R L в направлении пунктирной стрелки, создавая напряжение с

указана полярность. Когда входной сигнал становится отрицательным, транзистор Q 1 проводник и транзистор Q 2 проводит меньше. В упрощенной схеме переменное плечо резистора R 1 перемещается к точке 2 и к точке резистора R 2 движется к точке 4. Мост снова разбалансирован,

и ток течет через резистор R L в направлении

сплошной стрелки, производя напряжение с указанной полярностью.

В упрощенной схеме переменное плечо резистора R 1 перемещается к точке 1 и к точке резистора R 2 перемещается к точке 3. Это действие приводит к дисбалансу

мост и ток течет через резистор R L в направлении пунктирной стрелки, создавая напряжение с

указана полярность. Когда входной сигнал становится отрицательным, транзистор Q 1 проводник и транзистор Q 2 проводит меньше. В упрощенной схеме переменное плечо резистора R 1 перемещается к точке 2 и к точке резистора R 2 движется к точке 4. Мост снова разбалансирован,

и ток течет через резистор R L в направлении

сплошной стрелки, производя напряжение с указанной полярностью.

Ни в классе B, ни в классе A постоянный ток не протекает через нагрузочный резистор.

Преимущество этого свойства можно получить, подключив громкоговоритель напрямую.

вместо резистора Р Л . Громкоговоритель не будет смещен

постоянным током, протекающим через него, и поэтому искажения не произойдут.

Громкоговоритель не будет смещен

постоянным током, протекающим через него, и поэтому искажения не произойдут.

На рисунке ниже показана дополнительная схема симметрии, к которой было применено прямое смещение. Напряжение, развиваемое на диодах D 1 и D 2 обеспечивает прямое смещение для каждого транзистор. Два диода выбраны в соответствии с характеристиками транзисторы. Р 1 и R 2 обеспечить необходимый ток смещения и обычно делаются равными, чтобы смещать оба транзисторы поровну.

Схема дополнительной симметрии со смещающими диодами.

ТРАНЗИСТОРНАЯ ПОЛНАЯ СУММАРНАЯ ЦЕПЬ С ИСПОЛЬЗОВАНИЕМ 4-Х ТРАНЗИСТОРНЫХ ЗАтворов XOR И ПЕРЕДАЧИ

- Идентификатор корпуса: 212604059

title={ТРАНЗИСТОРНАЯ ПОЛНАЯ СУММИТЕЛЬНАЯ ЦЕПЬ С ИСПОЛЬЗОВАНИЕМ 4-Х ТРАНЗИСТОРНЫХ ЗАтворов XOR И ПЕРЕДАЧИ},

автор={С. Нарендра и А. Махешвара Редди, Сайед Салим и Хан Мохаммад Ханиф},

год = {2018}

}

Нарендра и А. Махешвара Редди, Сайед Салим и Хан Мохаммад Ханиф},

год = {2018}

} - С. Нарендра, А. Редди, К. М. Ханиф

- Опубликовано в 2018 г.

- Информатика

Быстрый рост наблюдается в области технологии интегральных схем (ИС). Все интегральные схемы должны быть спроектированы оптимизированным образом, чтобы они отвечали всем требованиям: были быстрее, занимали меньшую площадь и потребляли меньше энергии. Одной из схем, занимающих большую часть ИС, является АЛУ, представляющее собой комбинацию арифметических и логических блоков. Из арифметических устройств наиболее важными являются два: сумматоры и множители. В этой статье описывается эффективный метод разработки полных сумматоров…

с показателями 1-10 из 22 ссылок

Сорт Byrelevancemost, подчеркнутая бумагой,

Дизайн и анализ 10-транзисторных полных добавок с использованием новых Xor-xnor Gates

- H. Bui, A. Al-Sheraida Engineering

WCC 2000 — ICSP 2000.

2000 5-я Международная конференция по материалам обработки сигналов. 16th World Computer Congress 2000

2000 5-я Международная конференция по материалам обработки сигналов. 16th World Computer Congress 2000 - 2000

Предлагается метод создания в общей сложности 41 нового 10-транзисторного полного сумматора с использованием новых логических элементов XOR и XNOR в сочетании с существующими, которые потребляют меньше энергии на высоких частотах, в то время как три новые сумматоры стабильно потребляют в среднем на 10% меньше энергии и имеют более высокое быстродействие.

Внедрение высокоскоростного сумматора переменной задержки с эффективной площадью

- К. Вивек, С. Раджан, В. Кавита

Информатика

- 2016

Сравнительный анализ площади, энергопотребления, задержки и задержки мощности Продукт (PDP) реализован для проектирования сумматора пропуска переноса с другими сумматорами, такими как сумматор пульсирующего переноса и сумматор параллельного префикса, чтобы оценить производительность предлагаемого проекта с точки зрения логики и задержки маршрута по экспериментальным результатам.

Проектирование и анализ маломощных 10-транзисторных полных сумматоров с использованием новых вентилей XOR-XNOR

- H. Bui, Yuke Wang, Yingtao Jiang

Engineering

- 2002

- К. Каартик, К. Вивек

Информатика

- 2016

- Д. Радхакришнан

Инженерное дело

- 2001

- Jyh-Ming Wang, S. Fang, Wu-Shiung Feng

Engineering

- 1994

- S.

0 в общей сложности 41 новый 10-транзисторный полный сумматор с использованием новых логических элементов XOR и XNOR в сочетании с существующими для уменьшения потерь порогового напряжения проходных транзисторов.

Гибридная архитектура сумматора Han Carlson для снижения мощности и задержки

Работа включает сравнение различных параллельных сумматоров префиксов для получения сумматора, который может получить результат за короткий промежуток времени с потреблением. меньшей мощности и площади, которые будут получены в процессе проектирования маломощных СБИС.

Анализ производительности маломощных 1-разрядных ячеек полного сумматора CMOS

Представлен анализ производительности 1-разрядной ячейки полного сумматора после того, как сумматор был разделен на более мелкие модули и разработано несколько конструкций каждого из них. , прототипирование, моделирование и анализ.

, прототипирование, моделирование и анализ.

Низковольтный маломощный КМОП-сумматор

В последние годы маломощные схемы СБИС были определены как критическая технологическая потребность спрос на портативную бытовую электронику. В связи с этим многие…

Новые 4-транзисторные конструкции XOR и XNOR

Предлагается новый набор маломощных 4-транзисторных вентилей XOR/XNOR, который потребляет более чем в 3 раза меньше энергии, чем комплементарная реализация CMOS, и может имеют на 34% лучшую задержку распространения.

Новые эффективные конструкции для функций XOR и XNOR на уровне транзисторов

Для реализации предложены два эксклюзивных новых метода -ИЛИ и исключающее-ИЛИ функционируют на уровне транзистора. В первом методе используются некомплементарные сигнальные входы и наименьшее количество…

Нарендра и А. Махешвара Редди, Сайед Салим и Хан Мохаммад Ханиф},

год = {2018}

}

Нарендра и А. Махешвара Редди, Сайед Салим и Хан Мохаммад Ханиф},

год = {2018}

}  2000 5-я Международная конференция по материалам обработки сигналов. 16th World Computer Congress 2000

2000 5-я Международная конференция по материалам обработки сигналов. 16th World Computer Congress 2000