Полупроводниковая схемотехника

Полупроводниковая схемотехника

ОглавлениеПредисловие редактора переводаЧасть I. Основные положения 1. Пояснение применяемых величин 2.  2.1. ФИЛЬТР НИЖНИХ ЧАСТОТ 2.1.3. ДЛИТЕЛЬНОСТЬ ФРОНТА ИМПУЛЬСА И ЧАСТОТА СРЕЗА ФИЛЬТРА 2.2. ФИЛЬТР ВЕРХНИХ ЧАСТОТ 2.3. КОМПЕНСИРОВАННЫЙ ДЕЛИТЕЛЬ НАПРЯЖЕНИЯ 2.4. ПАССИВНЫЙ ПОЛОСОВОЙ RC-ФИЛЬТР 2.5. МОСТ ВИНА-РОБИНСОНА 2.6. ДВОЙНОЙ Т-ОБРАЗНЫЙ ФИЛЬТР 2.7. КОЛЕБАТЕЛЬНЫЙ КОНТУР 3. Диоды 3.2. СТАБИЛИТРОНЫ 3.3. ВАРИКАПЫ 4. Транзистор и схемы на его основе 4.2. СХЕМА С ОБЩИМ ЭМИТТЕРОМ 4.2.2. НЕЛИНЕЙНЫЕ ИСКАЖЕНИЯ 4.2.3. СХЕМА С ОБЩИМ ЭМИТТЕРОМ И ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО ТОКУ 4.2.4. ОТРИЦАТЕЛЬНАЯ ОБРАТНАЯ СВЯЗЬ ПО НАПРЯЖЕНИЮ 4.2.5. УСТАНОВКА РАБОЧЕЙ ТОЧКИ 4.3. СХЕМА С ОБЩЕЙ БАЗОЙ 4.4. СХЕМА С ОБЩИМ КОЛЛЕКТОРОМ, ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ 4.5.2. БИПОЛЯРНЫЙ ИСТОЧНИК ПИТАНИЯ 4.5.3. СХЕМА «ТОКОВОГО ЗЕРКАЛА» 4.6. СХЕМА ДАРЛИНГТОНА 4.7. ДИФФЕРЕНЦИАЛЬНЫЕ УСИЛИТЕЛИ 4.7.2. РЕЖИМ БОЛЬШОГО СИГНАЛА 4.7.3. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО ТОКУ 4.  7.4. НАПРЯЖЕНИЕ РАЗБАЛАНСА 7.4. НАПРЯЖЕНИЕ РАЗБАЛАНСА4.8. ИЗМЕРЕНИЕ НЕКОТОРЫХ ПАРАМЕТРОВ ПРИ МАЛОМ СИГНАЛЕ 4.9. ШУМЫ ТРАНЗИСТОРА 4.10. ПРЕДЕЛЬНЫЕ ПАРАМЕТРЫ 5. Полевые транзисторы 5.2. ХАРАКТЕРИСТИКИ И ПАРАМЕТРЫ МАЛЫХ СИГНАЛОВ 5.3. ПРЕДЕЛЬНЫЕ ЭЛЕКТРИЧЕСКИЕ ПАРАМЕТРЫ 5.4. ОСНОВНЫЕ СХЕМЫ ВКЛЮЧЕНИЯ 5.4.2. СХЕМА С ОБЩИМ ЗАТВОРОМ 5.4.3. СХЕМА С ОБЩИМ СТОКОМ, ИСТОКОВЫЙ ПОВТОРИТЕЛЬ 5.5. ПОЛЕВОЙ ТРАНЗИСТОР КАК СТАБИЛИЗАТОР ТОКА 5.6. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ 5.7. ПОЛЕВОЙ ТРАНЗИСТОР В КАЧЕСТВЕ УПРАВЛЯЕМОГО СОПРОТИВЛЕНИЯ 6. Операционный усилитель 6.1. СВОЙСТВА ОПЕРАЦИОННОГО УСИЛИТЕЛЯ 6.2. ПРИНЦИП ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗИ 6.3. НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ 6.4. ИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ 7. Внутренняя структура операционных усилителей 7.2. ПРОСТЕЙШИЕ СХЕМЫ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 7.3. СТАНДАРТНАЯ СХЕМА ИНТЕГРАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ 7.4. КОРРЕКЦИЯ ЧАСТОТНОЙ ХАРАКТЕРИСТИКИ  2. ПОЛНАЯ ЧАСТОТНАЯ КОРРЕКЦИЯ 2. ПОЛНАЯ ЧАСТОТНАЯ КОРРЕКЦИЯ7.4.3. ПОДСТРАИВАЕМАЯ ЧАСТОТНАЯ КОРРЕКЦИЯ 7.4.4. СКОРОСТЬ НАРАСТАНИЯ 7.4.5. КОМПЕНСАЦИЯ ЕМКОСТНОЙ НАГРУЗКИ 7.5. ИЗМЕРЕНИЕ ПАРАМЕТРОВ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 8. Простейшие переключающие схемы 8.1. ТРАНЗИСТОРНЫЙ КЛЮЧ 8.2. БИСТАБИЛЬНЫЕ РЕЛАКСАЦИОННЫЕ СХЕМЫ 8.2.2. ТРИГГЕР ШМИТТА 8.3. МОНОСТАБИЛЬНАЯ РЕЛАКСАЦИОННАЯ СХЕМА 8.4. НЕСТАБИЛЬНАЯ РЕЛАКСАЦИОННАЯ СХЕМА 9. Базовые логические схемы 9.1. ОСНОВНЫЕ ЛОГИЧЕСКИЕ ФУНКЦИИ 9.2. СОСТАВЛЕНИЕ ЛОГИЧЕСКИХ ФУНКЦИЙ 9.2.1. ТАБЛИЦА КАРНО 9.3. ПРОИЗВОДНЫЕ ОСНОВНЫХ ЛОГИЧЕСКИХ ФУНКЦИЙ 9.4.1. РЕЗИСТИВНО-ТРАНЗИСТОРНАЯ ЛОГИКА (РТЛ) 9.4.2. ДИОДНО-ТРАНЗИСТОРНАЯ ЛОГИКА (ДТЛ) 9.4.3. ТРАНЗИСТОРНО-ТРАНЗИСТОРНАЯ ЛОГИКА (ТТЛ) 9.4.4. ИНТЕГРАЛЬНАЯ ИНЖЕКЦИОННАЯ ЛОГИКА 9.4.5. ЭМИТТЕРНО-СВЯЗАННАЯ ЛОГИКА (ЭСЛ) 9.4.6. n-КАНАЛЬНАЯ МОП-ЛОГИКА 9.4.7. КОМПЛЕМЕНТАРНАЯ МОП-ЛОГИКА (КМОП) 9.4.8. ОБЗОР 9.  4.9. СПЕЦИАЛЬНЫЕ СХЕМЫ ВЫХОДНЫХ КАСКАДОВ 4.9. СПЕЦИАЛЬНЫЕ СХЕМЫ ВЫХОДНЫХ КАСКАДОВ9.5. ИНТЕГРАЛЬНЫЕ ТРИГГЕРЫ 9.5.2. ТРИГГЕРЫ ТИПА M-S (MASTER-SLAVE) 9.5.3. ДИНАМИЧЕСКИЙ ТРИГГЕР 9.6. ПОЛУПРОВОДНИКОВЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА 9.6.3. ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ МАТРИЦЫ (ПЛМ) 10. Оптоэлектронные приборы 10.1. ОСНОВНЫЕ ПОНЯТИЯ ФОТОМЕТРИИ 10.2. ФОТОРЕЗИСТОР 10.3. ФОТОДИОДЫ 10.4. ФОТОТРАНЗИСТОРЫ 10.5. СВЕТОДИОДЫ 10.6. ОПТРОНЫ Часть II. Применения 11. Линейные и нелинейные аналоговые вычислительные схемы 11.1. СХЕМА СУММИРОВАНИЯ 11.2. СХЕМЫ ВЫЧИТАНИЯ 11.2.2. СХЕМА ВЫЧИТАНИЯ НА ОПЕРАЦИОННОМ УСИЛИТЕЛЕ 11.3. БИПОЛЯРНОЕ УСИЛИТЕЛЬНОЕ ЗВЕНО 11.4. СХЕМЫ ИНТЕГРИРОВАНИЯ 11.4.1. ИНВЕРТИРУЮЩИЙ ИНТЕГРАТОР 11.4.2. ЗАДАНИЕ НАЧАЛЬНЫХ УСЛОВИЙ 11.4.3. СУММИРУЮЩИЙ ИНТЕГРАТОР 11.4.4. НЕИНВЕРТИРУЮЩИЙ ИНТЕГРАТОР 11.5. СХЕМЫ ДИФФЕРЕНЦИРОВАНИЯ 11.  6. РЕШЕНИЕ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ 6. РЕШЕНИЕ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ11.7. ФУНКЦИОНАЛЬНЫЕ ПРЕОБРАЗОВАТЕЛИ 11.7.2. ЭКСПОНЕНТА 11.7.3. ВЫЧИСЛЕНИЕ СТЕПЕННЫХ ФУНКЦИЙ С ПОМОЩЬЮ ЛОГАРИФМОВ 11.7.4. ФУНКЦИИ SIN X И COS X 11.7.5. ПЕРЕСТРАИВАЕМЫЕ ФУНКЦИОНАЛЬНЫЕ СХЕМЫ 11.8. АНАЛОГОВЫЕ СХЕМЫ УМНОЖЕНИЯ 11.8.2. УМНОЖЕНИЕ С ПОМОЩЬЮ ЛОГАРИФМИЧЕСКИХ ФУНКЦИОНАЛЬНЫХ ГЕНЕРАТОРОВ 11.8.3. СХЕМА УМНОЖЕНИЯ, ИСПОЛЬЗУЮЩАЯ ИЗМЕНЕНИЕ КРУТИЗНЫ ХАРАКТЕРИСТИКИ ТРАНЗИСТОРОВ 11.8.4. СХЕМА УМНОЖЕНИЯ С ИЗОЛИРОВАННЫМИ ЗВЕНЬЯМИ 11.8.5. БАЛАНСИРОВКА СХЕМ УМНОЖЕНИЯ 11.8.7. ПРИМЕНЕНИЕ СХЕМЫ УМНОЖЕНИЯ ДЛЯ ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНЫХ КОРНЕЙ 11.9. ПРЕОБРАЗОВАНИЕ КООРДИНАТ 11.9.2. ПРЕОБРАЗОВАНИЕ ДЕКАРТОВЫХ КООРДИНАТ В ПОЛЯРНЫЕ 12. Управляемые источники и схемы преобразования полного сопротивления 12.1. ИСТОЧНИКИ НАПРЯЖЕНИЯ, УПРАВЛЯЕМЫЕ НАПРЯЖЕНИЕМ 12.2. ИСТОЧНИКИ НАПРЯЖЕНИЯ, УПРАВЛЯЕМЫЕ ТОКОМ 12.3. ИСТОЧНИКИ ТОКА, УПРАВЛЯЕМЫЕ НАПРЯЖЕНИЕМ 12.  3.2. ИСТОЧНИКИ ТОКА С ЗАЗЕМЛЕННОЙ НАГРУЗКОЙ 3.2. ИСТОЧНИКИ ТОКА С ЗАЗЕМЛЕННОЙ НАГРУЗКОЙ12.3.3. ЭТАЛОННЫЕ ИСТОЧНИКИ ТОКА НА ТРАНЗИСТОРАХ 12.4. ИСТОЧНИКИ ТОКА, УПРАВЛЯЕМЫЕ ТОКОМ 12.5. ПРЕОБРАЗОВАТЕЛЬ ОТРИЦАТЕЛЬНОГО СОПРОТИВЛЕНИЯ (NIC) 12.6. ГИРАТОР 12.7. ЦИРКУЛЯТОР 13. Активные фильтры 13.1. ТЕОРЕТИЧЕСКОЕ ОПИСАНИЕ ФИЛЬТРОВ НИЖНИХ ЧАСТОТ 13.1.1. ФИЛЬТР БАТТЕРВОРТА 13.1.2. ФИЛЬТР ЧЕБЫШЕВА 13.1.3. ФИЛЬТРЫ БЕССЕЛЯ 13.1.4. ОБОБЩЕННОЕ ОПИСАНИЕ ФИЛЬТРОВ 13.2. ПРЕОБРАЗОВАНИЕ НИЖНИХ ЧАСТОТ В ВЕРХНИЕ 13.3. РЕАЛИЗАЦИЯ ФИЛЬТРОВ НИЖНИХ И ВЕРХНИХ ЧАСТОТ ПЕРВОГО ПОРЯДКА 13.4. РЕАЛИЗАЦИЯ ФИЛЬТРОВ НИЖНИХ И ВЕРХНИХ ЧАСТОТ ВТОРОГО ПОРЯДКА 13.4.2. ФИЛЬТР СО СЛОЖНОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.4.3. ФИЛЬТР С ПОЛОЖИТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.4.4. ФИЛЬТР НИЖНИХ ЧАСТОТ С ОМИЧЕСКОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.6. ПРЕОБРАЗОВАНИЕ ФИЛЬТРА НИЖНИХ ЧАСТОТ В ПОЛОСОВОЙ ФИЛЬТР 13.  6.1. ПОЛОСОВОЙ ФИЛЬТР ВТОРОГО ПОРЯДКА 6.1. ПОЛОСОВОЙ ФИЛЬТР ВТОРОГО ПОРЯДКА13.6.2. ПОЛОСОВОЙ ФИЛЬТР ЧЕТВЕРТОГО ПОРЯДКА 13.7. РЕАЛИЗАЦИЯ ПОЛОСОВЫХ ФИЛЬТРОВ ВТОРОГО ПОРЯДКА 13.7.2. ПОЛОСОВОЙ ФИЛЬТР СО СЛОЖНОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.7.3. ПОЛОСОВОЙ ФИЛЬТР С ПОЛОЖИТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.7.4. ПОЛОСОВОЙ ФИЛЬТР С ОМИЧЕСКОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.8. ПРЕОБРАЗОВАНИЕ ФИЛЬТРОВ НИЖНИХ ЧАСТОТ В ЗАГРАЖДАЮЩИЕ ПОЛОСОВЫЕ ФИЛЬТРЫ 13.9.1. ЗАГРАЖДАЮЩИЙ LRC-ФИЛЬТР 13.9.2. АКТИВНЫЙ ЗАГРАЖДАЮЩИЙ ФИЛЬТР С ДВОЙНЫМ Т-ОБРАЗНЫМ МОСТОМ 13.9.3. АКТИВНЫЙ ЗАГРАЖДАЮЩИЙ ФИЛЬТР С МОСТОМ ВИНА-РОБИНСОНА 13.10. ФАЗОВЫЙ ФИЛЬТР 13.10.2. РЕАЛИЗАЦИЯ ФАЗОВОГО ФИЛЬТРА ПЕРВОГО ПОРЯДКА 13.10.3. РЕАЛИЗАЦИЯ ФАЗОВОГО ФИЛЬТРА ВТОРОГО ПОРЯДКА 13.11. ПЕРЕСТРАИВАЕМЫЙ УНИВЕРСАЛЬНЫЙ ФИЛЬТР 14. Широкополосные усилители 14.1. ЗАВИСИМОСТЬ КОЭФФИЦИЕНТА УСИЛЕНИЯ ПО ТОКУ ОТ ЧАСТОТЫ 14.2. ВЛИЯНИЕ ВНУТРЕННИХ ЕМКОСТЕЙ ТРАНЗИСТОРА И ЕМКОСТЕЙ МОНТАЖА 14.  3. КАСКОДНАЯ СХЕМА 3. КАСКОДНАЯ СХЕМА14.4. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ КАК ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ 14.5.2. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ИНВЕРТОРОМ 14.5.3. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С КОМПЛЕМЕНТАРНОЙ КАСКОДНОЙ СХЕМОЙ 14.5.4. ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ 14.6. ШИРОКОПОЛОСНЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ 14.6.2. ДВУХТАКТНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ 14.7. ШИРОКОПОЛОСНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ 15. Усилители мощности 15.1. ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ КАК УСИЛИТЕЛЬ МОЩНОСТИ 15.2. КОМПЛЕМЕНТАРНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ 15.2.2. КОМПЛЕМЕНТАРНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ В РЕЖИМЕ AB 15.2.3. СПОСОБЫ ЗАДАНИЯ НАПРЯЖЕНИЯ СМЕЩЕНИЯ 15.3. СХЕМЫ ОГРАНИЧЕНИЯ ТОКА 15.4. КОМПЛЕМЕНТАРНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ ПО СХЕМЕ ДАРЛИНГТОНА 15.6. СХЕМЫ ПРЕДВАРИТЕЛЬНЫХ УСИЛИТЕЛЕЙ НАПРЯЖЕНИЯ 15.7. ПОВЫШЕНИЕ НАГРУЗОЧНОЙ СПОСОБНОСТИ ИНТЕГРАЛЬНЫХ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 16. Источники питания 16.  1. СВОЙСТВА СЕТЕВЫХ ТРАНСФОРМАТОРОВ 1. СВОЙСТВА СЕТЕВЫХ ТРАНСФОРМАТОРОВ16.2. ВЫПРЯМИТЕЛИ 16.2.1. ОДНОПОЛУПЕРИОДНЫЙ ВЫПРЯМИТЕЛЬ 16.2.2. МОСТОВОЙ ВЫПРЯМИТЕЛЬ 16.2.3. МОСТОВОЙ ВЫПРЯМИТЕЛЬ ДЛЯ ДВУХ СИММЕТРИЧНЫХ ОТНОСИТЕЛЬНО ЗЕМЛИ ВЫХОДНЫХ НАПРЯЖЕНИЙ 16.3. ПОСЛЕДОВАТЕЛЬНАЯ СТАБИЛИЗАЦИЯ НАПРЯЖЕНИЯ 16.3.2. СХЕМА С РЕГУЛИРУЮЩИМ УСИЛИТЕЛЕМ 16.3.3. ИНТЕГРАЛЬНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ 16.3.4. СТАБИЛИЗАТОР С МАЛЫМ НАПРЯЖЕНИЕМ ПОТЕРЬ 16.3.5. СТАБИЛИЗАЦИЯ НАПРЯЖЕНИЙ, СИММЕТРИЧНЫХ ОТНОСИТЕЛЬНО ЗЕМЛИ 16.3.6. СТАБИЛИЗАТОР НАПРЯЖЕНИЯ С ИЗМЕРИТЕЛЬНЫМИ ВЫВОДАМИ 16.3.7. ЛАБОРАТОРНЫЕ ИСТОЧНИКИ ПИТАНИЯ 16.3.8. ОКОНЕЧНЫЙ КАСКАД ЛАБОРАТОРНОГО ИСТОЧНИКА ПИТАНИЯ С БОЛЬШОЙ ВЫХОДНОЙ МОЩНОСТЬЮ 16.4. ПОЛУЧЕНИЕ ОПОРНОГО НАПРЯЖЕНИЯ 16.4.2. ПОЛУЧЕНИЕ МАЛЫХ ОПОРНЫХ НАПРЯЖЕНИЙ 16.5. ИМПУЛЬСНЫЕ РЕГУЛЯТОРЫ НАПРЯЖЕНИЯ 16.5.2. ПЕРВИЧНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ 17. Аналоговые коммутаторы и компараторы 17.2. ЭЛЕКТРОННЫЕ КОММУТАТОРЫ 17.2.2. ДИОДНЫЙ КОММУТАТОР 17.2.3. КОММУТАТОР НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ 17.  3. АНАЛОГОВЫЕ КОММУТАТОРЫ НА БАЗЕ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 3. АНАЛОГОВЫЕ КОММУТАТОРЫ НА БАЗЕ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ17.3.2. КОММУТАТОР НА ПОЛЕВОМ ТРАНЗИСТОРЕ С ПЕРЕМЕНОЙ ЗНАКА ВЫХОДНОГО НАПРЯЖЕНИЯ 17.3.3. КОММУТАТОР НА БАЗЕ ДИФФЕРЕНЦИАЛЬНОГО УСИЛИТЕЛЯ 17.4. АНАЛОГОВЫЕ КОММУТАТОРЫ С ПАМЯТЬЮ 17.5. КОМПАРАТОРЫ 17.5.2. КОМПАРАТОР С ПРЕЦИЗИОННЫМ ВЫХОДНЫМ НАПРЯЖЕНИЕМ 17.5.3. ДВУХПОРОГОВЫЙ КОМПАРАТОР 17.6. ТРИГГЕР ШМИТТА 17.6.1. ИНВЕРТИРУЮЩИЙ ТРИГГЕР ШМИТТА 17.6.2. НЕИНВЕРТИРУЮЩИЙ ТРИГГЕР ШМИТТА 17.6.3. ПРЕЦИЗИОННЫЙ ТРИГГЕР ШМИТТА 18. Генераторы сигналов 18.1. LC-ГЕНЕРАТОРЫ 18.1.2. ГЕНЕРАТОР С ТРАНСФОРМАТОРНОЙ СВЯЗЬЮ (СХЕМА МАЙССНЕРА) 18.1.3. ТРЕХТОЧЕЧНАЯ СХЕМА С ИНДУKТИВНОЙ ОБРАТНОЙ СВЯЗЬЮ (СХЕМА ХАРТЛИ) 18.1.4. ТРЕХТОЧЕЧНАЯ СХЕМА С ЕМКОСТНОЙ ОБРАТНОЙ СВЯЗЬЮ (СХЕМА КОЛПИТЦА) 18.1.5. LC-ГЕНЕРАТОР С ЭМИТТЕРНОЙ СВЯЗЬЮ 18.1.6. ДВУХТАКТНЫЕ ГЕНЕРАТОРЫ 18.2. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ 18.2.1. ЭЛЕКТРИЧЕСКИЕ СВОЙСТВА КВАРЦЕВОГО РЕЗОНАТОРА 18.2.2. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ С LC-КОЛЕБАТЕЛЬНЫМ КОНТУРОМ 18.  2.3. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ БЕЗ LC-КОНТУРА 2.3. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ БЕЗ LC-КОНТУРА18.3. СИНУСОИДАЛЬНЫЕ RC-ГЕНЕРАТОРЫ 18.3.2. МОДЕЛИРОВАНИЕ ДИФФЕРЕНЦИАЛЬНОГО УРАВНЕНИЯ СИНУСОИДАЛЬНЫХ КОЛЕБАНИЙ 18.4. ГЕНЕРАТОРЫ СИГНАЛОВ СПЕЦИАЛЬНОЙ ФОРМЫ (ФУНКЦИОНАЛЬНЫЕ ГЕНЕРАТОРЫ) 18.4.2. ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР С УПРАВЛЯЕМОЙ ЧАСТОТОЙ ВЫХОДНОГО СИГНАЛА 18.4.3. ВЫСОКОЧАСТОТНЫЙ ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР 18.5. МУЛЬТИВИБРАТОРЫ 18.5.1. НИЗКОЧАСТОТНЫЕ МУЛЬТИВИБРАТОРЫ 18.5.2. ВЫСОКОЧАСТОТНЫЕ МУЛЬТИВИБРАТОРЫ 19. Комбинационные логические схемы 19.1. ПРЕОБРАЗОВАТЕЛИ КОДОВ 19.1.2. ДВОИЧНО-ДЕСЯТИЧНЫЕ КОДЫ 19.1.3. КОД ГРЕЯ 19.2. МУЛЬТИПЛЕКСОР И ДЕМУЛЬТИПЛЕКСОР 19.3. КОМБИНАЦИОННОЕ УСТРОЙСТВО СДВИГА 19.4. КОМПАРАТОРЫ 19.5. СУММАТОРЫ 19.5.1. ПОЛУСУММАТОР 19.5.2. ПОЛНЫЙ СУММАТОР 19.5.3. СУММАТОРЫ С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ 19.5.4. СЛОЖЕНИЕ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ 19.5.5. ВЫЧИТАНИЕ 19.5.6. СЛОЖЕНИЕ ЧИСЕЛ С ЛЮБЫМИ ЗНАКАМИ 19.6. УМНОЖИТЕЛИ 19.7. ЦИФРОВЫЕ ФУНКЦИОНАЛЬНЫЕ ПРЕОБРАЗОВАТЕЛИ 20.  Интегральные схемы со структурами последовательностного типа Интегральные схемы со структурами последовательностного типа20.1. ДВОИЧНЫЕ СЧЕТЧИКИ 20.1.1. АСИНХРОННЫЙ (ПОСЛЕДОВАТЕЛЬНЫЙ) СЧЕТЧИК 20.1.2. СИНХРОННЫЙ (ПАРАЛЛЕЛЬНЫЙ) СЧЕТЧИК 20.2. ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК В КОДЕ 8421 20.2.1. АСИНХРОННЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК 20.2.2. СИНХРОННЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК 20.3. СЧЕТЧИК С ПРЕДВАРИТЕЛЬНОЙ УСТАНОВКОЙ 20.4. РЕГИСТРЫ СДВИГА 20.4.2. КОЛЬЦЕВОЙ РЕГИСТР 20.4.3. РЕГИСТР СДВИГА С ПАРАЛЛЕЛЬНЫМ ВВОДОМ 20.4.4. РЕГИСТР СДВИГА С ПЕРЕКЛЮЧАЕМЫМ НАПРАВЛЕНИЕМ СДВИГА 20.5. ПОЛУЧЕНИЕ ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ 20.6. ПЕРВОНАЧАЛЬНАЯ ОБРАБОТКА АСИНХРОННОГО СИГНАЛА 20.6.2. СИНХРОНИЗАЦИЯ ИМПУЛЬСОВ 20.6.3. СИНХРОННЫЙ ОДНОВИБРАТОР 20.6.4. СИНХРОННЫЙ ДЕТЕКТОР ИЗМЕНЕНИЙ 20.6.5. СИНХРОННЫЙ ТАКТОВЫЙ ПЕРЕКЛЮЧАТЕЛЬ 20.7. СИСТЕМАТИЧЕСКИЙ СИНТЕЗ ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМ 20.7.2. ПРИМЕР СИНТЕЗА ПЕРЕКЛЮЧАЕМОГО СЧЕТЧИКА 20.7.3. СОКРАЩЕНИЕ ЕМКОСТИ ПАМЯТИ 21. Микро-ЭВМ 21.1. ОСНОВНАЯ СТРУКТУРА МИКРО-ЭВМ 21.  2. ПРИНЦИП ДЕЙСТВИЯ МИКРОПРОЦЕССОРА 2. ПРИНЦИП ДЕЙСТВИЯ МИКРОПРОЦЕССОРА21.3. НАБОР КОМАНД 21.4. ОТЛАДОЧНЫЕ СРЕДСТВА 21.5. ОБЗОР МИКРОПРОЦЕССОРОВ РАЗЛИЧНОГО ТИПА 21.6. МОДУЛЬНОЕ ПОСТРОЕНИЕ МИКРО-ЭВМ 21.7. ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА 21.7.1. ПАРАЛЛЕЛЬНЫЙ ИНТЕРФЕЙС 21.7.2. ПОСЛЕДОВАТЕЛЬНЫЙ ИНТЕРФЕЙС 21.7.3. ИНТЕРФЕЙС МАГИСТРАЛИ «ОБЩАЯ ШИНА» 21.7.4. ПРОГРАММИРУЕМЫЙ СЧЕТЧИК 21.7.5. ПОДКЛЮЧЕНИЕ ПЕРИФЕРИЙНЫХ МОДУЛЕЙ СЕМЕЙСТВА 8080 К МАГИСТРАЛЯМ СЕМЕЙСТВА 6800 21.7.6. ОБЗОР ПЕРИФЕРИЙНЫХ УСТРОЙСТВ 21.8. МИНИМАЛЬНЫЕ СИСТЕМЫ 21.8.2. ОДНОКРИСТАЛЬНАЯ МИКРО-ЭВМ 22. Цифровые фильтры 22.1. ТЕОРЕМА О ДИСКРЕТИЗАЦИИ (ТЕОРЕМА О ВЫБОРКАХ) 22.1.2. ПРАКТИЧЕСКИЕ СООБРАЖЕНИЯ 22.2. ЦИФРОВАЯ ФУНКЦИЯ ПЕРЕДАЧИ ФИЛЬТРА 22.3. БИЛИНЕЙНОЕ ПРЕОБРАЗОВАНИЕ 22.4. РЕАЛИЗАЦИЯ ЦИФРОВЫХ ФИЛЬТРОВ 22.4.2. СТРУКТУРА ЦИФРОВЫХ ФИЛЬТРОВ ВТОРОГО ПОРЯДКА 22.4.3. ПРАКТИЧЕСКИЕ СООБРАЖЕНИЯ 23. Передача данных и индикация 23.1. СОЕДИНИТЕЛЬНЫЕ ЛИНИИ 23.2. ЗАЩИТА ДАННЫХ 23.2.2. КОД ХЕММИНГА 23.  3. СТАТИЧЕСКИЕ ЦИФРОВЫЕ ИНДИКАТОРЫ 3. СТАТИЧЕСКИЕ ЦИФРОВЫЕ ИНДИКАТОРЫ23.3.1. ДВОИЧНЫЕ ИНДИКАТОРЫ НА СВЕТОДИОДАХ 23.3.2. ДЕКАДНЫЕ ИНДИКАТОРЫ 23.3.3. ИНДИКАЦИЯ В ШЕСТНАДЦАТЕРИЧНОМ КОДЕ 23.4. МУЛЬТИПЛЕКСНЫЕ ИНДИКАТОРЫ 23.4.1. МНОГОРАЗРЯДНЫЕ 7-СЕГМЕНТНЫЕ ИНДИКАТОРЫ 23.4.2. МАТРИЦА ТОЧЕК 24. Цифро-аналоговые и аналого-цифровые преобразователи 24.1. СХЕМОТЕХНИЧЕСКИЕ ПРИНЦИПЫ ЦА-ПРЕОБРАЗОВАТЕЛЕЙ 24.1.2. ЦА-ПРЕОБРАЗОВАТЕЛЬ С ПЕРЕКИДНЫМИ КЛЮЧАМИ 24.1.3. РЕЗИСТИВНАЯ МАТРИЦА ПОСТОЯННОГО ИМПЕДАНСА (МАТРИЦА ТИПА R-2R) 24.1.4. РЕЗИСТИВНАЯ МАТРИЦА ДЛЯ ДЕКАДНЫХ ПРЕОБРАЗОВАТЕЛЕЙ 24.2. ПОСТРОЕНИЕ ЦА-ПРЕОБРАЗОВАТЕЛЕЙ С ЭЛЕКТРОННЫМИ КЛЮЧАМИ 24.2.2. ЦА-ПРЕОБРАЗОВАТЕЛЬ С ТОКОВЫМИ КЛЮЧАМИ 24.3. ЦА-ПРЕОБРАЮВАТЕЛИ ДЛЯ СПЕЦИАЛЬНЫХ ПРИМЕНЕНИЙ 24.3.2. ЦА-ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ДЕЛЕНИЯ 24.3.3. ЦА-ПРЕОБРАЗОВАТЕЛЬ КАК ГЕНЕРАТОР ФУНКЦИЙ 24.4. ОСНОВНЫЕ ПРИНЦИПЫ АЦ-ПРЕОБРАЗОВАНИЯ 24.5. ТОЧНОСТЬ АЦ-ПРЕОБРАЗОВАТЕЛЕЙ 24.6. ПОСТРОЕНИЕ АЦ-ПРЕОБРАЗОВАТЕЛЕЙ 25. Измерительные схемы 25.  1. ИЗМЕРЕНИЕ НАПРЯЖЕНИЙ 1. ИЗМЕРЕНИЕ НАПРЯЖЕНИЙ25.1.2. ИЗМЕРЕНИЕ РАЗНОСТИ ПОТЕНЦИАЛОВ 25.1.3. ИЗОЛИРОВАННЫЙ УСИЛИТЕЛЬ 25.2. ИЗМЕРЕНИЕ ТОКА 25.2.1. ИЗОЛИРОВАННЫЕ ОТ ЗЕМЛИ АМПЕРМЕТРЫ С МАЛЫМ ПАДЕНИЕМ НАПРЯЖЕНИЯ 25.2.2. ИЗМЕРЕНИЕ ТОКА ПРИ ВЫСОКОМ ПОТЕНЦИАЛЕ 25.3. ИЗМЕРИТЕЛЬНЫЙ ВЫПРЯМИТЕЛЬ 25.3.2. ИЗМЕРЕНИЕ ЭФФЕКТИВНОГО ЗНАЧЕНИЯ 25.3.3. ИЗМЕРЕНИЕ АМПЛИТУДНЫХ ЗНАЧЕНИЙ 25.3.4. СИНХРОННЫЙ ДЕТЕКТОР 26. Электронные регуляторы 26.2. ТИПЫ РЕГУЛЯТОРОВ 26.2.1. П-РЕГУЛЯТОР 26.2.2. ПИ-РЕГУЛЯТОР 26.2.3. ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР 26.2.4. НАСТРАИВАЕМЫЕ ПИД-РЕГУЛЯТОРЫ 26.3. УПРАВЛЕНИЕ НЕЛИНЕЙНЫМИ ОБЪЕКТАМИ 26.4. ОТСЛЕЖИВАЮЩАЯ СИНХРОНИЗАЦИЯ (АВТОПОДСТРОЙКА) 26.4.1. ЭЛЕМЕНТЫ ВЫБОРКИ-ХРАНЕНИЯ В КАЧЕСТВЕ ФАЗОВОГО ДЕТЕКТОРА 26.4.2. СИНХРОННЫЙ ВЫПРЯМИТЕЛЬ В КАЧЕСТВЕ ФАЗОВОГО ДЕТЕКТОРА 26.4.3. ЧАСТОТНО-ЧУВСТВИТЕЛЬНЫЙ ФАЗОВЫЙ ДЕТЕКТОР 26.4.4. ФАЗОВЫЙ ДЕТЕКТОР С ПРОИЗВОЛЬНО УВЕЛИЧИВАЕМЫМ ДИАПАЗОНОМ ИЗМЕРЕНИЙ 26.4.5. ФАЗОРЕГУЛЯТОР В КАЧЕСТВЕ ПЕРЕМНОЖИТЕЛЯ ЧАСТОТ |

39.

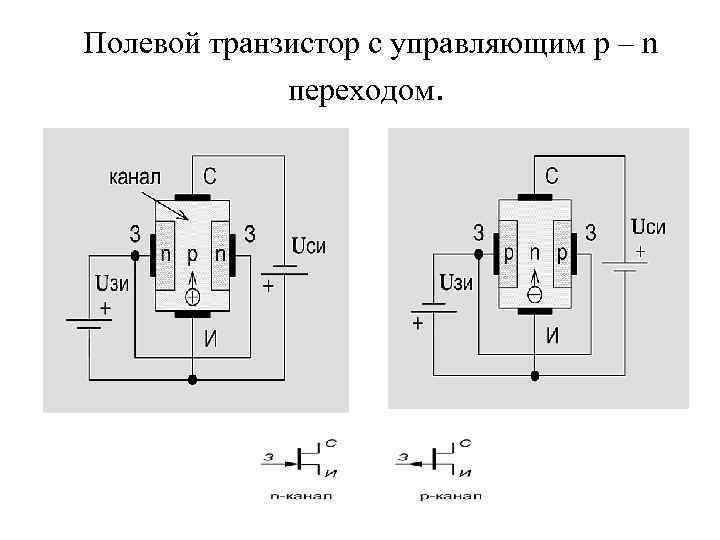

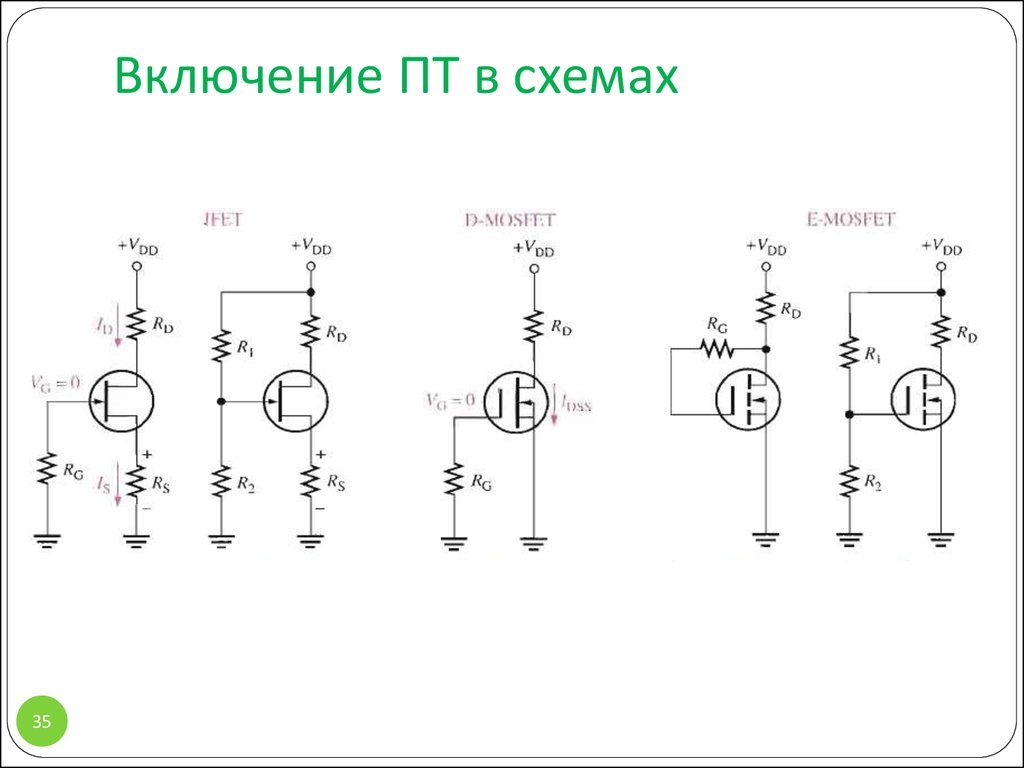

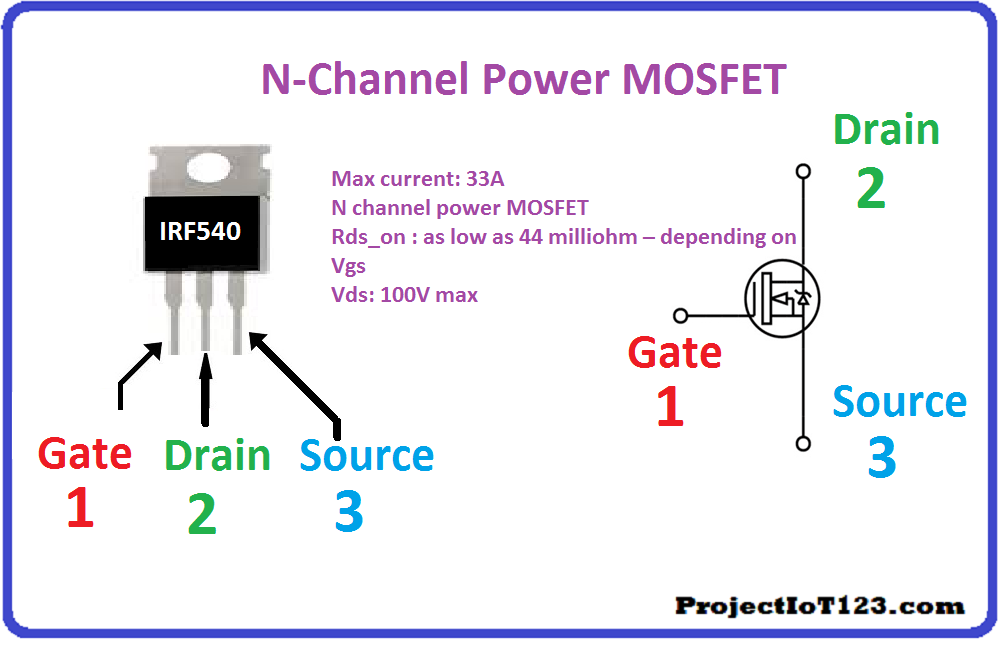

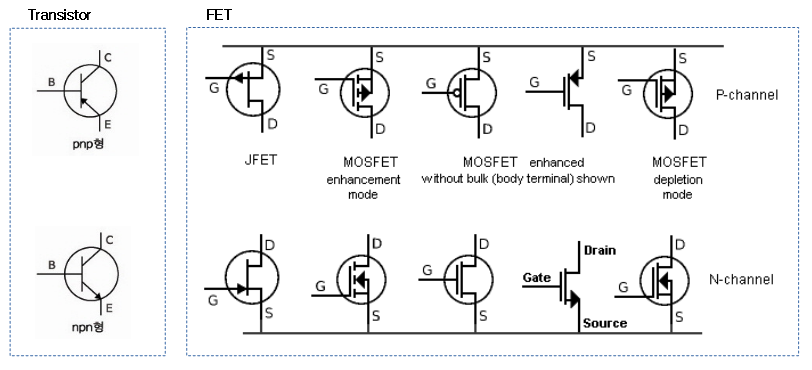

Схемы включения полевого транзистора

Схемы включения полевого транзистораполевые транзисторы используют в трех основных схемах включения: с общим истоком (ОИ), общим стоком (ОС) и общим затвором (ОЗ). Усилительный каскад по схеме ОИ аналогичен схеме ОЭ. Он дает большое усиление тока и мощности и инвертирует фазу входного напряжения. Коэффициент усиления каскада по напряжению приближенно равен Ku= SRH.

Схема ОС подобна эмиттерному повторителю и называется истоковым повторителем. Коэффициент усиления каскада по напряжению близок к единице. Усилитель по схеме ОС имеет сравнительно небольшое выходное сопротивление и большое входное сопротивление. Кроме того, здесь значительно уменьшена входная емкость, что способствует увеличению входного сопротивления на высоких частотах.

Схема

ОЗ аналогична схеме ОБ. Схема не усиливает

тока, поэтому

коэффициент усиления по мощности во

много раз меньше, чем в схеме ОИ. Эта

схема имеет малое входное сопротивление,

так как входным током является ток

стока. Фаза напряжения

при усилении не инвертируется.

Фаза напряжения

при усилении не инвертируется.

40. Формальная схема замещения пол транз и ее дифф параметры

Полевой транзистор, как и биполярный, можно представить в виде активного четырехполюсника и при работе с сигналами малых амплитуд характеризовать формальной схемой замещения и ее дифференциальными параметрами. На практике в качестве дифференциальных параметров используют у-параметры, в общем случае это комплексные функции частоты, а в частности на низкой частоте, это вещественные величины. К ним относятся:

1) крутизна стокозатворной ВАХ полевого транзистора ;

2) входная проводимость полевого транзистора ,на низких частотах близка к нулю;

3) выходная проводимость

Часто

при расчетах схем на полевых транзисторах

используют выходное сопротивление Ri = 1/Y22,

которое для области насыщения у маломощных

транзисторов равно 10 — 100 кОм. Кроме того,

полевой транзистор можно характеризовать

статическим коэффициентом усиления

Кроме того,

полевой транзистор можно характеризовать

статическим коэффициентом усиления

Здесь знак минус означает, что для сохранения неизменной величины тока стока при определении знаки приращений напряжений Ucи и Uзи должны быть разными.

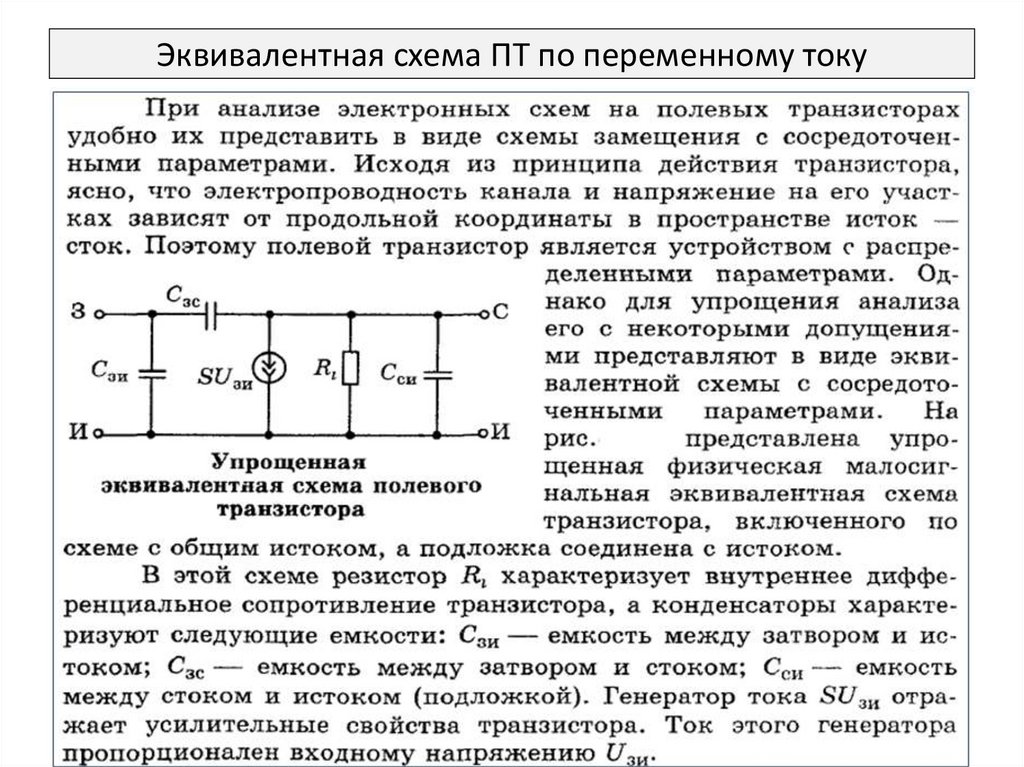

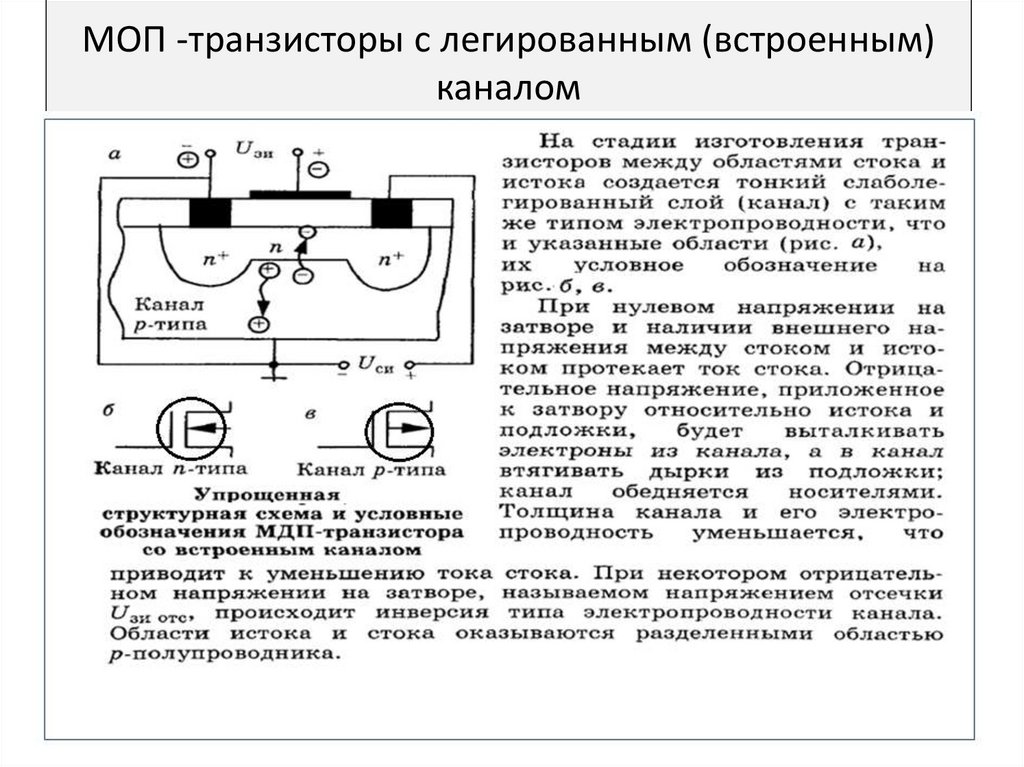

41. Физическая эквивалентная схема полевого транзистора

Для описания частотных свойств полевого транзистора в широком диапазоне частот применяется физическая эквивалентная схема (рис.4.12).

Усилительные

свойства транзистора, имеющего крутизну

S, отражаются идеальным генератором

тока SUmзи.

Ri = 1/Y22 — выходное сопротивление полевого

транзистора. rс rк,

rи – это обьемные сопротивления области

стока, канала и истока. В эквивалентной

схеме учтены также емкости. В транзисторе

с управляющим р-n-переходом

емкость Сси в основном определяется емкостью между

электродами стока и истока, а в МДП-

транзисторе емкость Сси определяется еще и емкостью р-n- перехода

между подложкой и областями истока и

стока. Поэтому в МДП- транзисторах

Поэтому в МДП- транзисторах

е мкость Сси существенно выше, чем в транзисторах с р-n- переходом. Поскольку полевой транзистор работает с обратно смещенным р-n- переходом, то емкости Сзи и Сзс являются барьерными. Для МДП- транзистора — это емкости затвора относительно областей истока и стока. Ориентировочно, для маломощных транзисторов различного типа Сзи=2-15 пФ, Сзс=0,3-10 пФ; для МДП – транзисторов Сси=315 пФ; для транзисторов с управляющим р-n

– переходом емкость Сси, как правило, не превышает 1 пФ.

Рассмотренная

схема справедлива до частоты, равной

примерно 0,7fг.

Частота fг на которой коэффициент усиления по

мощности в режиме согласования по входу

и выходу равен единице, называется

предельной частотой генерации транзистора.

Предельная частота генерации полевого

транзистора определяется как:

,

здесь rИ — сопротивление неуправляемого участка

канала вблизи области истока, зависящее

от тока насыщения и, как правило, не

превышающее нескольких десятков ом.

Используя схему рис.4.12, можно найти у — параметры полевого транзистора:

3нак минус в формуле для означает, что ток во входной цепи, вызванный напряжением Uси, вследствие обратной связи в транзисторе, имеет направление, противоположное тому, которое принято положительным для тока затвора.

[PDF] Моделирование и симуляция схем переключения полевых транзисторов с изолированным затвором

- title={Моделирование и симуляция схем включения полевых транзисторов с изолированным затвором},

автор = {Гарольд Шичман и Дэвид А. Ходжес},

journal={Журнал IEEE о твердотельных схемах},

год = {1968},

объем = {3},

страницы = {285-289}

}

- Х. Шичман, Д. Ходжес

- Опубликовано 1 сентября 1968 г.

- Физика

- IEEE Journal of Solid-state Circuits

Описана новая эквивалентная схема полевого транзистора с изолированным затвором (IGFET).

[] Ключевой результат В качестве примера практического применения показаны результаты моделирования для ячейки памяти IGFET на интегральной схеме.

[] Ключевой результат В качестве примера практического применения показаны результаты моделирования для ячейки памяти IGFET на интегральной схеме. Просмотр через Publisher

ece.jhu.edu

Усовершенствованная статическая модель полевого транзистора для моделирования интегральных схем

- В. Вонг, Дж. Лиоу, Дж. Прентис

Физика

- 1990

Разработана статическая модель полевого транзистора (JFET) для моделирования интегральных схем. Модель охватывает поведение областей линейного тока и тока насыщения без…

Улучшенная модель эквивалентной схемы GaAs MESFET для аналоговых интегральных схем

- L. Larson

Инженерия, информатика

- 1987

Описана усовершенствованная модель эквивалентной схемы полевого транзистора на основе арсенида галлия (GaAs), оптимизированная для проектирования и анализа прецизионных аналоговых интегральных схем.

Эти схемы влекут за собой…

Эти схемы влекут за собой…Модель MESFET для использования в разработке интегральных схем GaAs

- W. Curtice

Engineering

- 1980

Представлена обычная модель MESFET, пригодная для использования во времени программы моделирования доменных цепей. Параметры модели оцениваются либо по экспериментальным данным, либо по более…

Статические модели полевых транзисторов с большим сигналом

- B.D. Wedlock

Физика

- 1970

Серия статических полевых транзисторов с большим сигналом состоит из знакомых моделей полевых транзисторов (FET). блоки плюс новый нелинейный элемент, идеальный полевой диод. The…

Унифицированная статическая модель полевого транзистора с четырьмя выводами для моделирования цепей

- W. Wong, J. Liou, J. Prentice 9

- S.

Hengen, M. Alt, G. Hernandez-Sosa, J. Giehl, U. Lemmer, Norman0 Mechau

Hengen, M. Alt, G. Hernandez-Sosa, J. Giehl, U. Lemmer, Norman0 Mechau Engineering

- 2014

- W. Curtice

Инженерная инженерия

- 1988

- Л. Бисдунис, О. Куфопавлу, К. Гутис, С. Николаидис

Инженерное дело

Труды по проектированию, автоматизации и испытаниям в Европе

9000

- A. Parker, D.J. Skellern

Physics

1991., Международный симпозиум IEEE по схемам и системам

- 1991

- Hye-Ran Cha, O. Kwon

Engineering

- 2000

GAAS MESFET MODELING и нелинейный CAD

ЭКСКОЛЬНАЯ СЕМЕРИ GaAs MESFET. Использование модели большого сигнала в интерактивной программе для анализа усилителя…

Моделирование реакции переключения КМОП-инвертора для субмикронных устройств

Представлена точная аналитическая модель для оценки задержки КМОП-инвертора в субмикронном режиме, которая ясно показывает влияние конструктивных характеристик инвертора, емкости нагрузки и наклона формы входного сигнала, управляющего инверторами.

на задержку распространения.

на задержку распространения.Моделирование устройства GaAs для проектирования и применения

Рассмотрены характеристики устройств, включенные в доступные модели MESFET, и предложены расширения модели для повышения точности в широком диапазоне условий. Использование модели показано в…

Аналитическая модель шума одновременного переключения в КМОП-системах

Представлена точная и аналитическая модель шума одновременного переключения (SSN) на линиях заземления в схемах CMOS. Эта модель может вычислять SSN для случая, когда переключаются только некоторые драйверы и…

- 1961

Аннотация Представлена теория конструкции поверхностных полевых транзисторов с изолированным затвором. Показано, что при близких размерах поверхностный полевой транзистор имеет частотную характеристику…

Показано, что при близких размерах поверхностный полевой транзистор имеет частотную характеристику…

Компьютерные модели полевого транзистора

- Б. Д. Робертс, К. Харборт

Информатика

- 1967

- C.

Sah, H. Pao

Sah, H. Pao Физика

- 1966

- И. Сандберг, Х. Шичман

Математика

- 1968

- Ф. Куо

Информатика

- 1966

- Д. Фрохман-Бенчковски, Л. Вадаш

Информатика

- 1968

Проц. IEEE,

- 1921

Englewood Cliffs, NJ: Prent ice-Hall,

190014- Пожалуйста, свяжитесь с нами, чтобы сообщить, что эта страница отсутствует, или используйте поле выше, чтобы продолжить поиск

- Наша страница «О нас» содержит дополнительную информацию о сайте, на котором вы находитесь, WhatIs.

com.

com. - Посетите нашу домашнюю страницу и просмотрите наши технические темы

- Многопротокольная коммутация по меткам (MPLS)

Многопротокольная коммутация по меткам (MPLS) — это механизм коммутации, используемый в глобальных сетях (WAN).

- компьютерная сеть

Компьютерная сеть представляет собой группу взаимосвязанных узлов или вычислительных устройств, которые обмениваются данными и ресурсами друг с другом.

- Оптимизация WAN (ускорение WAN)

Оптимизация глобальной сети, также известная как ускорение глобальной сети, представляет собой набор технологий и методов, используемых для улучшения …

- трехфакторная аутентификация (3FA)

Трехфакторная аутентификация (3FA) — это использование учетных данных для подтверждения личности из трех отдельных категорий аутентификации.

..

.. - кибершпионаж

Кибершпионаж (кибершпионаж) — вид кибератаки, которую злоумышленники осуществляют против предприятия или правительства…

- управление доступом на основе ролей (RBAC)

Управление доступом на основе ролей (RBAC) — это метод ограничения доступа к сети на основе ролей отдельных пользователей в пределах …

- системы, основанные на знаниях (KBS)

Системы, основанные на знаниях (KBS), — это компьютерные программы, которые используют централизованное хранилище данных, известное как база знаний, для …

- Закон Сарбейнса-Оксли

Закон Сарбейнса-Оксли от 2002 года — это федеральный закон, устанавливающий широкомасштабные аудиторские и финансовые правила для публичных компаний.

- устав проекта

Устав проекта — это формальный краткий документ, в котором указывается, что проект существует, и предоставляется руководителям проекта письменные полномочия на.

..

.. - вовлечения сотрудников

Вовлеченность сотрудников — это эмоциональная и профессиональная связь, которую сотрудник испытывает к своей организации, коллегам и работе.

- кадровый резерв

Кадровый резерв — это база данных кандидатов на работу, которые могут удовлетворить немедленные и долгосрочные потребности организации.

- разнообразие, равенство и инклюзивность (DEI)

Разнообразие, справедливость и инклюзивность — термин, используемый для описания политики и программ, которые способствуют представительству и …

- представитель по развитию продаж (SDR)

Представитель по развитию продаж (SDR) — это лицо, занимающееся поиском, перемещением и квалификацией потенциальных клиентов через .

- 6 А 90 нелинейная представлена модель полевого транзистора для использования в приложениях с большим сигналом, и получено несколько кусочно-линейных моделей, подходящих для использования с программой анализа электронных цепей (ECAP).

Концепция управления зарядом в виде эквивалентных схем, представляющая собой связующее звено между классическими моделями диодов и транзисторов с большим сигналом концепцию управления зарядом можно рассматривать как особую форму модели Линвилла для полупроводников. Вместо математических инструментов модели управления зарядом становятся…

Влияние фиксированного объемного заряда на характеристики транзисторов металл-оксид-полупроводник

Теория характеристик МОП-транзисторов разработана на основе модели, в которой оба объемных заряда обусловлены ионизированной примесью в полупроводнике подложка и разность…

Численное интегрирование систем жестких нелинейных дифференциальных уравнений

Например, при проектировании транзисторных схем часто необходимо получить численное решение системы нелинейных обыкновенных дифференциальных уравнений. В некоторых случаях…

Сетевой анализ на цифровом компьютере

Методы и программы для лестничных сетей, ячеистого и узлового анализа, анализа топологии сети, состояния электронных схем Обсуждаются анализ переменных, n-портовый гибридный матричный анализ и анализ нелинейных цепей.

Компьютерное проектирование и характеристика МОП-интегральных схем

Компьютерные модели полевых транзисторов;

Итерационные методы решения уравнений

404: Страница не найдена

Страница, которую вы пытались открыть по этому адресу, похоже, не существует. Обычно это результат плохой или устаревшей ссылки. Мы извиняемся за любые неудобства.

Что я могу сделать сейчас?

Если вы впервые посещаете TechTarget, добро пожаловать! Извините за обстоятельства, при которых мы встречаемся. Вот куда вы можете пойти отсюда:

ПоискПросмотр по категории

Сеть

Безопасность

ИТ-директор

HRSoftware

Отдел обслуживания клиентов

[] Ключевой результат В качестве примера практического применения показаны результаты моделирования для ячейки памяти IGFET на интегральной схеме.

[] Ключевой результат В качестве примера практического применения показаны результаты моделирования для ячейки памяти IGFET на интегральной схеме.  Эти схемы влекут за собой…

Эти схемы влекут за собой…