ЛОГИЧЕСКИЕ МИКРОСХЕМЫ ТТЛ 74хх СЕРИИ И ИХ ОТЕЧЕСТВЕННЫЕ АНАЛОГИ

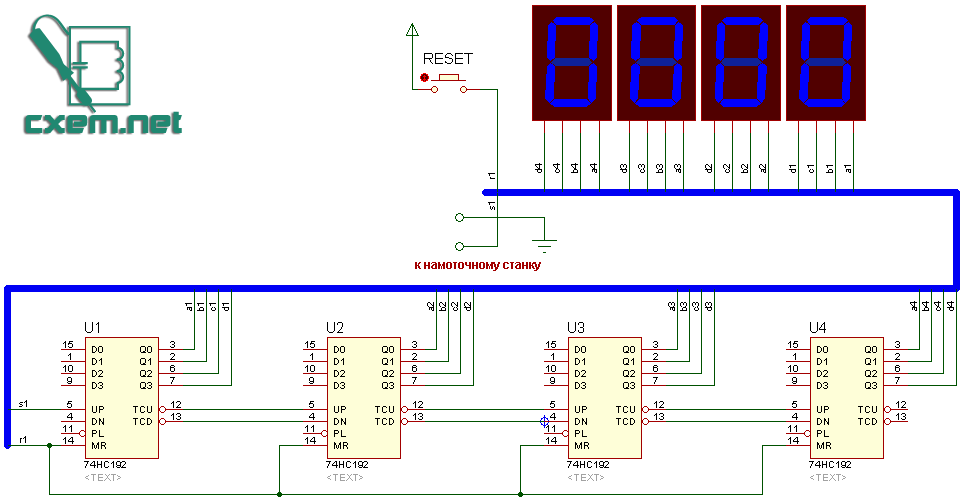

Несмотря на появление микропроцессоров, микроконтроллеров и других программируемых схем и постоянное расширение сфер их применения, потребность в микросхемах стандартной логики уменьшилась не настолько, чтобы полностью отказаться от их применения.

Во-первых, и в микроконтроллерных устройствах широко используются элементы, например, шинные формирователи, регистры.

Во-вторых, улучшаются потребительские качества схем логики — быстродействие, потребляемая мощность, нагрузочная способность, что позволяет использовать их в простых применениях вместо микроконтроллеров, сокращая путь от идеи до ее воплощения за счет отсутствия необходимости разработки дорогого программного обеспечения.

СерияПараметр |

U пит., В |

t зад. |

Iвых. мax, мА |

Iпотр. мах, мА |

74 (54)/К155 (133) |

4,75 — 5,25 |

22/15 |

-0,4/16 |

8/22 |

74S (54S)/К531 (530) |

4,75 — 5,25 |

4,5/5 |

-1/20 |

16/36 |

74LS (54LS)/К555 (533) |

4,75 — 5,25 |

15/15 |

-0,4/8 |

1,6/4,4 |

74F (54F)/КР1531 |

4,5 — 5,5 |

6/5,3 |

-1/20 |

2,8/10,2 |

74AS (54AS)/К1530 |

4,5 — 5,5 |

4,5/4 |

-2/20 |

3,2/17,4 |

74ALS/КР1533 |

4,5 — 5,5 |

11/8 |

-0,4/ 8 |

0,85/3 |

Краткий перечень предлагаемых ТТЛ микросхем стандартной логики первого поколения

Функциональное назначение |

Импортный аналог |

155 (133), 74 |

К531 |

555 (533), 74LS |

KP1531 |

1533, 74ALS |

АГ1 |

121 |

· |

|

|

|

|

АГ3 |

123 |

· |

|

· |

|

· |

АГ4 |

221 |

|

|

· |

|

|

АП3 |

240 |

|

· |

· | · |

· |

АП2 |

216 |

|

· |

|

|

|

АП4 |

241 |

|

· |

· |

· |

· |

АП5 |

244 |

|

|

· |

|

· |

АП6 |

245 |

|

|

· |

|

· |

АП9 |

640 |

|

|

|

|

· |

АП10 |

646 |

|

|

· |

|

|

ВА1 |

226 |

|

· |

|

|

|

ВГ1 |

482 |

|

· |

|

|

|

ВЖ1 |

630 |

|

|

· |

|

|

ГГ1 |

124 |

|

· |

|

|

|

ИВ1 |

148 |

· |

|

· |

|

|

ИВ2 |

348 |

|

|

· |

|

|

ИД1 |

141 |

· |

|

|

|

|

ИД3 |

154 |

· |

|

· |

|

· |

ИД4 |

155 |

· |

|

· |

|

· |

ИД5 |

156 |

|

|

· |

|

|

ИД6 |

42 |

|

|

· |

|

|

ИД7 |

138 |

|

· |

· |

|

· |

ИД10 |

145 |

· |

|

· |

|

|

ИД11 |

|

· |

|

|

|

|

ИД13 |

|

· |

|

|

|

|

ИД14 |

139 |

|

· |

|

· |

· |

ИД18 |

247 |

|

|

· |

|

|

ИД19 |

238 |

|

|

· |

|

|

ИД22 |

537 |

|

|

|

· |

|

ИЕ1 |

|

· |

|

|

|

|

ИЕ2 |

90 |

· |

|

· |

|

· |

ИЕ4 |

92 |

· |

|

|

|

|

ИЕ5 |

93 |

· |

|

· |

|

· |

ИЕ6 |

192 |

· |

|

· |

|

· |

ИЕ7 |

193 |

· |

|

· |

|

· |

ИЕ8 |

97 |

· |

|

|

|

|

ИЕ9 |

160 |

· |

|

· |

|

· |

ИЕ10 |

161 |

|

|

· |

|

· |

ИЕ11 |

162 |

|

· |

|

|

· |

ИЕ13 |

191 |

|

|

· |

|

|

ИЕ14 |

196 |

· |

· |

· |

|

|

ИЕ15 |

197 |

|

· |

· |

|

|

ИЕ16 |

|

|

· |

|

|

|

ИЕ17 |

169 |

|

· |

· |

|

|

ИЕ18 |

163 |

|

· |

· |

|

· |

ИЕ19 |

393 |

|

|

· |

|

· |

ИЕ20 |

|

|

|

· |

|

|

ИК1 |

|

|

· |

|

|

|

ИК2 |

381 |

|

· |

|

|

|

ИМ1 |

80 |

· |

|

|

|

|

ИМ2 |

82 |

· |

|

|

|

|

ИМ3 |

83 |

· |

|

|

|

|

ИМ5 |

183 |

|

|

· |

|

|

ИМ6 |

283 |

|

|

· |

|

|

ИМ7 |

385 |

|

|

· |

|

|

ИП2 |

180 |

· |

|

|

|

|

ИП3 |

181 |

· |

· |

· |

|

· |

ИП4 |

182 |

· |

· |

· |

· |

· |

ИП5 |

280 |

|

· |

· |

|

· |

ИП6 |

242 |

|

|

· |

|

· |

ИП7 |

243 |

|

|

· |

|

· |

ИП8 |

261 |

|

|

· |

|

|

ИР1 |

95 |

· |

|

|

|

|

ИР8 |

164 |

|

|

· |

|

· |

ИР9 |

165 |

|

|

· |

|

· |

ИР10 |

166 |

|

|

· |

|

· |

ИР11 |

194 |

|

· |

|

|

|

ИР12 |

195 |

|

· |

|

|

|

ИР13 |

198 |

· |

|

|

|

|

ИР15 |

173 |

· |

|

· |

|

· |

ИР16 |

295 |

|

|

· |

|

· |

ИР17 |

|

· |

|

|

|

|

ИР18 |

|

|

· |

|

|

|

ИР21 |

|

|

· |

|

|

|

ИР22 |

373 |

|

· |

· |

|

· |

ИР23 |

374 |

|

· |

· |

|

· |

ИР24 |

299 |

|

· |

|

|

· |

ИР25 |

395 |

|

|

· |

|

|

ИР26 |

670 |

|

|

· |

|

· |

ИР27 |

377 |

|

|

· |

|

· |

ИР28 |

322 |

|

|

· |

|

|

ИР29 |

323 |

|

|

|

|

· |

ИР30 |

259 |

|

|

· |

|

· |

ИР31 |

|

|

|

|

|

· |

ИР32 |

170 |

· |

|

· |

|

· |

ИР35 |

273 |

|

|

· |

|

· |

ИР37 |

574 |

|

|

|

|

· |

ИР38 |

874 |

|

|

|

|

· |

ИР40 |

533 |

|

|

|

· |

|

ИР42 |

|

|

|

|

· |

|

КП1 |

150 |

· |

|

|

|

|

КП2 |

153 |

· |

· |

· |

|

· |

КП5 |

152 |

· |

|

|

|

|

КП7 |

151 |

· |

· |

· |

|

· |

КП11 |

257 |

|

· |

· |

· |

· |

КП12 |

253 |

|

· |

· |

|

· |

Функциональное назначение |

Импортный аналог |

155 (133), 74 |

К531 |

555 (533), 74LS |

KP1531 |

1533, 74ALS |

КП13 |

298 |

|

|

· |

|

· |

КП14 |

258 |

|

· |

· |

|

· |

КП15 |

251 |

|

· |

· |

|

· |

КП16 |

157 |

|

|

· |

|

· |

КП18 |

158 |

|

|

|

· |

· |

ЛА1 |

20 |

· |

· |

· |

· |

· |

ЛА2 |

30 |

· |

· |

· |

|

· |

ЛА3 |

0 |

· |

· |

· |

· |

· |

ЛА4 |

10 |

· |

· |

· |

· |

· |

ЛА6 |

40 |

· |

|

· |

|

|

ЛА7 |

22 |

· |

· |

· |

|

· |

ЛА8 |

1 |

· |

|

|

|

· |

ЛА9 |

3 |

|

· |

· |

|

· |

ЛА10 |

12 |

· |

|

· |

|

· |

ЛА11 |

26 |

· |

|

· |

|

|

ЛА12 |

37 |

· |

|

· |

|

· |

ЛА13 |

38 |

· |

· |

· |

|

|

ЛА17 |

|

|

· |

|

|

|

ЛА18 |

452 |

· |

|

|

|

|

ЛА19 |

134 |

|

· |

|

|

|

ЛД1 |

60 |

· |

|

|

|

|

ЛД3 |

|

· |

|

|

|

|

ЛЕ1 |

2 |

· |

· |

· |

|

· |

ЛЕ2 |

23 |

· |

|

|

|

|

ЛЕ3 |

25 |

· |

|

|

|

|

ЛЕ4 |

27 |

· |

|

· |

|

· |

ЛЕ5 |

28 |

· |

|

|

|

|

ЛЕ6 |

128 |

· |

|

|

|

|

ЛЕ7 |

260 |

|

· |

|

|

|

ЛЕ10 |

1002 |

|

|

|

|

· |

ЛИ1 |

8 |

· |

· |

· |

· |

· |

ЛИ2 |

9 |

|

|

· |

|

· |

ЛИ3 |

11 |

|

· |

· |

· |

· |

ЛИ4 |

15 |

|

|

· |

|

· |

ЛИ5 |

451 |

· |

|

|

|

|

ЛИ6 |

21 |

|

|

· |

|

· |

ЛИ8 |

1008 |

|

|

|

|

· |

ЛИ10 |

1011 |

|

|

|

|

· |

ЛЛ1 |

32 |

· |

· |

· |

|

· |

ЛЛ2 |

453 |

· |

|

|

|

|

ЛН1 |

4 |

· |

· |

· |

· |

· |

ЛН2 |

5 |

· |

· |

· |

|

· |

ЛН3 |

6 |

· |

|

|

|

|

ЛН5 |

16 |

· |

|

|

|

|

ЛН6 |

366 |

· |

|

|

|

|

ЛП3 |

|

|

|

· |

|

· |

ЛП5 |

86 |

· |

· |

· |

|

· |

ЛП7 |

450 |

· |

|

|

|

|

ЛП8 |

125 |

· |

|

· |

|

· |

ЛП9 |

7 |

· |

|

|

|

|

ЛП10 |

365 |

· |

|

|

|

|

ЛП11 |

367 |

· |

|

|

|

|

ЛП12 |

136 |

|

|

· |

|

· |

ЛР1 |

50 |

· |

|

|

|

|

ЛР3 |

53 |

· |

|

|

|

|

ЛР4 |

55 |

· |

|

· |

|

· |

ЛР9 |

64 |

|

· |

|

|

|

ЛР10 |

64 |

|

· |

|

|

|

ЛР11 |

51 |

|

· |

· |

|

· |

ЛР13 |

54 |

|

|

· |

|

· |

ПП4 |

49 |

· |

|

|

|

|

ПР1 |

4094 |

|

|

|

|

|

ПР6 |

184 |

· |

|

|

|

|

ПР7 |

185 |

· |

|

|

|

|

ПЦ1 |

292 |

|

|

· |

|

|

РЕ3 |

|

· |

|

|

|

|

РЕ4 |

|

|

|

· |

|

|

РЕ21 |

|

· |

|

|

|

|

РЕ22 |

|

· |

|

|

|

|

РЕ23 |

|

· |

|

|

|

|

РЕ24 |

|

· |

|

|

|

|

РП3 |

172 |

· |

|

|

|

|

РУ1 |

81 |

· |

|

|

|

|

РУ2 |

89 |

|

|

|

|

|

РУ5 |

|

· |

|

|

|

|

РУ7 |

|

· |

|

|

|

|

РУ8 |

189 |

|

· |

|

|

|

РУ9 |

289 |

|

· |

|

|

|

СП1 |

85 |

|

· |

· |

|

· |

ТВ1 |

72 |

· |

|

|

|

|

ТВ6 |

107 |

|

|

· |

|

· |

ТВ9 |

112 |

|

· |

· |

· |

· |

ТВ10 |

113 |

|

· |

|

|

· |

ТВ11 |

114 |

|

· |

|

|

· |

ТВ15 |

109 |

· |

|

|

|

· |

ТЛ1 |

13 |

· |

|

|

|

|

ТЛ2 |

14 |

· |

|

· |

|

· |

ТЛ3 |

132 |

· |

· |

|

|

|

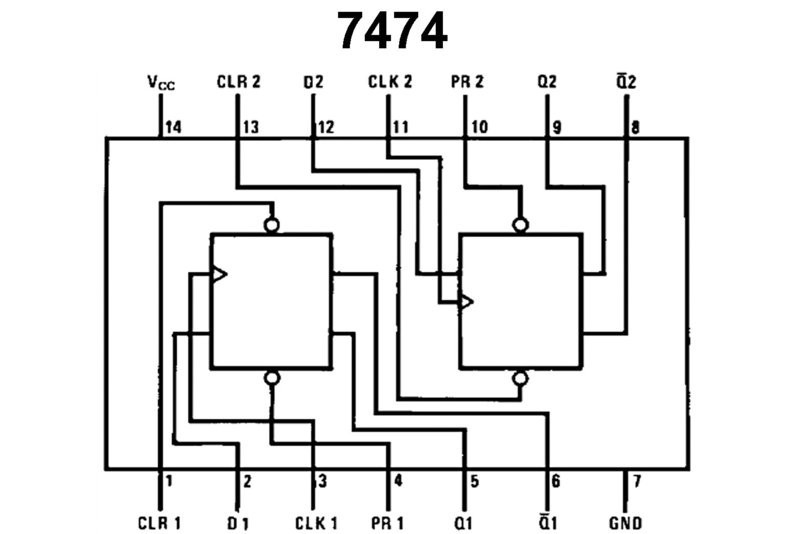

ТМ2 |

74 |

· |

· |

· |

· |

· |

ТМ5 |

77 |

· |

|

|

|

|

ТМ7 |

75 |

· |

|

· |

|

|

ТМ8 |

175 |

· |

· |

· |

|

· |

ТМ9 |

174 |

|

· |

· |

|

· |

ТР2 |

279 |

|

|

· |

|

· |

ХЛ1 |

|

· |

· |

|

|

|

· — присутствуют в серии

НЕ ИМЕЮЩИЕ ОТЕЧЕСТВЕННЫХ АНАЛОГОВ

Модель |

Краткое описание |

73 |

Триггер JK х 2 с очисткой |

137 |

Дешифратор двоичный 3->8 с защелкой |

133 |

И-НЕ 1 х 13 |

521 |

Компаратор 8-бит |

590 |

Счетчик двоичный 8-бит |

595 |

Регистр сдвиговый 8 бит параллельный вход, последовательный выход с защелкой |

652 |

Шинный формирователь, инвертирующий двунаправленный 8-бит + регистр хранения |

688 |

Компаратор 8-бит |

4060 |

Счетчик универсальный 14-бит |

4538 |

Одновибратор х 2 |

Наименование

К продаже

Цена от

К продаже:

159 шт.

К продаже:

72 шт.К продаже:

122 шт.

К продаже:

46 шт.К продаже:

161 шт.

К продаже:

141 шт.К продаже:

176 шт.

К продаже:

913 шт.К продаже:

751 шт.

К продаже:

18 шт.К продаже:

49 шт.

К продаже:

36 шт.К продаже:

234 шт.

К продаже:

4 шт.К продаже:

221 шт.

К продаже:

108 шт.К продаже:

240 шт.

К продаже:

575 шт.К продаже:

398 шт.

К продаже:

299 шт.К продаже:

694 шт.

К продаже:

131 шт.К продаже:

19 шт.

К продаже:

287 шт.К продаже:

2 392 шт.

К продаже:

102 шт.К продаже:

40 шт.

К продаже:

119 шт.К продаже:

35 шт.

К продаже:

59 шт.К продаже:

28 шт.

К продаже:

380 шт.К продаже:

8 965 шт.

К продаже:

26 шт.К продаже:

117 шт.

К продаже:

109 шт.К продаже:

64 шт.

К продаже:

1 633 шт.К продаже:

4 шт.

К продаже:

668 шт.К продаже:

120 шт.

К продаже:

394 шт.К продаже:

46 шт.

К продаже:

146 шт.К продаже:

98 шт.

К продаже:

49 шт.К продаже:

146 шт.К продаже:

72 шт.К продаже:

144 шт.К продаже:

226 шт.К продаже:

24 шт.К продаже:

11 шт.К продаже:

36 шт.К продаже:

594 шт.К продаже:

313 шт.К продаже:

55 шт.К продаже:

231 шт.К продаже:

31 шт.К продаже:

363 шт.К продаже:

321 шт.К продаже:

280 шт.К продаже:

1 901 шт.К продаже:

27 шт.К продаже:

1 283 шт.К продаже:

42 шт.К продаже:

25 шт.К продаже:

142 шт.К продаже:

146 шт.К продаже:

155 шт.К продаже:

135 шт.К продаже:

101 шт.К продаже:

21 шт.К продаже:

42 шт.К продаже:

218 шт.| Импортная серия | Серия ГОСТ | Напряжение питания Vcc±10% | Совместимость | Входной ток mkA, при Vccmax | Ток нагрузки mA, при Vccmax | Ток потребления Icc, mkA | Быстродействие | |||

| по входам | по выходам | I IL | I IH | I OL | I OH | |||||

| 74AC | КР1554 | 3,3/5 | CMOS | TTL,CMOS | -1 | 1 | 24 | -24 | 80 | 7,5 |

| 74ACT | КР1594 | 5 | TTL,CMOS | TTL,CMOS | -1 | 1 | 24 | -24 | 80 | 10 |

| 74HC | КР1564 | 2/4,5/6 | CMOS | TTL,CMOS | -1 | 1 | 6 | -6 | 80 | 25 |

| 74AS | КР1530 | 5 | TTL | TTL | -1,6mA | 5 | 64 | -15 | 90 мА | 6,5 |

| 74F | КР1531 | 5 | TTL | TTL | -1,0mA | 20 | 64 | -15 | 90 mA | 6,2 |

| 74ALS | КР1533 | 5 | TTL | TTL | -0,1mA | 20 | 24 | -15 | 27 мА | 10 |

| 74LS | КР555 | 5 | TTL | TTL | -200 | 20 | 24 | -15 | 54 мА | 18 |

| 74S | КР531 | 5 | TTL | TTL | -400 | 50 | 64 | -15 | 120 мА | 9 |

| 74 | КР155 | 5 | TTL | TTL | -1,6mA | 40 | 40 | -250мкА | 41 мА | 30 |

| 74 серия | ГОСТ | Назначение | 74 серия | ГОСТ | Назначение | 74 серия | ГОСТ | Назначение | ||

| 00 | ЛА3 | Четыре логических элемента 2И-НЕ | 136 | ЛП12 | 4 логических элемента «исключающее ИЛИ» с открытым коллектором | 301 | РУ6 | статическое ОЗУ 1024×1 | ||

| 01 | ЛА8 | Четыре логических элемента 2И-НЕ с открытым коллектором | 138 | ИД7 | демультиплексор 3 в 8 со стробом и логикой | 322 | ИР28 | 8-разрядный последовательно-параллельный регистр | ||

| 02 | ЛЕ1 | Четыре логических элемента 2ИЛИ-НЕ | 129 | ИД14 | 2 демультиплексора со 1 в 4 стробом | 323 | ИР29 | 8-разрядный универсальный регистр с тремя состояниями | ||

| 03 | ЛА9 | Четыре логических элемента 2И-НЕ с открытым коллектором | 140 | ЛА16 | Два логических элемента 4И-НЕ работающих на 50 Ом (I(0)=60 мА, I(1)= 40 мА) | 348 | ИВ2 | Каскадируемый приоритетный кодер 8-3 с тремя состояниями | ||

| 04 | ЛН1 | Шесть логических элементов НЕ | 141 | ИД1 | Высоковольтный дешифратор управления газоразрядным индикатором | 350 | ИР42 | 4-разрядный сдвигатель на 0,1,2,3 разряда с тремя состояниями | ||

| 05 | ЛН2 | Шесть логических элементов НЕ с открытым коллектором | 145 | ИД10 | Полный дешифратор 2-10 кода в десятичный с открытым коллектором (15 В) | 352 | КП19 | Сдвоенный мультиплексор 4 в 1, инвертирующий | ||

| 06 | ЛН3 | Шесть мощных (40 мА) инверторов с высоковольтным открытым коллектором (30 В) | 147 | ИВ3 | Приоритетный кодер 10 в 4 | 353 | КП17 | Сдвоенный инверсный мультиплексор 4 в 1 с 3 состояниями | ||

| 07 | ЛП9 | Шесть мощных (40 мА) неинверторов с высоковольтным открытым коллектором (30 В) | 148 | ИВ1 | Каскадируемый приоритетный кодер 8-3 | 365 | ЛП10 | Шесть мощных (32 мА) драйверов-неинверторов с общим стробированием выхода (3 состояния) | ||

| 08 | ЛИ1 | Четыре логических элемента 2И | 150 | КП1 | Мультиплексор 16 в 1 со стробом и инверсией | 366 | ЛН6 | Шесть мощных (32 мА) драйверов-инверторов с общим стробированием выходов (3 состояния) | ||

| 09 | ЛИ2 | Четыре логических элемента 2И с открытым коллектором | 151 | КП7 | Мультиплексор 8 в 1 с инверсией (со стробом) | 367 | ЛП11 | Шесть мощных (32 мА) драйверов-неинверторов со стробированием 2-х и 4-х линий (3 состояния) | ||

| 10 | ЛА4 | Три логических элемента 3И-НЕ | 152 | КП5 | Мультиплексор 8 в 1 с инверсией (со стробом) | 368 | ЛН8 | Шесть мощных инверторов | ||

| 11 | ЛИ3 | Три логических элемента 3И | 153 | КП2 | Сдвоенный мультиплексор 2 в 1 со стробом | 373 | ИР22 | 8-разрядный буферный регистр с тремя состояниями | ||

| 12 | ЛА10 | Три логических элемента 3И-НЕ с открытым коллектором | 154 | ИД3 | Демультиплексор 4 в 16 | 374 | ИР23 | 8 триггеров с тремя состояниями | ||

| 13 | ТЛ1 | Два логических элемента 4И-НЕ с триггером Шмитта | 155 | ИД4 | Сдвоенный демультиплексор 2 в 4 со стробом | 377 | ИР27 | 8-разрядный регистр с разрешением записи | ||

| 14 | ТЛ2 | Шесть логических элементов НЕ с триггером Шмитта | 156 | ИД5 | Сдвоенный демультиплексор 2 в 4 со стробом | 379 | ТМ10 | четыре D-триггера с прямыми и инверсными выходами | ||

| 15 | ЛИ4 | Три логических элемента 3И с открытым коллектором | 157 | КП16 | 4 мультиплексора 2 в 1 со стробом | 381 | ИК2 | АЛУ | ||

| 16 | ЛН5 | Шесть мощных (40 мА) инверторов с высоковольтным открытым коллектором (15 В) | 158 | КП18 | 4 мультиплексора 2 в 1 со стробом и инверсией | 384 | ИП9 | 8-разрядный последовательный умножитель | ||

| 17 | ЛП4 | Шесть мощных (40 мА) неинверторов с высоковольтным открытым коллектором (15 В) | 159 | ИД19 | Дешифратор 3х8 | 385 | ИМ7 | 4 последовательных сумматора/вычитателя | ||

| 20 | ЛА1 | Два логических элемента 4И-НЕ | 160 | ИЕ9 | 4-разрядный десятичный синхронный счетчик | 390 | ИЕ20 | Два 4-разрядных десятичных счетчика | ||

| 21 | ЛИ6 | Два логических элемента 4И | 161 | ИЕ10 | 4-разрядный двоичный синхронный счетчик | 393 | ИЕ19 | Два 4-разрядных двоичных счетчика | ||

| 22 | ЛА7 | Два логических элемента 4И-НЕ с открытым коллектором | 162 | ИЕ11 | 4-разрядный десятичный синхронный счетчик | 395 | ИР25 | 4-разрядный каскадируемый сдвигающий регистр с 3 состояниями | ||

| 23 | ЛЕ2 | Два логических элемента 4ИЛИ-НЕ со стробированием одного элемента и возможностью расширения по ИЛИ на другом | 163 | ИЕ18 | 4-разрядный двоичный синхронный счетчик | 396 | ИР43 | 8-разрядный регистр | ||

| 25 | ЛЕ3 | Два логических элемента 4ИЛИ-НЕ со стробированием | 164 | ИР8 | 8-разрядный сдвигающий регистр со сбросом с параллельным выходом | 399 | КП20 | 4 мультиплексора 2 в 1 с памятью (триггер) | ||

| 26 | ЛА11 | Четыре логических элемента 2И-НЕ с высоковольтным (до 15 В) открытым коллектором | 165 | ИР9 | 8-разрядный сдвигающий регистр с параллельными входами | 450 | ЛП7 | 2 логических элемента 2И-НЕ с общим входом и двумя мощными транзисторами | ||

| 27 | ЛЕ4 | Три логических элемента 3ИЛИ-НЕ | 166 | ИР10 | 8-разрядный сдвигающий регистр со сбросом с параллельной загрузкой и последовательным выходом | 451 | ЛИ5 | Два логических элемента 2И с мощным открытым коллектором | ||

| 28 | ЛЕ5 | Четыре логических элемента 2ИЛИ-НЕ (драйвер линии 75 Ом) I(0)=48 мА, I(1)=2.4 мА | 168 | ИЕ16 | Двоично-десятичный синхронный счетчик | 452 | ЛА18 | Два логических элемента 2И-НЕ с мощным открытым коллектором | ||

| 30 | ЛА2 | Логический элемент 8И-НЕ | 169 | ИЕ17 | Десятичный синхронный счетчик | 453 | ЛЛ2 | Два логических элемента 2ИЛИ с мощным открытым коллектором | ||

| 32 | ЛЛ1 | Четыре логических элемента 2ИЛИ | 170 | ИР32 | 4×4 регистровый файл | 465 | АП14 | 8 неинверсных драйверов с 3 состояниями | ||

| 33 | ЛЕ11 | Четыре логических элемента 2ИЛИ-НЕ с открытым коллектором | 172 | РП3 | 16-битовый регистровый файл с 3 состояниями | 466 | АП15 | 8 инверсных драйверов с 3 состояниями | ||

| 34 | ЛИ9 | Шесть повторителей | 173 | ИР15 | 4-разрядный параллельный регистр с общим сбросом и выходом с тремя состояниями | 482 | ВГ1 | Контроллер адреса | ||

| 37 | ЛА12 | Четыре логических элемента 2И-НЕ с мощным выходом (до 48 мА) | 174 | ТМ9 | Шесть D-триггеров с общим сбросом и тактированием | 533 | ИР40 | 8-разрядный инверсный лэтч с 3 состояниями | ||

| 38 | ЛА13 | Четыре логических элемента 2И-НЕ с мощным (до 48 мА) открытым коллектором | 175 | ТМ8 | Четыре D-триггеров с общим сбросом и тактированием | 534 | ИР41 | 8-разрядный инверсный регистр с 3 состояниями | ||

| 40 | ЛА6 | Два логических элемента 4И-НЕ с повышенной нагрузочной способностью | 180 | ИП2 | 8-разрядная схема контроля по четности | 537 | ИД22 | Дешифратор 4 в 10 с тремя состояниями и изменяемой полярностью выходов | ||

| 42 | ИД6 | Демультиплексор 4 в 10 | 181 | ИП3 | Четырехразрядное АЛУ | 540 | АП12 | 8 инверсных драйверов с 3 состояниями | ||

| 45 | ИД24 | Полный дешифратор 2-10 в десятичный с открытым коллектором (30В) | 182 | ИП4 | Схема быстрого переноса для АЛУ | 541 | АП13 | 8 неинверсных драйверов с 3 состояниями | ||

| 49 | ПП4 | Преобразователь двоичного кода в семисегментный | 183 | ИМ5 | Два одноразрядных полных сумматора | 573 | ИР33 | 8 лэтчей с тремя состояниями | ||

| 50 | ЛР1 | Два логических элемента 2И-2ИЛИ-НЕ, один расширяемый по ИЛИ | 184 | ПР6 | Преобразователь двоично-десятичного кода в двоичный | 574 | ИР37 | 8 триггеров с тремя состояниями | ||

| 51 | ЛР11 | Логический элемент 4-2-3-2И-4ИЛИ-НЕ | 185 | ПР7 | Преобразователь двоичного кода в двоично- десятичный | 593 | ИЕ21 | 8-разрядный двоичный счетчик с входным регистром и двунаправленной шиной ввода/вывода | ||

| 53 | ЛР3 | Логический элемент 2-2-2-3И-4ИЛИ-НЕ расширяемый по ИЛИ | 187 | РЕ2 | ПЗУ | 620 | АП25 | Восьмиканальный двунаправленный приемопередатчик с тремя состояниями и инверсией на выходе | ||

| 54 | ЛР13 | Логический элемент 2-3-3-2И-4ИЛИ-НЕ | 189 | РУ8 | ОЗУ на 64 бит с произвольной выборкой | 623 | АП26 | Восьмиканальный двунаправленный приемопередатчик с тремя состояниями на выходе | ||

| 55 | ЛР4 | Логический элемент 4-4И-2ИЛИ-НЕ расширяемый по ИЛИ | 190 | ИЕ12 | Двоично-десятичный счетчик | 624 | ГГ6 | Генератор | ||

| 60 | ЛД1 | Два 4-входовых расширителя по ИЛИ | 191 | ИЕ13 | Десятичный счетчик | 626 | ГГ2 | Два генератора, управляемых напряжением | ||

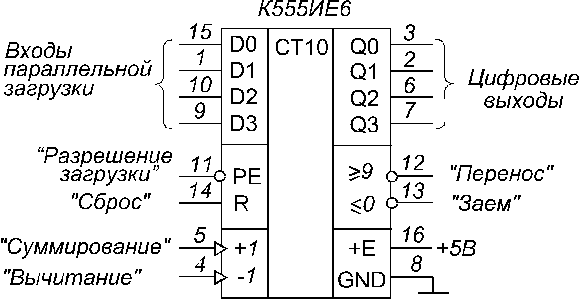

| 64 | ЛР9 | Логический элемент 4-2-3-2И-4ИЛИ-НЕ | 192 | ИЕ6 | Двоично-десятичный счетчик | 630 | ВЖ1 | 16-разрядная схема контроля по коду Хэмминга | ||

| 65 | ЛР10 | Логический элемент 4-2-3-2И-4ИЛИ-НЕ с открытым коллектором | 193 | ИЕ7 | Десятичный счетчик | 640 | АП9 | 8-разрядный двунаправленный драйвер с 3 состояниями | ||

| 72 | ТВ1 | J-K триггер с логикой 3И на входе | 194 | ИР11 | 4-разрядный универсальный регистр | 641 | АП7 | 8-разрядный двунаправленный неинверсный драйвер с открытым коллектором | ||

| 74 | ТМ2 | Два D-триггера | 195 | ИР12 | 4-разрядный двунаправленный приемопередатчик без инверсии и выходом с 3 состояниями | 643 | АП16 | 8 двунаправленных драйверов с 3 состояниями | ||

| 75 | ТМ7 | Два сдвоенных лэтча | 196 | ИЕ14 | Двоично-десятичный счетчик | 645 | АП8 | 8-разрядный двунаправленный неинверсный драйвер с тремя состояниями | ||

| 76 | ТК3 | Два JK-триггера | 197 | ИЕ15 | Десятичный счетчик | 646 | ВА1 | 4-разрядный двунаправленный приемо-передатчик с лэтчами на обоих шинах | ||

| 77 | ТМ5 | Два сдвоенных лэтча | 198 | ИР13 | 8-разрядный универсальный регистр | 648 | ВА2 | 8-разрядный двунаправленный приемо-передатчик с тремя состояниями | ||

| 78 | ТВ14 | Триггер | 214 | — | SRAM 4k | 651 | АП17 | 8-разрядный двунаправленный приемо-передатчик с регистрами на обоих шинах | ||

| 80 | ИМ1 | Одноразрядный полный сумматор | 216 | АП2 | Четырехразрядный драйвер с открытым коллектором | 652 | АП24 | 8-разрядный двунаправленный неинверсный приемо-передатчик с тремя состояниями | ||

| 81 | РУ1 | Статическое ОЗУ со схемой управления (16×1) | 221 | АГ4 | Два одновибратора с триггером Шмитта на входе | 670 | ИР26 | 4×4 регистровый файл с тремя состояниями | ||

| 82 | ИМ2 | Двухразрядный полный сумматор | 224 | РУ12 | — | 804 | ЛА20 | 6 мощных логических элемента 2И-НЕ | ||

| 83 | ИМ3 | Четырехразрядный полный сумматор | 225 | РУ10 | FIFO 16×5 бит | 805 | ЛЕ8 | 6 мощных логических элемента 2ИЛИ | ||

| 84 | РУ3 | Статическое ОЗУ (4×4) | 238 | ИД19 | 8-разрядный универсальный регистр сдвига с 3 состояниями | 808 | ЛИ7 | 6 мощных логических элемента 2И | ||

| 85 | СП1 | 4-разрядный цифровой компаратор | 240 | АП3 | Два четырехразрядных драйвера с тремя состояниями | 832 | ЛЛ3 | Шесть логических элементов 2ИЛИ | ||

| 86 | ЛП5 | 4 логических элемента «исключающее ИЛИ» | 241 | АП4 | Два четырехразрядных драйвера с тремя состояниями | 873 | ИР34 | Два 4-разрядных лэтча с тремя состояниями и сбросом | ||

| 89 | РУ2 | ОЗУ на 64 бит с произвольной выборкой | 242 | ИП6 | Четырехразрядные двунаправленные драйвера | 874 | ИР38 | Два 4-разрядных триггера с тремя состояниями и сбросом | ||

| 90 | ИЕ2 | 4-разрядный двоично-десятичный счетчик | 243 | ИП7 | Четырехразрядные двунаправленные драйвера | 881 | ИП14 | Четырехразрядное АЛУ | ||

| 91 | ИР2 | 8-разрядный сдвиговый регистр | 244 | АП5 | Два четырехразрядных драйвера с тремя состояниями | 882 | ИП16 | 32-разрядный генератор с предварительным просмотром и схемой ускоренного переноса | ||

| 92 | ИЕ4 | Счетчик-делитель на 12 | 245 | АП6 | 8-разрядный двунаправленный шинный транслятор | 1000 | ЛА21 | Четыре логических элемента 2И-НЕ | ||

| 93 | ИЕ5 | 4-разрядный двоичный счетчик | 247 | ИД18 | Декодер двоичного кода в семисегментный | 1002 | ЛЕ10 | Четыре логических элемента 2ИЛИ-НЕ | ||

| 95 | ИР1 | 4-разрядный универсальный регистр | 251 | КП15 | Мультиплексор 8 в 1 с 3 состояниями, прямым и инверсным выходами | 1003 | ЛА23 | Четыре логических элемента 2И-НЕ с открытым коллектором | ||

| 97 | ИЕ8 | 6-разрядный делитель частоты с переменным коэффициентом деления | 253 | КП12 | Сдвоенный мультиплексор 4 в 1 с 3 состояниями | 1004 | ЛН8 | Шесть мощных инверторов | ||

| 98 | ИР5 | — | 257 | КП11 | 4 мультиплексора 2 в 1 с 3 состояниями | 1005 | ЛН10 | Шесть мощных инверторов с открытым коллектором | ||

| 100 | ТК7 | JK-триггер | 258 | КП14 | 4 мультиплексора 2 в 1 с 3 состояниями и инверсией | 1008 | ЛИ8 | Четыре логических элемента 2И | ||

| 107 | ТВ6 | Два J-K триггера со сбросом | 259 | ИР30 | 8-разрядный адресуемый лэтч | 1010 | ЛА24 | Три логических элемента 3И-НЕ | ||

| 109 | ТВ15 | Два J-K триггера | 260 | ЛЕ7 | Два логических элемента 5ИЛИ-НЕ | 1011 | ЛИ10 | Три логических элемента 3И | ||

| 112 | ТВ9 | Два J-K триггера | 261 | ИП8 | Умножитель 2×4 | 1020 | ЛА22 | Два логических элемента 4И-НЕ | ||

| 113 | ТВ10 | Два J-K триггера | 237 | ИР35 | 8 D-триггеров с общим тактированием и сбросом | 1032 | ЛЛ4 | Четыре логических элемента 2ИЛИ | ||

| 114 | ТВ11 | Два J-K триггера | 297 | ТР2 | Четыре R-S-триггера | 1034 | ЛП16 | Шесть неинверторов | ||

| 121 | АГ1 | Одновибратор | 280 | ИП5 | 9-разрядная схема контроля по четности | 1035 | ЛП17 | Шесть неинверторов с открытым коллектором | ||

| 123 | АГ3 | Два одновибратора | 281 | ИК4 | 4-разрядный аккумулятор | 4002 | ЛЕ9 | Два счетверенных логических элемента НЕ-ИЛИ | ||

| 124 | ГГ1 | Два генератора, управляемых напряжением | 283 | ИМ6 | 4-разрядный полный сумматор с ускоренным переносом | 4006 | ИР47 | Сдвиговый регистр | ||

| 125 | ЛП8 | 4 неинвертора (3 состояния) | 289 | РУ9 | ОЗУ на 64 бит с произвольной выборкой | 4015 | ИР46 | 4-разрядный регистр с последовательным вводом и Reset | ||

| 126 | ЛП14 | 4 неинвертора (3 состояния) | 292 | ПЦ1 | Программируемый делитель частоты/таймер | 4035 | ИР51 | 4-разрядный последовательно-параллельный регистр | ||

| 128 | ЛЕ6 | Четыре логических элемента 2ИЛИ-НЕ | 295 | ИР16 | 4-разрядный универсальный регистр с тремя состояниями | 4511 | ИД23 | Лэтч, декодер, драйвер семисегментный | ||

| 132 | ТЛ3 | Четыре триггера Шмитта | 298 | КП13 | 4 мультиплексора 2 в 1 с памятью (триггер) | 4520 | ИЕ23 | Два четырехразрядных двоичных счетчика | ||

| 134 | ЛА19 | Элемент 12И-НЕ с тремя состояниями | 299 | ИР24 | 8-разрядный универсальный сдвиговый регистр с объединенными входами/выходами | — | ИР50 | Универсальный двухпортовый регистр | ||

ЛОГИЧЕСКИЕ МИКРОСХЕМЫ ТТЛ 74хх — CHIPkin

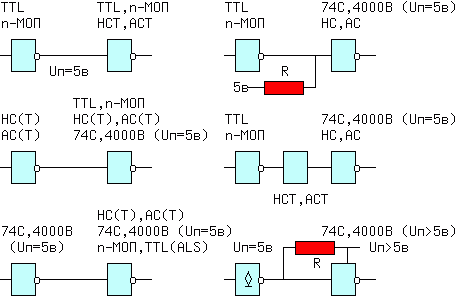

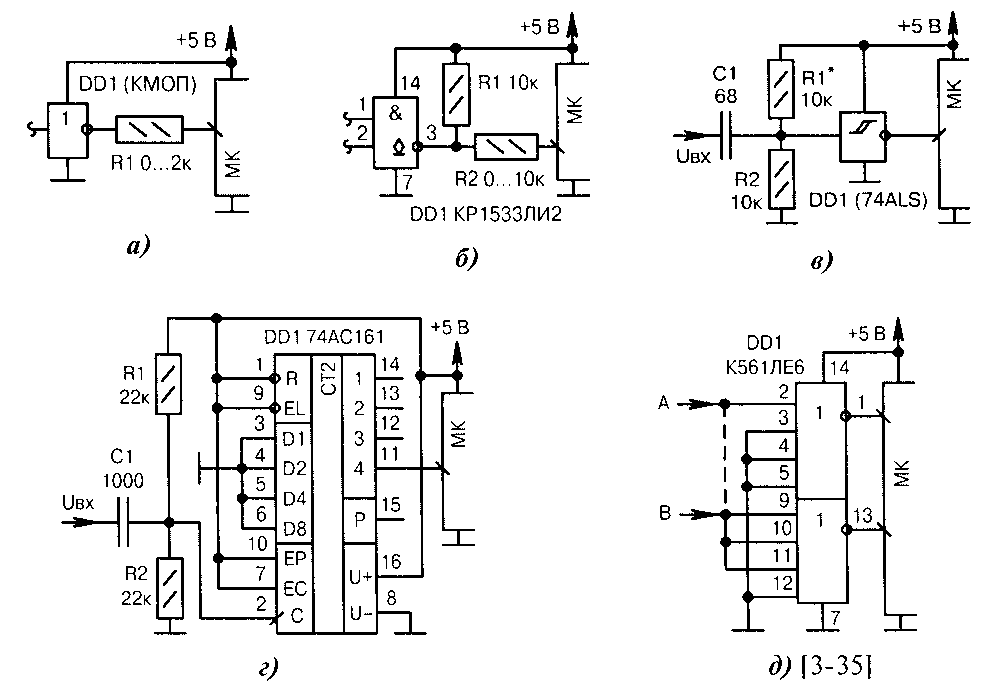

Отличие между 74АС/АСТ, НС/НСТ и АНС/АНСТ заключается только в логических уровнях сигналов. Серии без буквы <Т> допускают питание в широком диапазоне напряжений, однако, уровни логических сигналов у них будут зависеть от этого напряжения. В сериях АСТ, НСТ и АНСТ логические сигналы всегда соответствуют стандартным ТТЛ уровням при напряжении питания +5 вольт.

Для АВТ серии параметры <ЛА3> (74АВТ00) не слишком характерны. Более интересными в этой серии являются шинные формирователи и регистры. Так для <АП5> (74АВТ244) и других подобных типономиналов выходной ток достигает -32/64 мА. Правда, собственное потребление в таких случаях возрастает до 30 мА при нулевом состоянии выходов.

Микросхемы КМОП серии 40хх

| Серия\Параметр | U пит., В | t зад.распр., нс | Iвых. мax, мА | Iпотр. мах, мА |

| 74AC/КP1554 | 1,5 — 5,5 | 6,6 | -24/24 | 0,08 |

| 74АCT/КP1594 | 4,5 — 5,5 | 9,5 | -24/24 | 0,08 |

| 74HC/КP1564 | 2 — 6 | 20 | -4/4 | 0,04 |

| 74HCT | 4,5 — 5,5 | 25 | -4/4 | 0,04 |

| 74ABT | 4,5 — 5,5 | 4,1/3,4 | -15/20 | 0,05 |

| 74AHC | 2 — 5,5 | 8,5 | -8/8 | 0,02 |

| 74AHCT | 4,5 — 5,5 | 9 | -8/8 | 0,02 |

Краткий перечень предлагаемых КМОП микросхем серии 74хх

| Функциональное назначение | Импортный аналог | 74AC, KP1554 | 74ACT | 74HC, KP1564 | 74HCT | 74ABT | 74AHCT | 74VHCT |

| АГ3 | 123 | · | · | · | ||||

| АГ4 | 221 | · | · | |||||

| АП3 | 240 | · | · | · | · | · | · | |

| АП4 | 241 | · | · | · | · | · | ||

| АП5 | 244 | · | · | · | · | · | · | · |

| АП6 | 245 | · | · | · | · | · | · | · |

| АП8 | 645 | · | · | |||||

| АП9 | 640 | · | · | · | ||||

| АП12 | 540 | · | · | · | · | · | ||

| АП13 | 541 | · | · | · | · | · | · | |

| АП17 | 651 | · | · | |||||

| АП24 | 652 | · | · | |||||

| АП26 | 623 | · | · | |||||

| ВА1 | 646 | · | · | |||||

| ИВ1 | 148 | · | ||||||

| ИВ3 | 147 | · | ||||||

| ИД3 | 154 | · | · | |||||

| ИД4 | 155 | · | ||||||

| ИД6 | 42 | · | ||||||

| ИД7 | 138 | · | · | · | · | · | ||

| ИД14 | 139 | · | · | · | · | |||

| ИД19 | 238 | · | · | |||||

| ИЕ5 | 93 | · | · | |||||

| ИЕ6 | 192 | · | · | |||||

| ИЕ7 | 193 | · | · | |||||

| ИЕ9 | 160 | · | · | |||||

| ИЕ10 | 161 | · | · | · | · | |||

| ИЕ12 | 190 | · | ||||||

| ИЕ13 | 191 | · | · | |||||

| ИЕ17 | 169 | · | ||||||

| ИЕ18 | 163 | · | · | · | · | |||

| ИЕ19 | 393 | · | · | |||||

| ИЕ20 | 390 | · | ||||||

| ИЕ23 | 4520 | · | · | |||||

| ИМ6 | 283 | · | · | · | ||||

| ИП5 | 280 | · | · | · | ||||

| ИП7 | 243 | · | · | |||||

| ИР8 | 164 | · | · | · | · | · | ||

| ИР9 | 165 | · | · | |||||

| ИР10 | 166 | · | · | |||||

| ИР11 | · | |||||||

| ИР12 | 195 | · | ||||||

| ИР15 | 173 | · | · | |||||

| ИР22 | 373 | · | · | · | · | · | · | · |

| ИР23 | 374 | · | · | · | · | · | · | · |

| ИР24 | 299 | · | · | |||||

| ИР26 | 670 | · | ||||||

| ИР27 | 377 | · | · | · | · | · | ||

| ИР30 | 259 | · | · | · | ||||

| ИР33 | 573 | · | · | · | · | · | · | · |

| ИР35 | 273 | · | · | · | · | · | · | |

| ИР37 | 574 | · | · | · | · | · | · | · |

| Функциональное назначение | Импортный аналог | 74AC, KP1554 | 74ACT | 74HC, KP1564 | 74HCT | 74ABT | 74AHCT | 74VHCT |

| ИР40 | 533 | · | · | · | · | |||

| ИР41 | 534 | · | · | · | · | · | ||

| ИР46 | 4015 | · | ||||||

| ИР51 | 4035 | · | ||||||

| КП1 | 150 | · | ||||||

| КП2 | 153 | · | · | · | · | |||

| КП5 | 152 | · | ||||||

| КП7 | 151 | · | · | · | · | |||

| КП11 | 257 | · | · | · | · | · | ||

| КП12 | 253 | · | · | · | · | |||

| КП13 | 298 | · | ||||||

| КП14 | 258 | · | · | · | · | |||

| КП15 | 251 | · | · | · | · | |||

| КП16 | 157 | · | · | · | · | · | ||

| КП18 | 158 | · | · | · | · | |||

| ЛА1 | 20 | · | · | · | · | · | ||

| ЛА2 | 30 | · | · | · | ||||

| ЛА3 | 00 | · | · | · | · | · | ||

| ЛА4 | 10 | · | · | · | · | · | ||

| ЛА9 | 03 | · | · | |||||

| ЛА10 | 12 | · | ||||||

| ЛЕ1 | 02 | · | · | · | · | |||

| ЛЕ4 | 27 | · | · | |||||

| ЛИ1 | 08 | · | · | · | · | · | ||

| ЛИ2 | 09 | · | ||||||

| ЛИ3 | 11 | · | · | · | · | |||

| ЛИ6 | 21 | · | · | · | ||||

| ЛИ9 | 34 | · | ||||||

| ЛЛ1 | 32 | · | · | · | · | · | · | |

| ЛН1 | 04 | · | · | · | · | · | ||

| ЛН2 | 05 | · | · | · | ||||

| ЛН6 | 366 | · | ||||||

| ЛН7 | 368 | · | ||||||

| ЛН8 | 1004 | · | ||||||

| ЛП5 | 86 | · | · | · | · | · | ||

| ЛП8 | 125 | · | · | · | · | · | · | · |

| ЛП10 | 365 | · | ||||||

| ЛП11 | 367 | · | ||||||

| ЛП14 | 126 | · | · | · | · | |||

| ЛР11 | 51 | · | ||||||

| ПР1 | 4094 | · | · | |||||

| СП1 | 85 | · | · | |||||

| ТВ6 | 107 | · | · | |||||

| ТВ9 | 112 | · | · | · | · | |||

| ТВ15 | 109 | · | · | · | · | |||

| ТЛ2 | 14 | · | · | · | · | · | · | |

| ТЛ3 | 132 | · | · | · | · | |||

| ТМ2 | 74 | · | · | · | · | · | · | · |

| ТМ7 | 75 | · | · | |||||

| ТМ8 | 175 | · | · | · | · | |||

| ТМ9 | 174 | · | · | · | · |

ЛОГИЧЕСКИЕ МИКРОСХЕМЫ ТТЛ 74хх СЕРИИ И ИХ ОТЕЧЕСТВЕННЫЕ АНАЛОГИ Несмотря на появление микропроцессоров, микроконтроллеров и других программируемых схем и постоянное расширение сфер их применения, потребность в микросхемах стандартной логики уменьшилась не настолько, чтобы полностью отказаться от их применения.

Во-первых, и в микроконтроллерных устройствах широко используются элементы <обвязки>, например, шинные формирователи, регистры.

Во-вторых, улучшаются потребительские качества схем логики — быстродействие, потребляемая мощность, нагрузочная способность, что позволяет использовать их в простых применениях вместо микроконтроллеров, сокращая путь от идеи до ее воплощения за счет отсутствия необходимости разработки дорогого программного обеспечения.

| Серия\Параметр | U пит., В | t зад.распр., нс | Iвых. мax, мА | Iпотр. мах, мА |

| 74 (54)/К155 (133) | 4,75 — 5,25 | 22/15 | -0,4/16 | 8/22 |

| 74S (54S)/К531 (530) | 4,75 — 5,25 | 4,5/5 | -1/20 | 16/36 |

| 74LS (54LS)/К555 (533) | 4,75 — 5,25 | 15/15 | -0,4/8 | 1,6/4,4 |

| 74F (54F)/КР1531 | 4,5 — 5,5 | 6/5,3 | -1/20 | 2,8/10,2 |

| 74AS (54AS)/К1530 | 4,5 — 5,5 | 4,5/4 | -2/20 | 3,2/17,4 |

| 74ALS/КР1533 | 4,5 — 5,5 | 11/8 | -0,4/ 8 | 0,85/3 |

Краткий перечень предлагаемых ТТЛ микросхем стандартной логики первого поколения

| Функциональное назначение | Импортный аналог | 155 (133), 74 | К531 | 555 (533), 74LS | KP1531 | 1533, 74ALS |

| АГ1 | 121 | · | ||||

| АГ3 | 123 | · | · | · | ||

| АГ4 | 221 | · | ||||

| АП3 | 240 | · | · | · | · | |

| АП2 | 216 | · | ||||

| АП4 | 241 | · | · | · | · | |

| АП5 | 244 | · | · | |||

| АП6 | 245 | · | · | |||

| АП9 | 640 | · | ||||

| АП10 | 646 | · | ||||

| ВА1 | 226 | · | ||||

| ВГ1 | 482 | · | ||||

| ВЖ1 | 630 | · | ||||

| ГГ1 | 124 | · | ||||

| ИВ1 | 148 | · | · | |||

| ИВ2 | 348 | · | ||||

| ИД1 | 141 | · | ||||

| ИД3 | 154 | · | · | · | ||

| ИД4 | 155 | · | · | · | ||

| ИД5 | 156 | · | ||||

| ИД6 | 42 | · | ||||

| ИД7 | 138 | · | · | · | ||

| ИД10 | 145 | · | · | |||

| ИД11 | · | |||||

| ИД13 | · | |||||

| ИД14 | 139 | · | · | · | ||

| ИД18 | 247 | · | ||||

| ИД19 | 238 | · | ||||

| ИД22 | 537 | · | ||||

| ИЕ1 | · | |||||

| ИЕ2 | 90 | · | · | · | ||

| ИЕ4 | 92 | · | ||||

| ИЕ5 | 93 | · | · | · | ||

| ИЕ6 | 192 | · | · | · | ||

| ИЕ7 | 193 | · | · | · | ||

| ИЕ8 | 97 | · | ||||

| ИЕ9 | 160 | · | · | · | ||

| ИЕ10 | 161 | · | · | |||

| ИЕ11 | 162 | · | · | |||

| ИЕ13 | 191 | · | ||||

| ИЕ14 | 196 | · | · | · | ||

| ИЕ15 | 197 | · | · | |||

| ИЕ16 | · | |||||

| ИЕ17 | 169 | · | · | |||

| ИЕ18 | 163 | · | · | · | ||

| ИЕ19 | 393 | · | · | |||

| ИЕ20 | · | |||||

| ИК1 | · | |||||

| ИК2 | 381 | · | ||||

| ИМ1 | 80 | · | ||||

| ИМ2 | 82 | · | ||||

| ИМ3 | 83 | · | ||||

| ИМ5 | 183 | · | ||||

| ИМ6 | 283 | · | ||||

| ИМ7 | 385 | · | ||||

| ИП2 | 180 | · | ||||

| ИП3 | 181 | · | · | · | · | |

| ИП4 | 182 | · | · | · | · | · |

| ИП5 | 280 | · | · | · | ||

| ИП6 | 242 | · | · | |||

| ИП7 | 243 | · | · | |||

| ИП8 | 261 | · | ||||

| ИР1 | 95 | · | ||||

| ИР8 | 164 | · | · | |||

| ИР9 | 165 | · | · | |||

| ИР10 | 166 | · | · | |||

| ИР11 | 194 | · | ||||

| ИР12 | 195 | · | ||||

| ИР13 | 198 | · | ||||

| ИР15 | 173 | · | · | · | ||

| ИР16 | 295 | · | · | |||

| ИР17 | · | |||||

| ИР18 | · | |||||

| ИР21 | · | |||||

| ИР22 | 373 | · | · | · | ||

| ИР23 | 374 | · | · | · | ||

| ИР24 | 299 | · | · | |||

| ИР25 | 395 | · | ||||

| ИР26 | 670 | · | · | |||

| ИР27 | 377 | · | · | |||

| ИР28 | 322 | · | ||||

| ИР29 | 323 | · | ||||

| ИР30 | 259 | · | · | |||

| ИР31 | · | |||||

| ИР32 | 170 | · | · | · | ||

| ИР35 | 273 | · | · | |||

| ИР37 | 574 | · | ||||

| ИР38 | 874 | · | ||||

| ИР40 | 533 | · | ||||

| ИР42 | · | |||||

| КП1 | 150 | · | ||||

| КП2 | 153 | · | · | · | · | |

| КП5 | 152 | · | ||||

| КП7 | 151 | · | · | · | · | |

| КП11 | 257 | · | · | · | · | |

| КП12 | 253 | · | · | · |

| Функциональное назначение | Импортный аналог | 155 (133), 74 | К531 | 555 (533), 74LS | KP1531 | 1533, 74ALS |

| КП13 | 298 | · | · | |||

| КП14 | 258 | · | · | · | ||

| КП15 | 251 | · | · | · | ||

| КП16 | 157 | · | · | |||

| КП18 | 158 | · | · | |||

| ЛА1 | 20 | · | · | · | · | · |

| ЛА2 | 30 | · | · | · | · | |

| ЛА3 | 0 | · | · | · | · | · |

| ЛА4 | 10 | · | · | · | · | · |

| ЛА6 | 40 | · | · | |||

| ЛА7 | 22 | · | · | · | · | |

| ЛА8 | 1 | · | · | |||

| ЛА9 | 3 | · | · | · | ||

| ЛА10 | 12 | · | · | · | ||

| ЛА11 | 26 | · | · | |||

| ЛА12 | 37 | · | · | · | ||

| ЛА13 | 38 | · | · | · | ||

| ЛА17 | · | |||||

| ЛА18 | 452 | · | ||||

| ЛА19 | 134 | · | ||||

| ЛД1 | 60 | · | ||||

| ЛД3 | · | |||||

| ЛЕ1 | 2 | · | · | · | · | |

| ЛЕ2 | 23 | · | ||||

| ЛЕ3 | 25 | · | ||||

| ЛЕ4 | 27 | · | · | · | ||

| ЛЕ5 | 28 | · | ||||

| ЛЕ6 | 128 | · | ||||

| ЛЕ7 | 260 | · | ||||

| ЛЕ10 | 1002 | · | ||||

| ЛИ1 | 8 | · | · | · | · | · |

| ЛИ2 | 9 | · | · | |||

| ЛИ3 | 11 | · | · | · | · | |

| ЛИ4 | 15 | · | · | |||

| ЛИ5 | 451 | · | ||||

| ЛИ6 | 21 | · | · | |||

| ЛИ8 | 1008 | · | ||||

| ЛИ10 | 1011 | · | ||||

| ЛЛ1 | 32 | · | · | · | · | |

| ЛЛ2 | 453 | · | ||||

| ЛН1 | 4 | · | · | · | · | · |

| ЛН2 | 5 | · | · | · | · | |

| ЛН3 | 6 | · | ||||

| ЛН5 | 16 | · | ||||

| ЛН6 | 366 | · | ||||

| ЛП3 | · | · | ||||

| ЛП5 | 86 | · | · | · | · | |

| ЛП7 | 450 | · | ||||

| ЛП8 | 125 | · | · | · | ||

| ЛП9 | 7 | · | ||||

| ЛП10 | 365 | · | ||||

| ЛП11 | 367 | · | ||||

| ЛП12 | 136 | · | · | |||

| ЛР1 | 50 | · | ||||

| ЛР3 | 53 | · | ||||

| ЛР4 | 55 | · | · | · | ||

| ЛР9 | 64 | · | ||||

| ЛР10 | 64 | · | ||||

| ЛР11 | 51 | · | · | · | ||

| ЛР13 | 54 | · | · | |||

| ПП4 | 49 | · | ||||

| ПР1 | 4094 | |||||

| ПР6 | 184 | · | ||||

| ПР7 | 185 | · | ||||

| ПЦ1 | 292 | · | ||||

| РЕ3 | · | |||||

| РЕ4 | · | |||||

| РЕ21 | · | |||||

| РЕ22 | · | |||||

| РЕ23 | · | |||||

| РЕ24 | · | |||||

| РП3 | 172 | · | ||||

| РУ1 | 81 | · | ||||

| РУ2 | 89 | |||||

| РУ5 | · | |||||

| РУ7 | · | |||||

| РУ8 | 189 | · | ||||

| РУ9 | 289 | · | ||||

| СП1 | 85 | · | · | · | ||

| ТВ1 | 72 | · | ||||

| ТВ6 | 107 | · | · | |||

| ТВ9 | 112 | · | · | · | · | |

| ТВ10 | 113 | · | · | |||

| ТВ11 | 114 | · | · | |||

| ТВ15 | 109 | · | · | |||

| ТЛ1 | 13 | · | ||||

| ТЛ2 | 14 | · | · | · | ||

| ТЛ3 | 132 | · | · | |||

| ТМ2 | 74 | · | · | · | · | · |

| ТМ5 | 77 | · | ||||

| ТМ7 | 75 | · | · | |||

| ТМ8 | 175 | · | · | · | · | |

| ТМ9 | 174 | · | · | · | ||

| ТР2 | 279 | · | · | |||

| ХЛ1 | · | · |

· — присутствуют в серии

НЕ ИМЕЮЩИЕ ОТЕЧЕСТВЕННЫХ АНАЛОГОВ

| Модель | Краткое описание |

| 73 | Триггер JK х 2 с очисткой |

| 137 | Дешифратор двоичный 3->8 с защелкой |

| 133 | И-НЕ 1 х 13 |

| 521 | Компаратор 8-бит |

| 590 | Счетчик двоичный 8-бит |

| 595 | Регистр сдвиговый 8 бит параллельный вход, последовательный выход с защелкой |

| 652 | Шинный формирователь, инвертирующий двунаправленный 8-бит + регистр хранения |

| 688 | Компаратор 8-бит |

| 4060 | Счетчик универсальный 14-бит |

| 4538 | Одновибратор х 2 |

1 188

| НОМЕР | ОПИСАНИЕ |

| 7400 | 4е элемента 2НЕ-И |

| 741G00 | 1 элемент 2НЕ-И |

| 7401 | 4е элемента 2НЕ-И с открытыми коллекторами на выходах |

| 741G01 | 1 элемент 2НЕ-И с открытым стоком на выходе |

| 7402 | 4е элемента 2НЕ-ИЛИ |

| 741G02 | 1 элемент 2НЕ-ИЛИ |

| 7403 | 4е элемента 2НЕ-И с открытыми коллекторами на выходах |

| 741G03 | 1 элемент 2НЕ-И с открытым стоком на выходе |

| 7404 | 6 эелементов НЕ |

| 741G04 | 1 элемент НЕ |

| 7405 | 6 эелементов НЕ с открытыми коллекторами на выходах |

| 741G05 | 1 элемент НЕ с открытым стоком на выходе |

| 7406 | 6 элементов НЕ буффер/драйвер с 30 v открытыми коллекторами на выходах |

| 741G06 | 1 элемент inverting с буффером/drive |

| 7407 | 6 элементов буффер/драйвер с 30 v открытыми коллекторами на выходах |

| 741G07 | 1 элемент буффер/драйвер с открытым стоком на выходе |

| 7408 | 4е элемента 2И |

| 741G08 | 1 элемент 2И |

| 7409 | 4е элемента 2И с открытыми коллекторами на выходах |

| 741G09 | 1 элемент 2И с открытым стоком на выходе |

| 7410 | 3 элемента 3НЕ-И |

| 7411 | 3 элемента 3И |

| 7412 | 3 элемента 3НЕ-И с открытыми коллекторами на выходах |

| 7413 | 2 триггера Шмитта и 4НЕ-И |

| 7414 | 6 триггеров Шмитта с выходами НЕ |

| 741G14 | 1 триггер Шмитта с выходом НЕ |

| 7415 | 3 элемента 3И с открытыми коллекторами на выходах |

| 7416 | 6 элементов НЕ буффер/драйвер с 15 v открытыми коллекторами на выходах |

| 7417 | 6 элементов буффер/драйвер с 15 v открытыми коллекторами на выходах |

| 741G17 | 1 триггер Шмитта |

| 7418 | 2 элемента 4НЕ-И с триггерами Шмитта на входах |

| 7419 | 6 элементов НЕ с триггерами Шмитта |

| 7420 | 2 элемента 4НЕ-И |

| 7421 | 2 элемента 4И |

| 7422 | 2 элемента 4НЕ-И с открытыми коллекторами на выходах |

| 7423 | Расширяемые 2 элемента 4НЕ-ИЛИ со стробирующим входом |

| 7424 | 4е элемента 2НЕ-И с триггерами Шмитта на входе. |

| 7425 | 2 элемента 4НЕ-ИЛИ со стробирующим входом |

| 7426 | 4е элемента 2НЕ-И with 15 v открытыми коллекторами на выходах |

| 7427 | 3 элемента 3НЕ-ИЛИ |

| 741G27 | 1 элемент 3НЕ-ИЛИ |

| 7428 | 4е элемента 2НЕ-ИЛИ с буффером |

| 7430 | 8НЕ-И |

| 7431 | 6 элементов задержки |

| 7432 | 4е элемента 2ИЛИ |

| 741G32 | 1 элемент 2ИЛИ |

| 7433 | 4е элемента 2НЕ-ИЛИ с буффером с открытыми коллекторами на выходах |

| 7436 | 4е элемента 2НЕ-ИЛИ (с другими выводами, чем 7402) |

| 7437 | 4е элемента 2НЕ-И с буффером |

| 7438 | 4е элемента 2НЕ-И с буффером с открытыми коллекторами на выходах |

| 7439 | 4е элемента 2НЕ-И с буффером |

| 7440 | 2 элемента 4НЕ-И с буффером |

| 7441 | Двоично-десяти |

| 7442 | Двоично-десяти |

| 7443 | excess-3 to decimal decoder |

| 7444 | excess-3-Gray code to decimal decoder |

| 7445 | Двоично-десяти |

| 7446 | Двоично-десяти |

| 7447 | Двоично-десяти |

| 7448 | Двоично-десяти |

| 7449 | Двоично-десяти |

| 7450 | 2 элемента 2-расширенных 2И-ИЛИ-НЕ (один расширяемый) |

| 7451 | 2 элемента 2-расширенных 2И-ИЛИ-НЕ |

| 7452 | Расширяемые 4-расширенных 2И-ИЛИ |

| 7453 | Расширяемые 4-расширенных 2И-ИЛИ-НЕ |

| 7454 | 4-расширенных 2И-ИЛИ-НЕ |

| 7455 | 2-расширенных 4И-ИЛИ-НЕ (74H версия расширяемая) |

| 7456 | Делитель частоты 50 к 1 |

| 7457 | Делитель частоты 60 к 1 |

| 7458 | 2И-ИЛИ & 3И-ИЛИ |

| 7459 | 2И-ИЛИ-НЕ & 3И-ИЛИ-НЕ |

| 7460 | 2 элемента 4х входной расширитель |

| 7461 | 3 элемента 3х входной расширитель |

| 7462 | 3-2-2-3-И-ИЛИ расширитель |

| 7463 | 6 элементов детекторов тока |

| 7464 | 4-2-3-2И-ИЛИ-Н |

| 7465 | 4-2-3-2И-ИЛИ-Н |

| 7468 | 2 элемента 4х разрядный десятичный счетчик |

| 7469 | 2 элемента 4х разрядный двоичный счетчик |

| 7470 | AND-gated positive edge triggered J-K flip-flop with preset and clear |

| 74H71 | AND-or-gated J-K master-slave flip-flop with preset |

| 74L71 | AND-gated R-S master-slave flip-flop with preset and clear |

| 7472 | AND gated J-K master-slave flip-flop with preset and clear |

| 7473 | 2 элемента J-K flip-flop with clear |

| 7474 | 2 элемента D positive edge triggered flip-flop with preset and clear |

| 7475 | 4-bit bistable latch |

| 7476 | 2 элемента J-K flip-flop with preset and clear |

| 7477 | 4-bit bistable latch |

| 74H78 | 2 элемента positive pulse triggered J-K flip-flop with preset, common clock, and common clear (different pinout than 74L78 / 74Ls78) |

| 74L78 | 2 элемента positive pulse triggered J-K flip-flop with preset, common clock, and common clear |

| 74Ls78 | 2 элемента negative edge triggered J-K flip-flop with preset, common clock, and common clear |

| 7479 | 2 элемента D flip-flop |

| 741G79 | 1 элемент D-type flip-flop positive edge trigger non-inverting output |

| 7480 | gated full adder |

| 741G80 | 1 элемент D-type flip-flop positive edge trigger inverting output |

| 7481 | 1 элемент 6-bit random access memory |

| 7482 | 2-bit binary full adder |

| 7483 | 4-bit binary full adder |

| 7484 | 1 элемент6-bit random access memory |

| 7485 | 4-bit magnitude comparator |

| 7486 | 4е элемента 2-input XOR gate |

| 741G86 | 1 элемент 2 input exclusive-OR gate |

| 7487 | 4-bit true/complemen |

| 7488 | 256-bit read-only memory |

| 7489 | 64-bit random access memory |

| 7490 | decade counter (separate divide-by-2 and divide-by-5 sections) |

| 7491 | 8-bit shift register, serial In, serial out, gated input |

| 7492 | divide-by-12 counter (separate divide-by-2 and divide-by-6 sections) |

| 7493 | 4-bit binary counter (separate divide-by-2 and divide-by-8 sections) |

| 7494 | 4-bit shift register, 2 элемента asynchronous presets |

| 7495 | 4-bit shift register, parallel In, parallel out, serial input |

| 7496 | 5-bit parallel-In/pa |

| 7497 | synchronous 6-bit binary rate multiplier |

| 741G97 | configurable multiple-funct |

| 7498 | 4-bit data selector/stora |

| 7499 | 4-bit bidirectional universal shift register |

| 74100 | 2 элемента 4-bit bistable latch |

| 74101 | AND-or-gated J-K negative-edge- |

| 74102 | AND-gated J-K negative-edge- |

| 74103 | 2 элемента J-K negative-edge- |

| 74104 | J-K master-slave flip-flop |

| 74105 | J-K master-slave flip-flop |

| 74106 | 2 элемента J-K negative-edge- |

| 74107 | 2 элемента J-K flip-flop with clear |

| 74107a | 2 элемента J-K negative-edge- |

| 74108 | 2 элемента J-K negative-edge- |

| 74109 | 2 элемента J-Not-K positive-edge- |

| 74110 | AND-gated J-K master-slave flip-flop with data lockout |

| 74111 | 2 элемента J-K master-slave flip-flop with data lockout |

| 74112 | 2 элемента J-K negative-edge- |

| 74113 | 2 элемента J-K negative-edge- |

| 74114 | 2 элемента J-K negative-edge- |

| 74116 | 2 элемента 4-bit latch with clear |

| 74118 | 6 элементов set/reset latch |

| 74119 | 6 элементов set/reset latch |

| 74120 | 2 элемента pulse synchronizer/d |

| 74121 | monostable multivibrator |

| 74122 | retriggerable monostable multivibrator with clear |

| 74123 | 2 элемента retriggerable monostable multivibrator with clear |

| 741G123 | 1 элемент retriggerable monostable multivibrator with clear |

| 74124 | 2 элемента voltage-contro |

| 74125 | 4е элемента bus с буффером with three-state outputs, negative enable |

| 741G125 | с буффером/Line driver, three-state output with active low output enable |

| 74126 | 4е элемента bus с буффером with three-state outputs, positive enable |

| 74128 | 4е элемента 2НЕ-ИЛИ Line driver |

| 741G126 | с буффером/line driver, three-state output with active high output enable |

| 74130 | 4е элемента 2И с буффером with 30 v открытыми коллекторами на выходах |

| 74131 | 4е элемента 2И с буффером with 15 v открытыми коллекторами на выходах |

| 74132 | 4е элемента 2НЕ-И schmitt trigger |

| 74133 | 1 элемент3НЕ-И |

| 74134 | 1 элемент2НЕ-И with three-state output |

| 74135 | 4е элемента exclusive-or/N |

| 74136 | 4е элемента 2-input XOR gate с открытыми коллекторами на выходах |

| 74137 | 3 to 8-line decoder/demult |

| 74138 | 3 to 8-line decoder/demult |

| 74139 | 2 элемента 2 to 4-line decoder/demult |

| 74140 | 2 элемента 4НЕ-И line driver |

| 74141 | Двоично-десяти |

| 74142 | decade counter/latch/ |

| 74143 | decade counter/latch/ |

| 74144 | decade counter/latch/ |

| 74145 | Двоично-десяти |

| 74147 | 1 элемент0-line to 4-line priority encoder |

| 74148 | 8-line to 3-line priority encoder |

| 74150 | 1 элемент6-line to 1-line data selector/multi |

| 74151 | 8-line to 1-line data selector/multi |

| 74152 | 8-line to 1-line data selector/multi |

| 74153 | 2 элемента 4-line to 1-line data selector/multi |

| 74154 | 4-line to 16-line decoder/demult |

| 74155 | 2 элемента 2-line to 4-line decoder/demult |

| 74156 | 2 элемента 2-line to 4-line decoder/demult |

| 74157 | 4е элемента 2-line to 1-line data selector/multi |

| 74158 | 4е элемента 2-line to 1-line data selector/multi |

| 74159 | 4-line to 16-line decoder/demult |

| 74160 | synchronous 4-bit decade counter with asynchronous clear |

| 74161 | synchronous 4-bit binary counter with asynchronous clear |

| 74162 | synchronous 4-bit decade counter with synchronous clear |

| 74163 | synchronous 4-bit binary counter with synchronous clear |

| 74164 | 8-bit parallel-out serial shift register with asynchronous clear |

| 74165 | 8-bit serial shift register, parallel Load, complementary outputs |

| 74166 | parallel-Load 8-bit shift register |

| 74167 | synchronous decade rate multiplier |

| 74168 | synchronous 4-bit up/down decade counter |

| 74169 | synchronous 4-bit up/down binary counter |

| 74170 | 4 by 4 register file с открытыми коллекторами на выходах |

| 74172 | 1 элемент6-bit multiple port register file with three-state outputs |

| 74173 | 4е элемента d flip-flop with three-state outputs |

| 74174 | 6 элементов d flip-flop with common clear |

| 74175 | 4е элемента d edge-triggered flip-flop with complementary outputs and asynchronous clear |

| 74176 | presettable decade (bi-quinary) counter/latch |

| 74177 | presettable binary counter/latch |

| 74178 | 4-bit parallel-acces |

| 74179 | 4-bit parallel-acces |

| 74180 | 9-bit odd/even parity bit generator and checker |

| 74181 | 4-bit arithmetic logic unit and function generator |

| 74182 | lookahead carry generator |

| 74183 | 2 элемента carry-save full adder |

| 74184 | BCD to binary converter |

| 74185 | binary to BCD converter |

| 74186 | 512-bit (64×8) read-only memory с открытыми коллекторами на выходах |

| 74187 | 1 элемент024-bit (256×4) read only memory с открытыми коллекторами на выходах |

| 74188 | 256-bit (32×8) programmable read-only memory с открытыми коллекторами на выходах |

| 74189 | 64-bit (16×4) ram with inverting three-state outputs |

| 74190 | synchronous up/down decade counter |

| 74191 | synchronous up/down binary counter |

| 74192 | synchronous up/down decade counter with clear |

| 74193 | synchronous up/down binary counter with clear |

| 74194 | 4-bit bidirectional universal shift register |

| 74195 | 4-bit parallel-acces |

| 74196 | presettable decade counter/latch |

| 74197 | presettable binary counter/latch |

| 74198 | 8-bit bidirectional universal shift register |

| 74199 | 8-bit bidirectional universal shift register with J-Not-K serial inputs |

| 74200 | 256-bit ram with three-state outputs |

| 74201 | 256-bit (256×1) ram with three-state outputs |

| 74206 | 256-bit ram с открытыми коллекторами на выходах |

| 74209 | 1 элемент024-bit (1024×1) ram with three-state output |

| 74210 | octal с буффером |

| 74219 | 64-bit (16×4) ram with noninverting three-state outputs |

| 74221 | 2 элемента monostable multivibrator with schmitt trigger input |

| 74222 | 1 элемент6 by 4 synchronous FIFO memory with three-state outputs |

| 74224 | 1 элемент6 by 4 synchronous FIFO memory with three-state outputs |

| 74225 | asynchronous 16×5 FIFO memory |

| 74226 | 4-bit parallel latched bus transceiver with three-state outputs |

| 74230 | octal буффер/драйвер с three-state outputs |

| 74232 | 4е элемента NOR Schmitt trigger |

| 74237 | 1 элемент-of-8 decoder/demult |

| 74238 | 1 элемент-of-8 decoder/demult |

| 74239 | 2 элемента 2-of-4 decoder/demult |

| 74240 | octal с буффером with Inverted three-state outputs |

| 74241 | octal с буффером with noninverted three-state outputs |

| 74242 | 4е элемента bus transceiver with Inverted three-state outputs |

| 74243 | 4е элемента bus transceiver with noninverted three-state outputs |

| 74244 | octal с буффером with noninverted three-state outputs |

| 74245 | octal bus transceiver with noninverted three-state outputs |

| 74246 | Двоично-десяти |

| 74247 | Двоично-десяти |

| 74248 | Двоично-десяти |

| 74249 | Двоично-десяти |

| 74251 | 8-line to 1-line data selector/multi |

| 74253 | 2 элемента 4-line to 1-line data selector/multi |

| 74255 | 2 элемента 4-bit addressable latch |

| 74256 | 2 элемента 4-bit addressable latch |

| 74257 | 4е элемента 2-line to 1-line data selector/multi |

| 74258 | 4е элемента 2-line to 1-line data selector/mulit |

| 74259 | 8-bit addressable latch |

| 74260 | 2 элемента 5-input NOR gate |

| 74261 | 2-bit by 4-bit parallel binary multiplier |

| 74265 | 4е элемента complementary output elements |

| 74266 | 4е элемента 2-input XNOR gate with open collectoroutpu |

| 74270 | 2048-bit (512×4) read only memory с открытыми коллекторами на выходах |

| 74271 | 2048-bit (256×8) read only memory с открытыми коллекторами на выходах |

| 74273 | 8-bit register with reset |

| 74274 | 4-bit by 4-bit binary multiplier |

| 74275 | 7-bit slice Wallace tree |

| 74276 | 4е элемента J-Not-K edge-triggered Flip-Flops with separate clocks, common preset and clear |

| 74278 | 4-bit cascadeable priority registers with latched data inputs |

| 74279 | 4е элемента set-reset latch |

| 74280 | 9-bit odd/even Parity bit Generator/chec |

| 74281 | 4-bit parallel binary accumulator |

| 74283 | 4-bit binary Full adder |

| 74284 | 4-bit by 4-bit parallel binary multiplier (low order 4 bits of product) |

| 74285 | 4-bit by 4-bit parallel binary multiplier (high order 4 bits of product) |

| 74287 | 1 элемент024-bit (256×4) programmable read-only memory with three-state outputs |

| 74288 | 256-bit (32×8) programmable read-only memory with three-state outputs |

| 74289 | 64-bit (16×4) RAM с открытыми коллекторами на выходах |

| 74290 | decade counter (separate divide-by-2 and divide-by-5 sections) |

| 74291 | 4-bit universal shift register, binary up/down counter, synchronous |

| 74292 | programmable frequency divider/digita |

| 74293 | 4-bit binary counter (separate divide-by-2 and divide-by-8 sections) |

| 74294 | programmable frequency divider/digita |

| 74295 | 4-bit bidirectional register with three-state outputs |

| 74297 | digital phase-locked-l |

| 74298 | 4е элемента 2-input multiplexer with storage |

| 74299 | 8-bit bidirectional universal shift/storage register with three-state outputs |

| 74301 | 256-bit (256×1) random access memory с выходами с открытыми коллекторами |

| 74309 | 1 элемент024-bit (1024×1) random access memory с выходами с открытыми коллекторами |

| 74310 | octal с буффером с триггерами Шмитта на входах |

| 74314 | 1 элемент024-bit random access memory |

| 74320 | crystal controlled oscillator |

| 74322 | 8-bit shift register with sign extend, three-state outputs |

| 74323 | 8-bit bidirectional universal shift/storage register with three-state outputs |

| 74324 | voltage controlled oscillator (or crystal controlled) |

| 74340 | octal с буффером с триггерами Шмитта на входах and three-state inverted outputs |

| 74341 | octal с буффером с триггерами Шмитта на входах and three-state noninverted outputs |

| 74344 | octal с буффером с триггерами Шмитта на входах and three-state noninverted outputs |

| 74348 | 8 to 3-line priority encoder with three-state outputs |

| 74350 | 4-bit shifter with three-state outputs |

| 74351 | 2 элемента 8-line to 1-line data selectors/mult |

| 74352 | 2 элемента 4-line to 1-line data selectors/mult |

| 74353 | 2 элемента 4-line to 1-line data selectors/mult |

| 74354 | 8 to 1-line data selector/multi |

| 74356 | 8 to 1-line data selector/multi |

| 74361 | bubble memory function timing generator |

| 74362 | four-phase clock generator/driv |

| 74365 | 6 элементов с буффером with noninverted three-state outputs |

| 74366 | 6 элементов с буффером with Inverted three-state outputs |

| 74367 | 6 элементов с буффером with noninverted three-state outputs |

| 74368 | 6 элементов с буффером with Inverted three-state outputs |

| 74370 | 2048-bit (512×4) read-only memory with three-state outputs |

| 74371 | 2048-bit (256×8) read-only memory with three-state outputs |

| 74373 | octal transparent latch with three-state outputs |

| 741G373 | 1 элемент transparent latch with three-state output |

| 74374 | octal register with three-state outputs |

| 741G374 | 1 элемент d-type flip-flop with three-state output |

| 74375 | 4е элемента bistable latch |

| 74376 | 4е элемента J-Not-K flip-flop with common clock and common clear |

| 74377 | 8-bit register with clock enable |

| 74378 | 6-bit register with clock enable |

| 74379 | 4-bit register with clock enable and complementary outputs |

| 74380 | 8-bit multifunction register |

| 74381 | 4-bit arithmetic logic unit/function generator with generate and propagate outputs |

| 74382 | 4-bit arithmetic logic unit/function generator with ripple carry and overflow outputs |

| 74385 | 4е элемента 4-bit adder/subtract |

| 74386 | 4е элемента 2-input XOR gate |

| 74387 | 1 элемент024-bit (256×4) programmable read-only memory с открытыми коллекторами на выходах |

| 74388 | 4-bit register with standard and three-state outputs |

| 74390 | 2 элемента 4-bit decade counter |

| 74393 | 2 элемента 4-bit binary counter |

| 74395 | 4-bit universal shift register with three-state outputs |

| 74398 | 4е элемента 2-input mulitplexers with storage and complementary outputs |

| 74399 | 4е элемента 2-input mulitplexer with storage |

| 74405 | 1 элемент to 8 decoder, equivalent to Intel 8205, only found as UCY74S405 so might be non-TI number |

| 74408 | 8-bit parity tree |

| 74412 | multi-mode с буфферомed 8-bit latches with three-state outputs and clear |

| 74423 | 2 элемента retriggerable monostable multivibrator |

| 74424 | two-phase clock generator/driv |

| 74425 | 4е элемента gates with three-state outputs and active low enables |

| 74426 | 4е элемента gates with three-state outputs and active high enables |

| 74428 | system controller for 8080a |

| 74438 | system controller for 8080a |

| 74440 | 4е элемента tridirectional bus transceiver with noninverted открытыми коллекторами на выходах |

| 74441 | 4е элемента tridirectional bus transceiver with Inverted открытыми коллекторами на выходах |

| 74442 | 4е элемента tridirectional bus transceiver with noninverted three-state outputs |

| 74443 | 4е элемента tridirectional bus transceiver with Inverted three-state outputs |

| 74444 | 4е элемента tridirectional bus transceiver with Inverted and noninverted three-state outputs |

| 74448 | 4е элемента tridirectional bus transceiver with Inverted and noninverted открытыми коллекторами на выходах |

| 74450 | 1 элемент6-to-1 multiplexer with complementary outputs |

| 74451 | 2 элемента 8-to-1 multiplexer |

| 74452 | 2 элемента decade counter, synchronous |

| 74453 | 2 элемента binary counter, synchronous |

| 74453 | 4е элемента 4-to-1 multiplexer |

| 74454 | 2 элемента decade up/down counter, synchronous, preset input |

| 74455 | 2 элемента binary up/down counter, synchronous, preset input |

| 74456 | NBCD (Natural binary coded decimal) adder |

| 74460 | bus transfer switch |

| 74461 | 8-bit presettable binary counter with three-state outputs |

| 74462 | fiber-optic link transmitter |

| 74463 | fiber-optic link receiver |

| 74465 | octal с буффером with three-state outputs |

| 74468 | 2 элемента mos-to-ttL level converter |

| 74470 | 2048-bit (256×8) programmable read-only memory с открытыми коллекторами на выходах |

| 74471 | 2048-bit (256×8) programmable read-only memory with three-state outputs |

| 74472 | programmable read-only memory с открытыми коллекторами на выходах |

| 74473 | programmable read-only memory with three-state outputs |

| 74474 | programmable read-only memory с открытыми коллекторами на выходах |

| 74475 | programmable read-only memory with three-state outputs |

| 74481 | 4-bit slice processor elements |

| 74482 | 4-bit slice expandable control elements |

| 74484 | BCD-to-binary converter |

| 74485 | binary-to-BCD converter |

| 74490 | 2 элемента decade counter |

| 74491 | 1 элемент0-bit binary up/down counter with limited preset and three-state outputs |

| 74498 | 8-bit bidirectional shift register with parallel inputs and three-state outputs |

| 74508 | 8-bit multiplier/div |

| 74520 | 8-bit comparator |

| 74521 | 8-bit comparator |

| 74526 | fuse programmable identity comparator, 16 bit |

| 74527 | fuse programmable identity comparator, 8 bit + 4 bit conventional Identity comparator |

| 74528 | fuse programmable Identity comparator, 12 bit |

| 74531 | octal transparent latch with 32 ma three-state outputs |

| 74532 | octal register with 32 ma three-state outputs |

| 74533 | octal transparent latch with inverting three-state Logic outputs |

| 74534 | octal register with inverting three-state outputs |

| 74535 | octal transparent latch with inverting three-state outputs |

| 74536 | octal register with inverting 32 ma three-state outputs |

| 74537 | Двоично-десяти |

| 74538 | 1 элемент of 8 decoder with three-state outputs |

| 74539 | 2 элемента 1 of 4 decoder with three-state outputs |

| 74540 | inverting octal с буффером with three-state outputs |

| 74541 | non-inverting octal с буффером with three-state outputs |

| 74544 | non-inverting octal registered transceiver with three-state outputs |

| 74558 | 8-bit by 8-bit multiplier with three-state outputs |

| 74560 | 4-bit decade counter with three-state outputs |

| 74561 | 4-bit binary counter with three-state outputs |

| 74563 | 8-bit d-type transparent latch with inverting three-state outputs |

| 74564 | 8-bit d-type edge-triggered register with inverting three-state outputs |

| 74568 | decade up/down counter with three-state outputs |

| 74569 | binary up/down counter with three-state outputs |

| 74573 | octal D-type transparent latchwith three-state outputs |

| 74574 | octal D-type edge-triggered flip-flop with three-state outputs |

| 74575 | octal D-type flip-flop with synchronous clear, three-state outputs |

| 74576 | octal D-type flip-flop with inverting three-state outputs |

| 74577 | octal D-type flip-flop with synchronous clear, inverting three-state outputs |

| 74580 | octal transceiver/la |

| 74589 | 8-bit shift register with input latch, three-state outputs |

| 74590 | 8-bit binary counter with output registers and three-state outputs |

| 74592 | 8-bit binary counter with input registers |

| 74593 | 8-bit binary counter with input registers and three-state outputs |

| 74594 | serial-in shift register with output registers |

| 74595 | serial-in shift register with output latches |

| 74596 | serial-in shift register with output registers and открытыми коллекторами на выходах |

| 74597 | serial-out shift register with input latches |

| 74598 | shift register with input latches |

| 74600 | dynamic memory refresh controller, transparent and burst modes, for 4K or 16K drams |

| 74601 | dynamic memory refresh controller, transparent and burst modes, for 64K drams |

| 74602 | dynamic memory refresh controller, cycle steal and burst modes, for 4K or 16K drams |

| 74603 | dynamic memory refresh controller, cycle steal and burst modes, for 64K drams |

| 74604 | octal 2-input multiplexer with latch, high-speed, with three-state outputs |

| 74605 | latch, high-speed, с открытыми коллекторами на выходах |

| 74606 | octal 2-input mulitplexer with latch, glitch-free, with three-state outputs |

| 74607 | octal 2-input mulitplexer with latch, glitch-free, с открытыми коллекторами на выходах |

| 74608 | memory cycle controller |

| 74610 | memory mapper, latched, three-state outputs |

| 74611 | memory mapper, latched, открытыми коллекторами на выходах |

| 74612 | memory mapper, three-state outputs |

| 74613 | memory mapper, открытыми коллекторами на выходах |

| 74620 | octal bus transceiver, inverting, three-state outputs |

| 74621 | octal bus transceiver, noninverting, открытыми коллекторами на выходах |

| 74622 | octal bus transceiver, inverting, открытыми коллекторами на выходах |

| 74623 | octal bus transceiver, noninverting, three-state outputs |

| 74624 | voltage-contro |

| 74625 | 2 элемента voltage-contro |

| 74626 | 2 элемента voltage-contro |

| 74627 | 2 элемента voltage-contro |

| 74628 | voltage-contro |

| 74629 | 2 элемента voltage-contro |

| 74630 | 1 элемент6-bit error detection and correction (EDAC) with three-state outputs |

| 74631 | 1 элемент6-bit error detection and correction с открытыми коллекторами на выходах |

| 74632 | 32-bit error detection and correction |

| 74638 | octal bus transceiver with inverting three-state outputs |

| 74639 | octal bus transceiver with noninverting three-state outputs |

| 74640 | octal bus transceiver with inverting three-state outputs |

| 74641 | octal bus transceiver with noninverting открытыми коллекторами на выходах |

| 74642 | octal bus transceiver with inverting открытыми коллекторами на выходах |

| 74643 | octal bus transceiver with mix of inverting and noninverting three-state outputs |

| 74644 | octal bus transceiver with mix of inverting and noninverting открытыми коллекторами на выходах |

| 74645 | octal bus transceiver |

| 74646 | octal bus transceiver/la |

| 74647 | octal bus transceiver/la |

| 74648 | octal bus transceiver/la |

| 74649 | octal bus transceiver/la |

| 74651 | octal bus transceiver/re |

| 74652 | octal bus transceiver/re |

| 74653 | octal bus transceiver/re |

| 74654 | octal bus transceiver/re |

| 74658 | octal bus transceiver with Parity, inverting |

| 74659 | octal bus transceiver with Parity, noninverting |

| 74664 | octal bus transceiver with Parity, inverting |

| 74665 | octal bus transceiver with Parity, noninverting |

| 74668 | synchronous 4-bit decade Up/down counter |

| 74669 | synchronous 4-bit binary Up/down counter |

| 74670 | 4 by 4 register File with three-state outputs |

| 74671 | 4-bit bidirectional shift register/latch /multiplexer with three-state outputs |

| 74672 | 4-bit bidirectional shift register/latch |

| 74673 | 1 элемент6-bit serial-in serial-out shift register with output storage registers, three-state outputs |

| 74674 | 1 элемент6-bit parallel-in serial-out shift register with three-state outputs |

| 74677 | 1 элемент6-bit address comparator with enable |

| 74678 | 1 элемент6-bit address comparator with latch |

| 74679 | 1 элемент2-bit address comparator with latch |

| 74680 | 1 элемент2-bit address comparator with enable |

| 74681 | 4-bit parallel binary accumulator |

| 74682 | 8-bit magnitude comparator |

| 74683 | 8-bit magnitude comparator с открытыми коллекторами на выходах |

| 74684 | 8-bit magnitude comparator |

| 74685 | 8-bit magnitude comparator с открытыми коллекторами на выходах |

| 74686 | 8-bit magnitude comparator with enable |

| 74687 | 8-bit magnitude comparator with enable |

| 74688 | 8-bit equality comparator |

| 74689 | 8-bit magnitude comparator с открытыми коллекторами на выходах |

| 74690 | three state outputs |

| 74691 | 4-bit binary counter/latch/ |

| 74692 | 4-bit decimal counter/latch/ |

| 74693 | 4-bit binary counter/latch/ |

| 74694 | 4-bit decimal counter/latch/ |

| 74695 | 4-bit binary counter/latch/ |

| 74696 | 4-bit decimal counter/regist |

| 74697 | 4-bit binary counter/regist |

| 74698 | 4-bit decimal counter/regist |

| 74699 | 4-bit binary counter/regist |

| 74716 | programmable decade counter |

| 74718 | programmable binary counter |

| 74724 | voltage controlled multivibrator |

| 74740 | octal с буффером/Line driver, inverting, three-state outputs |

| 74741 | octal с буффером/Line driver, noninverting, three-state outputs, mixed enable polarity |

| 74744 | octal с буффером/Line driver, noninverting, three-state outputs |

| 74748 | 8 to 3-line priority encoder |

| 74779 | 8-bit bidirectional binary counter (3-state) |

| 74783 | synchronous address mulitplexer |

| 74790 | error detection and correction (EDAC) |

| 74794 | 8-bit register with readback |

| 74795 | octal с буффером with three-state outputs |

| 74796 | octal с буффером with three-state outputs |

| 74797 | octal с буффером with three-state outputs |

| 74798 | octal с буффером with three-state outputs |

| 74804 | 6 элементов 2НЕ-И drivers |

| 74805 | 6 элементов 2НЕ-ИЛИ drivers |

| 74808 | 6 элементов 2-input AND drivers |

| 74832 | 6 элементов 2-input OR drivers |

| 74848 | 8 to 3-line priority encoder with three-state outputs |

| 74873 | octal transparent latch |

| 74874 | octal d-type flip-flop |

| 74876 | octal d-type flip-flop with inverting outputs |

| 74878 | 2 элемента 4-bit d-type flip-flop with synchronous clear, noninverting three-state outputs |

| 74879 | 2 элемента 4-bit d-type flip-flop with synchronous clear, inverting three-state outputs |

| 74880 | octal transparent latchwith inverting outputs |

| 74881 | arithmetic logic unit |

| 74882 | 32-bit lookahead carry generator |

| 74888 | 8-bit slice processor |

| 74901 | 6 элементов inverting TTL с буффером |

| 74902 | 6 элементов non-inverting TTL с буффером |

| 74903 | 6 элементов inverting CMOS с буффером |

| 74904 | 6 элементов non-inverting CMOS с буффером |

| 74905 | 1 элемент2-Bit successive approximation register |

| 74906 | 6 элементов open drain n-channel с буфферомs |