Комбинационные схемы

Если рассматривать микросхему при сильном увеличении, можно увидеть её стройную архитектуру. Чтобы понять, как она работает, вспомним, что компьютер работает на электричестве, то есть любая информация представлена в компьютере в виде электрических импульсов.

Преобразование информации в ЭВМ производится электронными устройствами (логическими схемами) двух классов: комбинационными схемами и цифровыми автоматами.

Комбинационной схемой (КС) называется логическая схема, комбинация сигналов на выходе которой в любой момент времени однозначно определяется комбинацией сигналов на её входе.

Реализуемый в этих схемах способ обработки информации называется комбинационным, так как результат обработки информации зависит от комбинации входных сигналов и вырабатывается сразу при подаче входной информации.

Закон функционирования комбинационной

схемы определен, если задано соответствие

между ее входными и выходными сигналами

(например, в виде таблицы истинности),

при этом охватываются все сочетания

входных сигналов, а их очередность

следования не имеет значения.

Примером КС могут служить разнообразные шифраторы, дешифраторы, преобразователи кодов, сумматоры и целый ряд других схем, не содержащих элементов памяти.

Цифровые автоматы – это логические устройства, в которых помимо логических элементов имеются элементы памяти. Значение выходных сигналов такого устройства зависит не только от аргументов на входе в данный момент времени, но и от предыдущего состояния автомата, которое фиксируется элементами памяти. В качестве элементов памяти могут использоваться триггеры.

Комбинационную схему реализуют при помощи т. н.

Логический вентиль – базовый

элемент комбинационной схемы, выполняющий

элементарную логическую операцию,

преобразуя таким образом множество

входных логических сигналов в выходной

логический сигнал. Логика работы вентиля

основана на битовых операциях с входными

цифровыми сигналами в качестве операндов. При создании комбинационной схемы

вентили соединяют между собой, при этом,

если вентиль не выходной, то его выход

должен быть подключён к одному или к

нескольким входам других вентилей. В

настоящее время в созданных человеком

цифровых устройствах доминируют

электронные логические вентили на базе

полевых транзисторов, однако в прошлом

для создания вентилей использовались

и другие устройства, например,

электромагнитные реле, гидравлические

устройства, а также механические

устройства. В поисках более совершенных

логических вентилей исследуются

квантовые устройства, биологические

молекулы, фононные тепловые системы.

При создании комбинационной схемы

вентили соединяют между собой, при этом,

если вентиль не выходной, то его выход

должен быть подключён к одному или к

нескольким входам других вентилей. В

настоящее время в созданных человеком

цифровых устройствах доминируют

электронные логические вентили на базе

полевых транзисторов, однако в прошлом

для создания вентилей использовались

и другие устройства, например,

электромагнитные реле, гидравлические

устройства, а также механические

устройства. В поисках более совершенных

логических вентилей исследуются

квантовые устройства, биологические

молекулы, фононные тепловые системы.

В цифровой электронике логический уровень сигнала представлен в виде уровня напряжения (попадающего в один из двух диапазонов) или в виде значения тока. Это зависит от типа используемой технологии построения электронной логики. Поэтому любой тип электронного вентиля требует наличия питания для приведения выходного сигнала к необходимым уровням сигнала.

Название элемента | Обозначение |

И (конъюнктор) | |

И-НЕ (штрих Шеффера) | |

ИЛИ (дизъюнктор) | |

ИЛИ-НЕ (стрелка Пирса) | |

ИСКЛЮЧАЮЩЕЕ ИЛИ (xor) | |

ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ (эквиваленция) | |

НЕ (инвертор) |

Любой сколь угодно сложный элемент

компьютера может быть сконструирован

из элементарных вентилей.

Пример 3 (задача синтеза комбинационной схемы). Приёмная комиссия в составе трех членов комиссии и одного председателя решает судьбу абитуриента большинством голосов. В случае равного распределения голосов большинство определяется той группой, в которой оказался председатель приемной комиссии. Построить комбинационную схему, обеспечивающую определение большинства голосов.

►

А | B | C | D (председатель) | F(А, B, C, D) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 0 | 1 | 0 |

0 | 1 | 0 | 0 | |

0 | 0 | 1 | 1 | 1 |

0 | 1 | 0 | 0 | |

0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 0 |

0 | 1 | 1 | 1 | |

1 | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 1 | 1 |

1 | 0 | 1 | 0 | 0 |

1 | 0 | 1 | 1 | 1 |

1 | 1 | 0 | 0 | |

1 | 1 | 0 | 1 | 1 |

1 | 1 | 1 | 0 | 1 |

1 | 1 | 1 | 1 | 1 |

СДНФ и её упрощение:

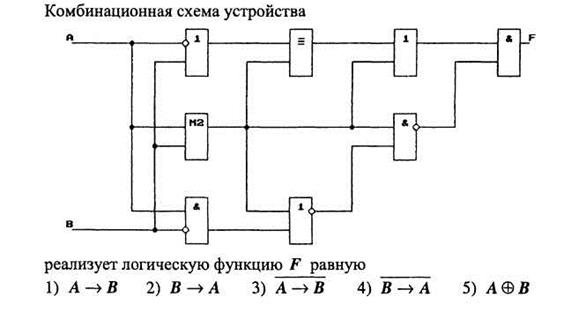

Комбинационная схема:

Построим минимальную ДНФ:

. Комбинационная схема:

Комбинационная схема:

(Минимальная КНФ: )

Применим к минимальной ДНФ дистрибутивный закон, вынеся D за скобки:

. В результате получим ещё более простую комбинационную схему:

◄

~ 9 ~ © LKN

Комбинационные схемы — CoderLessons.com

Комбинационная схема – это схема, в которой мы объединяем различные элементы схемы, например, кодер, декодер, мультиплексор и демультиплексор. Некоторые характеристики комбинационных схем следующие –

Выход комбинационной цепи в любой момент времени зависит только от уровней, присутствующих на входных клеммах.

Комбинационная схема не использует никакой памяти. Предыдущее состояние входа не влияет на текущее состояние схемы.

Комбинационная схема может иметь n входов и m выходов.

Выход комбинационной цепи в любой момент времени зависит только от уровней, присутствующих на входных клеммах.

Комбинационная схема не использует никакой памяти. Предыдущее состояние входа не влияет на текущее состояние схемы.

Комбинационная схема может иметь n входов и m выходов.

Блок-схема

Мы собираемся разработать несколько важных комбинационных схем следующим образом.

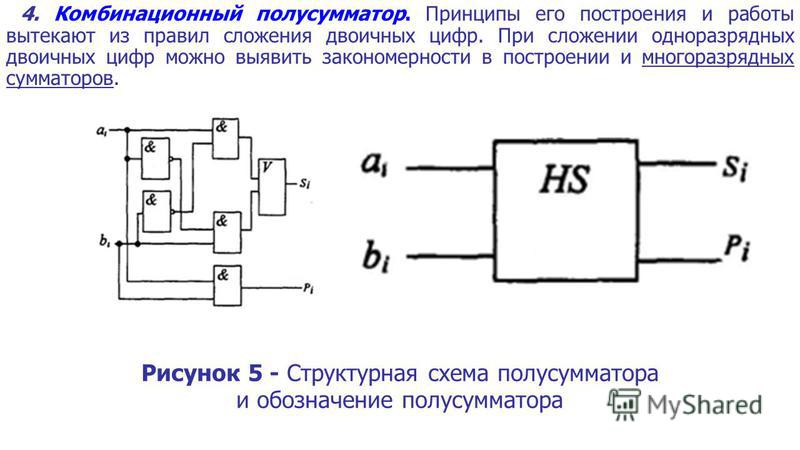

Полумесяц

Половина сумматора представляет собой комбинационную логическую схему с двумя входами и двумя выходами. Схема полусумметра предназначена для сложения двух однобитовых двоичных чисел A и B. Это базовый строительный блок для сложения двух однобитовых чисел. Эта схема имеет два выхода переноса и суммы .

Блок-схема

Таблица правды

Принципиальная электрическая схема

Полный сумматор

Полный сумматор разработан, чтобы преодолеть недостаток схемы Half Adder. Он может добавлять два однобитных числа A и B и переносить c. Полный сумматор представляет собой комбинацию из трех входов и двух выходов.

Блок-схема

Таблица правды

Принципиальная электрическая схема

N-битный параллельный сумматор

Полный сумматор способен добавлять только два однозначных двоичных числа вместе с вводом переноса. Но на практике нам нужно добавить двоичные числа, которые намного длиннее одного бита. Чтобы добавить два n-битных двоичных числа, нам нужно использовать n-битный параллельный сумматор. Он использует несколько полных сумматоров в каскаде. Выход переноса предыдущего полного сумматора соединен с вводом переноса следующего полного сумматора.

4-битный параллельный сумматор

На блок-схеме A 0 и B 0 представляют младший бит четырехбитовых слов A и B. Следовательно, Full Adder-0 является самой низкой ступенью. Следовательно, его C in постоянно равен 0. Остальные соединения точно такие же, как у n-битного параллельного сумматора, показанного на рис. Четырехбитный параллельный сумматор – очень распространенная логическая схема.

Блок-схема

N-разрядный параллельный вычитатель

Вычитание можно выполнить, взяв 1 или 2 в дополнение к числу, которое должно быть вычтено. Например, мы можем выполнить вычитание (AB), добавив 1 или 2 в дополнение к B к A. Это означает, что мы можем использовать двоичный сумматор для выполнения двоичного вычитания.

4-битный параллельный вычитатель

Вычитаемое число (B) сначала пропускается через инверторы для получения дополнения к 1. Затем 4-разрядный сумматор добавляет A и 2 к B для вычитания. S 3 S 2 S 1 S 0 представляет результат двоичного вычитания (AB), а выходной сигнал C out представляет полярность результата. Если A> B, то Cout = 0 и результат двоичной формы (AB), тогда C out = 1, и результат находится в форме дополнения 2.

Блок-схема

Половина вычитателей

Половина вычитателя представляет собой комбинированную схему с двумя входами и двумя выходами (разность и заем). Он выдает разницу между двумя двоичными битами на входе, а также выводит (заимствовать), чтобы указать, был ли заимствован 1. В вычитании (AB) A называется битом Minuend, а B называется битом Subtrahend.

Он выдает разницу между двумя двоичными битами на входе, а также выводит (заимствовать), чтобы указать, был ли заимствован 1. В вычитании (AB) A называется битом Minuend, а B называется битом Subtrahend.

Таблица правды

Принципиальная электрическая схема

Полные вычитатели

Недостаток половины вычитателя преодолевается полным вычитателем. Полный вычитатель представляет собой комбинационную схему с тремя входами A, B, C и двумя выходами D и C ‘. A – это «minuend», B – «вычитаемое», C – «заем», полученный на предыдущем этапе, D – это результат разницы, а C «- результат заимствования».

Таблица правды

Принципиальная электрическая схема

мультиплексоры

Мультиплексор – это особый тип комбинационной схемы. Есть n входов данных, один выход и m выбор входа с 2m = n. Это цифровая схема, которая выбирает один из n входов данных и направляет его на выход. Выбор одного из n входов осуществляется выбранными входами. В зависимости от цифрового кода, применяемого на выбранных входах, один из n источников данных выбирается и передается на один выход Y. E называется стробирующим или разрешающим входом, который полезен для каскадирования. Обычно это активный терминал низкого уровня, что означает, что он будет выполнять требуемую операцию, когда он низкий.

В зависимости от цифрового кода, применяемого на выбранных входах, один из n источников данных выбирается и передается на один выход Y. E называется стробирующим или разрешающим входом, который полезен для каскадирования. Обычно это активный терминал низкого уровня, что означает, что он будет выполнять требуемую операцию, когда он низкий.

Блок-схема

Мультиплексоры бывают разных вариантов

- Мультиплексор 2: 1

- Мультиплексор 4: 1

- Мультиплексор 16: 1

- Мультиплексор 32: 1

Блок-схема

Таблица правды

демультиплексоры

Демультиплексор выполняет обратную операцию мультиплексора, то есть он получает один вход и распределяет его по нескольким выходам. Он имеет только один вход, n выходов, m выбор входа. Одновременно выбирается только одна выходная строка, и вход передается на выбранную выходную строку. Демультиплексор эквивалентен однополюсному многоходовому переключателю, как показано на рис.

Демультиплексоры выпускаются в нескольких вариантах.

- Демультиплексор 1: 2

- Демультиплексор 1: 4

- Демультиплексор 1:16

- Демультиплексор 1:32

Блок-схема

Таблица правды

дешифратор

Декодер – комбинационная схема. Он имеет n входов и максимум m = 2n выходов. Декодер идентичен демультиплексору без ввода данных. Он выполняет операции, которые в точности противоположны кодировщику.

Блок-схема

Примеры декодеров следующие.

- Преобразователи кода

- BCD до семи сегментных декодеров

- Nixie ламповые декодеры

- Релейный привод

2 до 4-х строчный декодер

Блок-схема 2-4 линейного декодера показана на рис. A и B – два входа, где от D до D – четыре выхода. Таблица правды объясняет операции декодера. Это показывает, что каждый выход равен 1 только для определенной комбинации входов.

Блок-схема

Таблица правды

Логическая схема

кодировщик

Энкодер – комбинационная схема, которая предназначена для выполнения обратной операции декодера. Кодер имеет n входных линий и m выходных строк. Кодер генерирует m-битный двоичный код, соответствующий номеру цифрового входа. Кодер принимает n входных цифровых слов и преобразует их в m битов в другое цифровое слово.

Кодер имеет n входных линий и m выходных строк. Кодер генерирует m-битный двоичный код, соответствующий номеру цифрового входа. Кодер принимает n входных цифровых слов и преобразует их в m битов в другое цифровое слово.

Блок-схема

Примеры кодеров следующие.

- Приоритетные кодеры

- Десятичный кодировщик в BCD

- Восьмеричное в двоичный кодировщик

- Шестнадцатеричный к двоичному кодеру

Приоритетный кодировщик

Это особый тип кодировщика. Приоритет отдается линиям ввода. Если две или более строки ввода равны 1, то будет рассматриваться строка ввода с наивысшим приоритетом. Есть четыре входа D 0 , D 1 , D 2 , D 3 и два выхода Y 0 , Y 1 . Из четырех входов D 3 имеет самый высокий приоритет, а D 0 имеет самый низкий приоритет. Это означает, что если D 3 = 1, то Y 1, Y 1 = 11 независимо от других входов. Аналогично, если D 3 = 0 и D 2 = 1, тогда Y 1, Y 0 = 10 независимо от других входов.

Аналогично, если D 3 = 0 и D 2 = 1, тогда Y 1, Y 0 = 10 независимо от других входов.

Комбинационные логические схемы — Javatpoint

следующий → ← предыдущая Комбинационные логические схемы — это схемы, содержащие различные типы логических элементов. Проще говоря, схема, в которой объединены различные типы логических вентилей, известна как комбинационная логическая схема . Выход комбинационной схемы определяется из текущей комбинации входов, независимо от предыдущего входа. Входные переменные, логические элементы и выходные переменные являются основными компонентами комбинационной логической схемы. Существуют различные типы комбинационных логических схем, такие как сумматор, вычитатель, декодер, кодировщик, мультиплексор и демультиплексор. Существуют следующие характеристики комбинационной логической схемы:

Входная переменная ‘n’ поступает из внешнего источника, а выходная переменная ‘m’ направляется во внешний пункт назначения. Во многих приложениях источником или адресатом являются регистры хранения. ПолугадюкаПолусумматор представляет собой базовый строительный блок с двумя входами и двумя выходами. Сумматор используется для выполнения операции ИЛИ над двумя однобитными двоичными числами. перенос и сумма являются двумя выходными состояниями полусумматора. Полный сумматор Полусумматор используется для сложения только двух чисел. Чтобы преодолеть эту проблему, был разработан полный сумматор. Полный сумматор используется для сложения трех 1-битных двоичных чисел A, B и переноса C. ПолувычитателиПолувычитатель также является строительным блоком для вычитания двух двоичных чисел. Он имеет два входа и два выхода. Эта схема используется для вычитания двух однобитовых двоичных чисел A и B. ‘diff ‘ и ‘заимствование’ — два выходных состояния полусумматора. Полные вычитателиПолувычитатель используется для вычитания только двух чисел. Чтобы решить эту проблему, был разработан полный вычитатель. Полный вычитатель используется для вычитания трех 1-битных чисел A, B и C, которые равны уменьшаемому, вычитаемому и заимствованному, соответственно. Полный вычитатель имеет три входных состояния и два выходных состояния, то есть diff и заимствование. Мультиплексоры Мультиплексор представляет собой комбинационную схему с n входами данных и одним выходом. ДемультиплексорыДемультиплексор выполняет операцию, обратную мультиплексору. Демультиплексор имеет только один вход, который распределен на несколько выходов. Одна выходная строка выбирается за раз путем выбора строк. Вход передается на выбранную выходную линию. ДекодерДекодер представляет собой комбинационную схему, имеющую n входов и максимум m = 2n выходов. Декодер такой же, как и демультиплексор. Единственная разница между демультиплексором и декодером заключается в том, что в декодере нет ввода данных. Декодер выполняет операцию, полностью противоположную кодировщику. Энкодер Кодер используется для выполнения операции, обратной декодеру. Кодер, имеющий n входов и m выходов, используется для создания m-битного двоичного кода, который связан с числом цифровых входов. Next TopicHalf Adder ← предыдущая следующий → |

Комбинированные схемы — GATE CSE Примечания

В цифровой электронике комбинационная схема — это схема, в которой выход зависит от текущей комбинации входов. Комбинационные схемы состоят из логических вентилей. Выход каждого логического элемента определяется его логической функцией.

Содержание

- Что такое комбинационные схемы?

- Применение комбинационных схем

- Типы комбинационных цепей

- Видео о комбинационных схемах

Что такое комбинационные схемы?

Комбинационная схема — это цифровая схема, выход которой зависит не только от текущего входа, но и от последовательности прошлых входов. Таким образом, выход комбинационной схемы можно рассматривать как функцию всех входов, прошлых и настоящих. Этот тип схемы противопоставляется последовательной схеме, в которой выход зависит не только от текущего входа, но и от состояния схемы, то есть ее предыдущей истории.

Этот тип схемы противопоставляется последовательной схеме, в которой выход зависит не только от текущего входа, но и от состояния схемы, то есть ее предыдущей истории.

Применение комбинационных схем

Комбинационная схема представляет собой электронную схему, в которой выход зависит от текущей комбинации входов. Комбинационные схемы используются в цифровой электронике, такой как компьютеры, для выполнения операций с данными.

Примером комбинационной схемы является полный сумматор, который принимает на вход две двоичные цифры и выдает бит суммы и бит переноса на выходе. Полные сумматоры используются во многих цифровых устройствах, включая калькуляторы и компьютеры.

Другим примером комбинационной схемы является мультиплексор. Мультиплексор принимает несколько входных сигналов и выбирает один из них для передачи на выход. Мультиплексоры используются во многих приложениях, включая передачу данных и компьютерную память.

Комбинационные схемы могут быть созданы с использованием различных логических элементов, таких как элементы И, элементы ИЛИ и элементы НЕ.

Типы комбинационных цепей

Существует три основных типа комбинационных схем: декодеры, кодировщики и мультиплексоры.

- Декодеры представляют собой комбинационные схемы, преобразующие двоичный код в форму, удобную для чтения человеком. Например, декодер может взять четырехбитное двоичное число и преобразовать его в семисегментный дисплей. Кодировщики

- — это комбинационные схемы, преобразующие информацию из одной формы в другую. Например, энкодер может взять семисегментный дисплей и преобразовать его в четырехбитное двоичное число.

- Мультиплексоры представляют собой комбинационные схемы, которые выбирают один из нескольких входных сигналов и посылают его на выход. Например, мультиплексор может принимать четыре входных сигнала и посылать на выход только один из них.

Видео о комбинационных схемах

Продолжайте учиться и следите за обновлениями, чтобы получать последние обновления об экзамене GATE, а также о критериях приемлемости GATE, GATE 2023, пропускной карте GATE, программе GATE, вопроснике GATE за предыдущий год и многом другом.

Полный сумматор имеет три входных состояния и два выходных состояния, т. е. суммирование и перенос.

Полный сумматор имеет три входных состояния и два выходных состояния, т. е. суммирование и перенос. Он также известен как селектор данных , который выбирает один вход из входов и направляет его на выход. С помощью выбранных входов выбирается одна входная линия из n-входных линий. Вход разрешения обозначается E, который используется в каскаде.

Он также известен как селектор данных , который выбирает один вход из входов и направляет его на выход. С помощью выбранных входов выбирается одна входная линия из n-входных линий. Вход разрешения обозначается E, который используется в каскаде. Кодер берет цифровое слово и преобразует его в другое цифровое слово.

Кодер берет цифровое слово и преобразует его в другое цифровое слово.