Прямые и инверсные логические сигналы микропроцессорной технике.

Прямые и инверсные логические сигналы микропроцессорной технике.

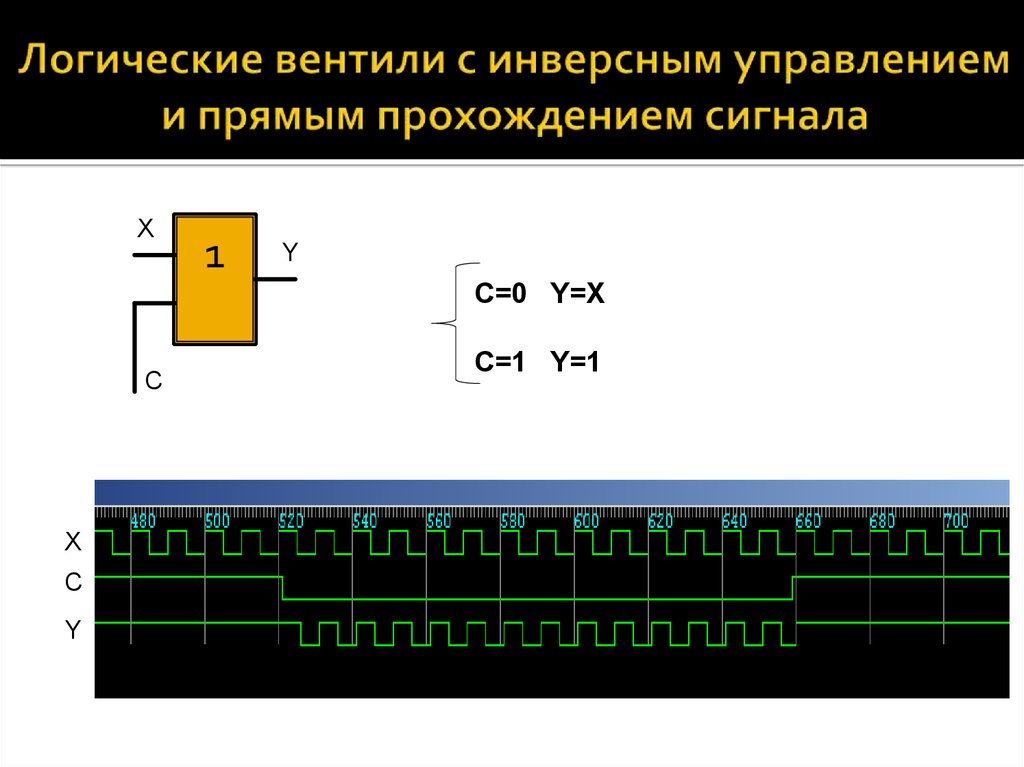

В микропроцессорной технике применяются прямые и

инверсные логические сигналы. В случае прямых сигналов логическому нулю

соответствует низкий уровень сигнала, логической единице — высокий. В случае

инверсных сигналов все наоборот. Инверсию сигналов обозначают разными

способами: перед названием сигнала ставят знак «минус», над именем

проводят черту, после имени ставят обратную косую черту или решетку. В данной

статье используется последний способ. Управляющие сигналы обычно инверсные. Это

так называемые L (Low)-активные сигналы, у которых активный уровень сигнала -

низкий. Это нужно, чтобы: повысить помехозащищенность, которая у ТТЛ

несимметричная. Входные токи стремятся подтянуть уровень к высокому, и в случае

прямых H (High)-активных сигналов это действует согласно с помехой, чреватой

ложными срабатываниями.

..D8, при этом

младший бит — D1. На рисунках принято старший бит изображать слева, а младший -

справа. Обозначение D[7:0] относится к группе сигналов D7, D6,…, D1, D0, a

D[0:7] — к тем же сигналам, но в порядке естественной нумерации.

..D8, при этом

младший бит — D1. На рисунках принято старший бит изображать слева, а младший -

справа. Обозначение D[7:0] относится к группе сигналов D7, D6,…, D1, D0, a

D[0:7] — к тем же сигналам, но в порядке естественной нумерации. В

двухбайтном слове, размещаемом в памяти, принят LH-порядок следования: адрес

слова указывает на младший байт L (Low), а старший байт Н (High) размещается по

адресу, на единицу большему. В двойном слове порядок будет аналогичным — адрес

укажет на самый младший байт, после которого будут размещены следующие по

старшинству. Этот порядок естествен для процессоров Intel. На рис. 1 показаны

диапазоны и способы представления двоичных нуля и единицы.

Эффективность любого сигнального

протокола состоит в конечных значениях логических уровней (напряжение,

соответствующее логическому «0» и «1») и их дискретности

(разности между уровнями логического «0» и «1»).

Разделение сигналов на группы по логическим уровням способствует уменьшению влияния электромагнитной интерференции и повышению эффективности протокола. Например, технология Rambus основана на новом электрическом интерфейсе RSL (Rambus Signaling Levels), который дает возможность получить результирующую частоту 800 МГц и более, а также использовать стандартный CMOS-интерфейс сигналов ввода-вывода ядра ASIC. Высокоскоростной протокол сигналов RSL использует низковольтный перекос номинальных напряжений логического «0» (1,8В) и логической «1» (1,0В) с перекосом всего-навсего в 800 мВ.

Рис. 1. Способы представления двоичных нуля и единицы: а) для цифровых элементов ТТЛ ; б) для цифровых CMOS – структур.

Таблица

2. Примеры сигнальных интерфейсов памяти.

Например, для стандартных

модулей SDR/DDR SDRAM DIMM используется низковольтная

транзисторно-транзисторная логика 3,3V-LVTTL (Low Voltage Transistor-Transistor

Logic) с интерфейсом 3,3 В, а для некоторых современных вариантов SDR/DDR PC133

и Registered DIMM намечается скорый переход с применением более совершенного

варианта терминирующей логики — SSTL_3 (Stub Series Terminated Logic) с

последующим переходом на SSTL_2. Использование дифференциального протокола

направлено на уменьшение задержек, связанных со временем переключения

транзистора между активными логическими уровнями: переключение между уровнями

логического «0» и «1» происходит не по достижении конечного

значения напряжения, а несколько ранее.

Например, в RSL,

при использовании линии опорного напряжения 1,4 В, уровень логической

«1» соответствует промежутку 1,2-1,0 В, а уровень логического

«0» — 1,6-1,8 В. Поэтому значение 1,2 В можно считать «1»,

а уровень 1,6 В — «0», причем реальная логическая дискретность теперь

составляет всего-навсего 0,4 В. Контрольным порогом срабатывания является точка

пересечения реального и дополняющего сигналов (VX — cross-point), уровень

которой составляет 50% от разности уровня опорного напряжения и порога

переключения между активными уровнями, оговоренными сигнальным протоколом.

Данная псевдо-дифференциальная схема позволяет не только компенсировать

задержки на переключение, но и значительно снизить влияние электромагнитной

интерференции за счет уменьшения длительности шума коммутации сигнала.

Например, в RSL,

при использовании линии опорного напряжения 1,4 В, уровень логической

«1» соответствует промежутку 1,2-1,0 В, а уровень логического

«0» — 1,6-1,8 В. Поэтому значение 1,2 В можно считать «1»,

а уровень 1,6 В — «0», причем реальная логическая дискретность теперь

составляет всего-навсего 0,4 В. Контрольным порогом срабатывания является точка

пересечения реального и дополняющего сигналов (VX — cross-point), уровень

которой составляет 50% от разности уровня опорного напряжения и порога

переключения между активными уровнями, оговоренными сигнальным протоколом.

Данная псевдо-дифференциальная схема позволяет не только компенсировать

задержки на переключение, но и значительно снизить влияние электромагнитной

интерференции за счет уменьшения длительности шума коммутации сигнала.

Для того чтобы любая синхронизируемая схема зафиксировала желаемое состояние, сигналы на входах должны установиться до синхронизирующего перепада за некоторое время, называемое временем установки TSETUP, И удерживаться после него в течение времени удержания THOLD. Значение этих параметров определяется типом и быстродействием синхронизируемой схемы, и в пределе один из них может быть нулевым.

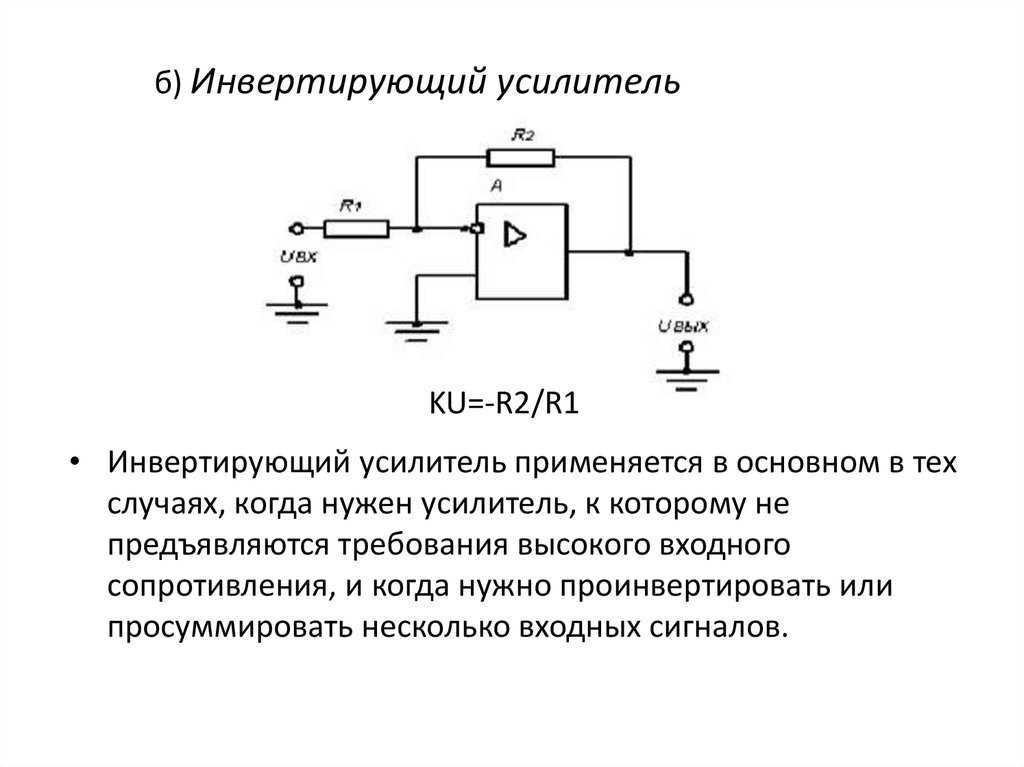

Инверсный выход — определение термина

Термин и определение

выход, выдающий сигнал инверсной полярности по сравнению со входным сигналом.

Еще термины по предмету «Электроника, электротехника, радиотехника»

Плотность энергии электромагнитного поля (Electromagnetic energy density)

физическая величина, равная отношению энергии электромагнитного поля в некотором объеме к этому объему.

Табличный функциональный преобразователь (LUT, Look-Up Table)

логический блок программируемых БИС/СБИС, реализованный на основе схем программируемой памяти.

Флэш-память (Flash Memory)

разновидность РПЗУ с электрическим стиранием информации и возможностью многократной перезаписи.

Похожие

- Инверсность

- Инверсный слой

- Выход

- Инверсный выключатель СВЧ

- Обратный (инверсный) счет

- Аварийный выход; запасной выход

- Дискретный выход

- Выход продукта

- Выход с рынка

- Выход пиломатериалов

- Выход по току

- Выход реакции

- Выход годного

- Выход из системы

- Выход из операции

- Выход процесса

- Подача на выходе

- Выход из гражданства

- Аварийный выход

Смотреть больше терминов

Научные статьи на тему «Инверсный выход»

базе транзисторов, резисторов и тому подобное, каждый из которых может иметь несколько входов и один выход. ..

..

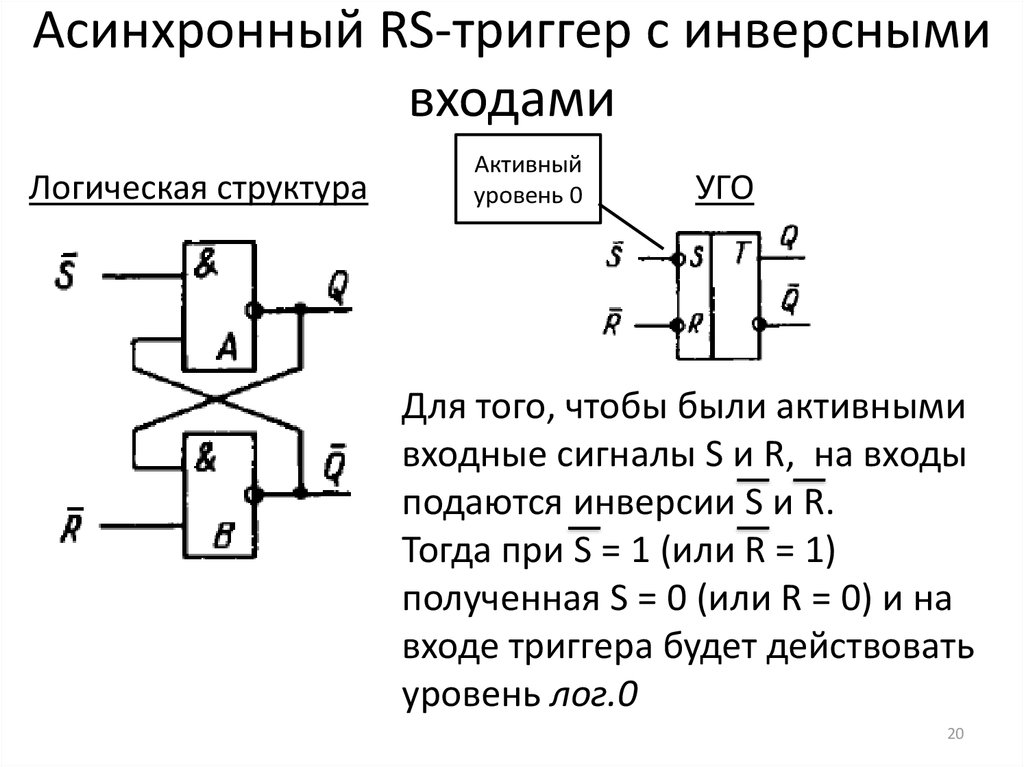

У триггера есть два входа, которые обозначены как R и S, и два выхода, обозначенные символом Q (прямым…

и инверсным, черта над Q обозначает отрицание)….

Работа триггера построена так, что прямой и инверсный выходы всегда являются противоположными по значению

Статья от экспертов

Научный журнал

Creative Commons

Автор24 — интернет-биржа студенческих работ

У представленной схемы имеется два инверсных входа: -R –…

В ее состав входят также два выхода: прямой выход — Q и инверсный выход — -Q….

Приход импульса на вход -R переводит выход Q в состояние единицы, а так как -S-сигнал единичный, то выход…

Если импульс входит на вход -S выход Q в единицу, выход -Q в нуль. …

…

выходы попадут в одно из устойчивых состояний.

Статья от экспертов

Рассматривается задача синтеза асимптотически оптимальных схем, реализующих булевы функции, при инверсных неисправностях на выходах элементов в базисе. Доказано, что почти все булевы функции можно реализовать асимптотически оптимальными по надежности схемами, которые функционируют с ненадежностью, асимптотически равной 3ε при ε→0, где ε вероятность инверсной неисправности на выходе базисного элемента. Сложность предлагаемых схем превышает сложность минимальных схем, построенных только из наде…

Научный журнал

Creative Commons

Повышай знания с онлайн-тренажером от Автор24!

- 📝 Напиши термин

- ✍️ Выбери определение из предложенных или загрузи свое

- 🤝 Тренажер от Автор24 поможет тебе выучить термины, с помощью удобных и приятных карточек

Возможность создать свои термины в разработке

Еще чуть-чуть и ты сможешь писать определения на платформе Автор24. Укажи почту и мы пришлем уведомление с обновлением ☺️

Укажи почту и мы пришлем уведомление с обновлением ☺️

— Что означает обратная полоса пропускания сигнала?

спросил

Изменено 8 месяцев назад

Просмотрено 824 раза

$\begingroup$

Я изучал двухлучевую модель в системах связи.

Текст, который я изучаю, имеет два сигнала: $u(t)$, который является прямой видимостью, и $u(t-t’)$, который является отраженным сигналом.

Цитаты,

Если передаваемый сигнал является узкополосным относительно разброса задержек ($B \ll \frac{1}{t’}$), то $u(t)$ приблизительно равно $u(t-t’)$.

- Что означает это утверждение?

- Как задержка связана с пропускной способностью?

Извините, если вопрос не был ясен с первого раза. Для источника можно обратиться к https://en.wikipedia.org/wiki/Two-ray_ground-reflection_model или Андреа Голдсмит Беспроводная связь (у меня страница 34, глава 2), которая цитирует выше.

Для источника можно обратиться к https://en.wikipedia.org/wiki/Two-ray_ground-reflection_model или Андреа Голдсмит Беспроводная связь (у меня страница 34, глава 2), которая цитирует выше.

Обратная ширина полосы сигнала составляет ($\frac{1}{B}$), а обратная разброс задержки составляет ($\frac{1}{t’}$). Так что либо ($B \ll \frac{1}{t’}$), либо эквивалентно ($t’ \ll \frac{1}{B}$).

Итак, позвольте мне перефразировать. Как я могу показать, что $u(t)$ приблизительно равно $u(t-t’)$, если задано либо ($B \ll \frac{1}{t’}$), либо эквивалентно ($t’ \ll \frac{1}{B}$). Другими словами, что является доказательством предложения в кавычках (или выделениях)?

- цифровая связь

- пропускная способность

- задержка

$\endgroup$

4

$\begingroup$

Хорошо, теперь стало понятнее. В двухлучевой модели у вас есть две версии сигнала; луч зрения $u(t)$ и отраженный вариант $u(t-\tau)$, где $\tau$ — разброс задержки канала.

В двухлучевой модели у вас есть две версии сигнала; луч зрения $u(t)$ и отраженный вариант $u(t-\tau)$, где $\tau$ — разброс задержки канала.

Если $\tau<<\frac{1}{B_s} \simeq T_s$, где $B_s$ и $T_s$ — ширина полосы и длительность сигнала, то сдвиг в отраженном варианте будет очень мал по сравнению с к продолжительности символа. Таким образом, версия LOS будет получена в момент времени $t_0$ до $t_0+T_s$, а отраженная версия будет получена в момент времени $t_0+\tau$ до $t_0+T_s+\tau$. Но $\tau< Что касается второго вопроса, максимальный разброс задержки канала связан с так называемой полосой когерентности канала. Грубо говоря, ширина полосы когерентности $B_c$ обратно пропорциональна максимальному разбросу задержки, в данном случае $\tau$. Если ширина полосы сигнала $B_s\simeq \frac{1}{T_s} $\endgroup$ Зарегистрируйтесь с помощью Google Зарегистрироваться через Facebook Зарегистрируйтесь, используя электронную почту и пароль Электронная почта Требуется, но никогда не отображается Электронная почта Требуется, но не отображается Зарегистрируйтесь или войдите в систему

Опубликовать как гость

Опубликовать как гость

Нажимая «Опубликовать свой ответ», вы соглашаетесь с нашими условиями обслуживания, политикой конфиденциальности и политикой использования файлов cookie

. Задержка

Задержка— Проектирование обратной системы с дискретным временем

спросил

Изменено 6 лет, 7 месяцев назад

Просмотрено 824 раза

$\begingroup$

Я пытаюсь разработать инверсионную систему с дискретным временем для устранения нежелательного эха в задаче передачи данных.

Эхо, вызванное каналом передачи, представлено как затухание с коэффициентом 0,9и задержку, соответствующую одной единице времени входной последовательности.

Принятый сигнал $y[n]$ может быть выражен следующим образом;

$$y[n] = x[n] + 0,9x[n-1]$$

В общем, я пытаюсь определить единичную импульсную характеристику причинно-обратной системы, чтобы обнаружить $x[n] $ из $y[n]$.