парафазный сигнал — это… Что такое парафазный сигнал?

- парафазный сигнал

- push-pull pulse output

парафазный сигнал

—

[Л.Г.Суменко. Англо-русский словарь по информационным технологиям. М.: ГП ЦНИИС, 2003.]Тематики

- информационные технологии в целом

EN

Русско-английский словарь нормативно-технической терминологии. academic.ru. 2015.

- парасланцы

- парафиза

Смотреть что такое «парафазный сигнал» в других словарях:

парафазный сигнал — — [Л.Г.Суменко. Англо русский словарь по информационным технологиям. М.: ГП ЦНИИС, 2003.] Тематики информационные технологии в целом EN push pull pulse output … Справочник технического переводчика

Электронный усилитель

Усилитель (электроника) — Электронный усилитель усилитель электрических сигналов, в усилительных элементах которого используется явление электрической проводимости в газах, вакууме и полупроводниках. Электронный усилитель может представлять собой как самостоятельное… … Википедия

Триггер — У этого термина существуют и другие значения, см. Триггер (значения). Триггер (триггерная система) класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под… … Википедия

Бит — Эта статья о единице измерения информации; другие значения: бит (значения). Наименование Международное по МЭК обозначение (англ.)[1] Русское По ГОСТ обозначение[2] Значение бит bit бит 1 октет, байт o, В Б (байт) 1 Б = 8 бит Бит (англ … Википедия

Синфазный сигнал — Википедия

Материал из Википедии — свободной энциклопедии

Текущая версия страницы пока не проверялась опытными участниками и может значительно отличаться от версии, проверенной 12 февраля 2017; проверки требует 1 правка. Текущая версия страницы пока не проверялась опытными участниками и может значительно отличаться от версии, проверенной 12 февраля 2017; проверки требует 1 правка.- Uсинф=U1+U22.{\displaystyle U_{\text{синф}}={\frac {U_{1}+U_{2}}{2}}.}

Синфазный сигнал можно рассчитать зная величину дифференциального сигнала Uдиф{\displaystyle U_{\text{диф}}} и величину аналогового сигнала U{\displaystyle U} «в роли уменьшаемого» на одном из выводов:

- Uсинф=U−Uдиф/2.{\displaystyle U_{\text{синф}}=U-U_{\text{диф}}/2.}

Электронные системы кабельной связи, например множество Ethernet-технологий, обычно построены по принципу передачи дифференциального сигнала через кабели, состоящие из витых пар. Синфазный сигнал в таких системах представляет собой помеху[2], которая должна быть подавлена на терминальном оборудовании[3]. Однако из-за разбалансировки пары и несовершенства терминальных устройств часть синфазного сигнала переходит в дифференциальный сигнал, чем вызывает искажения полезного сигнала и соответственно увеличение вероятности потери передаваемых данных.

Синфазный сигнал в дифференциальных усилителях[править | править код]

- ↑ Реферативная работа. Фабрикант В. Л. «Элементы автоматических устройств», 1981. с. 393 (недоступная ссылка с 12-02-2017 [1108 дней]).

- ↑ Возникающую, например, из-за электромагнитных наводок силовых кабелей.

- ↑ Журнал Сети и Системы Связи, номер 2 за 2001 год, статья: «Витая пара и радиочастотные помехи».

- ↑ Обычно из-за электронного моста, построенного на транзисторах, а также из-за источника тока, питающего его.

Преобразователь унарного сигнала в парафазный сигнал с нулевым спейсером

Преобразователь унарного сигнала в парафазный сигнал с нулевым спейсером относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных комбинационных, тригтерных, регистровых и вычислительных устройств, систем цифровой обработки информации.

Известен самосинхронный многоразрядный преобразователь унарного сигнала в парафазный сигнал [1, рис. 11.19], состоящий из элементов И-ИЛИ-НЕ, И-НЕ ИЛИ-НЕ и инверторов.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является формирователь парафазного сигнала с высоким активным уровнем сигнала управления [2], содержащий элемент ИЛИ-И-НЕ, два элемента ИЛИ-НЕ и инвертор.

Недостаток прототипа — унарный сигнал может изменяться только при пассивном уровне на входе управления.

Задача, решаемая в изобретении, заключается в обеспечении самосинхронной работы преобразователя унарного сигнала в парафазный с нулевым спейсером, разрешающего изменение унарного входа сразу по окончании формирования рабочего состояния на парафазном выходе.

Это достигается тем, что в преобразователь унарного сигнала в парафазный с нулевым спейсером, содержащий инвертор, элемент ИЛИ-И-НЕ, элемент ИЛИ-НЕ, унарный вход, вход управления, парафазный выход с нулевым спейсером, причем выход инвертора соединен с первым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ и первым входом элемента ИЛИ-НЕ, второй вход которого подключен к выходу элемента ИЛИ-И-НЕ, второй вход первой группы входов ИЛИ элемента ИЛИ-И-НЕ подключен к унарному входу, первый вход второй группы входов ИЛИ элемента ИЛИ-И-НЕ соединен с входом управления, согласно изобретению введены второй инвертор, второй элемент ИЛИ-И-НЕ, выход инверсии входа управления и индикаторный выход, третий вход первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ подключен к первому входу второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ, входу второго инвертора и входу управления, вторые входы вторых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ соединены друг с другом, выходом элемента ИЛИ-НЕ и индикаторным выходом преобразователя, третий вход второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ подключен к выходу первого инвертора, прямой составляющей парафазного выхода и первым входам первой и второй групп входов ИЛИ второго элемента ИЛИ-И-НЕ, выход первого элемента ИЛИ-И-НЕ соединен с инверсной составляющей парафазного выхода, вход первого инвертора соединен с выходом второго элемента ИЛИ-И-НЕ, второй вход первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ соединен с унарным входом, вход третьей группы входов ИЛИ второго элемента ИЛИ-И-НЕ соединен с выходом второго инвертора и выходом инверсии входа управления.

Предлагаемое устройство удовлетворяет критерию «существенные отличия». Действительно, элементы ИЛИ-НЕ, ИЛИ-И-НЕ и инвертор используются и в прототипе. Но способ их подключения к входам и выходам преобразователя запрещает изменение угарного входа при активном уровне на входе управления. Добавление в схему второго инвертора и второго элемента ИЛИ-И-НЕ и реализация описанных связей между ними и другими элементами схемы преобразователя позволили достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

Понятие «парафазный», используемое в тексте данной заявки, определяется следующим образом. Парафазным считается сигнал, представленный двумя составляющими — парой переменных {X, ХВ}, которые в активной фазе имеют взаимоинверсные значения: {Х=0, ХВ=1} или {Х=1, ХВ=0}. Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться двумя способами.

Первый способ предполагает использование парафазного сигнала со спейсером: когда переходу в следующее рабочее состояние обязательно предшествует переход в третье статическое состояние — спейсерное (нерабочее состояние или состояние гашения). Если используется состояние {1, 1}, то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние {0, 0} — парафазный сигнал с нулевым спейсером. Спейсерное состояние — статическое состояние, установка которого в самосинхронной схемотехнике должна фиксироваться индикатором окончания переходного процесса, в данном случае — окончания установки спейсерного состояния.

Второй способ предполагает использование парафазного сигнала без спейсера. При этом переход из одного рабочего статического состояния в другое осуществляется через динамическое (кратковременное) состояние: {1, 1} или {0, 0}, — называемое транзитным состоянием.

В материалах данной заявки речь идет о формировании на выходе преобразователя парафазного сигнала с нулевым спейсером, в дальнейшем — просто парафазного сигнала.

Унарный сигнал — обычный одиночный информационный сигнал, имеющий два возможных значения: 0 или 1. Вход управления переключением в состояние «1» отражает факт появления на информационном унарном входе нового значения, которое может и совпадать с предшествующим значением.

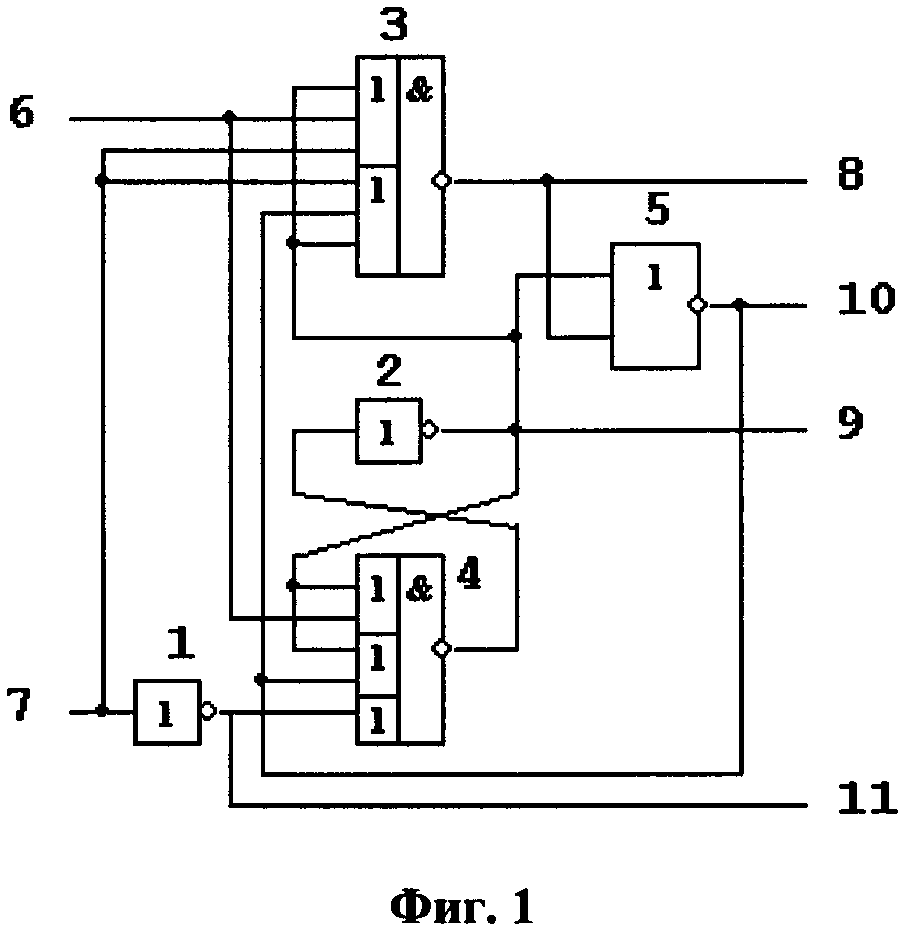

На фиг. 1 представлена схема преобразователя унарного сигнала в парафазный с нулевым спейсером. Схема содержит два инвертора 1-2, два элемента ИЛИ-И-НЕ 3-4, элемент ИЛИ-НЕ 5, унарный вход 6, вход управления 7, парафазный информационный выход 8-9, индикаторный выход 10, выход инверсии входа управления 11, вход инвертора 1 подключен к входу управления 7 и к первым входам первой и второй групп входов ИЛИ элемента ИЛИ-И-НЕ 3, выход инвертора 1 соединен с входом третьей группы входов ИЛИ элемента ИЛИ-И-НЕ 4 и выходом инверсии входа управления 11, вторые входы первых групп входов ИЛИ элементов ИЛИ-И-НЕ 3 и 4 подключены к унарному входу 6, третьи входы первой и второй групп входов ИЛИ элемента ИЛИ-И-НЕ 3 соединены с выходом инвертора 2, первыми входами первой и второй групп входов ИЛИ элемента ИЛИ-И-НЕ 4, прямой составляющей парафазного информационного выхода 9 и первым входом элемента ИЛИ-НЕ 5, второй вход которого подключен к выходу элемента ИЛИ-И-НЕ 3 и инверсной составляющей парафазного информационного выхода 8, вход инвертора 2 соединен с выходом элемента ИЛИ-И-НЕ 4, второй вход второй группы входов ИЛИ которого подключен ко второму входу второй группы входов ИЛИ элемента ИЛИ-И-НЕ 3, выходу элемента ИЛИ-НЕ 5 и индикаторному выходу 10.

Схема работает следующим образом. В спейсерной фазе на вход управления подается уровень логической 1, в результате обе составляющие парафазного выхода 8 и 9 принимают значение логического 0 и на индикаторном выходе 10 появляется логическая 1 как признак спейсера. При этом значение сигнала на унарном входе 6 никак не влияет на значения выходов преобразователя. В рабочей фазе на вход управления 7 подается значение логического 0, в результате чего парафазный выход 8, 9 переключится в рабочее состояние, соответствующее значению унарного входа 6. По окончании переключения парафазного выхода 8, 9 в рабочую фазу индикаторный выход 10 перейдет в логический 0, отражая окончание всех переходных процессов в преобразователе.

Особенности данной схемы по сравнению с прототипом следующие.

Вместо второго элемента ИЛИ-НЕ введены второй элемент ИЛИ-И-НЕ и второй инвертор. Это обеспечивает самосинхронность переключения преобразователя из рабочей фазы в спейсер и обратно и разрешает унарному сигналу переключаться в следующее рабочее значение сразу по окончании записи в преобразователь его текущего значения, т.е. еще в рабочей фазе сигнала управления.

Таким образом, предлагаемое устройство обеспечивает самосинхронную работу преобразователя унарного сигнала в парафазный сигнал с нулевым спейсером. Цель изобретения достигнута.

Источники информации

[1] Варшавский В.И., Кишиневский М.А., Мараховский В.Б. и др. Автоматное управление асинхронными процессами в ЭВМ и дискретных системах / Под ред. В.И.Варшавского. — М.: Наука. Гл. ред. физ.-мат.лит., 1986. — 400 с.

[2] Пат. 2469470 Российская Федерация, МПК Н03K 3/00. Формирователь парафазного сигнала с высоким активным уровнем входа управления / Степченков Ю.А., Дьяченко Ю.Г., Шнейдер А.Ю., Прокофьев А.А., Хилько Д.В.; заявитель и патентообладатель ИПИ РАН. — №2011129014/08; заявл. 13.07.11; опубл. 20.02.13, Бюл. №34. — 6 с.

Преобразователь унарного сигнала в парафазный сигнал с нулевым спейсером, содержащий инвертор, элемент ИЛИ-И-НЕ, элемент ИЛИ-НЕ, унарный вход, вход управления, парафазный выход с нулевым спейсером, причем выход инвертора соединен с первым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ и первым входом элемента ИЛИ-НЕ, второй вход которого подключен к выходу элемента ИЛИ-И-НЕ, второй вход первой группы входов ИЛИ элемента ИЛИ-И-НЕ подключен к унарному входу, первый вход второй группы входов ИЛИ элемента ИЛИ-И-НЕ соединен с входом управления, отличающийся тем, что в схему введены второй инвертор, второй элемент ИЛИ-И-НЕ, выход инверсии входа управления и индикаторный выход, третий вход первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ подключен к первому входу второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ, входу второго инвертора и входу управления, вторые входы вторых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ соединены друг с другом, выходом элемента ИЛИ-НЕ и индикаторным выходом преобразователя, третий вход второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ подключен к выходу первого инвертора, прямой составляющей парафазного выхода и первым входам первой и второй групп входов ИЛИ второго элемента ИЛИ-И-НЕ, выход первого элемента ИЛИ-И-НЕ соединен с инверсной составляющей парафазного выхода, вход первого инвертора соединен с выходом второго элемента ИЛИ-И-НЕ, второй вход первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ соединен с унарным входом, вход третьей группы входов ИЛИ второго элемента ИЛИ-И-НЕ соединен с выходом второго инвертора и выходом инверсии входа управления.

формирователь парафазного сигнала с низким активным уровнем входа управления — патент РФ 2475952

Изобретение относится к области импульсной и вычислительной техники и может быть использовано при построении самосинхронных вычислительных устройств, систем цифровой обработки информации. Техническим результатом является обеспечение самосинхронной реализации формирования парафазного сигнала с низким активным уровнем входа управления, гарантирующей работоспособность устройства при любых задержках составляющих его элементов. Устройство содержит инвертор, элемент И-ИЛИ-НЕ, два элемента И-НЕ, выходы которых формируют парафазный информационный сигнал. 3 ил.

Рисунки к патенту РФ 2475952

Формирователь парафазного сигнала с низким активным уровнем входа управления относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных комбинационных, триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации.

Известна многоразрядная схема преобразования унарного информационного сигнала в парафазный [1] Автоматное управление асинхронными процессами в ЭВМ и дискретных системах. Под ред. В.И.Варшавского. М.: Наука, 1986. — 400 с.(рис.11.19), содержащая элементы И-ИЛИ-НЕ, И-НЕ, инверторы и гистерезисный триггер.

Недостаток известного устройства — большая сложность схемы и связанное с этим низкое быстродействие.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является самосинхронный однотактный D-триггер с низким активным уровнем сигнала управления [2] Патент RU № 2362267. Опублик. 20.07 2009 г. Бюл. № 20. МПК H03K 3/00 (фиг.1), содержащий инвертор элемент И-ИЛИ-НЕ, бистабильную ячейку на элементах И-ИЛИ-НЕ и индикаторный элемент И-ИЛИ-НЕ.

Недостаток прототипа — формирование бифазного кода на информационном выходе, являющемся выходом бистабильной ячейки, что не позволяет использовать прототип в качестве приемника унарного информационного сигнала на входе комбинационной самосинхронной схемы.

Целью настоящего изобретения является обеспечение самосинхронной реализации формирователя парафазного сигнала с низким активным уровнем входа управления, гарантирующей работоспособность формирователя при любых задержках составляющих его элементов.

Поставленная цель достигается за счет того, что в формирователе, содержащем инвертор, элемент И-ИЛИ-НЕ, информационный унарный вход, подключенный к входу инвертора, управляющий вход, подключенный к входу второй группы входов И элемента И-ИЛИ-НЕ, и две составляющие информационного выхода, вход инвертора соединен со вторым входом первой группы входов И элемента И-ИЛИ-НЕ, выход инвертора подключен к первому входу первой группы входов И элемента И-ИЛИ-НЕ, введены два элемента И-НЕ, первые входы первого и второго элементов И-НЕ соединены с выходом и входом инвертора соответственно, вторые входы первого и второго элементов И-НЕ подключены к выходу элемента И-ИЛИ-НЕ, а выходы первого и второго элементов И-НЕ формируют парафазный сигнал и подключены к первой и второй составляющим информационного выхода формирователя соответственно.

Предлагаемое устройство удовлетворяет критерию «существенные отличия». Использование элемента И-ИЛИ-НЕ и инвертора в качестве входного блока при реализации самосинхронного однотактного D-триггера с унарным информационным входом известно. Однако использование их в данном случае позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

Понятие «парафазный», используемое в тексте данной заявки, определяется следующим образом. Парафазным считается сигнал, представленный двумя составляющими — парой переменных {X, ХВ}, которые в активной фазе имеют взаимоинверсные значения: {Х=0, ХВ=1} или {Х=1, ХВ=0}. Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться двумя способами.

Первый способ предполагает использование парафазного сигнала со спейсером: когда переходу в следующее рабочее состояние обязательно предшествует переход в третье статическое состояние-спейсерное (нерабочее состояние или состояние гашения). Если используется состояние {1,1}, то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние {0,0}, то парафазный сигнал с нулевьм спейсером. Спейсерное состояние — статическое состояние, установка которого в самосинхронной схемотехнике должна фиксироваться индикатором окончания переходного процесса, в данном случае — окончания установки спейсерного состояния.

Второй способ предполагает использование парафазного сигнала без спейсера. При этом переход из одного рабочего статического состояния в другое осуществляется через динамическое (кратковременное) состояние: {1,1} или {0,0}, называемое транзитным состоянием.

В материалах данной заявки речь идет о формировании на выходе преобразователя парафазного сигнала с единичным спейсером, в дальнейшем — просто парафазного сигнала.

Унарный сигнал — обычный одиночный информационный сигнал, имеющий два возможных значения: 0 или 1. Вход управления переключением в состояние «О» отражает факт появления на информационном унарном входе нового значения, которое может и совпадать с предшествующим значением.

На фиг.1 изображена схема формирователя парафазного сигнала с низким активным уровнем входа управления.

Схема формирователя содержит инвертор 1, элемент И-ИЛИ-НЕ 2, элементы И-НЕ 3-4, информационный унарный вход 5, вход управления 6, первую 7 и вторую 8 составляющие парафазного выхода, информационный унарный вход 5 подключен к входу инвертора 1, второму входу первой группы входов И элемента И-ИЛИ-НЕ 2 и первому входу второго элемента И-НЕ 4, выход инвертора 1 соединен с первым входом первого элемента И-НЕ 3 и первым входом первой группы входов И элемента И-ИЛИ-НЕ 2, вход управления 6 соединен с входом второй группы входов И элемента И-ИЛИ-НЕ 2, выход которого подключен ко вторым входам первого 3 и второго 4 элементов И-НЕ, выходы первого 3 и второго 4 элементов И-НЕ подключены к первой 7 и второй 8 составляющим парафазного выхода формирователя соответственно.

Схема работает следующим образом. В исходном состоянии при неактивном состоянии входа управления 6 (высокий логический уровень) выход элемента 2 находится в состоянии логического «0» и обе составляющие парафазного выхода 7 и 8 находятся в состоянии «1» (в спейсере). Появление на информационном унарном входе 5 нового значения подтверждается подачей на управляющий вход 6 активного низкого уровня. Выход элемента 2 переключается в состояние логической «1», разрешая тем самым трансляцию значения унарного информационного входа и его инверсии на выходы элементов 3 и 4. Если при этом на информационном входе 5 высокий уровень, элемент 3 останется в состоянии «1», а элемент 4 переключится в состояние «0». Если на информационном входе 5 низкий уровень, элемент 3 переключится в состояние «0», а элемент 4 останется в состоянии «1».

На первый взгляд использование элемента И-ИЛИ-НЕ является избыточным, так как, с точки зрения булевой алгебры, выполняемая им функция упрощается до инверсии входа управления из-за того, что входами первой группы входов И являются взаимоинверсные сигналы. Однако именно такое использование элемента И-ИЛИ-НЕ обеспечивает самосинхронность предлагаемой схемы формирователя.

Особенности данной схемы по сравнению с прототипом следующие.

Информационный выход является парафазным с единичным спейсером, что позволяет использовать формирователь в качестве элемента интерфейса между синхронной схемой и самосинхронной комбинационной схемой. Парафазный выход формирователя своим состоянием индицирует окончание переходных процессов в схеме формирователя в любой фазе его работы, обеспечивая его самосинхронность.

Таким образом, предлагаемое устройство обеспечивает самосинхронную работу формирователя парафазного сигнала с низким активным уровнем входа управления. Цель изобретения достигнута.

Источники информации

[1] Автоматное управление асинхронными процессами в ЭВМ и дискретных системах. Под ред. В.И.Варшавского. М.: Наука, 1986. (рис.11.19)

[2] Патент № 2362267 RU. Опубликовано: 20.07 2009 г. Бюл. № 20. МПК H03K 3/00 (фиг.1)

Приведенное выше описание работы формирователя парафазного сигнала с низким активным уровнем входа управления самодостаточно. Однако текстовая форма описания не очень компактна и наглядна. Как правило, в таких случаях текстовая форма описания дополняется таблицами истинности работы составных элементов или устройства в целом, логическими уравнениями, временными диаграммами, блок-схемами алгоритма их работы.

В данном случае мы имеем дело с самосинхронным элементом, т.е. элементом, правильная работа которого не зависит от задержек его составных элементов. Задержка каждого элемента, в том числе и инвертора, может быть сколь угодно большой, но конечной величиной. Указанная особенность самосинхронных схем и является основой их многочисленных преимуществ перед традиционными синхронными схемами, главными из которых являются:

— устойчивая работа при любых задержках и любых возможных условиях эксплуатации;

— безопасная работа: прекращение всех переключений в момент появления неисправностей элементов (константных).

Указанные преимущества могут иметь место только тогда, когда схема действительно является самосинхронной, т.е. ее поведение не зависит от задержек ее компонентов. Для подтверждения этого свойства указанных выше средств описания (схема, временная диаграмма и т.д.) недостаточно. Поскольку в основе работы самосинхронных схем лежит событийная модель, то адекватным средством описания их функционирования являются сигнальные графы (СГ). СГ одновременно являются формальным средством спецификации разрабатываемого устройства, наглядным средством описания функционирования и визуальным средством подтверждения самосинхронного характера устройства.

Самосинхронность схемы проверяется путем ее замыкания — добавления элементов, обеспечивающих надлежащее изменение входов анализируемой схемы при изменении ее выходов. На фиг.2 показана схема проверки формирователя парафазного сигнала на самосинхронность. Помимо самого формирователя она включает одноразрядный самосинхронный счетчик 9, формирующий входы формирователя, и индикатор окончания переходных процессов в формирователе 10 при его переключении из одной фазы работы в другую (элемент И). Информационный выход счетчика задает унарный информационный вход формирователя, индикаторный выход счетчика задает вход управления формирователя. Это позволяет перебрать все возможные сочетания входов формирователя.

На фиг.3 приведен сигнальный граф работы схемы фиг.2. Замыкание формирователя обеспечивает непрерывное чередование фаз его работы: сразу же после окончания переключения в рабочую фазу (низкий уровень сигнала CTI) схема замыкания инициирует переключение формирователя в фазу гашения (переход в спейсер парафазного выхода O7, O8). Символ ‘+’ перед именем переменной используется для обозначения установки высокого уровня сигнала, а знак ‘-‘- низкого уровня. Имена переменных соответствуют нумерации элементов и выводов в описании заявки. Буквы «I» и «О» в имени обозначают входы и выходы формирователя. Имена CY, CYB, RR, СТО — внутренние сигналы счетчика 9.

Начальное состояние схемы: СTI=15=1, 16=0, O2=07=1, O8=0. Оно неустойчивое, так как элемент И 10 стремится переключиться в состояние «0». С этого переключения и начинается работа схемы, иллюстрируемая графом на фиг.3. Как видно из фиг.3, это приводит к установке высокого уровня на управляющем входе (+16,1), что вызывает изменения состояния элемента И-ИЛИ-НЕ 2 (выход O2). Когда переходной процесс в нем закончится (на его выходе сформируется низкий уровень), инициируется изменение состояния элемента И-НЕ 4 (выход O8), он переходит в состояние «1» и на парафазном выходе {7, 8} формируется спейсер. Напомним еще раз, что на время переходного процесса любого элемента не накладывается ограничений.

Единичный спейсер {1, 1} на входах элемента 10 приводит к переключению его выхода в состояние «I». Это вызывает переключение счетчика, изменяется информационный унарный вход 15 (15=0), что инициирует параллельное переключение двух цепочек элементов в счетчике и формирователе (разветвление на графе). Дальнейшее функционирование формирователя происходит в соответствии с фиг.3. Зацикливание графа отражает поведение самосинхронного формирователя парафазного сигнала: при надлежащем замыкании его переключения продолжаются бесконечно, при этом он проходит по одной и той же последовательности своих состояний.

Из фиг.3 видно, что индикаторный сигнал CTI — выход элемента 10, — изменяется только тогда, когда переходные процессы во всех элементах самосинхронного формирователя уже завершены. Это является визуальным подтверждением самосинхронного характера рассматриваемого формирователя.

Таким образом, приведенный сигнальный граф подтверждает самосинхронность предлагаемого решения формирователя.

ФОРМУЛА ИЗОБРЕТЕНИЯ

Формирователь парафазного сигнала с низким активным уровнем входа управления, содержащий инвертор, элемент И-ИЛИ-НЕ, информационный унарный вход, подключенный к входу инвертора, управляющий вход, подключенный к входу второй группы входов И элемента И-ИЛИ-НЕ, и две составляющие информационного выхода, вход инвертора соединен со вторым входом первой группы входов И элемента И-ИЛИ-НЕ, выход инвертора подключен к первому входу первой группы входов И элемента И-ИЛИ-НЕ, отличающийся тем, что в схему введены два элемента И-НЕ, первые входы первого и второго элементов И-НЕ соединены с выходом и входом инвертора соответственно, вторые входы первого и второго элементов И-НЕ подключены к выходу элемента И-ИЛИ-НЕ, а выходы первого и второго элементов И-НЕ формируют парафазный сигнал и подключены к первой и второй составляющим информационного выхода формирователя соответственно.

парафазный — это… Что такое парафазный?

парафазный сигнал — — [Л.Г.Суменко. Англо русский словарь по информационным технологиям. М.: ГП ЦНИИС, 2003.] Тематики информационные технологии в целом EN push pull pulse output … Справочник технического переводчика

парафазный усилитель — parafazinis stiprintuvas statusas T sritis radioelektronika atitikmenys: angl. paraphase amplifier vok. Paraphasenverstärker, m rus. парафазный усилитель, m pranc. amplificateur déphaseur, m … Radioelektronikos terminų žodynas

Инверсный каскад — фазоинверсный, или парафазный, каскад, усилительный каскад на транзисторе или электронной лампе, на выходе которого получаются 2 равных по амплитуде и противоположных по фазе (сдвинутых на 180°) электрических напряжения. И. к. применяют… … Большая советская энциклопедия

Бит — Эта статья о единице измерения информации; другие значения: бит (значения). Наименование Международное по МЭК обозначение (англ.)[1] Русское По ГОСТ обозначение[2] Значение бит bit бит 1 октет, байт o, В Б (байт) 1 Б = 8 бит Бит (англ … Википедия

БЭСМ-6 — (Большая Электронно Счётная Машина) советская электронная вычислительная машина серии БЭСМ, первая суперЭВМ на элементной базе второго поколения полупроводниковых транзисторах … Википедия

Электронный усилитель — Электронный усилитель усилитель электрических сигналов, в усилительных элементах которого используется явление электрической проводимости в газах, вакууме и полупроводниках. Электронный усилитель может представлять собой как самостоятельное … Википедия

Д-68 — БЭСМ 6 советская электронная вычислительная машина, первая супер ЭВМ второго поколения на полупроводниковых транзисторах. Разработка БЭСМ 6 завершена в конце 1966 года. Главный конструктор Сергей Алексеевич Лебедев, заместители главного… … Википедия

Диспетчер-68 — БЭСМ 6 советская электронная вычислительная машина, первая супер ЭВМ второго поколения на полупроводниковых транзисторах. Разработка БЭСМ 6 завершена в конце 1966 года. Главный конструктор Сергей Алексеевич Лебедев, заместители главного… … Википедия

Усилитель (электроника) — Электронный усилитель усилитель электрических сигналов, в усилительных элементах которого используется явление электрической проводимости в газах, вакууме и полупроводниках. Электронный усилитель может представлять собой как самостоятельное… … Википедия

Триггер — У этого термина существуют и другие значения, см. Триггер (значения). Триггер (триггерная система) класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под… … Википедия

Paraphasenverstärker — parafazinis stiprintuvas statusas T sritis radioelektronika atitikmenys: angl. paraphase amplifier vok. Paraphasenverstärker, m rus. парафазный усилитель, m pranc. amplificateur déphaseur, m … Radioelektronikos terminų žodynas

Преобразователь унарного сигнала в парафазный сигнал с нулевым спейсером

Изобретение относится к импульсной и вычислительно технике. Технический результат — обеспечение самосинхронной реализации преобразователя унарного информационного сигнала в парафазный сигнал с нулевым спейсером. В схему, содержащую инвертор, элемент ИЛИ-И-НЕ, элемент ИЛИ-НЕ, информационный унарный вход, вход управления, парафазный информационный выход, введены второй инвертор, второй элемент ИЛИ-И-НЕ, выход инверсии входа управления и индикаторный выход, разрешающие изменение унарного входа сразу по окончании формирования рабочего состояния на парафазном выходе. 1 ил.

Преобразователь унарного сигнала в парафазный сигнал с нулевым спейсером относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных комбинационных, тригтерных, регистровых и вычислительных устройств, систем цифровой обработки информации.

Известен самосинхронный многоразрядный преобразователь унарного сигнала в парафазный сигнал [1, рис. 11.19], состоящий из элементов И-ИЛИ-НЕ, И-НЕ ИЛИ-НЕ и инверторов.

Недостаток известного устройства — невозможность его использования в самосинхронном режиме работы и единичный спейсер парафазного выхода.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является формирователь парафазного сигнала с высоким активным уровнем сигнала управления [2], содержащий элемент ИЛИ-И-НЕ, два элемента ИЛИ-НЕ и инвертор.

Недостаток прототипа — унарный сигнал может изменяться только при пассивном уровне на входе управления.

Задача, решаемая в изобретении, заключается в обеспечении самосинхронной работы преобразователя унарного сигнала в парафазный с нулевым спейсером, разрешающего изменение унарного входа сразу по окончании формирования рабочего состояния на парафазном выходе.

Это достигается тем, что в преобразователь унарного сигнала в парафазный с нулевым спейсером, содержащий инвертор, элемент ИЛИ-И-НЕ, элемент ИЛИ-НЕ, унарный вход, вход управления, парафазный выход с нулевым спейсером, причем выход инвертора соединен с первым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ и первым входом элемента ИЛИ-НЕ, второй вход которого подключен к выходу элемента ИЛИ-И-НЕ, второй вход первой группы входов ИЛИ элемента ИЛИ-И-НЕ подключен к унарному входу, первый вход второй группы входов ИЛИ элемента ИЛИ-И-НЕ соединен с входом управления, согласно изобретению введены второй инвертор, второй элемент ИЛИ-И-НЕ, выход инверсии входа управления и индикаторный выход, третий вход первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ подключен к первому входу второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ, входу второго инвертора и входу управления, вторые входы вторых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ соединены друг с другом, выходом элемента ИЛИ-НЕ и индикаторным выходом преобразователя, третий вход второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ подключен к выходу первого инвертора, прямой составляющей парафазного выхода и первым входам первой и второй групп входов ИЛИ второго элемента ИЛИ-И-НЕ, выход первого элемента ИЛИ-И-НЕ соединен с инверсной составляющей парафазного выхода, вход первого инвертора соединен с выходом второго элемента ИЛИ-И-НЕ, второй вход первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ соединен с унарным входом, вход третьей группы входов ИЛИ второго элемента ИЛИ-И-НЕ соединен с выходом второго инвертора и выходом инверсии входа управления.

Предлагаемое устройство удовлетворяет критерию «существенные отличия». Действительно, элементы ИЛИ-НЕ, ИЛИ-И-НЕ и инвертор используются и в прототипе. Но способ их подключения к входам и выходам преобразователя запрещает изменение угарного входа при активном уровне на входе управления. Добавление в схему второго инвертора и второго элемента ИЛИ-И-НЕ и реализация описанных связей между ними и другими элементами схемы преобразователя позволили достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

Понятие «парафазный», используемое в тексте данной заявки, определяется следующим образом. Парафазным считается сигнал, представленный двумя составляющими — парой переменных {X, ХВ}, которые в активной фазе имеют взаимоинверсные значения: {Х=0, ХВ=1} или {Х=1, ХВ=0}. Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться двумя способами.

Первый способ предполагает использование парафазного сигнала со спейсером: когда переходу в следующее рабочее состояние обязательно предшествует переход в третье статическое состояние — спейсерное (нерабочее состояние или состояние гашения). Если используется состояние {1, 1}, то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние {0, 0} — парафазный сигнал с нулевым спейсером. Спейсерное состояние — статическое состояние, установка которого в самосинхронной схемотехнике должна фиксироваться индикатором окончания переходного процесса, в данном случае — окончания установки спейсерного состояния.

Второй способ предполагает использование парафазного сигнала без спейсера. При этом переход из одного рабочего статического состояния в другое осуществляется через динамическое (кратковременное) состояние: {1, 1} или {0, 0}, — называемое транзитным состоянием.

В материалах данной заявки речь идет о формировании на выходе преобразователя парафазного сигнала с нулевым спейсером, в дальнейшем — просто парафазного сигнала.

Унарный сигнал — обычный одиночный информационный сигнал, имеющий два возможных значения: 0 или 1. Вход управления переключением в состояние «1» отражает факт появления на информационном унарном входе нового значения, которое может и совпадать с предшествующим значением.

На фиг. 1 представлена схема преобразователя унарного сигнала в парафазный с нулевым спейсером. Схема содержит два инвертора 1-2, два элемента ИЛИ-И-НЕ 3-4, элемент ИЛИ-НЕ 5, унарный вход 6, вход управления 7, парафазный информационный выход 8-9, индикаторный выход 10, выход инверсии входа управления 11, вход инвертора 1 подключен к входу управления 7 и к первым входам первой и второй групп входов ИЛИ элемента ИЛИ-И-НЕ 3, выход инвертора 1 соединен с входом третьей группы входов ИЛИ элемента ИЛИ-И-НЕ 4 и выходом инверсии входа управления 11, вторые входы первых групп входов ИЛИ элементов ИЛИ-И-НЕ 3 и 4 подключены к унарному входу 6, третьи входы первой и второй групп входов ИЛИ элемента ИЛИ-И-НЕ 3 соединены с выходом инвертора 2, первыми входами первой и второй групп входов ИЛИ элемента ИЛИ-И-НЕ 4, прямой составляющей парафазного информационного выхода 9 и первым входом элемента ИЛИ-НЕ 5, второй вход которого подключен к выходу элемента ИЛИ-И-НЕ 3 и инверсной составляющей парафазного информационного выхода 8, вход инвертора 2 соединен с выходом элемента ИЛИ-И-НЕ 4, второй вход второй группы входов ИЛИ которого подключен ко второму входу второй группы входов ИЛИ элемента ИЛИ-И-НЕ 3, выходу элемента ИЛИ-НЕ 5 и индикаторному выходу 10.

Схема работает следующим образом. В спейсерной фазе на вход управления подается уровень логической 1, в результате обе составляющие парафазного выхода 8 и 9 принимают значение логического 0 и на индикаторном выходе 10 появляется логическая 1 как признак спейсера. При этом значение сигнала на унарном входе 6 никак не влияет на значения выходов преобразователя. В рабочей фазе на вход управления 7 подается значение логического 0, в результате чего парафазный выход 8, 9 переключится в рабочее состояние, соответствующее значению унарного входа 6. По окончании переключения парафазного выхода 8, 9 в рабочую фазу индикаторный выход 10 перейдет в логический 0, отражая окончание всех переходных процессов в преобразователе.

Особенности данной схемы по сравнению с прототипом следующие.

Вместо второго элемента ИЛИ-НЕ введены второй элемент ИЛИ-И-НЕ и второй инвертор. Это обеспечивает самосинхронность переключения преобразователя из рабочей фазы в спейсер и обратно и разрешает унарному сигналу переключаться в следующее рабочее значение сразу по окончании записи в преобразователь его текущего значения, т.е. еще в рабочей фазе сигнала управления.

Таким образом, предлагаемое устройство обеспечивает самосинхронную работу преобразователя унарного сигнала в парафазный сигнал с нулевым спейсером. Цель изобретения достигнута.

Источники информации

[1] Варшавский В.И., Кишиневский М.А., Мараховский В.Б. и др. Автоматное управление асинхронными процессами в ЭВМ и дискретных системах / Под ред. В.И.Варшавского. — М.: Наука. Гл. ред. физ.-мат.лит., 1986. — 400 с.

[2] Пат. 2469470 Российская Федерация, МПК Н03K 3/00. Формирователь парафазного сигнала с высоким активным уровнем входа управления / Степченков Ю.А., Дьяченко Ю.Г., Шнейдер А.Ю., Прокофьев А.А., Хилько Д.В.; заявитель и патентообладатель ИПИ РАН. — №2011129014/08; заявл. 13.07.11; опубл. 20.02.13, Бюл. №34. — 6 с.

Преобразователь унарного сигнала в парафазный сигнал с нулевым спейсером, содержащий инвертор, элемент ИЛИ-И-НЕ, элемент ИЛИ-НЕ, унарный вход, вход управления, парафазный выход с нулевым спейсером, причем выход инвертора соединен с первым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ и первым входом элемента ИЛИ-НЕ, второй вход которого подключен к выходу элемента ИЛИ-И-НЕ, второй вход первой группы входов ИЛИ элемента ИЛИ-И-НЕ подключен к унарному входу, первый вход второй группы входов ИЛИ элемента ИЛИ-И-НЕ соединен с входом управления, отличающийся тем, что в схему введены второй инвертор, второй элемент ИЛИ-И-НЕ, выход инверсии входа управления и индикаторный выход, третий вход первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ подключен к первому входу второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ, входу второго инвертора и входу управления, вторые входы вторых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ соединены друг с другом, выходом элемента ИЛИ-НЕ и индикаторным выходом преобразователя, третий вход второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ подключен к выходу первого инвертора, прямой составляющей парафазного выхода и первым входам первой и второй групп входов ИЛИ второго элемента ИЛИ-И-НЕ, выход первого элемента ИЛИ-И-НЕ соединен с инверсной составляющей парафазного выхода, вход первого инвертора соединен с выходом второго элемента ИЛИ-И-НЕ, второй вход первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ соединен с унарным входом, вход третьей группы входов ИЛИ второго элемента ИЛИ-И-НЕ соединен с выходом второго инвертора и выходом инверсии входа управления.

Формирователь парафазного сигнала с низким активным уровнем входа управления

Изобретение относится к области импульсной и вычислительной техники и может быть использовано при построении самосинхронных вычислительных устройств, систем цифровой обработки информации. Техническим результатом является обеспечение самосинхронной реализации формирования парафазного сигнала с низким активным уровнем входа управления, гарантирующей работоспособность устройства при любых задержках составляющих его элементов. Устройство содержит инвертор, элемент И-ИЛИ-НЕ, два элемента И-НЕ, выходы которых формируют парафазный информационный сигнал. 3 ил.

Формирователь парафазного сигнала с низким активным уровнем входа управления относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных комбинационных, триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации.

Известна многоразрядная схема преобразования унарного информационного сигнала в парафазный [1] Автоматное управление асинхронными процессами в ЭВМ и дискретных системах. Под ред. В.И.Варшавского. М.: Наука, 1986. — 400 с.(рис.11.19), содержащая элементы И-ИЛИ-НЕ, И-НЕ, инверторы и гистерезисный триггер.

Недостаток известного устройства — большая сложность схемы и связанное с этим низкое быстродействие.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является самосинхронный однотактный D-триггер с низким активным уровнем сигнала управления [2] Патент RU №2362267. Опублик. 20.07 2009 г. Бюл. №20. МПК H03K 3/00 (фиг.1), содержащий инвертор элемент И-ИЛИ-НЕ, бистабильную ячейку на элементах И-ИЛИ-НЕ и индикаторный элемент И-ИЛИ-НЕ.

Недостаток прототипа — формирование бифазного кода на информационном выходе, являющемся выходом бистабильной ячейки, что не позволяет использовать прототип в качестве приемника унарного информационного сигнала на входе комбинационной самосинхронной схемы.

Целью настоящего изобретения является обеспечение самосинхронной реализации формирователя парафазного сигнала с низким активным уровнем входа управления, гарантирующей работоспособность формирователя при любых задержках составляющих его элементов.

Поставленная цель достигается за счет того, что в формирователе, содержащем инвертор, элемент И-ИЛИ-НЕ, информационный унарный вход, подключенный к входу инвертора, управляющий вход, подключенный к входу второй группы входов И элемента И-ИЛИ-НЕ, и две составляющие информационного выхода, вход инвертора соединен со вторым входом первой группы входов И элемента И-ИЛИ-НЕ, выход инвертора подключен к первому входу первой группы входов И элемента И-ИЛИ-НЕ, введены два элемента И-НЕ, первые входы первого и второго элементов И-НЕ соединены с выходом и входом инвертора соответственно, вторые входы первого и второго элементов И-НЕ подключены к выходу элемента И-ИЛИ-НЕ, а выходы первого и второго элементов И-НЕ формируют парафазный сигнал и подключены к первой и второй составляющим информационного выхода формирователя соответственно.

Предлагаемое устройство удовлетворяет критерию «существенные отличия». Использование элемента И-ИЛИ-НЕ и инвертора в качестве входного блока при реализации самосинхронного однотактного D-триггера с унарным информационным входом известно. Однако использование их в данном случае позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

Понятие «парафазный», используемое в тексте данной заявки, определяется следующим образом. Парафазным считается сигнал, представленный двумя составляющими — парой переменных {X, ХВ}, которые в активной фазе имеют взаимоинверсные значения: {Х=0, ХВ=1} или {Х=1, ХВ=0}. Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться двумя способами.

Первый способ предполагает использование парафазного сигнала со спейсером: когда переходу в следующее рабочее состояние обязательно предшествует переход в третье статическое состояние-спейсерное (нерабочее состояние или состояние гашения). Если используется состояние {1,1}, то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние {0,0}, то парафазный сигнал с нулевьм спейсером. Спейсерное состояние — статическое состояние, установка которого в самосинхронной схемотехнике должна фиксироваться индикатором окончания переходного процесса, в данном случае — окончания установки спейсерного состояния.

Второй способ предполагает использование парафазного сигнала без спейсера. При этом переход из одного рабочего статического состояния в другое осуществляется через динамическое (кратковременное) состояние: {1,1} или {0,0}, называемое транзитным состоянием.

В материалах данной заявки речь идет о формировании на выходе преобразователя парафазного сигнала с единичным спейсером, в дальнейшем — просто парафазного сигнала.

Унарный сигнал — обычный одиночный информационный сигнал, имеющий два возможных значения: 0 или 1. Вход управления переключением в состояние «О» отражает факт появления на информационном унарном входе нового значения, которое может и совпадать с предшествующим значением.

На фиг.1 изображена схема формирователя парафазного сигнала с низким активным уровнем входа управления.

Схема формирователя содержит инвертор 1, элемент И-ИЛИ-НЕ 2, элементы И-НЕ 3-4, информационный унарный вход 5, вход управления 6, первую 7 и вторую 8 составляющие парафазного выхода, информационный унарный вход 5 подключен к входу инвертора 1, второму входу первой группы входов И элемента И-ИЛИ-НЕ 2 и первому входу второго элемента И-НЕ 4, выход инвертора 1 соединен с первым входом первого элемента И-НЕ 3 и первым входом первой группы входов И элемента И-ИЛИ-НЕ 2, вход управления 6 соединен с входом второй группы входов И элемента И-ИЛИ-НЕ 2, выход которого подключен ко вторым входам первого 3 и второго 4 элементов И-НЕ, выходы первого 3 и второго 4 элементов И-НЕ подключены к первой 7 и второй 8 составляющим парафазного выхода формирователя соответственно.

Схема работает следующим образом. В исходном состоянии при неактивном состоянии входа управления 6 (высокий логический уровень) выход элемента 2 находится в состоянии логического «0» и обе составляющие парафазного выхода 7 и 8 находятся в состоянии «1» (в спейсере). Появление на информационном унарном входе 5 нового значения подтверждается подачей на управляющий вход 6 активного низкого уровня. Выход элемента 2 переключается в состояние логической «1», разрешая тем самым трансляцию значения унарного информационного входа и его инверсии на выходы элементов 3 и 4. Если при этом на информационном входе 5 высокий уровень, элемент 3 останется в состоянии «1», а элемент 4 переключится в состояние «0». Если на информационном входе 5 низкий уровень, элемент 3 переключится в состояние «0», а элемент 4 останется в состоянии «1».

На первый взгляд использование элемента И-ИЛИ-НЕ является избыточным, так как, с точки зрения булевой алгебры, выполняемая им функция упрощается до инверсии входа управления из-за того, что входами первой группы входов И являются взаимоинверсные сигналы. Однако именно такое использование элемента И-ИЛИ-НЕ обеспечивает самосинхронность предлагаемой схемы формирователя.

Особенности данной схемы по сравнению с прототипом следующие.

Информационный выход является парафазным с единичным спейсером, что позволяет использовать формирователь в качестве элемента интерфейса между синхронной схемой и самосинхронной комбинационной схемой. Парафазный выход формирователя своим состоянием индицирует окончание переходных процессов в схеме формирователя в любой фазе его работы, обеспечивая его самосинхронность.

Таким образом, предлагаемое устройство обеспечивает самосинхронную работу формирователя парафазного сигнала с низким активным уровнем входа управления. Цель изобретения достигнута.

Источники информации

[1] Автоматное управление асинхронными процессами в ЭВМ и дискретных системах. Под ред. В.И.Варшавского. М.: Наука, 1986. (рис.11.19)

[2] Патент №2362267 RU. Опубликовано: 20.07 2009 г. Бюл. №20. МПК H03K 3/00 (фиг.1)

Приведенное выше описание работы формирователя парафазного сигнала с низким активным уровнем входа управления самодостаточно. Однако текстовая форма описания не очень компактна и наглядна. Как правило, в таких случаях текстовая форма описания дополняется таблицами истинности работы составных элементов или устройства в целом, логическими уравнениями, временными диаграммами, блок-схемами алгоритма их работы.

В данном случае мы имеем дело с самосинхронным элементом, т.е. элементом, правильная работа которого не зависит от задержек его составных элементов. Задержка каждого элемента, в том числе и инвертора, может быть сколь угодно большой, но конечной величиной. Указанная особенность самосинхронных схем и является основой их многочисленных преимуществ перед традиционными синхронными схемами, главными из которых являются:

— устойчивая работа при любых задержках и любых возможных условиях эксплуатации;

— безопасная работа: прекращение всех переключений в момент появления неисправностей элементов (константных).

Указанные преимущества могут иметь место только тогда, когда схема действительно является самосинхронной, т.е. ее поведение не зависит от задержек ее компонентов. Для подтверждения этого свойства указанных выше средств описания (схема, временная диаграмма и т.д.) недостаточно. Поскольку в основе работы самосинхронных схем лежит событийная модель, то адекватным средством описания их функционирования являются сигнальные графы (СГ). СГ одновременно являются формальным средством спецификации разрабатываемого устройства, наглядным средством описания функционирования и визуальным средством подтверждения самосинхронного характера устройства.

Самосинхронность схемы проверяется путем ее замыкания — добавления элементов, обеспечивающих надлежащее изменение входов анализируемой схемы при изменении ее выходов. На фиг.2 показана схема проверки формирователя парафазного сигнала на самосинхронность. Помимо самого формирователя она включает одноразрядный самосинхронный счетчик 9, формирующий входы формирователя, и индикатор окончания переходных процессов в формирователе 10 при его переключении из одной фазы работы в другую (элемент И). Информационный выход счетчика задает унарный информационный вход формирователя, индикаторный выход счетчика задает вход управления формирователя. Это позволяет перебрать все возможные сочетания входов формирователя.

На фиг.3 приведен сигнальный граф работы схемы фиг.2. Замыкание формирователя обеспечивает непрерывное чередование фаз его работы: сразу же после окончания переключения в рабочую фазу (низкий уровень сигнала CTI) схема замыкания инициирует переключение формирователя в фазу гашения (переход в спейсер парафазного выхода O7, O8). Символ ‘+’ перед именем переменной используется для обозначения установки высокого уровня сигнала, а знак ‘-‘- низкого уровня. Имена переменных соответствуют нумерации элементов и выводов в описании заявки. Буквы «I» и «О» в имени обозначают входы и выходы формирователя. Имена CY, CYB, RR, СТО — внутренние сигналы счетчика 9.

Начальное состояние схемы: СTI=15=1, 16=0, O2=07=1, O8=0. Оно неустойчивое, так как элемент И 10 стремится переключиться в состояние «0». С этого переключения и начинается работа схемы, иллюстрируемая графом на фиг.3. Как видно из фиг.3, это приводит к установке высокого уровня на управляющем входе (+16,1), что вызывает изменения состояния элемента И-ИЛИ-НЕ 2 (выход O2). Когда переходной процесс в нем закончится (на его выходе сформируется низкий уровень), инициируется изменение состояния элемента И-НЕ 4 (выход O8), он переходит в состояние «1» и на парафазном выходе {7, 8} формируется спейсер. Напомним еще раз, что на время переходного процесса любого элемента не накладывается ограничений.

Единичный спейсер {1, 1} на входах элемента 10 приводит к переключению его выхода в состояние «I». Это вызывает переключение счетчика, изменяется информационный унарный вход 15 (15=0), что инициирует параллельное переключение двух цепочек элементов в счетчике и формирователе (разветвление на графе). Дальнейшее функционирование формирователя происходит в соответствии с фиг.3. Зацикливание графа отражает поведение самосинхронного формирователя парафазного сигнала: при надлежащем замыкании его переключения продолжаются бесконечно, при этом он проходит по одной и той же последовательности своих состояний.

Из фиг.3 видно, что индикаторный сигнал CTI — выход элемента 10, — изменяется только тогда, когда переходные процессы во всех элементах самосинхронного формирователя уже завершены. Это является визуальным подтверждением самосинхронного характера рассматриваемого формирователя.

Таким образом, приведенный сигнальный граф подтверждает самосинхронность предлагаемого решения формирователя.

Формирователь парафазного сигнала с низким активным уровнем входа управления, содержащий инвертор, элемент И-ИЛИ-НЕ, информационный унарный вход, подключенный к входу инвертора, управляющий вход, подключенный к входу второй группы входов И элемента И-ИЛИ-НЕ, и две составляющие информационного выхода, вход инвертора соединен со вторым входом первой группы входов И элемента И-ИЛИ-НЕ, выход инвертора подключен к первому входу первой группы входов И элемента И-ИЛИ-НЕ, отличающийся тем, что в схему введены два элемента И-НЕ, первые входы первого и второго элементов И-НЕ соединены с выходом и входом инвертора соответственно, вторые входы первого и второго элементов И-НЕ подключены к выходу элемента И-ИЛИ-НЕ, а выходы первого и второго элементов И-НЕ формируют парафазный сигнал и подключены к первой и второй составляющим информационного выхода формирователя соответственно.