Мультиплексоры и демультиплексоры 2

Цель работы: Знакомство с принципом работы мультиплексора и демультиплексора. Получение навыков работы по определению временных диаграмм и составлению таблиц соответствия.

Описание работы стенда

Лицевая панель стенда с помощью пунктирной линии разделена на четыре части, каждая часть подписана: MS1, MS2 — мультиплексоры, DMS1, DMS2 — демультиплексоры. Все переключатели в правом положении подают на входы микросхем логическую единицу, в левом — логический ноль. Все переключатели имеют обозначение: D — информационные входы, Х — входы адреса, С — разрешающие входы. Выходы микросхем обозначены буквой Y. Цифры при буквах обозначают разряд (цифра больше — разряд старше и наоборот). На выходах микросхем установлены светодиоды.

Для включения стенда необходимо переключатель “Сеть” перевести в положение “Вкл.”, при этом должен загореться зеленый светодиод “Питание”

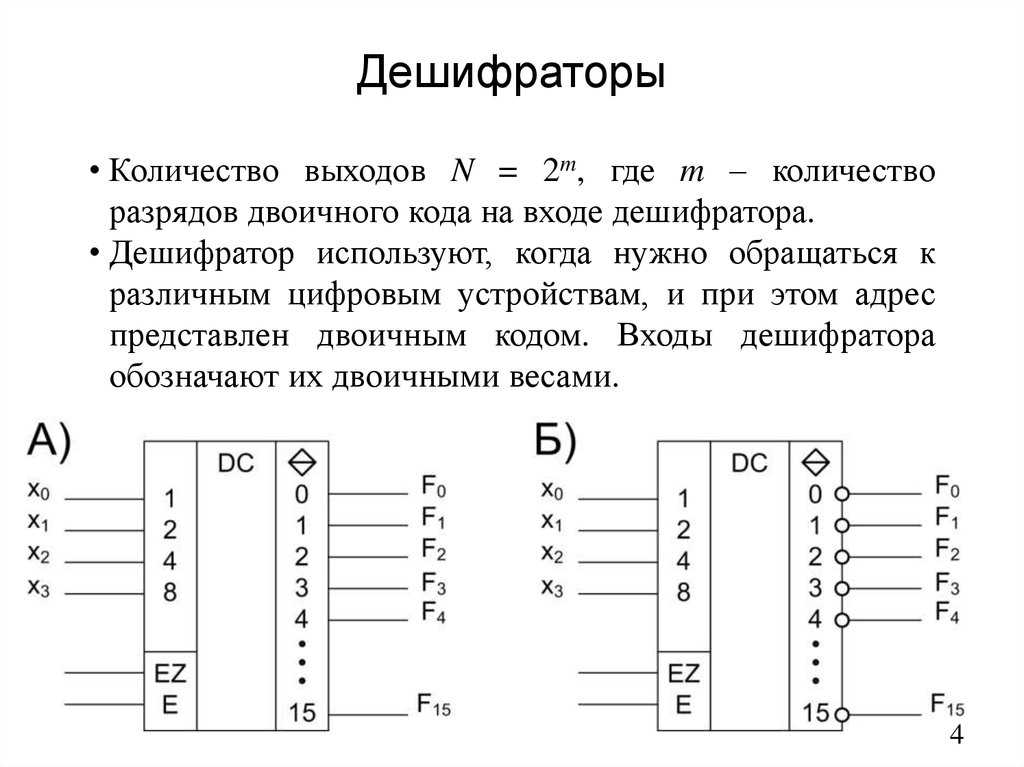

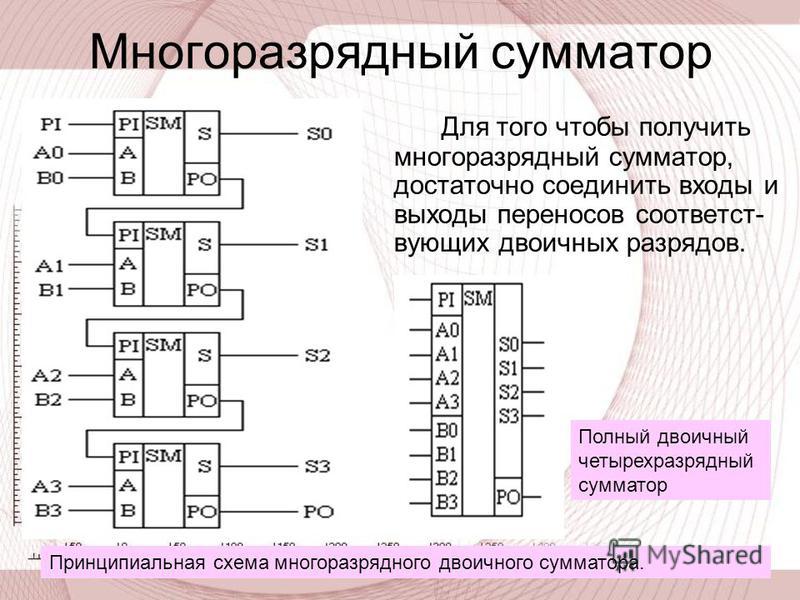

Рис.1 Четырехвходовой мультиплексор

Мультиплексор MS1 имеет четыре информационных входа D0 — D3, два адресных входа Х2, Х1 и вход разрешения С.

Например: подадим на вход D1 сигнал “1”. Чтобы он был скоммутирован на выход Y, необходимо на входах адреса Х2 Х1 набрать двоичное число 01 и подать на разрешающий вход С = 0, так как стробирующий вход С мультиплексора MS1 с инверсией и активным является низкий уровень. В подтверждение правильности набранного адреса на выходе Y загорается светодиод.

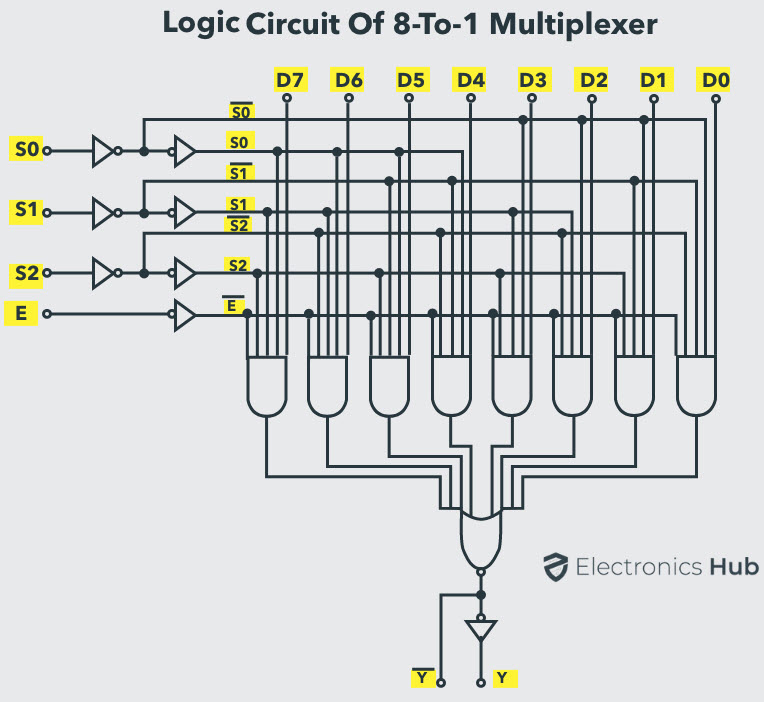

Рис.2 Восьмивходовой мультиплексор

Мультиплексор MS2 работает аналогично мультиплексору MS1, отличием является отсутствие входа разрешения С. Мультиплексор содержит восемь информационных входов D0 — D7 и три адресных входа Х1, Х2, Х3.

Например: для получения

на выходе сигнала с информационного

входа D5,

необходимо на адресных входах Х3 Х2 Х1

набрать двоичное число 1 0 1. Если операция

выполнена правильно, на выходе Y

загорится светодиод.

Если операция

выполнена правильно, на выходе Y

загорится светодиод.

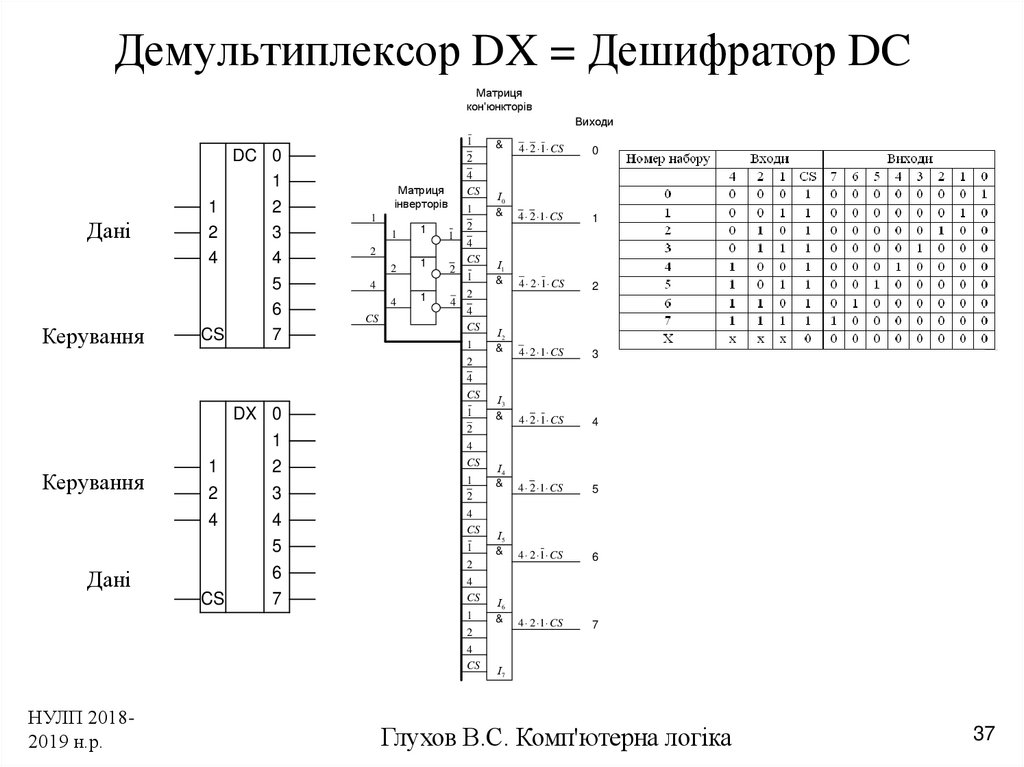

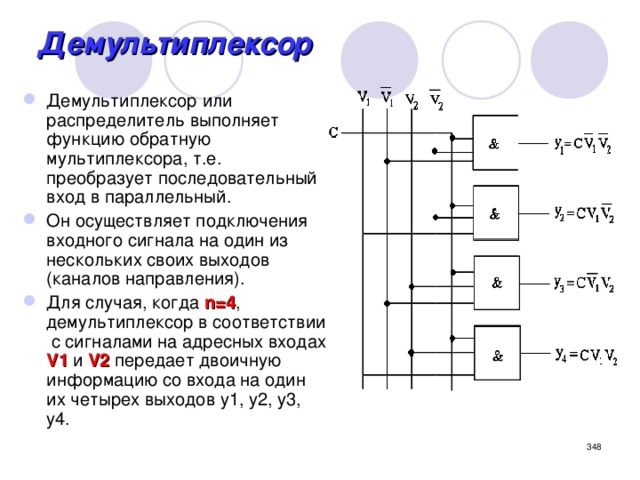

2) Рассмотрим работу демультиплексоров.

Демультиплексор DMS1 содержит один информационный вход D, два входа адреса Х2, Х1 и вход разрешения С.

Выходы Y0 — Y3 у демультиплексора с инверсией, поэтому при не работающем демультиплексоре, на всех его выходах будут гореть светодиоды, а при переключении входного сигнала на один из выходов светодиод на этом выходе погаснет.

Например: для получения сигнала на выходе Y2, необходимо на вход D подать “1”, на вход С — “0” и на входах адреса Х2 Х1 набрать двоичное число 10. Светодиод на выходе Y2 должен погаснуть.

Демультиплексор DMS2

содержит один информационный вход D,

три адресных входа Х1-Х3 и восемь выходов

Y0

-Y7.

Он работает аналогично DMS1.

Например: для того, чтобы получить

единичный сигнал на выходе Y6,

необходимо на вход D

подать “1”, а на входы адреса Х3 Х2 Х1

подать двоичное число 110 ..jpg)

Таблицы переключательных функций

Таблица 1 – четырехразрядный мультиплексор

Двоичный

код числа на входе мультиплексора D0 D | № тактового импульса | Адресный входХ1 | Адресный входХ2 | Выход У | |||

р0 | 11 | 1 | 1 | 1 2 3 4 | 0 0 1 1 | 0 1 0 1 | 0 1 1 1 |

Таблица 2 – восьмиразрядный мультиплексор

Двоичный

код числа на входе мультиплексора D0 D1 D2 D3 D4 D5 D | № тактового импульса | Адресный входХ1 | Адресный входХ2 | Адресный входХ3 | ВыходУ | ||||||||||||

11 | 00 | 00 | 11 | 11 | 11 | 11 | 1 2 3 4 5 6 7 8 | 0 0 0 0 1 1 1 1 | 0 0 1 0 0 1 1 | 0 1 0 1 0 1 0 1 | 1 0 0 1 1 1 1 0 | ||||||

Таблица 3 – четырехразрядный демультиплексор

Двоичный код числа на входе мультиплексора D0 D1 D2 D3 | № тактового импульса | Адресный входХ1 | Адресный входХ2 | Выходы У0У1У2У3 | ||||||

0 | 0 | 0 | 1 2 3 4 | 0 0 1 1 | 0 1 0 1 | |||||

Таблица 4 – восьмиразрядный демультиплексор

Двоичный код числа на входе мультиплексора D0 D1 D2 D3 D4 D5 D6 D7 | № тактового импульса | Адресный входХ1 | Адресный входХ2 | Адресный входХ3 | Выходы У0У1У2У3У4 У5У6У7 | ||||||||||||||||

00 | 11 | 00 | 00 | 1 | 0 | 0 | 0 | 1 2 3 4 5 6 7 8 | 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 | ||||||||||

Временные диаграммы

Четырехразрядный мультиплексор

Восьмиразрядный мультиплексор

Четырехразрядный демультиплексор

Восьмиразрядный демультиплексор

Вывод:

в процессе выполнения лабораторной

работы ознакомились с принципом работы

мультиплексора и демультиплексора. Получили навыки работы по определению

временных диаграмм и составлению таблиц

соответствия.

Получили навыки работы по определению

временных диаграмм и составлению таблиц

соответствия.

БАЛАКОВСКИЙ ИНСТИТУТ ТЕХНИКИ ТЕХНОЛОГИИ И УПРАВЛЕНИЯ

ИНЖЕНЕРНО – СТРОИТЕЛЬНЫЙ ФАКУЛЬТЕТ

КАФЕДРА УПРАВЛЕНИЕ И ИНФОРМАТИКА В ТЕХНИЧЕСКИХ СИСТЕМАХ

по дисциплине

Вычислительные машины, системы, сети.

Мультиплексоры и демультиплексоры.

Принял доцент каф. УИТ

»__»_____________2002г.

2002

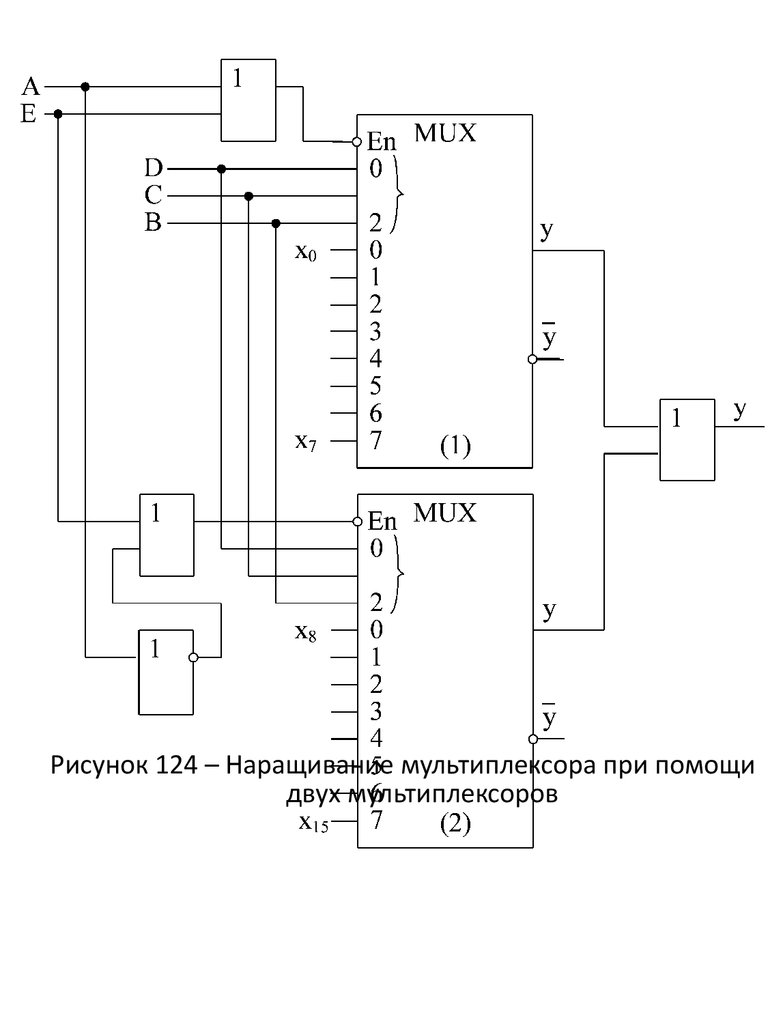

§ 2.4. Мультиплексоры и демультиплексоры

Функциональные узлы комбинационного типа | 91 |

Мультиплексоры

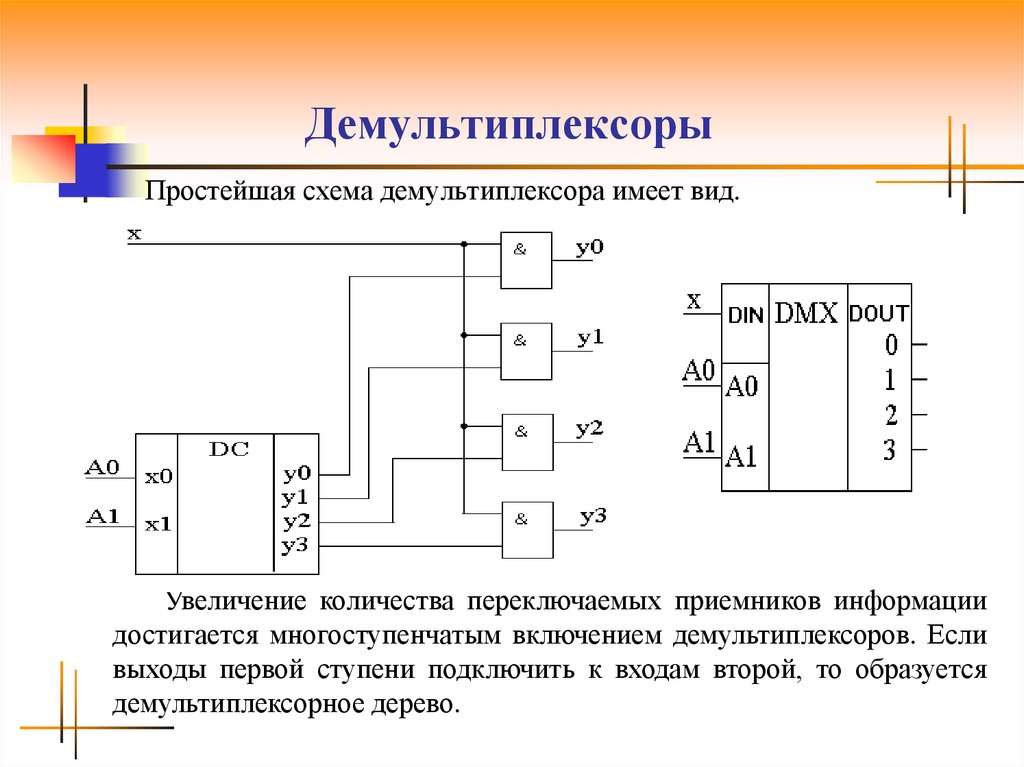

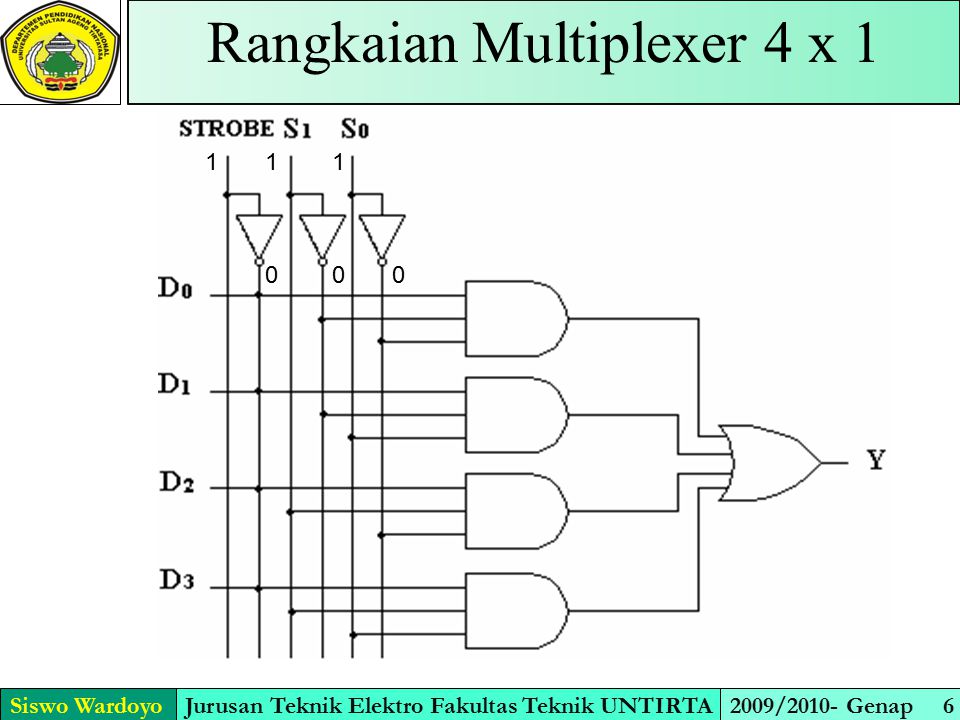

Мультиплексоры осуществляют подключение одного из входных каналов к выходному под управлением адресующего кода. Разрядности каналов могут быть различными, мультиплексоры для коммутации многоразрядных слов составляются из одноразрядных.

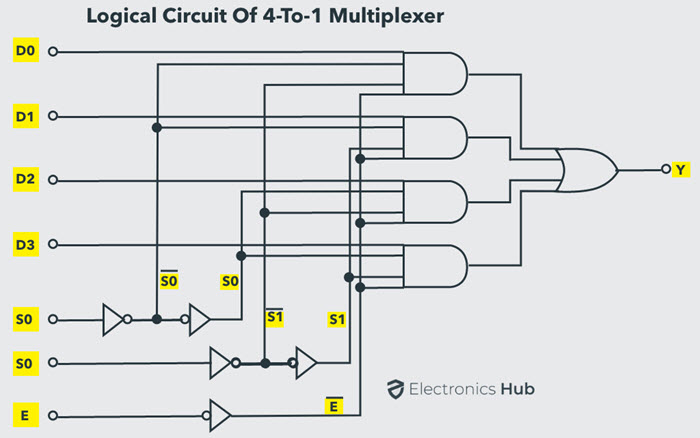

Рис. 2.10. Упрощенное представление мультиплексора многопозиционным ключом (а) и реализация мультиплексора на элементах И-НЕ (б)

Входы мультиплексора делятся на две группы: информационные и адресующие (управляющие). Работу мультиплексора можно упрощенно представить с помощью многопозиционного ключа. Для одноразрядного мультиплексора это представлено на рис. 2.10, а. Адресующий код А задает переключателю определенное положение, соединяя с выходом F один из информационных входов xi. При нулевом адресующем коде переключатель занимает верхнее положение x0, с увеличением кода на единицу переходит в соседнее положение x1 и т. д.

Работа мультиплексора описывается соотношением

F = x0аn-1an 2 …a1a0 x1an 1an 2 …a1a n 2 …a1a0 … x2n 1a n 1a n 2 …a1a0 ,

которое иногда называют мультиплексной формулой. При любом значении адресующего кода все слагаемые, кроме одного, равны нулю. Ненулевое слагаемое равно хi, где i — значение текущего адресного кода.

92 | Глава 2 |

|

|

Схемотехнически мультиплексор реализует электронную версию показанного переключателя, имея, в отличие от него, только одностороннюю передачу данных. На рис. 2.10, б показан мультиплексор с четырьмя информационными входами, двумя адресными входами и входом разрешения работы. При отсутствии разрешения работы (Е = 0) выход F становится нулевым независимо от информационных и адресных сигналов. В стандартных сериях размерность мультиплексоров не более 16×1.

На рис. 2.10, б показан мультиплексор с четырьмя информационными входами, двумя адресными входами и входом разрешения работы. При отсутствии разрешения работы (Е = 0) выход F становится нулевым независимо от информационных и адресных сигналов. В стандартных сериях размерность мультиплексоров не более 16×1.

Мультиплексоры в КМОП-схемотехнике

Схемотехника мультиплексоров на элементах КМОП имеет свои особенности. В число элементов схемы здесь наряду с обычной логикой входят специальные двунаправленные ключи, что позволяет строить экономичные структуры как мультиплексоров, так и других устройств (в частности, триггеров).

Двунаправленный ключ. Ключ (рис. 2.11) составлен из двух параллельно включенных транзисторов с взаимоинверсными напряжениями C и С на затворах. Один из транзисторов имеет n-канал, а другой — p-канал.

Упр

C

Рис. 2.11. Двунаправленный ключ

Такая схема позволяет получать замкнутое состояние ключа с приблизительно постоянным и малым сопротивлением независимо от величины переключаемого напряжения (т. е. напряжения UA ≈ UB, что имеет место в замкнутом ключе). При этом ключ может работать при идентичных уровнях переключаемого и управляющего напряжений, как это и требуется для цифровых схем.

е. напряжения UA ≈ UB, что имеет место в замкнутом ключе). При этом ключ может работать при идентичных уровнях переключаемого и управляющего напряжений, как это и требуется для цифровых схем.

Обычный однотранзисторный ключ указанного свойства не имеет. У него уровни входного (управляющего) и переключаемого напряжений не могут быть одинаковыми. Если, например, на затвор транзистора с n-каналом подать отпирающее напряжение U1 (уровень логической единицы), то переключаемое напряжение (UA ≈ UB) должно быть меньше чем U1, по меньшей мере на величину порогового напряжения, т. е. приблизительно вдвое. Иначе нарушится условие возникновения в транзисторе проводящего канала (Uзи >Uпор, где Uзи — напряжение на затворе относительно истока и Uпор — пороговое напряжение транзистора). Практически же максимальное переключаемое напряжение долж-

Функциональные узлы комбинационного типа | 93 |

но быть еще меньше, т. к. при приближении к порогу резко увеличивается сопротивление канала и ухудшаются условия передачи сигналов. Указанное обстоятельство исключает применение однотранзисторных ключей для передачи логических сигналов под управлением других логических сигналов, поскольку в этом случае не обеспечивается превышение сигналов на затворах ключей над переключаемыми сигналами.

к. при приближении к порогу резко увеличивается сопротивление канала и ухудшаются условия передачи сигналов. Указанное обстоятельство исключает применение однотранзисторных ключей для передачи логических сигналов под управлением других логических сигналов, поскольку в этом случае не обеспечивается превышение сигналов на затворах ключей над переключаемыми сигналами.

Иначе выглядит ситуация для ключей с параллельным включением двух разнотипных транзисторов. Подача на затвор транзистора с p-каналом низкого напряжение, а на затвор транзистора с n-каналом — высокого напряжения приводит ключ в замкнутое состояние. Изменение переключаемого напряжения при постоянстве напряжений на затворах изменяет напряжения «затвор-исток» и «затворсток», но при этом сопротивление одного из транзисторов растет, а другого падает, так что общее сопротивление ключа остается низким и приблизительно постоянным и, тем самым, решается проблема успешной передачи логических сигналов без потери их амплитуды. При подаче на затвор транзистора с р-каналом высокого напряжения, а на затвор транзистора с n-каналом — низкого напряжения, оба транзистора запираются и ключ размыкается.

Рис. 2.12. Структура мультиплексора, реализованного в КМОП-схемотехнике

В КМОП-схемотехнике одна и та же схема функционирует как мультиплексор или демультиплексор (при перемене местами входов и выходов). Кроме того, схема может работать не только с цифровыми, но и с аналоговыми сигналами, поскольку двунаправленный ключ на двух транзисторах обладает высоким качеством и способен передавать уровни сигналов с весьма высокой точностью. Схема мультиплексора/демультиплексора показана на рис. 2.12.

Рассмотрим режим мультиплексора «4—1». Входные сигналы D0…D3 подключены к КМОП-ключам, выходы которых соединены друг с другом в точке выхода мультиплексора. Адресующий код A1A0 дешифрируется и вырабатывает управляющий

94 | Глава 2 |

|

|

сигнал разрешения работы, т. е. замыкания, для ключа, номер которого соответствует коду A1A0. Остальные ключи остаются запертыми. Таким образом, на выход передается один из входных сигналов под управлением адресующего кода. Сигнал EN разрешает или запрещает работу мультиплексора.

Таким образом, на выход передается один из входных сигналов под управлением адресующего кода. Сигнал EN разрешает или запрещает работу мультиплексора.

Многоразрядные мультиплексоры

Для коммутации многоразрядных данных строятся мультиплексоры, представляющие собою совокупность одноразрядных схем. В этом случае мультиплексор характеризуется числом входных каналов n и их разрядностью m (рис. 2.13, а ).

|

|

| DI | MUX DO |

|

|

|

| MUX |

|

|

| 00 |

|

|

|

| 01 |

|

|

|

| 10 | 0 |

|

|

| 11 |

|

|

|

| 20 | 1 |

m |

| log2n | 21 |

|

| 30 | 2 | ||

|

|

| 31 |

|

m |

| m | 3 |

|

|

| |

|

|

| A |

n |

|

|

|

m |

|

| EN |

|

|

| |

| а |

| б |

|

|

|

Рис. 2.13. Структура (а) и условное графическое обозначение (б) многоразрядного мультиплексора

2.13. Структура (а) и условное графическое обозначение (б) многоразрядного мультиплексора

EN

A1

1

1

DI00

&

1 DO0

DI01 | & |

|

DI30

&

DO3

1

DI31 | & |

|

Рис. 2.14. Функциональная схема двухканального четырехразрядного мультиплексора

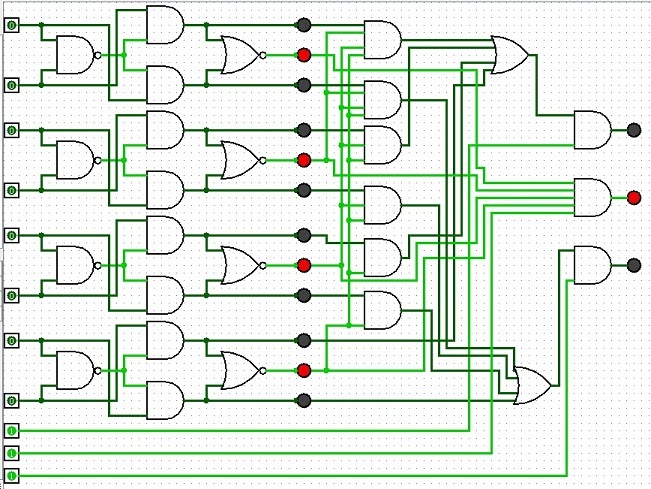

Вход— реализация многобитного мультиплексора 4 в 1 [Q]

спросил

Изменено 6 лет, 3 месяца назад

Просмотрено 17 тысяч раз

\$\начало группы\$

Перед нами стоит задача создать мультиплексор 4 к 1 с 4-битными входами. Я считаю, что полностью понимаю, как создать 1-битный мультиплексор 4 к 1, но я совершенно не понимаю, что такое «входная» и «выходная» стороны многобитного (в данном случае 4-битного) 4 к 1. мультиплексор будет выглядеть. Это мое первое знакомство со схемами, поэтому я не разбираюсь в более сложных темах.

Я считаю, что полностью понимаю, как создать 1-битный мультиплексор 4 к 1, но я совершенно не понимаю, что такое «входная» и «выходная» стороны многобитного (в данном случае 4-битного) 4 к 1. мультиплексор будет выглядеть. Это мое первое знакомство со схемами, поэтому я не разбираюсь в более сложных темах.

Мои обновленные попытки того, как будут выглядеть MUX и DMX, приведены ниже:

Схемы сделаны в Logisim.

- мультиплексор

- вход

- логисим

\$\конечная группа\$

4

\$\начало группы\$

Одним из основных свойств, которыми должна обладать ваша схема, является модульность, то есть вы создаете один модуль, а затем комбинируете этот модуль с другими модулями для создания большего модуля, что упрощает вашу конструкцию.

Теперь вернемся к вашей проблеме; На первом рисунке вы представили реализацию мультиплексора 4:1

, который может быть описан этим черным ящиком

Теперь описание поведения этого черного ящика

if(s0s1==00) выход=d0 иначе если (s0s1==01) выход=d1 иначе если (s0s1==10) выход=d2 иначе если (s0s1==11) выход=d3

Теперь для того, чтобы создать 4-битную версию этого мультиплексора, которую можно было бы описать с помощью этого черного ящика

Описание поведения этого черного ящика:

if(s0s1==00) output[3..0]=d0[3..0] //4-битный выход равен 4-битному входу иначе если (s0s1==01) выход[3..0]=d1[3..0] иначе если (s0s1==10) вывод[3..0]=d2[3..0] иначе если (s0s1==11) вывод[3..0]=d3[3..0]

Эта новая схема имеет 18 входов [ 2 для выбора и 4-битных 4 входов] и 4 выхода

Реализация новой схемы будет

Однако в вашем проекте

- Вы используете мультиплексор с 8 входами вместо встроенного мультиплексора с 6 входами ! это не тот модуль, который вы уже реализовали как мультиплексор 4:1!

- Вы подключаете биты выбора всех мультиплексоров к другому декодеру, при этом только один из битов выбора будет равен 1, а другие биты выбора равны 0 [поскольку они подключены к декодеру], однако это нарушает описание поведения нашего 4 :1 мультиплексор

Итак, чтобы исправить свой дизайн

- удалить декодер

- использовать уже реализованный мультиплексор 4:1 с правильным количеством входов

- подключите все линии выбора s0 и s1 к тем же линиям выбора вашего большего мультиплексора

\$\конечная группа\$

2

\$\начало группы\$

Мультиплексор с 4 входами имеет 4 входа данных и 2 входа адреса. Адресные входы определяют, какой вход данных соединяется с выходом. 4-битный мультиплексор с 4 входами — это просто 4 параллельных входных мультиплексора на каждые 4 входа, причем адресные входы подключены одинаково ко всем мультиплексорам. Итак, если у вас есть 4 канала данных (A0, A1, A3, A3), (B0, B1, B2, B3), (C0, C1, C2, C3) и (D0, D1, D2, D3), и адрес 0 создаст 4 выхода: A0, B0, C0 и D0.

Адресные входы определяют, какой вход данных соединяется с выходом. 4-битный мультиплексор с 4 входами — это просто 4 параллельных входных мультиплексора на каждые 4 входа, причем адресные входы подключены одинаково ко всем мультиплексорам. Итак, если у вас есть 4 канала данных (A0, A1, A3, A3), (B0, B1, B2, B3), (C0, C1, C2, C3) и (D0, D1, D2, D3), и адрес 0 создаст 4 выхода: A0, B0, C0 и D0.

При рисовании всего блока в виде блока сторона ввода (обычно показана слева). и выходная сторона. Входная сторона будет иметь 18 входов — 16 данных и 2 адреса. Выходная сторона будет иметь 4 вывода данных.

\$\конечная группа\$

4

Зарегистрируйтесь или войдите

Зарегистрироваться через Google

Зарегистрироваться через Facebook

Зарегистрируйтесь, используя электронную почту и пароль

Опубликовать как гость

Электронная почта

Обязательно, но не отображается

Опубликовать как гость

Электронная почта

Требуется, но не отображается

Нажимая «Опубликовать свой ответ», вы соглашаетесь с нашими условиями обслуживания, политикой конфиденциальности и политикой использования файлов cookie

. Цифровая логика

Цифровая логика— Как я могу объединить 4 отдельных бита в один 4-битный выход?

\$\начало группы\$

Предположим, у меня есть четыре переключателя 0-3. Я хочу, чтобы каждый переключатель представлял бит в четырехбитном длинном числе, причем переключатель 0 был первым битом, а переключатель 3 — последним. Конечная цель состоит в том, чтобы иметь возможность представлять 0-15 в шестнадцатеричном формате с помощью 4 переключателей с одним выходом. Как я могу объединить входы от переключателей в один 4-битный выход? Консультируясь с Google, кажется, что мультиплексор может достичь этого? Я не очень хорошо знаком с мультиплексором или цифровой логикой в целом, поэтому помощь очень ценится.

- цифровая логика

- переключатели

- логические элементы

- двоичный код

- шестнадцатеричный

\$\конечная группа\$

6

\$\начало группы\$

Вам не нужна дополнительная логика.

Четыре 1-битных провода можно рассматривать как один 4-битный сигнал.

Просто убедитесь, что вы правильно поняли порядок, какой бит является наименее значащим и так далее.

\$\конечная группа\$

3

\$\начало группы\$

Аппаратно это должен быть сдвиговый регистр (SR) с параллельным последовательным выходом (PISO) или цифровой мультиплексор 4:1.

4 бита довольно неэффективны для PISO, поскольку они обычно являются 8-битными устройствами, но позвольте мне показать вам, как это делается.

Во-первых, вам нужен автомат с 5 состояниями и 4 тактами, а 5-е состояние представляет собой короткий импульс для сброса счетчика с задержкой RC, усиленной дополнительным неинвертирующим затвором для создания импульса полной амплитуды (но не обязательно ) Необходимо только загрузить LD входных данных переключателя (LD) в PISO, чтобы быть готовым к следующему тактовому импульсу.

.0]=d0[3..0] //4-битный выход равен 4-битному входу

иначе если (s0s1==01)

выход[3..0]=d1[3..0]

иначе если (s0s1==10)

вывод[3..0]=d2[3..0]

иначе если (s0s1==11)

вывод[3..0]=d3[3..0]

.0]=d0[3..0] //4-битный выход равен 4-битному входу

иначе если (s0s1==01)

выход[3..0]=d1[3..0]

иначе если (s0s1==10)

вывод[3..0]=d2[3..0]

иначе если (s0s1==11)

вывод[3..0]=d3[3..0]