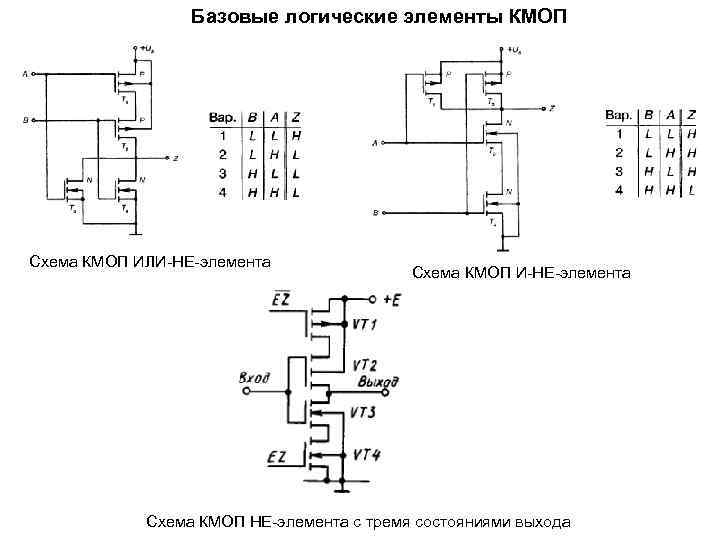

Инверторы кмоп с тремя выходными состояниями

Такие инверторы имеют дополнительные ключевые транзисторы, управление которыми осуществляется по независимой цепи ЕО. Если оба этих ключа открыты, инвертор

а | ЕО | F |

0 1 0 1 | 0 0 1 1 | Z Z 1 0 |

действует подобно обычному. Когда

ключи закрыты, питание прекращается и

выходной вывод приобретает очень большое

сопротивление по отношению к обеим

шинам питания (пример К561 ЛН1). Если к

выходу подсоединить конденсатор, то

при третьем состоянии разряд конденсатора

будет продолжительным вследствие

высоких сопротивлений входа и выхода

транзисторов.

Двунаправленный ключ.

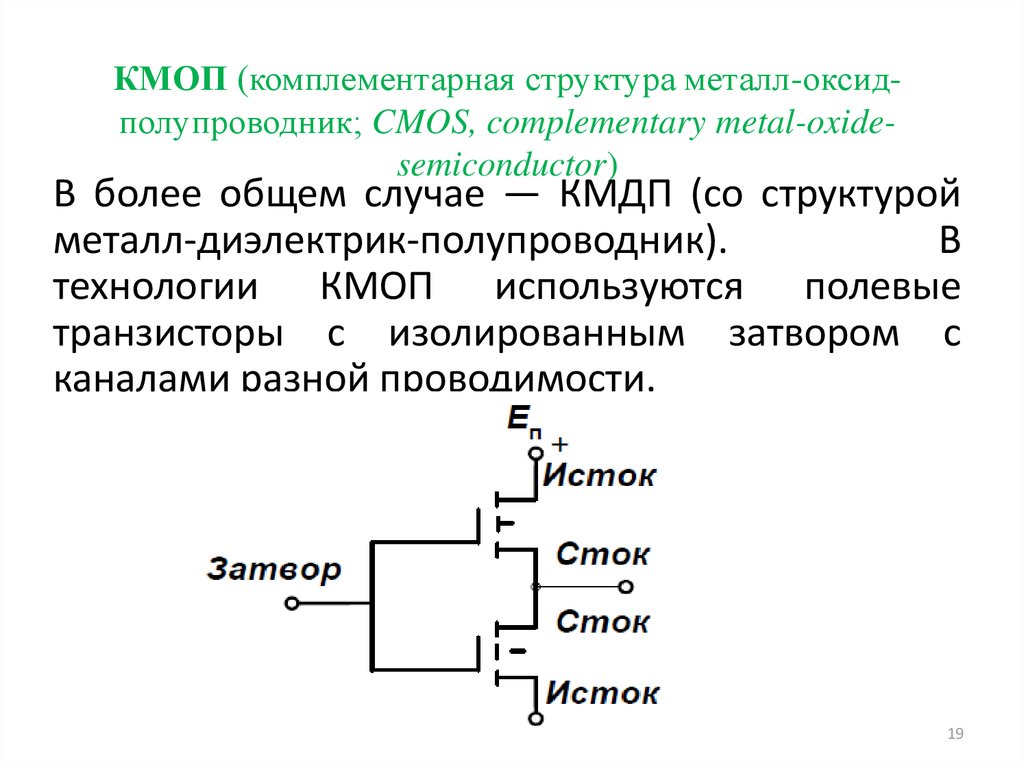

Эта специфический узел, состоящий из КМОП – транзисторов и не имеет функциональных аналогов среди микросхем других видов логики.

Ключ состоит из двух МОП транзисторов с каналами разных типов проводимости. Истоки и стоки обоих приборов соединены между собой и выведены наружу. Управление осуществляется двумя взаимоинверсными сигналами Vи, которые поступают на затворы транзисторов от управляющего инвертора.

При V=транзисторыиключе открыты.

При V=-,- заперты.

условное изображение

Проводящие каналы обоих транзисторов

имеют сопротивление 20 – 500 Ом, носит

активный характер, а линейно в рабочем

диапазоне входных напряжений, и обладают

двуобгонной проводимостью. По этим

причинам двунаправленные ключи используют

для коммутации как дискретных так и

аналоговых сигналов. В закрытом состоянии

сопротивление между выводами xиyсоставляетОм.

В закрытом состоянии

сопротивление между выводами xиyсоставляетОм.

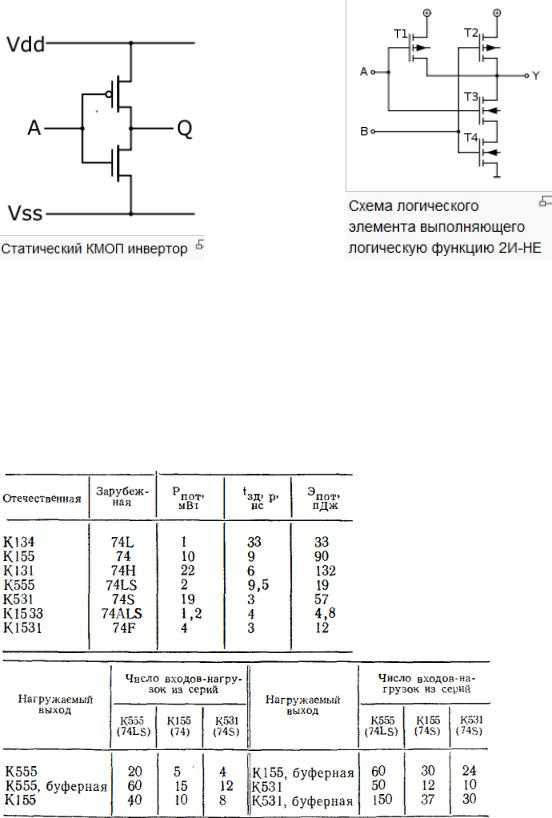

Логические элементы кмоп.

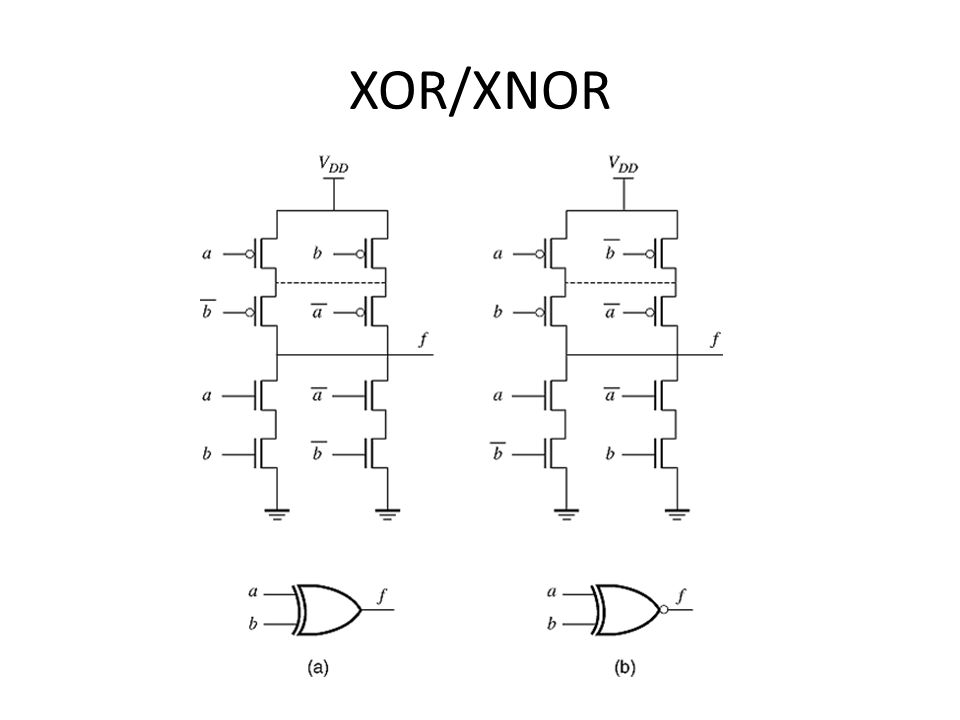

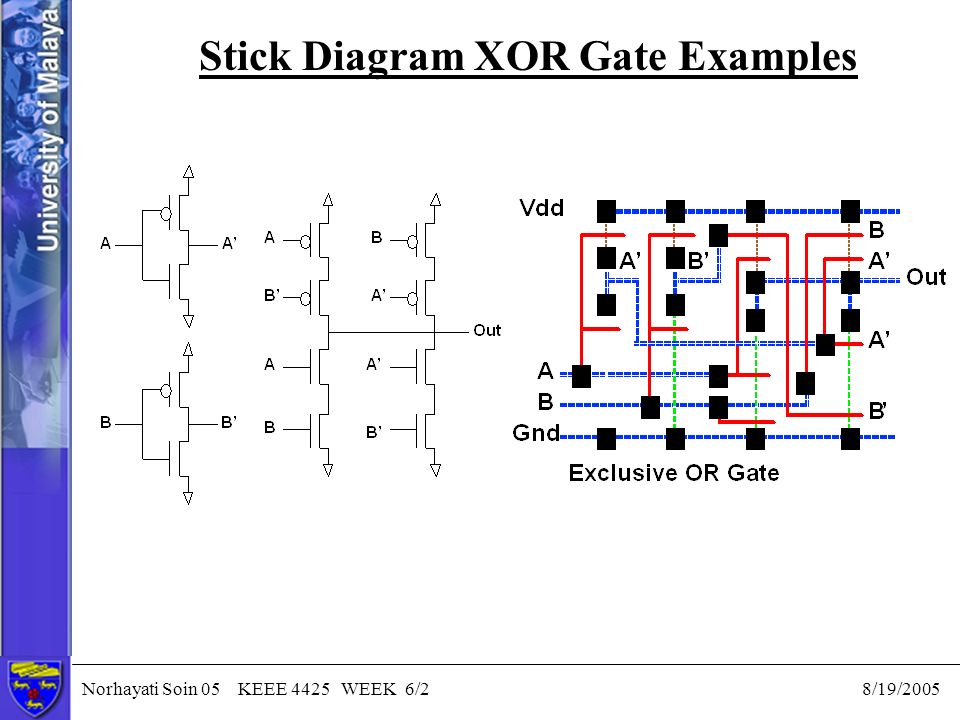

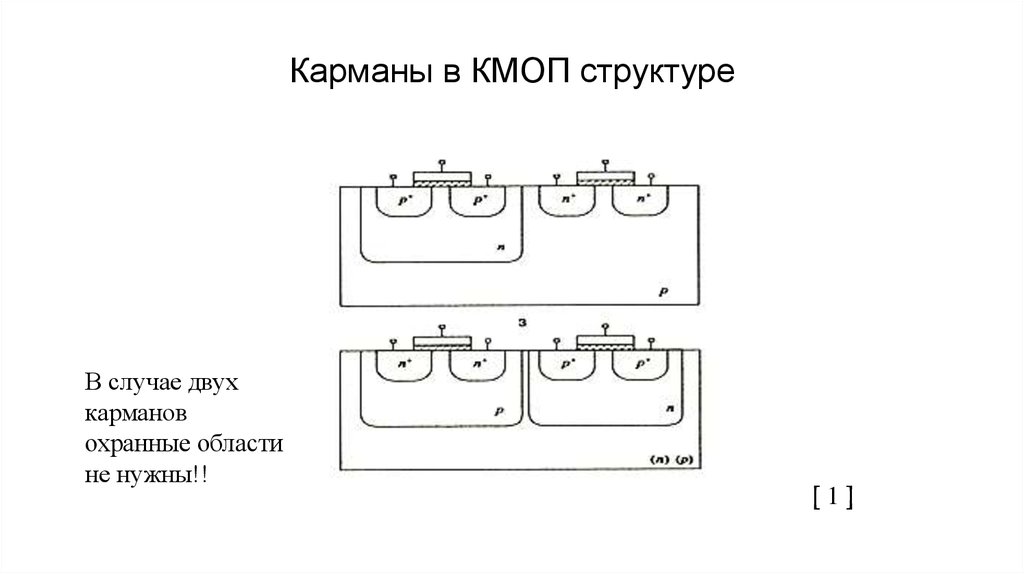

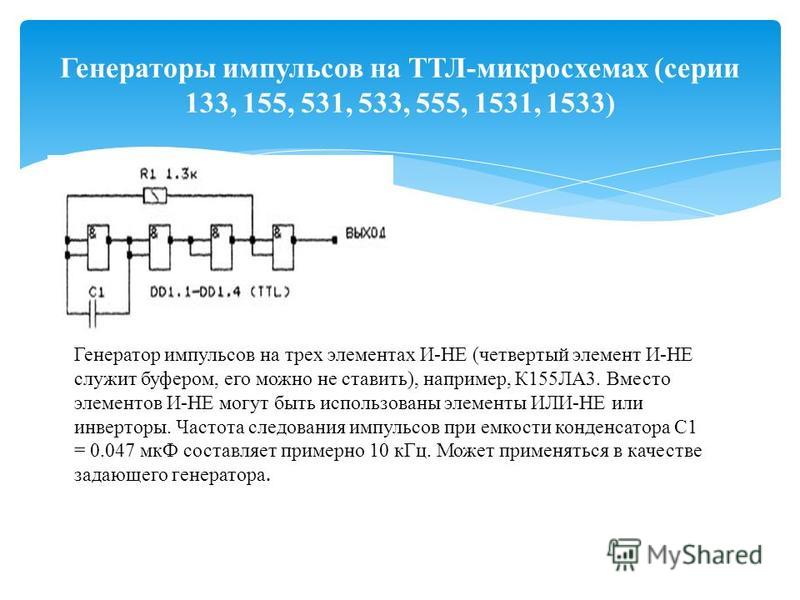

На основе инверторов КМОП реализуются многие функциональные логические схемы. Для реализации логических элементов И – НЕ в положительной логике транзисторы с n- каналом включаются последовательно друг с другом, с р- каналом параллельно, а для операции ИЛИ – НЕ наоборот.

Принципиальная схема логического Принципиальная схема логического

элемента 2И — НЕ элемента 2ИЛИ — НЕ

Для И – НЕ при a=b= 1 обаn- канальных транзистора открыты, а для р- канальные заперты, на выходеy= 0. Если хотя бы один входной сигнал равен 0, то один из р- транзисторов откроется, а спаренный с нимn- канальный транзистор закроется иy= 1.

Аналогично для элемента ИЛИ – НЕ, когда a=b= 0 оба р- канальных транзистора открыты, аn- канальные закрыты.

На выходе

.

Если хотя бы на один входaилиbили оба сразу

поступает,

соответствующийn- канальный

открывается, парный р- канальный закроется

и на выходе.

Логические элементы КМОП с большим числом входов организованы подобным образом.

Практические рекомендации.

Затвор и подложка МОП транзистора, разделенные диэлектриком образуют конденсатор (С = 5 пФ). Электрическая прочность не превышает 150 – 200 В. На теле человека и на оборудовании за счет электризации могут возникать заряды статического электричества в несколько киловольт.

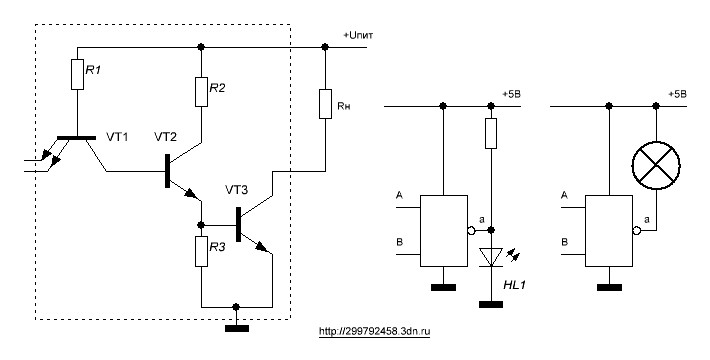

Для защиты транзисторов от повреждения высоким напряжением каждый вход ИС КМОВ снабжают диодно защитной цепью.

R= 0,5 – 1,5 кОм

В зависимости от значения и полярности перегрузочного напряжения диоды либо проводят в прямом направлении В, либо находятся в режиме лавинного пробоя, который наступает при обратном напряжении 30 – 35 В. Лавинный пробой диодов имеет обратимый характер и на работоспособности ИС не отражается.

В нормальных условиях, когда амплитуда

входного напряжения не выходит за

пределы – 0,7 В

В отпирания входных диодов не происходит.

Предельный допустимый ток охранных диодов мА (мА).

Если на вход поступают большие напряжения, то на вход подключают дополнительный ограничивающий резистор для ограничения тока через диоды (до 1 – 2 мА)

.

При работе ИС на большую емкостную нагрузку (С > 500 пФ) для защиты выходных транзисторов и выходу добавляется ограничивающий резистор.

Входы КМОП микросхем (в отличие от ТТЛ) недопустимо оставлять свободными на не подсоединенных входах могут возникнут непредсказуемые напряжения за счет наводок и связей через паразитные ёмкости.

Микросхемы КМОП при В допускают короткие замыкания выхода с шины питания или общей шиной.

Для создания уровней логических “1” и “0” входы непосредственно соединяют с шинами питания и общей шиной соответственно.

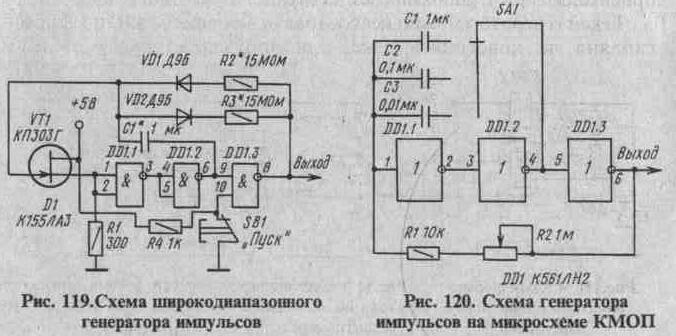

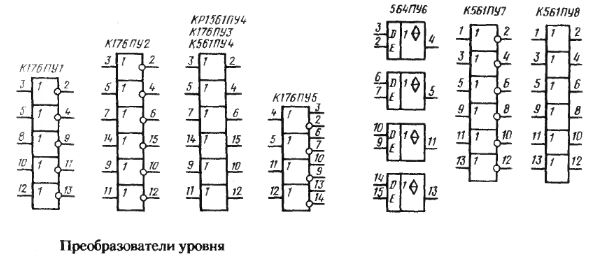

Для согласования выходных уровней КМОП структур со входами ТТЛ схем применяются ИСК561ЛН2 и К561ПУ4. ЛН2 содержит 6 инверторов, а ПУ4 6 повторителей с повышенной нагрузочной способностью по току.

Для согласования выхода ТТЛ со входом КМОП при питании последних повышенным напряжением >5 В применяют ИС К561ПУ7, ПУ8, содержащих по шесть преобразователей уровня. ПУ8 выполняет эту операцию без инверсии, а ПУ7 с инверсией.

|

Заглавная страница

Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: Археология ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрации Техника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ? Влияние общества на человека Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. |

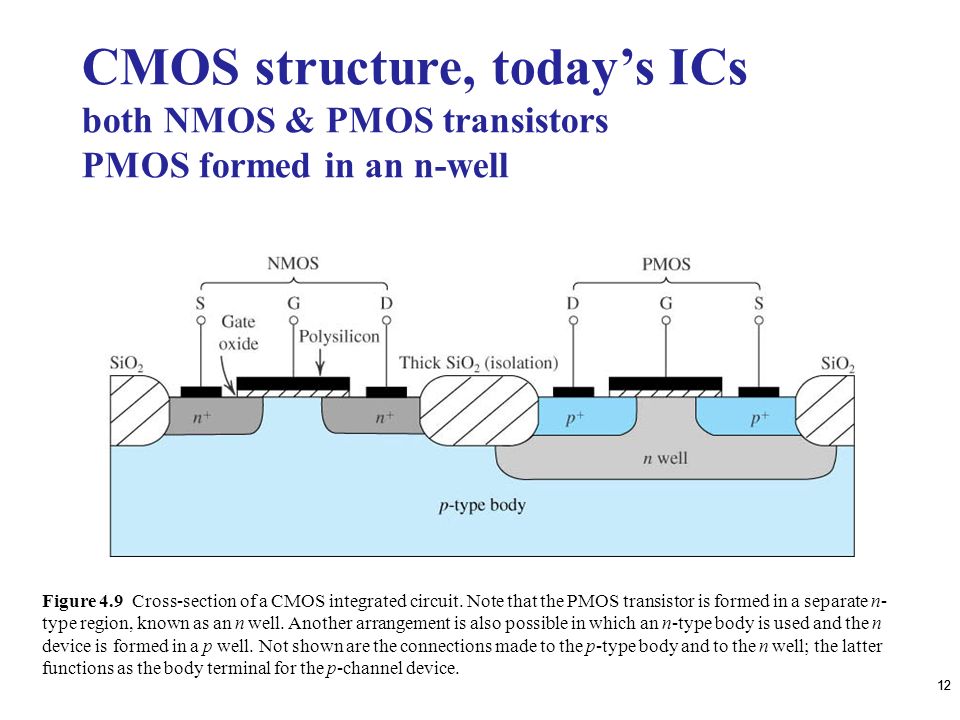

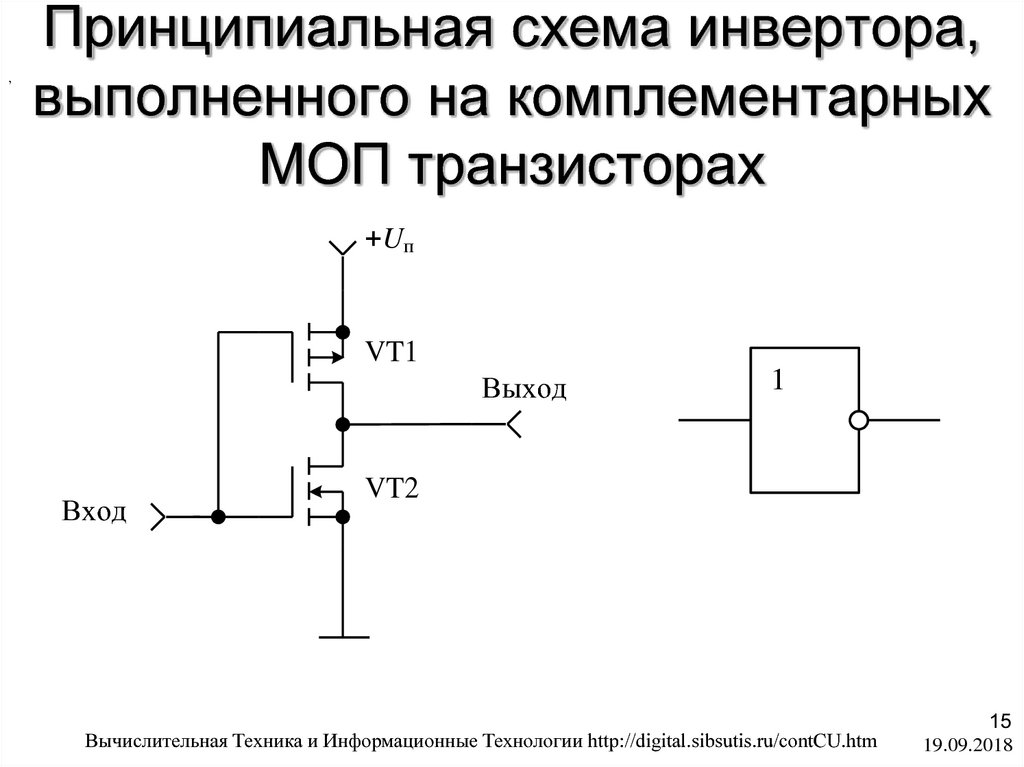

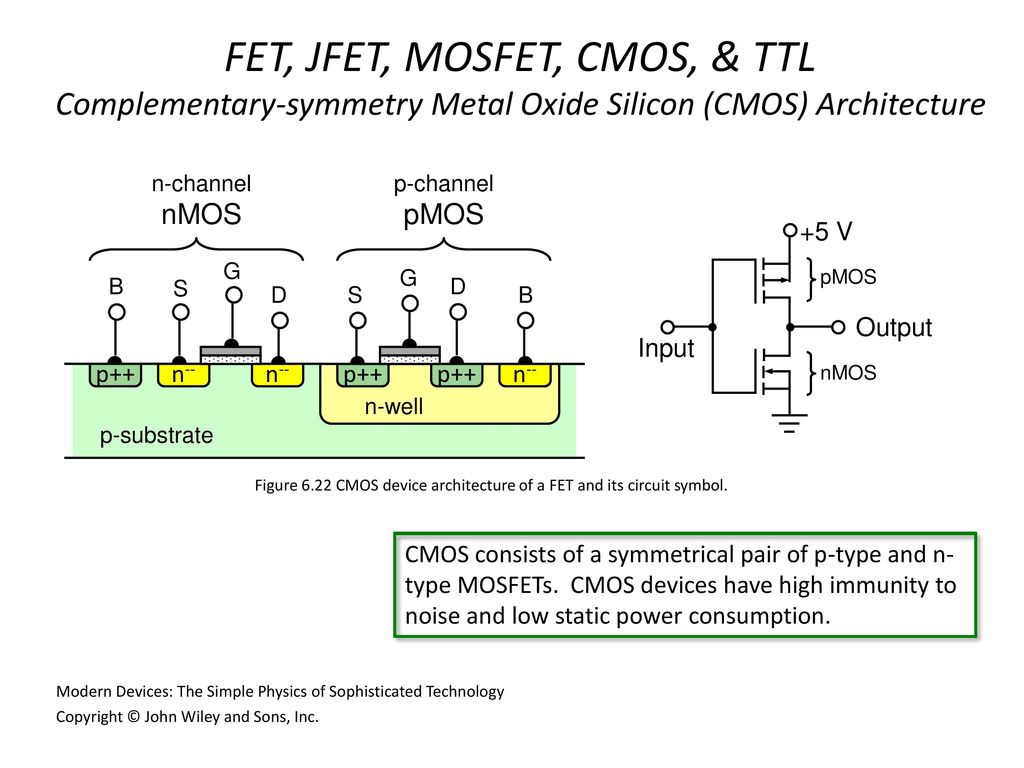

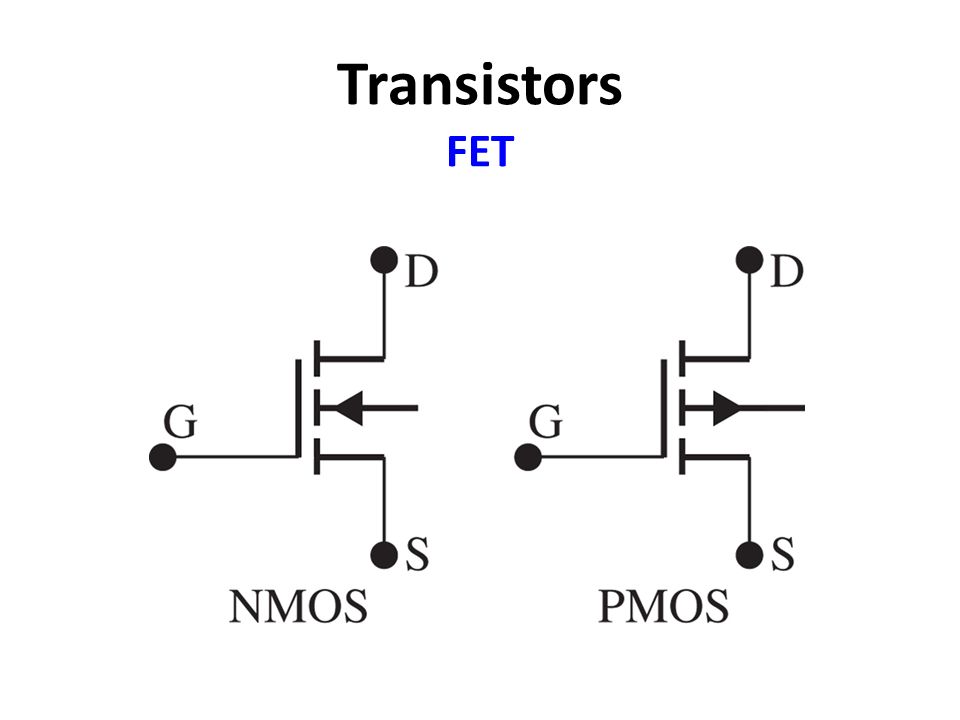

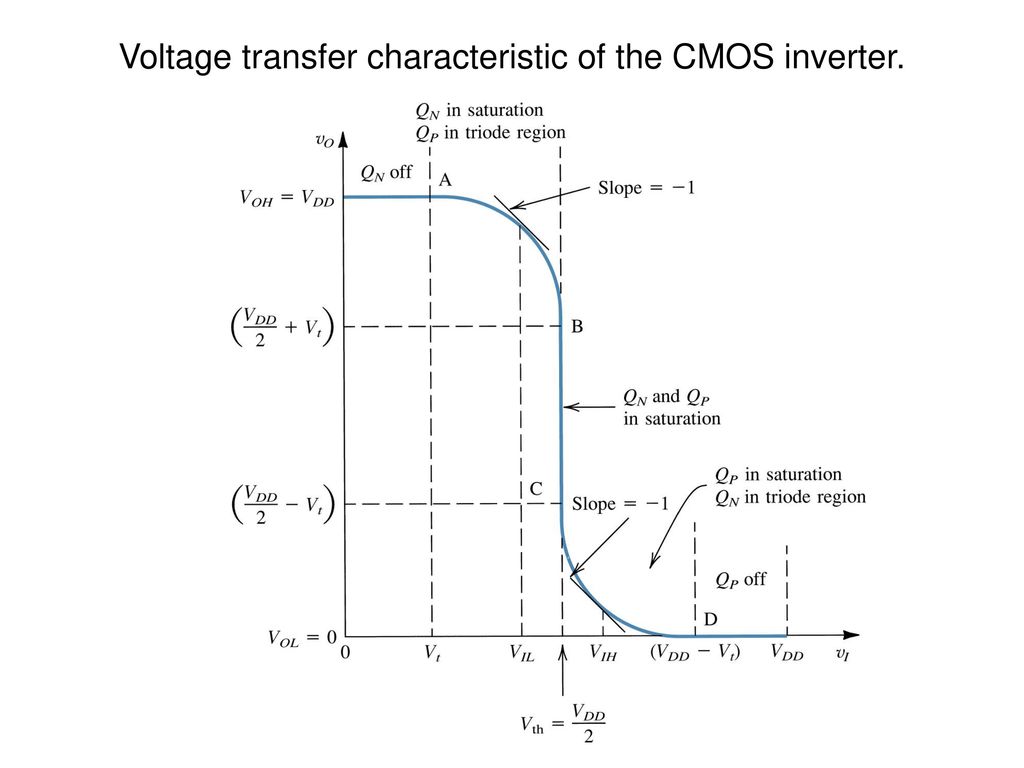

⇐ ПредыдущаяСтр 5 из 23Следующая ⇒ Микросхемы на комплементарных транзисторах (КМОП) строятся на основе МОП транзисторов с n- и p-каналами. Один и тот же входной потенциал открывает транзистор с n-каналом и закрывает транзистор с p-каналом. При формировании логической единицы открыт верхний транзистор, а нижний закрыт. В результате ток через КМОП микросхему не протекает. При формировании логического нуля открыт нижний транзистор, а верхний закрыт. И в этом случае ток через КМОП микросхему не протекает. Простейший логический элемент — это инвертор. Его схема приведена на рисунке 4.1.

На этой схеме для упрощения понимания принципов работы КМОП микросхемы не показаны защитные и паразитные диоды. В результате этой особенности КМОП микросхем, они обладают преимуществом перед рассмотренными ранее видами цифровых микросхем — потребляют ток в зависимости от поданной на вход тактовой частоты. Примерный график зависимости потребления тока КМОП микросхемы в зависимости от частоты ее переключения приведен на рисунке 4.2

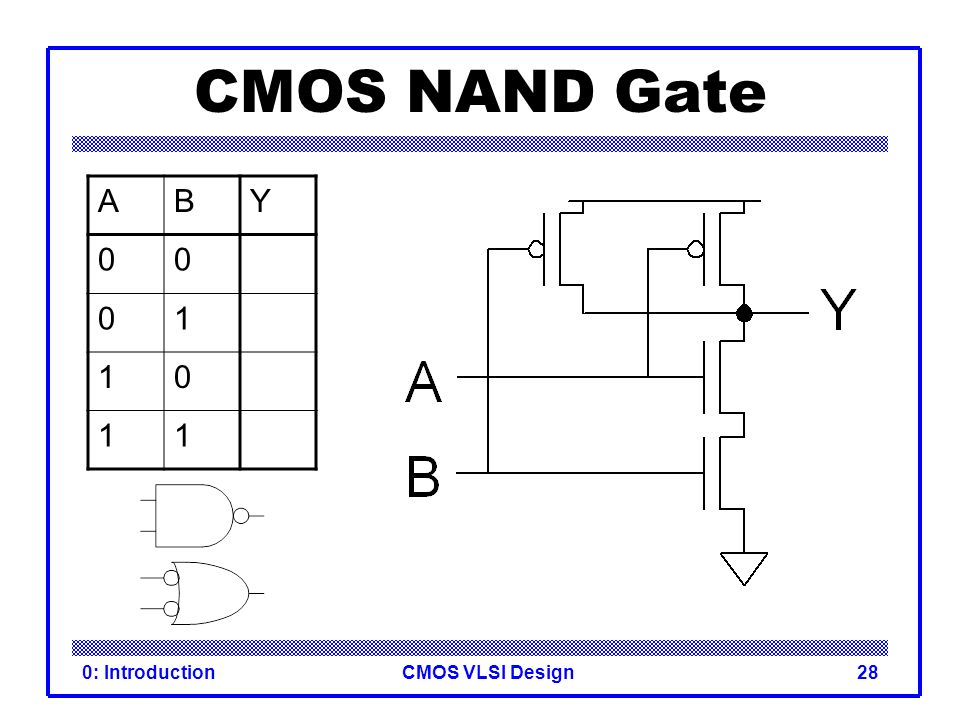

Логические КМОП (КМДП) элементы «И» Схема логического элемента «И-НЕ» на КМОП микросхемах практически совпадает с упрощенной схемой «И» на ключах с электронным управлением, которую мы рассматривали ранее. Отличие заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику питания. Принципиальная схема логического элемента «2И-НЕ», выполненного на комплементарных МОП транзисторах (КМОП), приведена на рисунке 4.

В этой схеме можно было бы применить в верхнем плече обыкновенный резистор, однако при формировании низкого уровня сигнала схема постоянно потребляла бы ток. Вместо этого, в качестве нагрузки используются p-МОП транзисторы. Эти транзисторы образуют активную нагрузку. Если на выходе требуется сформировать высокий потенциал, то транзисторы открываются, а если низкий — то закрываются. В приведённой на рисунке 4.2 схеме логического КМОП элемента «И», ток от источника питания на выход КМОП микросхемы будет поступать через один из транзисторов, если хотя бы на одном из входов (или на обоих сразу) будет присутствовать низкий потенциал (уровень логического нуля). Если же на обоих входах логического КМОП элемента «И» будет присутствовать уровень логической единицы, то оба p-МОП транзистора будут закрыты и на выходе КМОП микросхемы сформируется низкий потенциал. Условно-графическое изображение КМОП логического элемента «2И-НЕ» показано на рисунке 4.4, а таблица истинности приведена в таблице 4.1. В таблице 4.1 входы обозначены как x1 и x2, а выход — F.

Таблица 4.1. Таблица истинности МОП микросхемы, выполняющей логическую функцию «2И-НЕ»

Логические КМОП (КМДП) элементы «ИЛИ» Логический элемент «ИЛИ», выполненный на КМОП транзисторах, представляет собой параллельное соединение ключей с электронным управлением.

В схеме КМОП логического элемента «2ИЛИ-НЕ» в качестве нагрузки используются последовательно включенные p-МОП транзисторы. В ней ток от источника питания на выход КМОП микросхемы будет поступать только если все транзисторы в верхнем плече будут открыты, т.е. если сразу на всех входах будет присутствовать низкий потенциал (уровень логического нуля). Если же хотя бы на одном из входов будет присутствовать уровень логической единицы, то верхнее плечо двухтактного каскада, собранного на КМОП транзисторах, будет закрыто и ток от источника питания поступать на выход КМОП микросхемы не будет. Таблица истинности логического элемента «2ИЛИ-НЕ», реализуемая КМОП микросхемой, приведена в таблице 4.2, а условно-графическое обозначение этих элементов приведено на рисунке 4.6.

Таблица 4.2. Таблица истинности МОП микросхемы, выполняющей логическую функцию «2ИЛИ-НЕ»

В настоящее время именно КМОП микросхемы получили наибольшее развитие. Причём наблюдается постоянная тенденция к снижению напряжения питания. Первые серии микросхем такие как К1561 (иностранный аналог C4000В) обладали достаточно широким диапазоном изменения напряжения питания (3. ⇐ Предыдущая12345678910Следующая ⇒ Читайте также: Организация работы процедурного кабинета Статус республик в составе РФ Понятие финансов, их функции и особенности Сущность демографической политии |

||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-30; просмотров: 623; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia. |

Laikinio skaitmeninio keitiklio skiriamosios gebos didinimas.

Сантраука. Laikinis skaitmeninis keitiklis (LSK) yra vienas

pagrindiniu visiUkai skaitmenines structuros daPnio sintezatoriaus (DS)

блок, atliekantis fazes detektoriaus funkcija. LSK iUejimo signalas yra

skaitmeninis, todel jis daro itaka kvantavimo triukUmui daPnio

синтезаториус иУеджимэ. Siekiant gerinti DS iUejimo triukUmo lygi,

reikia didinti LSK skiriamaja geba. Ja galima didinti tobulinant KMOP

технология арба ЛСК структура. Pats paprasciausias LSK yra paremtas

инвертируй велинимо линия, о джо скириамойи геба йра атвиркУчай

proporcinga maPiausiam laiko tarpui, kuri galima iUmatuoti tokiu LSK—t.

у. инвертио velinimo trukmei. Jos maPinimas yra technologinio LSK

скириамосиос гебос дидинимо эсме. Darbe yra parodoma инвертио velinimo

trukmes priklausomebe nuo technologiniu parametru ir skaiciuojamos jos

reikUmes taikant 65 нм KMOP технология. Скайявимай родо, кад

инвертор velinimo trukme taikant Uia technologija gali kisti nuo 7 ps

ики 54 шт. Kai yra projektavimo apribojimas, norint taikyti tam tikra

KMOP technologija, pagal kuriavertio velinimo trukme negarantuoja

reikiamo DS fazes triukUmo lygio, reikia tobulinti LSK структура.

Tobulinant LSK structura, siekiama iUmatuoti laiko tarpa, maPesni nei

инвертио velinimo trukme. Darbe yra apPvelgiamos LSK structuros,

kuriomis galima iUmatuoti subinverterines laiko trukmes: LSK—Vernier

velinimo linija, LSK—2D Vernier plokUtuma, stochastinis LSK, Piedinis

LSK ir daugiapakopis LSK.

Darbe yra parodoma инвертио velinimo

trukmes priklausomebe nuo technologiniu parametru ir skaiciuojamos jos

reikUmes taikant 65 нм KMOP технология. Скайявимай родо, кад

инвертор velinimo trukme taikant Uia technologija gali kisti nuo 7 ps

ики 54 шт. Kai yra projektavimo apribojimas, norint taikyti tam tikra

KMOP technologija, pagal kuriavertio velinimo trukme negarantuoja

reikiamo DS fazes triukUmo lygio, reikia tobulinti LSK структура.

Tobulinant LSK structura, siekiama iUmatuoti laiko tarpa, maPesni nei

инвертио velinimo trukme. Darbe yra apPvelgiamos LSK structuros,

kuriomis galima iUmatuoti subinverterines laiko trukmes: LSK—Vernier

velinimo linija, LSK—2D Vernier plokUtuma, stochastinis LSK, Piedinis

LSK ir daugiapakopis LSK.

ReikUminiai PodPiai: laikinis skaitmeninis keitiklis, skiriamoji geba, velinimo trukme, KMOP.

Ивадас

Laikinis skaitmeninis keitiklis—tai itaisas, suteikiantis laiko

tarpui tarp dvieju signalu frontu skaitmenine iUraiUka (Staszewski et

др. 2006). Pastaruoju metu jis daPnai naudojamas kaip fazes detektorius

visiUkai skaitmeninese fazes derinimo kilpose (FDK), atliekanciose

daPnio sintezatoriaus (DS) функция irengtuose daPnio sintezatoriuose

(ДС) (1 пав.).

2006). Pastaruoju metu jis daPnai naudojamas kaip fazes detektorius

visiUkai skaitmeninese fazes derinimo kilpose (FDK), atliekanciose

daPnio sintezatoriaus (DS) функция irengtuose daPnio sintezatoriuose

(ДС) (1 пав.).

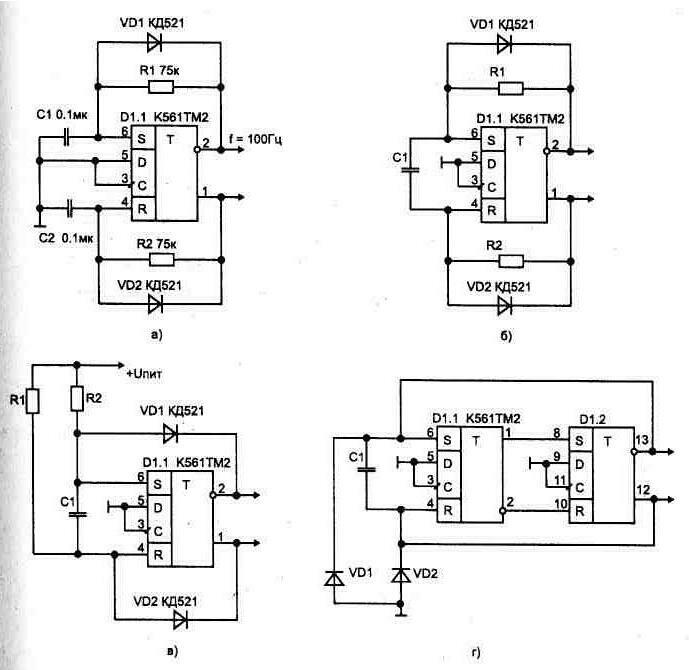

Pats paprasciausias LSK yra paremtas инверторный velinimo linija (2 пав.) (Сташевский и др., 2006; Эффендрик и др., 2011). Джеймс SVG генерируйямас сигналас склинда инвертиу велинимо линия, или атраминио signalo frontu Uis signalas fiksuojamas po kiekvieno velinimo elemento. LSK iUejime yra gaunamas pseudotermometrinis kodas, kuri iUkodavus gaunama informacija apie laiko tarpa, skirianti atraminio ir generuojamo фронтальный сигнал.

MaPiausias laiko tarpas, kuri galima pamatuoti tokiu LSK, yra инвертио velinimo trukme [t.sub.res] = [?t.sub.inv], или LSK skiriamoji геба:

[МАТЕМАТИЧЕСКОЕ ВЫРАЖЕНИЕ НЕ ВОСПРОИЗВОДИМО В ASCII] (1)

LSK ИУэхимо Сигналас Ира Скайтменинис, Тодел Джис ДаПнио

sintezatoriaus iUejime sukuria kvantavimo triukUma. Юра иУвеста

аналитин LSK kuriamo maPiausio fazes triukUmo lygio DS artimojoje

srityje (англ. внутриполосный) iUraiUka (Staszewski et al. 2011):

Юра иУвеста

аналитин LSK kuriamo maPiausio fazes triukUmo lygio DS artimojoje

srityje (англ. внутриполосный) iUraiUka (Staszewski et al. 2011):

[МАТЕМАТИЧЕСКОЕ ВЫРАЖЕНИЕ НЕ ВОСПРОИЗВОДИМО В ASCII] (2)

cia [F.sub.SVG]—generuojamojo signalo daPnis, [F.sub.REF] — atraminio signalo daPnis, [t.sub.res] — maPiausias LSK iUmatuojamas laiko tarpas.

МЕ (2) iUraiUkos matyti, kad LSK kuriamas triukUmas priklauso nuo genruojamojo ir atraminio signalu daPniu bei LSK skiriamosios gebos maPiausios vertes. Generuojamojo ir atraminio signalu daPniai yra daPnio sintezatoriaus technines uPduoties (reikalavimu) parametrai. Тодель ЛСК kuriama triukUma galima sumaPinti tik didinant jo skiriamaja geba. Тай galima pasiekti dviem budais: tobulinant KMOP integriniu grandynu (IG) gamybos technologija arba tobulinant LSK structura.

Technologinis LSK skiriamosios gebos didinimas

Tokio skiriamosios gebos didinimo esme—tobulinti KMOP IG technologija, siekiant sumaPinti инверторный velinimo trukme, kuri apibrePiama kaip инвертио iUejimo signalo kylanciojo ir krentanciojo frontu velinimo trukmiu vidurkis (Разави 2013):

[МАТЕМАТИЧЕСКОЕ ВЫРАЖЕНИЕ НЕ ВОСПРОИЗВОДИМО В ASCII] (3)

cia [t.![]() sub.kl] ir [t.sub.kr] — инвертор iUejimo signalo kylancio o

ir krenkltanciojo frontu velinimo trukmes (3 пав.).

sub.kl] ir [t.sub.kr] — инвертор iUejimo signalo kylancio o

ir krenkltanciojo frontu velinimo trukmes (3 пав.).

Inverterio iUejimo signalo kylanciojo fronto velinimo trukme [t.sub.kl] apibrePiama kaip laiko tarpas, за курс инвертио iUejimo signalas pakyla nuo nulines itampos iki puses maitinimo tampos. Atitinkamai [t.sub.kr] — laiko tarpas, per kurvertio iUejimo signalas nukrenta nuo maitinimo itampos iki puses maitinimo itampos (3 пав.).

Krentanciojo fronto metuvertio iejima veikia aukUto loginio lygio signalas (4 пав., а), тодел инверти сударантис NMOP tranzistorius yra soties busenos, o PMOP tranzistorius—atkirtos бусенос. Tokiu atveju инвертио iUejimo talpa bus iUkraunama per NMOP транзитная история juo tekancia santakos-iUtakos srove [I.sub.SIn], kuri apytiksliai gali buti iUreikUta (Разави 2013):

[МАТЕМАТИЧЕСКОЕ ВЫРАЖЕНИЕ НЕ ВОСПРОИЗВОДИМО В ASCII] (4)

cia [W.sub.n] ir [L.sub.n] — atitinkamai NMOP tranzistoriaus plotis

ir ilgis, [[micro]. sub.n]—NMOP tranzistoriaus kruvininku judris,

[C.sub.ox] — NMOP tranzistoriaus upturos oksido savitoi talpa,

[V.sub.tn] — NMOP tranzistoriaus atkirtos tampa, [V.sub.DD] — инвертор

майтинимо итампа.

sub.n]—NMOP tranzistoriaus kruvininku judris,

[C.sub.ox] — NMOP tranzistoriaus upturos oksido savitoi talpa,

[V.sub.tn] — NMOP tranzistoriaus atkirtos tampa, [V.sub.DD] — инвертор

майтинимо итампа.

Туринт транзитных серий иУрайУка (4) ир тариант, кад инвертио апкровос талпа иукраунама ики пусес майтинимо итампос, галима apskaicuoti krentanciojo fronto velinimo trukme:

[МАТЕМАТИЧЕСКОЕ ВЫРАЖЕНИЕ НЕ ВОСПРОИЗВОДИМО В ASCII] (5)

cia [C.sub.L]—inverterio apkrovos talpa.

AnalogiUkai (4) formulei galima iUvesti kylanciojo fronto metu apkrovos talpa ikraunancios PMOP tranzistoriaus sroves формула (6) (4 пав., б) ir iU jos apskaiciuoti kylanciojo fronto velinimo trukme (7), laikant, kad apkrovos talpa ikraunama iki puses maitinimo itampos:

[МАТЕМАТИЧЕСКОЕ ВЫРАЖЕНИЕ НЕ ВОСПРОИЗВОДИМО В ASCII] (6)

cia [W.sub.p] ir [L.sub.p] — atitinkamai PMOP tranzistoriaus plotis

ir ilgis, [[micro].sub.p]—PMOP tranzistoriaus kruvininku judris,

[C. sub.ox] — PMOP tranzistoriaus uPturos oksido savitoji talpa, kuri

apytikriai lygi NMOP transistoriaus oksido savitajai talpai,

[V.sub.tp] — PMOP tranzistoriaus atkirtos tampa, [V.sub.DD] — инвертор

майтинимо итампа;

sub.ox] — PMOP tranzistoriaus uPturos oksido savitoji talpa, kuri

apytikriai lygi NMOP transistoriaus oksido savitajai talpai,

[V.sub.tp] — PMOP tranzistoriaus atkirtos tampa, [V.sub.DD] — инвертор

майтинимо итампа;

[МАТЕМАТИЧЕСКОЕ ВЫРАЖЕНИЕ, НЕ ВОСПРОИЗВОДИМОЕ В ASCII] (7)

cia [C.sub.L]—inverterio apkrovos talpa.

Pagal (3), (5) ir (7) формул laikydami, kad PMOP ir NMOP tranzistoriu upturos oksidu savitosios talpos vienodos, ir manydami, kad PMOP tranzistoriaus plotis yra dvigubai didesnis nei NMOP tranzistoriaus сюжет, галиме гаути бендраджа инвертио велинимо трукмес иураиука:

[МАТЕМАТИЧЕСКОЕ ВЫРАЖЕНИЕ НЕ ВОСПРОИЗВОДИМО В ASCII]. (8)

Гаута иУрайУка ыра апытикре, нес я иуведант лайкома, кад НМОП ир

PMOP tranzistoriai, kai per juos pradeda teketivertio apkrovos

талпа икраунанти арба иукраунанти срове, неилуэина иу сотиес репимо. Быть

к, taikant Uia формула neivertinami trumpo kanalo efektai. Тодель (8)

iUraiUka yra tinkama tik greitiems skaiciavimams — ivertinti, kaip

technologiniai parametrai veikia velinimo trukme. Норинт апскайциуотус

rezultatus priartinti prie realiu velinimo trukmiu, gauta iUraiUka

reikia padauginti iU papildomo daugiklio, kuris 65 нм KMOP

technologijoje yra lygus:

Норинт апскайциуотус

rezultatus priartinti prie realiu velinimo trukmiu, gauta iUraiUka

reikia padauginti iU papildomo daugiklio, kuris 65 нм KMOP

technologijoje yra lygus:

D = 0,6ln[CL]+5. (9)

Projektuodamas integrini grandyna pagal konkrecia technologija, projektuotojas negali keisti tranzistoriaus kruvininku judrio, oksido савитосиос талпос, аткиртос итампос, кури недауг кинта, кай кейчиами транзисториаус матменис. Тодел пагал (8) iUraiUka, panaudojus daugikli (9), apskaiciuojamos инвертиу velinimo trukmes priklausomybes nuo tranzistoriaus ilgio ir plocio santykio (esant minimaliam uPturos ilgiui), apkrovos talpos ir maitinimo itampos taikant 65 нм KMOP технология.

Apskaiciuotos инвертио velinimo trukmes priklausomybes nuo

apkrovos talpos bei tranzistoriaus ilgio ir plocio santykio bei

инвертио velinimo trukmes priklausomybe nuo maitinimo itampos ir

апкровос талпос патейктос 5 и 6 пав. Visi atliekant skaiciavimus

taikyti technologiniai parametrai yra pateikti 1 lenteleje. Скайсиуойант

taip pat ivertinama, kad LSK sudaranciu инвертиу apкровос талпа негали

buti lygi nuliui, nesverti apkrauna kitas prie jo prijungtas

velinimo linijos инверторис.

Скайсиуойант

taip pat ivertinama, kad LSK sudaranciu инвертиу apкровос талпа негали

buti lygi nuliui, nesverti apkrauna kitas prie jo prijungtas

velinimo linijos инверторис.

МЕ 5 пав. pateiktu skaiciavimo rezultatu matyti, kad, esant 1,2 V майтинимо итампай, о апкровос талпай кинтан нуо 10 фФ ики 100 фф, инвертор velinimo trukme gali kisti nuo 7 ps iki 30 ps.

Skaiciavimo rezultatai, pateikti 6 pav., gauti, esant tranzistoriaus ilgio bei plocio santykiui [W.sub.n]/L lygiam 66,67 ir maitinimo itampai kintant nuo 0,9 V iki 1,4 V IU 6 пав. патейкту rezultatu matyti, kadvertio velinimo trukme gali kisti nuo 7,6 ps ики 54 шт.

IU skaiciavimo rezultatu анализирует iUplaukia iUvada, kad, didinant

транзитная история ilgio ir plocio santyki bei didinant maitinimo itampa,

инвертио velinimo trukme maPeja ир LSK skiriamoji geba dideja. Тай

vyksta del didejancios tranzistoriais tekancios sroves, kuri greiciau

ikrauna arba iУкрауна инвертио апкровос талпа. Дидежант апкровос

talpai LSK skiriamoji geba maPeja.

Дидежант апкровос

talpai LSK skiriamoji geba maPeja.

LSK структурные тобулинимы

Projektuojant integrinius grandynus, daPnai del gamybos kainos, del projektuojamo grandyno suderinamumo su kitais integriniais grandynais ir jau sukurtais blokais arba del kitu priePasciu gali buti taikoma tik tam tikra IG gamybos technologija. Jeigu ja taikant igyvendinamu LSK sudaranciu инвертиу velinimo trukme negarantuoja reikiamos skiriamosios gebos ir triukUmo, apskaiciuoto pagal (1) iUraiUka, lygio, tenka rinktis sudetingesne LSK структура. AppPvelgsime LSK структуры, leidPiancias iUmatuoti laiko tarpa, maPesni upvertio velinimo трукме.

Vernier velinimo linija. LSK—Vernier velinimo linijoje yra

naudojamos dvi velinimo linijos, sudarytos iU velinimo elementu,

turinciuskiringas velinimo trukmes (7 пав.) (Liscidini et al. 2009).

Per viena linija yra siunciamas DS generuojamas signalas, per

кита — сигналы атраминис. Jei pirma ir antra velinimo linija sudaranciu

velinimo elementu velinimo trukmes atitinkamai lygios [t. sub.1] ir

[t.sub.2], tai tokio LSK skiriamoji geba yra atvirkUciai proporcinga Uiu

велинимо трукмиу скирмуми (10):

sub.1] ir

[t.sub.2], tai tokio LSK skiriamoji geba yra atvirkUciai proporcinga Uiu

велинимо трукмиу скирмуми (10):

[МАТЕМАТИЧЕСКОЕ ВЫРАЖЕНИЕ НЕ ВОСПРОИЗВОДИМО В ASCII] (10)

Taigi, jei viena iU liniju yra sudaryta iU инвертиу, туринчу maPiausia velinimo trukme, tokio LSK skiriamoji geba yra didesne nei LSK—inverteriu velinimo linijos.

Prie velinimo liniju atitinkamu elementu iUejimu yra prijungti trigeriai, kuriu iUejimo signalo pobudis priklauso nuo to, kokio signalo frontas atkeliavo pirmas—loginis ,1″, jei atraminio signalo, arba loginis ,0″, jei generuojamojo signalo. velinimo linijos atveju, gaunamas termometrinis kodas. Джи Укодавус, taUke, kuriame trigerio iUejimas pakinta iU ,1″ i ,0″, gaunama informacija apie generuojamo ir atraminio signalu frontu скиртума (фазес скиртума).

2D Vernier velinimo linija. Двею размерность (2D) Vernier velinimo

linijos veikimas nuo iprastos Vernier velinimo linijos skiriasi tuo, kad

лайко юбкамуи брезент генеруоджамоджо ир атраминио сигнало гаути наудоджами

dvieju velinimo liniju elementai (8 pav. , a) ir visos dvieju velinimo

liniju elementu tarpusavio kombinacijos (8 pav., b), tarsi iUdestant dvi

linijas dvimateje plokUtumoje X ir Y aUyse—gaunama Vernier plokUtuma

(Версези и др., 2010).

, a) ir visos dvieju velinimo

liniju elementu tarpusavio kombinacijos (8 pav., b), tarsi iUdestant dvi

linijas dvimateje plokUtumoje X ir Y aUyse—gaunama Vernier plokUtuma

(Версези и др., 2010).

eioje plokUtumoje taip pat galima atvaizduoti LSK—inverteriu velinimo linija (горизонтальные связи) ir klasikine Vernier velinimo linija (истриПа тиесе). Taigi toks 2D velinimo linijos apraUymas gali buti naudojamas kaip apibendrintas velinimo liniju apraUymas.

2D Vernier velinimo linijos skiriamoji geba yra lygi dvieju

velinimo liniju elementu velinimo trukmiu didPiausiam bendrajam

даликлюи (DBD). Lyginant su iprasta Vernier velinimo linija, jei

elementu velinimo trukmes yra 3? ir 5?, iprastos Vernier velinimo

linijos skiriamoji geba butu lygi 5?—3? = 2?, o 2D Vernier velinimo

линихос—?. Be to, tokio LSK iejimo signalu (fazes klaidos) ruoPas yra

didesnis del padidejusio tolygaus laiko kvantavimo ruoPo pasiskirstymo:

8 пав., б, матити, кад джис падидехо нуо ?-5? ики—3?-9?.

eio LSK trukumas—sudetingesnis igyvendinimas, nes reikalinga salygiUkai didele palyginimo matrica. Be to, jai budingi ir iprastos Vernier velinimo linijos trukumai—reikalingas dvieju velinimo liniju elementu velinimo trukmiu DBD ? palaikymas ir liniju derinimas.

Стохастинис ЛСК. Stochastinio tipo LSK sudarytas iU N vienodu, lygiagreciai sujungtu arbitru (9 пав., ARB N), fksuojanciu atraminio ir generuojamojo signalu frontus (Кратюк и др., 2009 г.; Самара, Карузоне 2013). Idealiu atveju kiekvienas arguments sugeneruoja logini ,0″ arba ,1″, priklausomai nuo to, kurio signalo frontas atkeliauja Пирмы.

Реалыбеже арбитражи вейкиа эсант там тикримс нетикслюмамс,

pasireiUkiantiems del ivairiu neidealiu reiUkiniu. Арбитро иУэхимо

сигнало нусистовехимо трукме ильгея, кай лайко скиртумас брезент

генеруоджамоджо ир атраминио сигналу фронту тампа мапас—пасирейукия

метастабильные эффекты. Be to, del elektroniniu itaisu, sudaranciu

арбитраж, параметр sklaidos kiekvienas арбитражи iejime turi tam tikra

итампос послинки (9pav. , itampos Ualtiniai [V.sub.OFN]). Дель Уио

poslinkio arbitru iejimo signalu ribines (suveikimo) itampos vertes Uiek

тик скириаси. Turint dideli arbitru skaiciu, Uios ribines itampos

poslinkiai pasiskirsto pagal Gauso desni esant standartiniam nuokrypiui

[s.sub.V]. Iejimo itampos pokyciai transformuojasi i iejimo signalo

Лайко Покициус. Todel jie taip pat iUsideste pagal Gauso desni esant

стандарт нуокрипиуи [s.sub.T].

, itampos Ualtiniai [V.sub.OFN]). Дель Уио

poslinkio arbitru iejimo signalu ribines (suveikimo) itampos vertes Uiek

тик скириаси. Turint dideli arbitru skaiciu, Uios ribines itampos

poslinkiai pasiskirsto pagal Gauso desni esant standartiniam nuokrypiui

[s.sub.V]. Iejimo itampos pokyciai transformuojasi i iejimo signalo

Лайко Покициус. Todel jie taip pat iUsideste pagal Gauso desni esant

стандарт нуокрипиуи [s.sub.T].

[s.sub.V] ir [s.sub.T] susije [s.sub.T] = [s.sub.V]/S, cia S yra iejimo signalo fronto statumas. Del Uiu neidealumu realybeje visu arbitru iUejimai nepasikeis vienu metu ir jie nebutinai bus vienodi. Susumavus visu arbitru iUejimu signalus, gaunama informacija apie faziu юбка.

Stochastinio LSK skiriamoji geba yra lygi:

[МАТЕМАТИЧЕСКОЕ ВЫРАЖЕНИЕ НЕ ВОСПРОИЗВОДИМО В ASCII] (11)

cia N—arbitru skaicius, S—iejimo signalo fronto statumas,

[s.sub.V] ir [s.sub.T] — atitinkamai itampos ir laiko skirstiniu

стандартная нуокрипия.

Taigi didinti stochastinio LSK skiriamaja geba galima didinant arbitru skaiciu, signalo statuma ir maPinant elementu sklaida. Джо trukumas—maPas iejimo signalu fazes skipumo ruoPas.

LSK, парем Piediniu генераториуми. Aediniai generatoriai gali бути наудоджами лайкиниам скайтмениниам кейтиклиуи сударити (10 пав.) (Ченг и др., 2016).

Tokiu atveju turi buti naudojamas daugiakelis (англ. Многолучевое распространение) Пьединис генераториус. Jo velinimo elementu iejimai sujungiami su keliu velinimo elementu iUejimais, пвз., 10 пав. пародия на velinimo elemento PMOP tranzistorius sujungtas su penktojo prieU ji einancio velinimo elemento iUejimu, o NMOP tranzistoriai sujungti su atitinkamai treciojo ir pirmojo prieU ji esancio velinimo elemento iUejimu. Токс Юнгимас leidPia paankstinti velinimo elemento persijungimo laika.

LSK, паремто Piediniu generatoriumi, skiriamoji geba gali buti

padidinama 5-6 kartus, lyginant su LSK—inverteriu velinimo linija.

Даугяпакопяй ЛСК. Laikiniai skaitmeniniai keitikliai gali buti sudaromi iU keliu LSK, kuriu skiriamoji geba yra skiringa (11 пав).

Pirmuju LSK pakopu skiriamoji geba yra maPiausia, паскутиниу — сделал Пиаусию. PavyzdPiui, LSK—velinimo linija sklindancio signalo suvelinta versija, kurios frontas yra arciausiai atraminio signalo fronto, gali buti jungiama i stochastinio LSK iejima (Самара, Карузоне 2013). Tokiu atveju gaunama skiriamoji geba, lygi stochastinio LSK skiriamajai gebai, ir LSK—velinimo linijos iejimo signalu fazes юбка ruoPas.

Ювадос

1. LSK skiriamoji geba veikia daPnio sintezatoriaus iUejimo fazes триукУма. Norint sumaPinti fazes triukUmo lygi, reikia didinti скириамая геба. Tai galima pasiekti tobulinant KMOP technologija arba Структура ЛСК.

2. Tobulinant KMOP technologija siekiama gauti kuo maPesne

инвертио velinimo trukme. Projektuotojas, taikydamas konkrecia

technologija, negali keisti daugelio technologiniu параметр:

tranzistoriaus kruvininku judrio, oksido savitosios talpos, atkirtos

итампос. Todelvertio velinimo trukme galima didinti tik maPinant

uPturos ilgi, didinant tranzistoriaus matmenu plocio ir ilgio santyki,

майтинимо итампа. Tokiu atveju yra didinama tranzistoriaus srove, kuri

greiciau ikrauna arba iUkrauna LSK sudaranciu инвертиу апкровос талпа.

Todelvertio velinimo trukme galima didinti tik maPinant

uPturos ilgi, didinant tranzistoriaus matmenu plocio ir ilgio santyki,

майтинимо итампа. Tokiu atveju yra didinama tranzistoriaus srove, kuri

greiciau ikrauna arba iUkrauna LSK sudaranciu инвертиу апкровос талпа.

3. Skaiciavimo rezultatai rodo, kad, taikant 65 нм KMOP технология, апкровос талпай кинтан нуо 10 фФ ики 100 фФ, майтинимо itampai esant 1,2 V, tranzistoriaus plocio ir ilgio santykio vertems esant 66,67, 133,33 ir 266,67,vertio velinimo trukme kinta nuo 7 ps ики 30 шт. Esant tranzistoriaus ilgio ir plocio santykiui lygiam 66,67, maitinimo itampai kintant nuo 0,9 V iki 1,4 V, инвертор velinimo trukme gali kisti nuo 7,6 пс ики 54 пс.

4. Структура Tobulinant LSK, siekiama iUmatuoti laiko tarpa,

maPesni UP инвертио velinimo trukme. Тай Галима Атликти Наудоянт

tokias LSK структуры: LSK—Vernier velinimo linija, LSK—2D Vernier

plokUtuma, stochastini LSK, Piedini LSK, daugiapakopi LSK. Паминету ЛСК

projektavimas sudetingeja del jiems butinu papildomu skaitymo,

Synchronizavimo, derinimo grandynu projektavimo.

Литература

Ченг З.; Чжэн, X .; Дин, MJ; Пэн, Х. 2016. Недавнее разработки и проблемы проектирования высокопроизводительного кольцевого генератора Преобразователи времени в цифру CMOS, транзакции IEEE на электронных устройствах 63(1): 235-251. https://doi.org/10.1109/ТЭД.2015.2503718

Эффендрик П.; Цзян, В .; ван де Гевел, М.; Вервал, Ф.; Сташевски, Р. Б. 2011. Преобразователь времени в цифру (TDC) для WiMAX ADPLL. в 40-нм CMOS, на 20-й Европейской конференции по теории и дизайну схем (ECCTD), 29–31 августа 2011 г., Линчепинг, Швеция, 365–368.

Кратюк В.; Ханумолу, П.К.; Ок, К.; Мун, Великобритания; Маярам, К. 2009. Цифровой PLL со стохастическим время-цифровым преобразователем, IEEE. Сделки по цепям и системам I: Обычные документы 56 (8): 1612-1621. https://doi.org/10.1109/TCSI.2008.2010109

Лискидини, А.; Верчези, Л.; Кастелло, Р. 2009. Время цифровизации

преобразователь на основе двумерной архитектуры Вернье в IEEE 2009 г. Конференция по специализированным интегральным схемам (CICC), 13-16 сентября 2009 г., Сан.

Хосе, Калифорния, США, стр. 45–48.

Конференция по специализированным интегральным схемам (CICC), 13-16 сентября 2009 г., Сан.

Хосе, Калифорния, США, стр. 45–48.

Разави, Б. 2013. Основы микроэлектроники. 2-е изд. Уайли. 928 стр.

Самара, А.; Карузоне, AC 2013. Цифровой контур фазовой автоподстройки частоты с калиброванный грубый и стохастический точный TDC, IEEE Journal of Solid-State Схемы 48 (8): 1829 г.-1841. https://doi.org/10.1109/JSSC.2013.2259031

Сташевский, Р. Б.; Вемулапалли, С.; Валлюр, П.; Уоллберг, Дж.; Balsara, PT 2006. 1,3 В 20 пс Преобразователь времени в цифру для частоты синтез в 90-нм CMOS, IEEE Transactions on Circuits and Systems II: Экспресс-сводки 53 (3): 220-224. https://doi.org/10.1109/TCSII.2005.858754

Сташевский, Р. Б.; Вахид, К.; Дульгер, Ф.; Элиэзер, О. Э. 2011.

Многоскоростная полностью цифровая PLL без паразитных помех для мобильных телефонов на 65-нм CMOS,

Журнал IEEE твердотельных схем 46 (12): 2904-2919.

https://doi.org/10.1109/JSSC.2011. 2162769

2162769

Верчези, Л.; Лисидини, А .; Кастелло, Р. 2010. Два измерения. нониусный преобразователь времени в цифровой, IEEE Journal of Solid-State Circuits 45(8): 1504-1512. https://doi.org/10.1109/JSSC.2010.2047435

Мариян ЮРГО (1), Ромуальдас НАВИККАС (2)

Vilniaus Gedimino technikos universitetas, Вильнюс, Литва

Эл. paUtas: (1) [email protected]; (2) [email protected]

ПОВЫШЕНИЕ РАЗРЕШЕНИЯ ВРЕМЕНИ В ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

М. Юрго, Р. Навицкас

Аннотация

Временно-цифровой преобразователь (ВЦП) является одним из основных блоков

полностью цифровой синтезатор частот (ФС), где он используется как фазовый

детектор. Выход TDC цифровой, поэтому он вводит

шум квантования на выходе ФС. Разрешение TDC должно быть

увеличен, для улучшения уровня фазового шума на выходе ФС. Может быть

достигается за счет совершенствования технологии КМОП или структуры ВЦП.

простейший TDC основан на линии задержки инвертора. Его разрешение

обратно пропорциональна интервалу времени, который можно измерить с помощью

такой ВМТ, т.е. время задержки инвертора. Уменьшение этой задержки

суть технологического повышения разрешающей способности ВЦП. В этом

работы зависимость задержки инвертора от технологических параметров

показано, и его значение рассчитано по технологии CMOS 65 нм. Расчеты

показывают, что в этой технологии время задержки инвертора может варьироваться от 7

пс до 54 пс. Если конструкция ограничена использованием определенных CMOS

технология, в которой задержка инвертора не обеспечивает необходимого шума

уровень на выходе ФС, структура ВЦП нуждается в доработке.

Целью этого усовершенствования является измерение временного интервала, меньшего, чем

задержка инвертора. Некоторые из структур TDC, которые могут измерять

время задержки субинвертора, рассмотрены в этой работе: ВЦП — Вернье задержка

линейный, ВМТ — двумерная нониусная плоскость, стохастический, кольцевой и многоступенчатый ВМТ.

Его разрешение

обратно пропорциональна интервалу времени, который можно измерить с помощью

такой ВМТ, т.е. время задержки инвертора. Уменьшение этой задержки

суть технологического повышения разрешающей способности ВЦП. В этом

работы зависимость задержки инвертора от технологических параметров

показано, и его значение рассчитано по технологии CMOS 65 нм. Расчеты

показывают, что в этой технологии время задержки инвертора может варьироваться от 7

пс до 54 пс. Если конструкция ограничена использованием определенных CMOS

технология, в которой задержка инвертора не обеспечивает необходимого шума

уровень на выходе ФС, структура ВЦП нуждается в доработке.

Целью этого усовершенствования является измерение временного интервала, меньшего, чем

задержка инвертора. Некоторые из структур TDC, которые могут измерять

время задержки субинвертора, рассмотрены в этой работе: ВЦП — Вернье задержка

линейный, ВМТ — двумерная нониусная плоскость, стохастический, кольцевой и многоступенчатый ВМТ.

Ключевые слова: времяцифровой преобразователь, разрешение, время задержки, КМОП.

Подпись: 1 пав. Supaprastinta visiUkai skaitmeninio daPnio структура синтеза: SVG — skaitmeniniu budu valdomas generatorius, LSK—laikinis skaitmeninis keitiklis Рис. 1. Упрощенная структура полностью цифровой синтезатор частот. SVG — осциллятор с цифровым управлением (DCO), LSK-преобразователь времени в цифру (TDC)

Подпись: 2 пав. Laikinis skaitmeninis keitiklis—inverteriu velinimo linija (a) ir jos signalai (b) Рис. 2. Время перехода на цифровые технологии преобразователь-инвертор, линия задержки (а) и ее сигналы (б)

Подпись: 3 пав. Inverterio iUejimo signalo velinimo trukme Рис. 3. Задержка выходного сигнала инвертора

Подпись: 4 пав. Inverterio апкровос талпос иукровимас ир икровимас esant aukUtam (a) ir Pemam (b) loginiam iejimo signalo lygiui инвертио iejime Рис. 4. Разряд и заряд нагрузочного конденсатора инвертора когда логический уровень входного сигнала соответственно высокий (а) и низкий (б)

Подпись: 5 пав. Inverterio velinimo trukmes priklausomybe nuo

apkrovos talpos bei tranzistoriaus ilgio ir plocio santykio Рис. 5.

Зависимость времени задержки инвертора от емкости и коэффициента нагрузки

ширины и длины транзисторов

Inverterio velinimo trukmes priklausomybe nuo

apkrovos talpos bei tranzistoriaus ilgio ir plocio santykio Рис. 5.

Зависимость времени задержки инвертора от емкости и коэффициента нагрузки

ширины и длины транзисторов

Заголовок: 6 пав. Inverterio velinimo trukmes priklausomybe nuo maitinimo itampos ir apkrovos talpos Рис. 6. Зависимость время задержки инвертора по напряжению питания и емкости нагрузки

Подпись: 7 пав. LSK—Vernier velinimo linija Рис. 7. TDC—Vernier линия задержки

Подпись: 8 пав. LSK—Vernier velinimo linijos (a) ir 2D Vernier velinimo linijos (b) palyginimas Рис. 8. ВМТ – сравнение нониуса линия задержки (а) и двумерная линия задержки Вернье (б)

Заголовок: 9 пав. Стохастинис ЛСК Рис. 9. Стохастический ВЦП

Подпись: 10 пав. LSK, paremtas daugelio keliu Piediniu генераториуми Рис. 10. ВЦП на основе многолучевого кольцевого генератора

Подпись: 11 пав. Daugiapakopis LSK Рис. 11. Многокаскадный TDC

1 лентеле.Технологии 65 нм для тайкоми параметры Таблица 1. Параметры КМОП-технологии 65 нм, используемые для расчетов Параметры Верте L, нм 60 [W.sub.n], [микро]м 4 8 16 [W.sub.n]/ л 66,67 133,33 266,67 [COX], мФ/[м2] 12,8 [C.sub.L], fF 10 50 90 [Vtn], мВ 359,5 [Втр], мВ -413,8 [микро]n, [м.суп.]2 / (Vs) 0,0211 [микро]р, [м2] / (Вс) 0,0080

Gale Apps — Технические трудности

Приложение, к которому вы пытаетесь получить доступ, в настоящее время недоступно. Приносим свои извинения за доставленные неудобства. Повторите попытку через несколько секунд.

Если проблемы с доступом сохраняются, обратитесь за помощью в наш отдел технической поддержки по телефону 1-800-877-4253. Еще раз спасибо, что выбрали Gale, обучающую компанию Cengage.

org.springframework.remoting.RemoteAccessException: невозможно получить доступ к удаленной службе [authorizationService@theBLISAuthorizationService]; вложенным исключением является com.zeroc.Ice.UnknownException

unknown = «java. lang.IndexOutOfBoundsException: индекс 0 выходит за границы для длины 0

в java.base/jdk.internal.util.Preconditions.outOfBounds(Preconditions.java:64)

в java.base/jdk.internal.util.Preconditions.outOfBoundsCheckIndex(Preconditions.java:70)

в java.base/jdk.internal.util.Preconditions.checkIndex(Preconditions.java:248)

в java.base/java.util.Objects.checkIndex(Objects.java:372)

в java.base/java.util.ArrayList.get(ArrayList.java:458)

в com.gale.blis.data.subscription.dao.LazyUserSessionDataLoaderStoredProcedure.populateSessionProperties(LazyUserSessionDataLoaderStoredProcedure.java:60)

в com.gale.blis.data.subscription.dao.LazyUserSessionDataLoaderStoredProcedure.reQuery(LazyUserSessionDataLoaderStoredProcedure.java:53)

в com.gale.blis.data.model.session.UserGroupEntitlementsManager.reinitializeUserGroupEntitlements(UserGroupEntitlementsManager.java:30)

в com.

lang.IndexOutOfBoundsException: индекс 0 выходит за границы для длины 0

в java.base/jdk.internal.util.Preconditions.outOfBounds(Preconditions.java:64)

в java.base/jdk.internal.util.Preconditions.outOfBoundsCheckIndex(Preconditions.java:70)

в java.base/jdk.internal.util.Preconditions.checkIndex(Preconditions.java:248)

в java.base/java.util.Objects.checkIndex(Objects.java:372)

в java.base/java.util.ArrayList.get(ArrayList.java:458)

в com.gale.blis.data.subscription.dao.LazyUserSessionDataLoaderStoredProcedure.populateSessionProperties(LazyUserSessionDataLoaderStoredProcedure.java:60)

в com.gale.blis.data.subscription.dao.LazyUserSessionDataLoaderStoredProcedure.reQuery(LazyUserSessionDataLoaderStoredProcedure.java:53)

в com.gale.blis.data.model.session.UserGroupEntitlementsManager.reinitializeUserGroupEntitlements(UserGroupEntitlementsManager.java:30)

в com. gale.blis.data.model.session.UserGroupSessionManager.getUserGroupEntitlements(UserGroupSessionManager.java:17)

в com.gale.blis.api.authorize.contentmodulefetchers.CrossSearchProductContentModuleFetcher.getProductSubscriptionCriteria(CrossSearchProductContentModuleFetcher.java:244)

на com.gale.blis.api.authorize.contentmodulefetchers.CrossSearchProductContentModuleFetcher.getSubscribedCrossSearchProductsForUser(CrossSearchProductContentModuleFetcher.java:71)

на com.gale.blis.api.authorize.contentmodulefetchers.CrossSearchProductContentModuleFetcher.getAvailableContentModulesForProduct(CrossSearchProductContentModuleFetcher.java:52)

на com.gale.blis.api.authorize.strategy.productentry.strategy.AbstractProductEntryAuthorizer.getContentModules(AbstractProductEntryAuthorizer.java:130)

на com.gale.blis.api.authorize.strategy.productentry.strategy.CrossSearchProductEntryAuthorizer.isAuthorized(CrossSearchProductEntryAuthorizer.

gale.blis.data.model.session.UserGroupSessionManager.getUserGroupEntitlements(UserGroupSessionManager.java:17)

в com.gale.blis.api.authorize.contentmodulefetchers.CrossSearchProductContentModuleFetcher.getProductSubscriptionCriteria(CrossSearchProductContentModuleFetcher.java:244)

на com.gale.blis.api.authorize.contentmodulefetchers.CrossSearchProductContentModuleFetcher.getSubscribedCrossSearchProductsForUser(CrossSearchProductContentModuleFetcher.java:71)

на com.gale.blis.api.authorize.contentmodulefetchers.CrossSearchProductContentModuleFetcher.getAvailableContentModulesForProduct(CrossSearchProductContentModuleFetcher.java:52)

на com.gale.blis.api.authorize.strategy.productentry.strategy.AbstractProductEntryAuthorizer.getContentModules(AbstractProductEntryAuthorizer.java:130)

на com.gale.blis.api.authorize.strategy.productentry.strategy.CrossSearchProductEntryAuthorizer.isAuthorized(CrossSearchProductEntryAuthorizer. java:82)

на com.gale.blis.api.authorize.strategy.productentry.strategy.CrossSearchProductEntryAuthorizer.authorizeProductEntry(CrossSearchProductEntryAuthorizer.java:44)

на com.gale.blis.api.authorize.strategy.ProductEntryAuthorizer.authorize(ProductEntryAuthorizer.java:31)

в com.gale.blis.api.BLISAuthorizationServiceImpl.authorize_aroundBody0(BLISAuthorizationServiceImpl.java:57)

на com.gale.blis.api.BLISAuthorizationServiceImpl.authorize_aroundBody1$advice(BLISAuthorizationServiceImpl.java:61)

на com.gale.blis.api.BLISAuthorizationServiceImpl.authorize(BLISAuthorizationServiceImpl.java:1)

в com.gale.blis.auth.AuthorizationService._iceD_authorize(AuthorizationService.java:97)

в com.gale.blis.auth.AuthorizationService._iceDispatch(AuthorizationService.java:406)

в com.zeroc.IceInternal.Incoming.invoke(Incoming.java:221)

в com.zeroc.Ice.ConnectionI.invokeAll(ConnectionI.

java:82)

на com.gale.blis.api.authorize.strategy.productentry.strategy.CrossSearchProductEntryAuthorizer.authorizeProductEntry(CrossSearchProductEntryAuthorizer.java:44)

на com.gale.blis.api.authorize.strategy.ProductEntryAuthorizer.authorize(ProductEntryAuthorizer.java:31)

в com.gale.blis.api.BLISAuthorizationServiceImpl.authorize_aroundBody0(BLISAuthorizationServiceImpl.java:57)

на com.gale.blis.api.BLISAuthorizationServiceImpl.authorize_aroundBody1$advice(BLISAuthorizationServiceImpl.java:61)

на com.gale.blis.api.BLISAuthorizationServiceImpl.authorize(BLISAuthorizationServiceImpl.java:1)

в com.gale.blis.auth.AuthorizationService._iceD_authorize(AuthorizationService.java:97)

в com.gale.blis.auth.AuthorizationService._iceDispatch(AuthorizationService.java:406)

в com.zeroc.IceInternal.Incoming.invoke(Incoming.java:221)

в com.zeroc.Ice.ConnectionI.invokeAll(ConnectionI. java:2706)

на com.zeroc.Ice.ConnectionI.dispatch(ConnectionI.java:1292)

в com.zeroc.Ice.ConnectionI.message(ConnectionI.java:1203)

в com.zeroc.IceInternal.ThreadPool.run(ThreadPool.java:412)

в com.zeroc.IceInternal.ThreadPool.access$500(ThreadPool.java:7)

в com.zeroc.IceInternal.ThreadPool$EventHandlerThread.run(ThreadPool.java:781)

в java.base/java.lang.Thread.run(Thread.java:834)

»

org.springframework.remoting.ice.IceClientInterceptor.convertIceAccessException(IceClientInterceptor.java:348)

org.springframework.remoting.ice.IceClientInterceptor.invoke(IceClientInterceptor.java:310)

org.springframework.remoting.ice.MonitoringIceProxyFactoryBean.

java:2706)

на com.zeroc.Ice.ConnectionI.dispatch(ConnectionI.java:1292)

в com.zeroc.Ice.ConnectionI.message(ConnectionI.java:1203)

в com.zeroc.IceInternal.ThreadPool.run(ThreadPool.java:412)

в com.zeroc.IceInternal.ThreadPool.access$500(ThreadPool.java:7)

в com.zeroc.IceInternal.ThreadPool$EventHandlerThread.run(ThreadPool.java:781)

в java.base/java.lang.Thread.run(Thread.java:834)

»

org.springframework.remoting.ice.IceClientInterceptor.convertIceAccessException(IceClientInterceptor.java:348)

org.springframework.remoting.ice.IceClientInterceptor.invoke(IceClientInterceptor.java:310)

org.springframework.remoting.ice.MonitoringIceProxyFactoryBean. invoke(MonitoringIceProxyFactoryBean.java:71)

org.springframework.aop.framework.ReflectiveMethodInvocation.proceed(ReflectiveMethodInvocation.java:186)

org.springframework.aop.framework.JdkDynamicAopProxy.invoke(JdkDynamicAopProxy.java:215)

com.sun.proxy.$Proxy151.authorize(Неизвестный источник)

com.gale.auth.service.BlisService.getAuthorizationResponse(BlisService.java:61)

com.gale.apps.service.impl.MetadataResolverService.resolveMetadata(MetadataResolverService.java:65)

com.gale.apps.

invoke(MonitoringIceProxyFactoryBean.java:71)

org.springframework.aop.framework.ReflectiveMethodInvocation.proceed(ReflectiveMethodInvocation.java:186)

org.springframework.aop.framework.JdkDynamicAopProxy.invoke(JdkDynamicAopProxy.java:215)

com.sun.proxy.$Proxy151.authorize(Неизвестный источник)

com.gale.auth.service.BlisService.getAuthorizationResponse(BlisService.java:61)

com.gale.apps.service.impl.MetadataResolverService.resolveMetadata(MetadataResolverService.java:65)

com.gale.apps. controllers.DiscoveryController.resolveDocument(DiscoveryController.java:57)

com.gale.apps.controllers.DocumentController.redirectToDocument(DocumentController.java:22)

jdk.internal.reflect.GeneratedMethodAccessor309.invoke (неизвестный источник)

java.base/jdk.internal.reflect.DelegatingMethodAccessorImpl.invoke(DelegatingMethodAccessorImpl.java:43)

java.base/java.lang.reflect.Method.invoke(Method.java:566)

org.springframework.web.method.support.InvocableHandlerMethod.doInvoke(InvocableHandlerMethod.java:205)

org.

controllers.DiscoveryController.resolveDocument(DiscoveryController.java:57)

com.gale.apps.controllers.DocumentController.redirectToDocument(DocumentController.java:22)

jdk.internal.reflect.GeneratedMethodAccessor309.invoke (неизвестный источник)

java.base/jdk.internal.reflect.DelegatingMethodAccessorImpl.invoke(DelegatingMethodAccessorImpl.java:43)

java.base/java.lang.reflect.Method.invoke(Method.java:566)

org.springframework.web.method.support.InvocableHandlerMethod.doInvoke(InvocableHandlerMethod.java:205)

org. springframework.web.method.support.InvocableHandlerMethod.invokeForRequest(InvocableHandlerMethod.java:150)

org.springframework.web.servlet.mvc.method.annotation.ServletInvocableHandlerMethod.invokeAndHandle(ServletInvocableHandlerMethod.java:117)

org.springframework.web.servlet.mvc.method.annotation.RequestMappingHandlerAdapter.invokeHandlerMethod (RequestMappingHandlerAdapter.java:895)

org.springframework.web.servlet.mvc.method.annotation.RequestMappingHandlerAdapter.handleInternal (RequestMappingHandlerAdapter.java:808)

org.springframework.web.servlet.mvc.method.AbstractHandlerMethodAdapter.handle(AbstractHandlerMethodAdapter.java:87)

org.

springframework.web.method.support.InvocableHandlerMethod.invokeForRequest(InvocableHandlerMethod.java:150)

org.springframework.web.servlet.mvc.method.annotation.ServletInvocableHandlerMethod.invokeAndHandle(ServletInvocableHandlerMethod.java:117)

org.springframework.web.servlet.mvc.method.annotation.RequestMappingHandlerAdapter.invokeHandlerMethod (RequestMappingHandlerAdapter.java:895)

org.springframework.web.servlet.mvc.method.annotation.RequestMappingHandlerAdapter.handleInternal (RequestMappingHandlerAdapter.java:808)

org.springframework.web.servlet.mvc.method.AbstractHandlerMethodAdapter.handle(AbstractHandlerMethodAdapter.java:87)

org. springframework.web.servlet.DispatcherServlet.doDispatch(DispatcherServlet.java:1067)

org.springframework.web.servlet.DispatcherServlet.doService(DispatcherServlet.java:963)

org.springframework.web.servlet.FrameworkServlet.processRequest(FrameworkServlet.java:1006)

org.springframework.web.servlet.FrameworkServlet.doGet(FrameworkServlet.java:898)

javax.servlet.http.HttpServlet.service(HttpServlet.java:626)

org.springframework.web.servlet.FrameworkServlet.service(FrameworkServlet.java:883)

javax.

springframework.web.servlet.DispatcherServlet.doDispatch(DispatcherServlet.java:1067)

org.springframework.web.servlet.DispatcherServlet.doService(DispatcherServlet.java:963)

org.springframework.web.servlet.FrameworkServlet.processRequest(FrameworkServlet.java:1006)

org.springframework.web.servlet.FrameworkServlet.doGet(FrameworkServlet.java:898)

javax.servlet.http.HttpServlet.service(HttpServlet.java:626)

org.springframework.web.servlet.FrameworkServlet.service(FrameworkServlet.java:883)

javax. servlet.http.HttpServlet.service(HttpServlet.java:733)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:227)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.apache.tomcat.websocket.server.WsFilter.doFilter(WsFilter.java:53)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.

servlet.http.HttpServlet.service(HttpServlet.java:733)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:227)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.apache.tomcat.websocket.server.WsFilter.doFilter(WsFilter.java:53)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org. apache.catalina.filters.HttpHeaderSecurityFilter.doFilter(HttpHeaderSecurityFilter.java:126)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.springframework.web.servlet.resource.ResourceUrlEncodingFilter.doFilter(ResourceUrlEncodingFilter.java:67)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.

apache.catalina.filters.HttpHeaderSecurityFilter.doFilter(HttpHeaderSecurityFilter.java:126)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.springframework.web.servlet.resource.ResourceUrlEncodingFilter.doFilter(ResourceUrlEncodingFilter.java:67)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org. springframework.web.filter.RequestContextFilter.doFilterInternal (RequestContextFilter.java:100)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:102)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.

springframework.web.filter.RequestContextFilter.doFilterInternal (RequestContextFilter.java:100)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:102)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org. apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

com.gale.common.http.filter.SecurityHeaderFilter.doFilterInternal(SecurityHeaderFilter.java:29)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:102)

org.

apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

com.gale.common.http.filter.SecurityHeaderFilter.doFilterInternal(SecurityHeaderFilter.java:29)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:102)

org. apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.owasp.validation.GaleParameterValidationFilter.doFilterInternal(GaleParameterValidationFilter.java:97)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.

apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.owasp.validation.GaleParameterValidationFilter.doFilterInternal(GaleParameterValidationFilter.java:97)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org. springframework.boot.web.servlet.support.ErrorPageFilter.doFilter(ErrorPageFilter.java:126)

org.springframework.boot.web.servlet.support.ErrorPageFilter.access$000(ErrorPageFilter.java:64)

org.springframework.boot.web.servlet.support.ErrorPageFilter$1.doFilterInternal(ErrorPageFilter.java:101)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.springframework.boot.web.servlet.support.ErrorPageFilter.doFilter(ErrorPageFilter.java:119)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.

springframework.boot.web.servlet.support.ErrorPageFilter.doFilter(ErrorPageFilter.java:126)

org.springframework.boot.web.servlet.support.ErrorPageFilter.access$000(ErrorPageFilter.java:64)

org.springframework.boot.web.servlet.support.ErrorPageFilter$1.doFilterInternal(ErrorPageFilter.java:101)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.springframework.boot.web.servlet.support.ErrorPageFilter.doFilter(ErrorPageFilter.java:119)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org. apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.springframework.web.filter.FormContentFilter.doFilterInternal (FormContentFilter.java:93)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.springframework.boot.actuate.metrics.web.servlet.WebMvcMetricsFilter.doFilterInternal (WebMvcMetricsFilter.java:96)

org.

apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.springframework.web.filter.FormContentFilter.doFilterInternal (FormContentFilter.java:93)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.springframework.boot.actuate.metrics.web.servlet.WebMvcMetricsFilter.doFilterInternal (WebMvcMetricsFilter.java:96)

org. springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.springframework.web.filter.CharacterEncodingFilter.doFilterInternal (CharacterEncodingFilter.java:201)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.

springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org.apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.springframework.web.filter.CharacterEncodingFilter.doFilterInternal (CharacterEncodingFilter.java:201)

org.springframework.web.filter.OncePerRequestFilter.doFilter(OncePerRequestFilter.java:117)

org.apache.catalina.core.ApplicationFilterChain.internalDoFilter(ApplicationFilterChain.java:189)

org. apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.apache.catalina.core.StandardWrapperValve.invoke(StandardWrapperValve.java:202)

org.apache.catalina.core.StandardContextValve.invoke(StandardContextValve.java:97)

org.apache.catalina.authenticator.AuthenticatorBase.invoke(AuthenticatorBase.java:542)

org.apache.catalina.core.StandardHostValve.invoke(StandardHostValve.java:143)

org.apache.catalina.valves.ErrorReportValve.invoke(ErrorReportValve.java:92)

org.

apache.catalina.core.ApplicationFilterChain.doFilter(ApplicationFilterChain.java:162)

org.apache.catalina.core.StandardWrapperValve.invoke(StandardWrapperValve.java:202)

org.apache.catalina.core.StandardContextValve.invoke(StandardContextValve.java:97)

org.apache.catalina.authenticator.AuthenticatorBase.invoke(AuthenticatorBase.java:542)

org.apache.catalina.core.StandardHostValve.invoke(StandardHostValve.java:143)

org.apache.catalina.valves.ErrorReportValve.invoke(ErrorReportValve.java:92)

org. apache.catalina.valves.AbstractAccessLogValve.invoke(AbstractAccessLogValve.java:687)

org.apache.catalina.core.StandardEngineValve.invoke(StandardEngineValve.java:78)

org.apache.catalina.connector.CoyoteAdapter.service(CoyoteAdapter.java:357)

org.apache.coyote.http11.Http11Processor.service(Http11Processor.java:374)

org.apache.coyote.AbstractProcessorLight.process(AbstractProcessorLight.java:65)

org.apache.coyote.AbstractProtocol$ConnectionHandler.process(AbstractProtocol.java:893)

org.

apache.catalina.valves.AbstractAccessLogValve.invoke(AbstractAccessLogValve.java:687)

org.apache.catalina.core.StandardEngineValve.invoke(StandardEngineValve.java:78)

org.apache.catalina.connector.CoyoteAdapter.service(CoyoteAdapter.java:357)

org.apache.coyote.http11.Http11Processor.service(Http11Processor.java:374)

org.apache.coyote.AbstractProcessorLight.process(AbstractProcessorLight.java:65)

org.apache.coyote.AbstractProtocol$ConnectionHandler.process(AbstractProtocol.java:893)

org.

Определение реакций опор и моментов защемления

Определение реакций опор и моментов защемления

Потребление тока происходит только в момент переключения КМОП микросхемы из единичного состояния в нулевое и наоборот.

Потребление тока происходит только в момент переключения КМОП микросхемы из единичного состояния в нулевое и наоборот. 3.

3. В этой схеме, так же как и в схеме, приведенной на рисунке 4.1, если транзисторы верхнего плеча будут открыты, то транзисторы нижнего плеча будут закрыты, поэтому в статическом состоянии ток КМОП микросхемой от источника питания потребляться не будет.

В этой схеме, так же как и в схеме, приведенной на рисунке 4.1, если транзисторы верхнего плеча будут открыты, то транзисторы нижнего плеча будут закрыты, поэтому в статическом состоянии ток КМОП микросхемой от источника питания потребляться не будет. Отличие от упрощенной схемы «2ИЛИ», рассмотренной ранее, заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику питания. Вместо резистора в качестве нагрузки используются p-МОП транзисторы. Принципиальная схема логического элемента «2ИЛИ-НЕ», выполненного на комплементарных МОП-транзисторах приведена на рисунке 4.5.

Отличие от упрощенной схемы «2ИЛИ», рассмотренной ранее, заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику питания. Вместо резистора в качестве нагрузки используются p-МОП транзисторы. Принципиальная схема логического элемента «2ИЛИ-НЕ», выполненного на комплементарных МОП-транзисторах приведена на рисунке 4.5.

.18В). При этом при понижении напряжения питания у конкретной микросхемы понижается её предельная частота работы. В дальнейшем, по мере совершенствования технологии производства, появились улучшенные КМОП микросхемы с лучшими частотными свойствами и меньшим напряжением питания, например, SN74HC.

.18В). При этом при понижении напряжения питания у конкретной микросхемы понижается её предельная частота работы. В дальнейшем, по мере совершенствования технологии производства, появились улучшенные КМОП микросхемы с лучшими частотными свойствами и меньшим напряжением питания, например, SN74HC. su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь — 161.97.168.212 (0.004 с.)

su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь — 161.97.168.212 (0.004 с.) Технологии 65 нм для тайкоми

параметры

Таблица 1. Параметры КМОП-технологии 65 нм, используемые для расчетов

Параметры Верте

L, нм 60

[W.sub.n], [микро]м 4 8 16

[W.sub.n]/ л 66,67 133,33 266,67

[COX], мФ/[м2] 12,8

[C.sub.L], fF 10 50 90

[Vtn], мВ 359,5

[Втр], мВ -413,8

[микро]n, [м.суп.]2 / (Vs) 0,0211

[микро]р, [м2] / (Вс) 0,0080

Технологии 65 нм для тайкоми

параметры

Таблица 1. Параметры КМОП-технологии 65 нм, используемые для расчетов

Параметры Верте

L, нм 60

[W.sub.n], [микро]м 4 8 16

[W.sub.n]/ л 66,67 133,33 266,67

[COX], мФ/[м2] 12,8

[C.sub.L], fF 10 50 90

[Vtn], мВ 359,5

[Втр], мВ -413,8

[микро]n, [м.суп.]2 / (Vs) 0,0211

[микро]р, [м2] / (Вс) 0,0080