НОУ ИНТУИТ | Лекция | Реализация логических элементов

Аннотация: Рассматривается различные технологии реализации логических элементов.

Логические элементы транзисторно-транзисторной логики

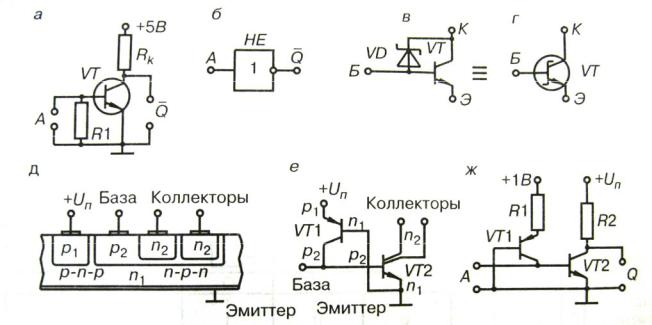

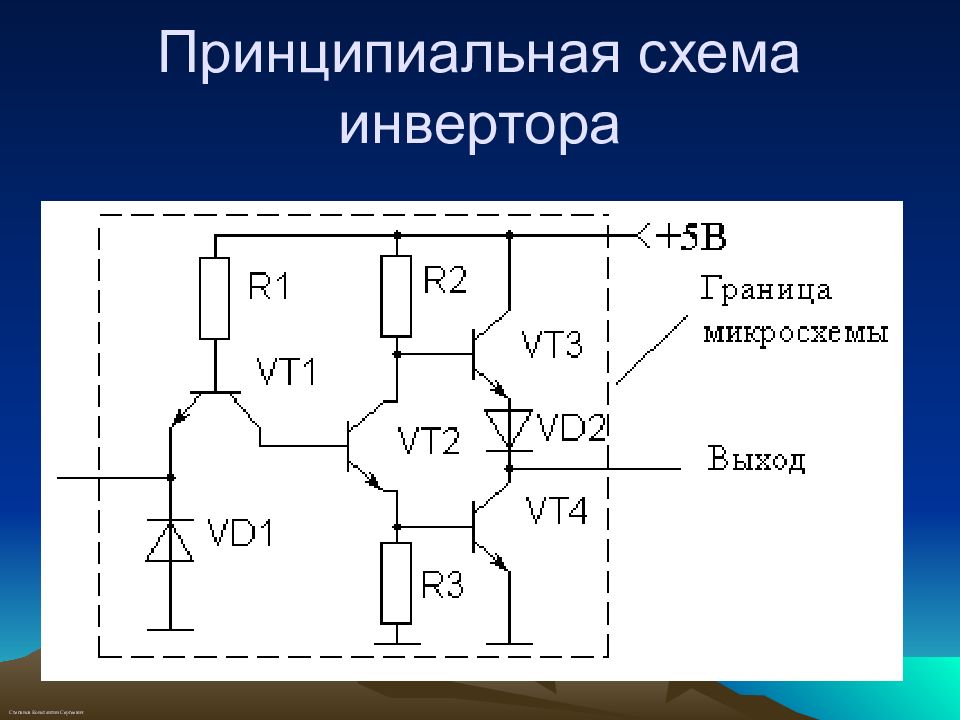

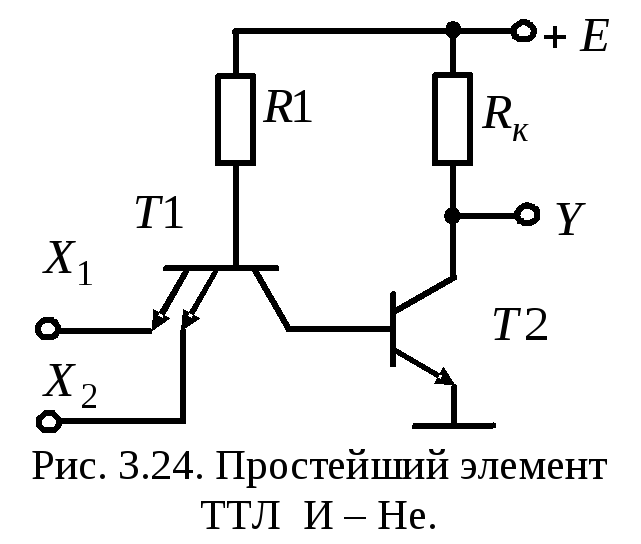

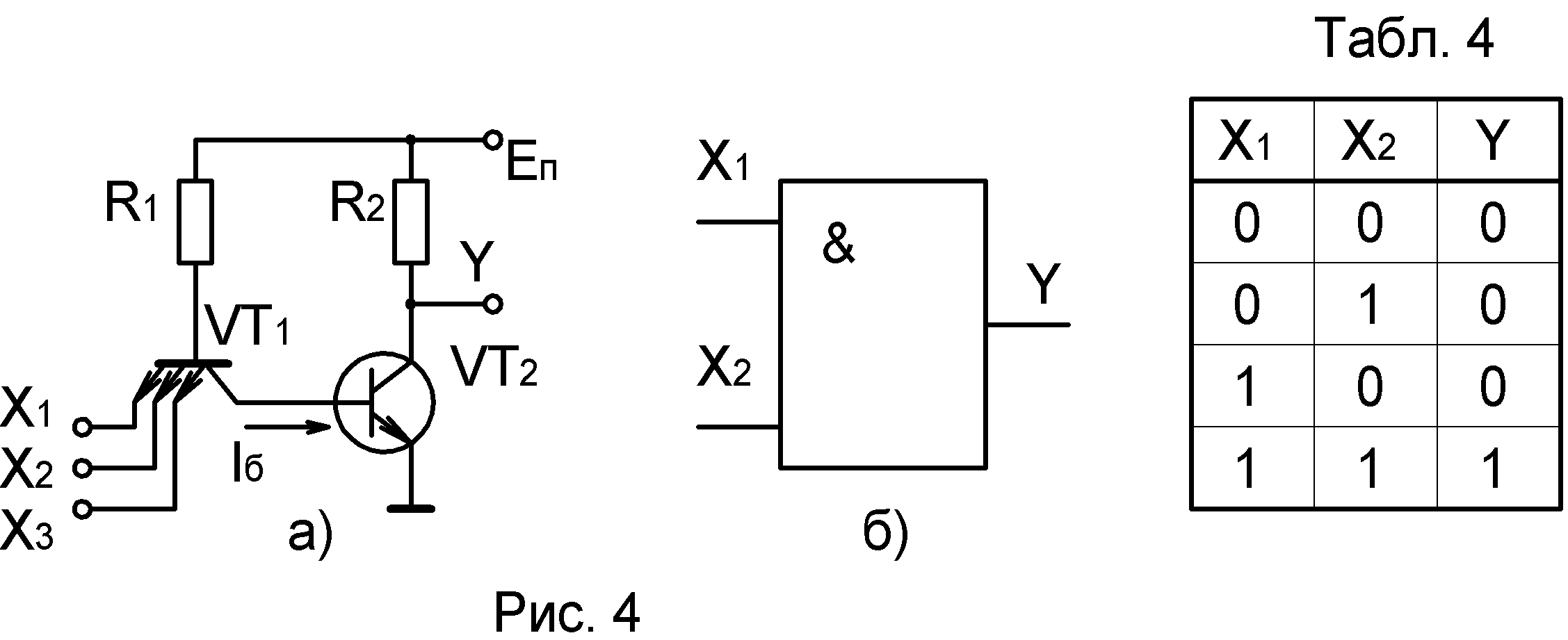

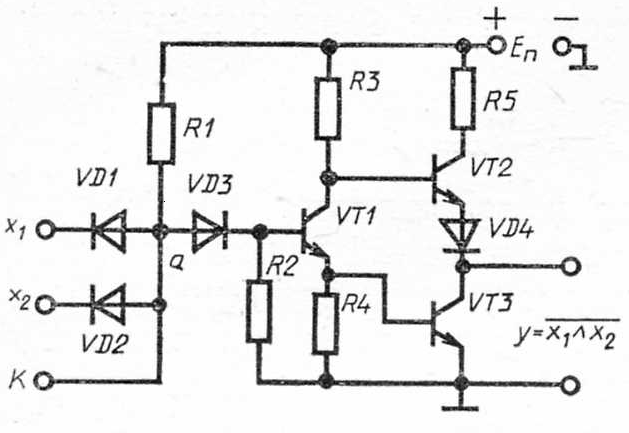

Схемы транзисторно-транзисторной логики (ТТЛ) базируются на биполярных транзисторах npn-структуры. Базовым элементом (рис. 16.1) данной технологии является схема И-НЕ. Логическое умножение осуществляется за счет свойств многоэмиттерного транзистора VT1 [1]. При подаче хотя бы одного логического нуля на эмиттеры этого транзистора замыкается цепь: +5 В, сопротивление R1, переход база-эмиттер, земля на входе. При этом транзисторы VT2 и VT3 остаются закрытыми. Поэтому выходная цепь не замкнута, падения напряжения в ней нет, следовательно, в точке F на выходе схемы будет потенциал источника питания, т.е. логическая единица. Выполняется правило И-НЕ [2]: при подаче хотя бы одного нуля на выходе схемы получили логическую единицу.

Рис.

16.1. Базовый элемент И-НЕ на ТТЛ

16.1. Базовый элемент И-НЕ на ТТЛНа рис. 16.2 представлен логический элемент ИЛИ-НЕ. Логическое сложение осуществляется за счет монтажного соединения транзисторов VT3 и VT4. Замыкание буферной цепи (состояние F=0 ) в этом случае возможно при замыкании хотя бы одной из цепей, проходящих через сопротивления R2 и R3. Эти цепи замыкаются в том случае, если на входы подается хотя бы одна логическая единица.

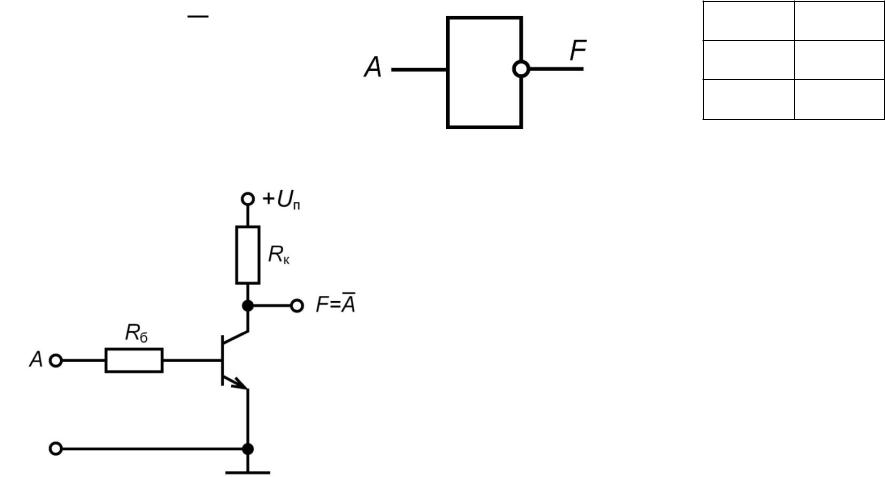

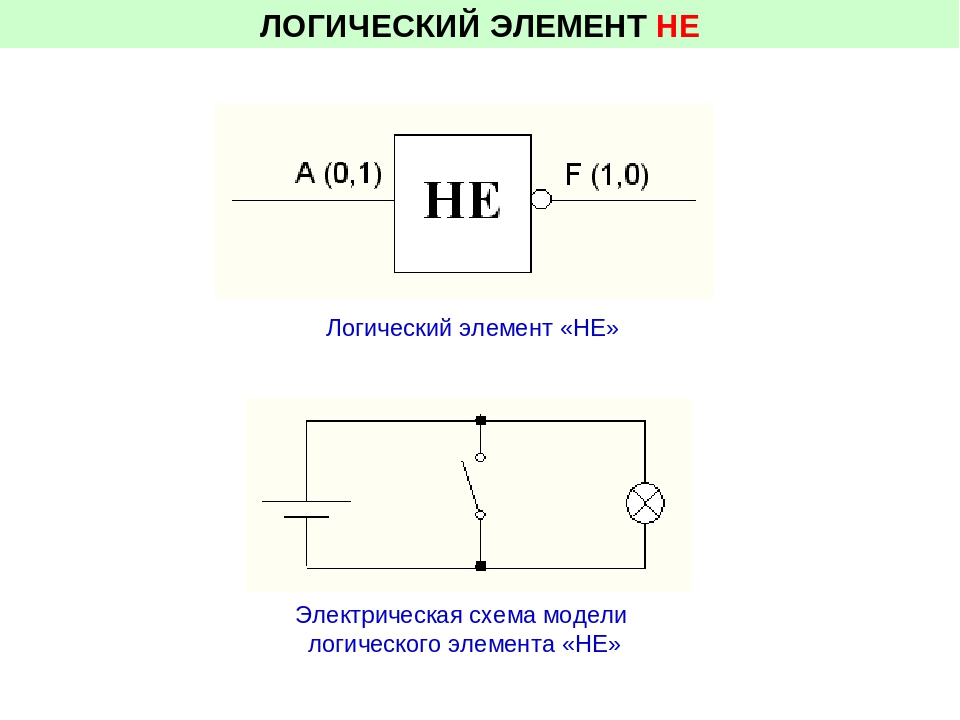

При замене в схеме И-НЕ многоэмиттерного транзистора VT1 на одноэмиттерный получается инвертор (рис. 16.3).

Рис. 16.3.

Буферная часть схем логических элементов ТТЛ-технологии может быть реализована по-разному. В частности, резистор в буферной части может быть вынесен за пределы интегральной схемы, при этом существенно уменьшаются потери и нагрев кристалла. Такие схемы называются схемами «с открытым коллектором «. Пример такой схемы приведен на рис. 16.4.

Рис. 16.4. Базовый элемент И-НЕ на ТТЛ с открытым коллектором

В схемах с активной нагрузкой (рис. 16.5) состояние буферной цепи определяется состоянием не одного, а двух транзисторов.

Рис. 16.5. Базовый элемент И-НЕ на ТТЛ с активной нагрузкой

Буферные схемы на три состояния (первые два – логический 0 и логическая 1 ) имеют помимо информационных, разрешающий вход Е (рис. 16.6). При Е=1 диод VD2 подключен на обратное напряжение, поэтому дополнительная цепь, включающая в себя диод VD2 и вход Е, разомкнута и не влияет на работу логического элемента. Таким образом, осуществляется «разрешение» работы элемента. При отсутствии такового разрешения Е=0. Диод VD2 оказывается подключенным на прямое напряжение, замыкается цепь + 5 В, сопротивление R2, открытый диод VD2, земля на входе E. Следовательно, на базу транзистора VT3 в буферной части схемы подается потенциал, соответствующий падению напряжения на открытом диоде, т.е. 0.2 В. При таких условиях данный транзистор закрыт, поэтому выход F оказывается отключенным от источника питания. Кроме того, независимо от состояния информационных входов A и B, замкнется входная цепь +5 В, сопротивление R1, переход база-эмиттер транзистора VT1, земля на входе E.

Рис. 16.6. Базовый элемент И-НЕ на ТТЛ с выходом на три состояния

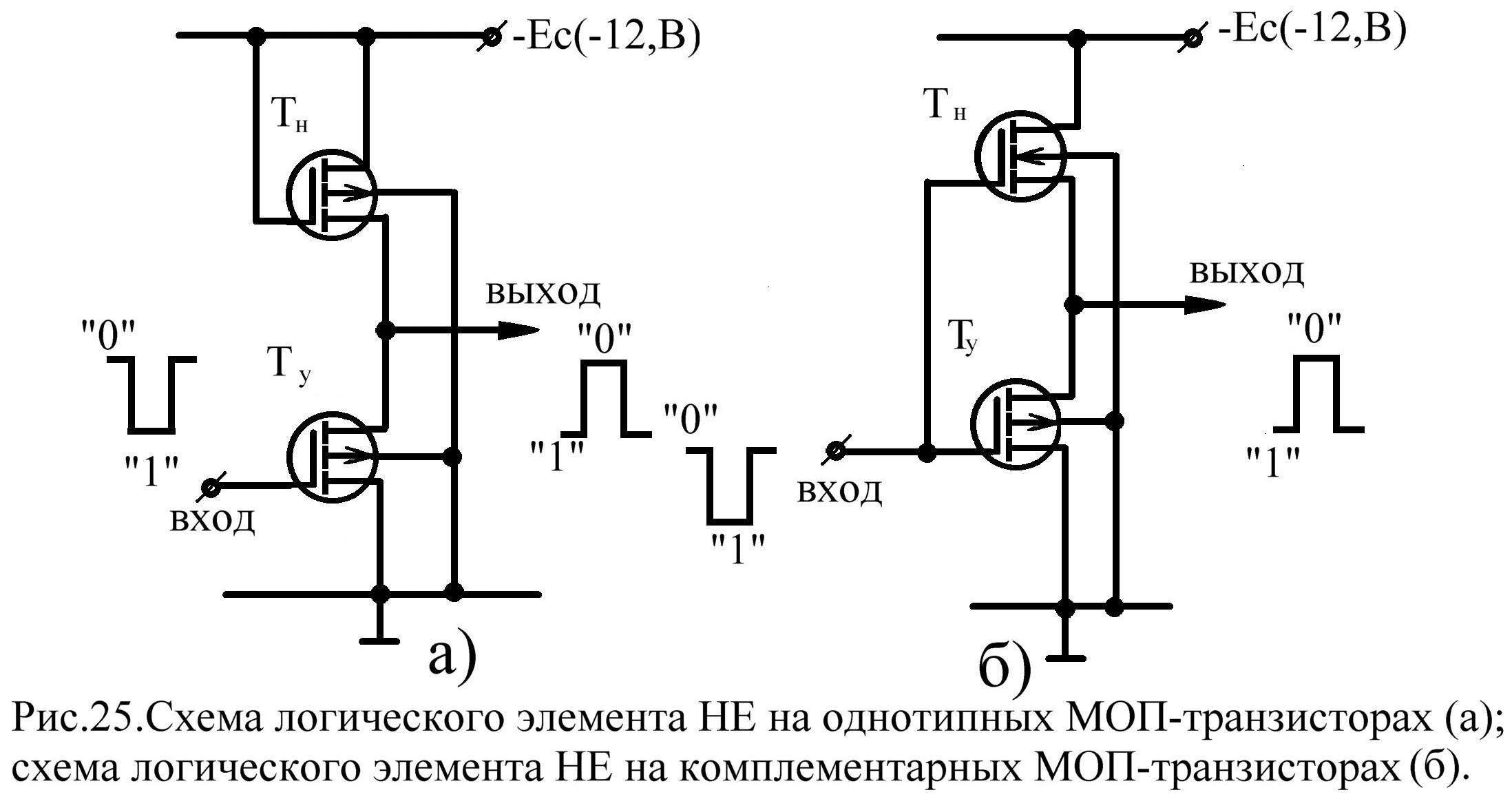

Логические элементы nМОП-технологии

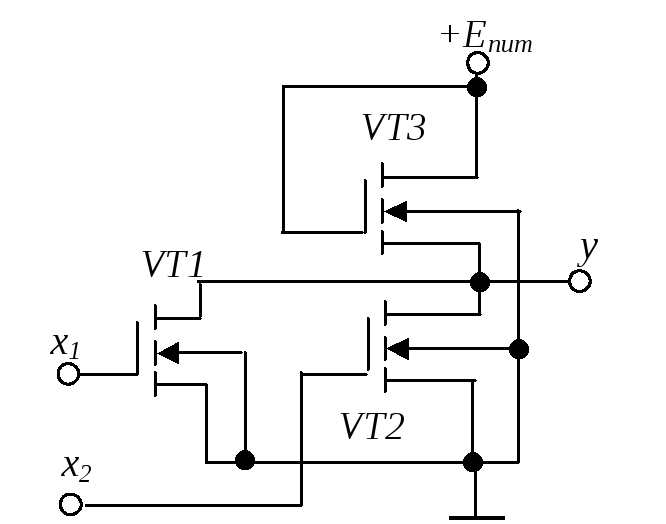

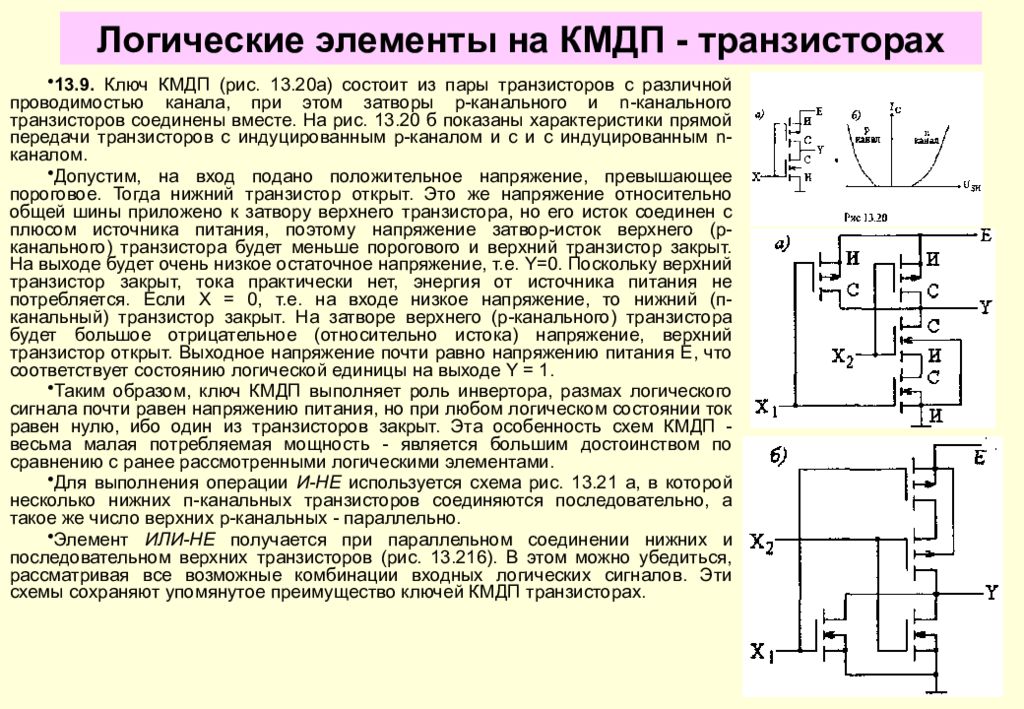

Схемы nМОП-технологии базируются на полевых (МОП) транзисторах с индуцированным каналом n-типа. Базовым элементом (рис. П16.7) данной технологии является схема И-НЕ. Логическое умножение осуществляется за счет последовательного соединения каналов транзисторов VT1 и VT2. Канал между истоком и стоком в nМОП-транзисторе индуцируется в том случае, когда на затвор (вход схемы) подается положительный относительно подложки потенциал.

Рис. 16.7. Логический элемент И-НЕ nМОП-технологии

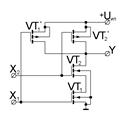

Функция ИЛИ-НЕ осуществляется за счет параллельного соединения таких транзисторов (рис. 16.8): при подаче хотя бы на один вход единицы индуцируется канал в соответствующем транзисторе и замыкается цепь от +5 В до земли. Следовательно, на выходе будет потенциал, соответствующий падению напряжения в канале транзистора, т.е. 0,2 В, при этом F=0.

Рис. 16.8. Логический элемент ИЛИ-НЕ nМОП-технологии

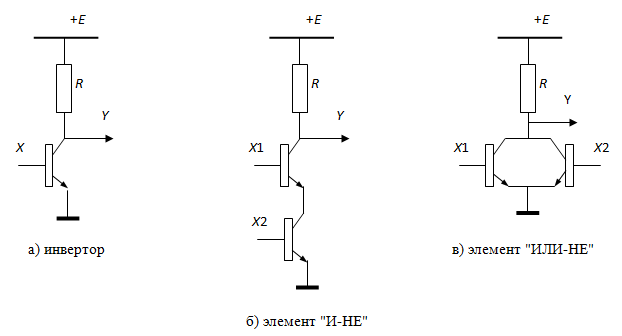

Схема инвертора (рис. 16.9) строится на базе одного транзистора.

Рис. 16.9. Логический элемент НЕ nМОП-технологии

Логические схемы

Логические элементы, включая вентили, счетчики и запоминающие устройства, изготавливаются в виде интегральных модулей, или интегральных схем (ИС).

|

1. |

ИС низкой степени интеграции |

до 10 приборов. |

|

2. |

ИС средней степени интеграции |

10-100 приборов. |

|

3. |

ИС большой степени интеграции, или большие ИС (БИС) |

100-1000 приборов. |

|

4. |

ИС сверхбольшой степени интеграции, или сверхбольшие ИС (СБИС) |

1000-10000 приборов. |

5. |

Ультрабольшие ИС (УБИС) |

10000-100000 приборов. |

Степень интеграции определяет сложность интегральной схемы. Каждое следующее по сложности семейство характеризуется десятикратным увеличением числа элементов по сравнению с предыдущим. К ИС низкой и средней степени интеграции относятся дискретные логические элементы, такие, как вентили, счетчики и регистры. БИС иСБИС используются в качестве запоминающих устройств, микропроцессоров и законченных систем, таких, как микрокомпьютеры.

Логические состояния

Логический элемент имеет два различных состояния: состояние логического 0, представляемое низким уровнем напряжения, обычно 0 В; и состояние логической 1. представляемое высоким уровнем напряжения (положительной полярности в случае

Уровень напряжения, который представляет логическую 1. зависит от используемого типа ИС. Для ИС, изготавливаемых по биполярной технологии, например для ПС ТТ, I (ИС на основе транзисторно-транзисторной логики), логической 1 соответствует напряжение 5 В, в то время как для ИС КМОП (ИС на комплементарных, или дополняющих, МОП-транзисторах) логическая 1 может быть представлена напряжением в диапазоне от 3 до 15 В и выше. ИС ТТЛ имеют преимущество в быстродействии, а ИС КМОП позволяют реализовать более высокую степень интеграции компонентов

Уровень напряжения, который представляет логическую 1. зависит от используемого типа ИС. Для ИС, изготавливаемых по биполярной технологии, например для ПС ТТ, I (ИС на основе транзисторно-транзисторной логики), логической 1 соответствует напряжение 5 В, в то время как для ИС КМОП (ИС на комплементарных, или дополняющих, МОП-транзисторах) логическая 1 может быть представлена напряжением в диапазоне от 3 до 15 В и выше. ИС ТТЛ имеют преимущество в быстродействии, а ИС КМОП позволяют реализовать более высокую степень интеграции компонентов(т. е. позволяют разместить большее число логических элементов в одном интегральном модуле) и не требуют использования стабилизированных источников питания.

Транзисторно-транзисторные логические элементы (ТТЛ)

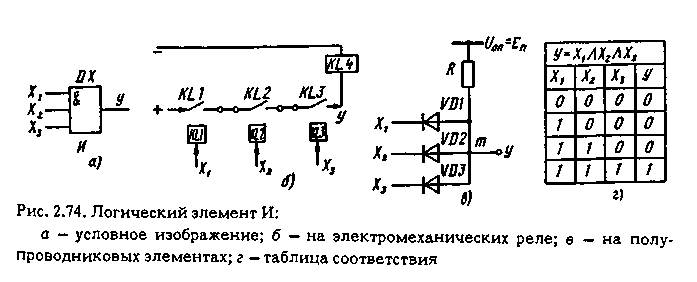

ТТЛ-элементы применяются в интегральных схемах и обеспечивают высокую скорость переключения. На рис. 34.1 показана упрощенная схема логического элемента И-НЕ с многоэмиттерным транзистором T1 на входе. Когда на обоих входах присутствует логический 0, транзистор T1 насыщен и напряжение на его коллекторе близко к 0 В. Следовательно, транзистор T2 находится в состоянии отсечки, и на выходе мыимеем логическую 1. Когда на оба входа подается логическая 1, транзистор T1 закрывается и переключает транзистор T2 в состояние насыщения. В этом случае на выходе элемента мы имеем логический 0.

Когда на обоих входах присутствует логический 0, транзистор T1 насыщен и напряжение на его коллекторе близко к 0 В. Следовательно, транзистор T2 находится в состоянии отсечки, и на выходе мыимеем логическую 1. Когда на оба входа подается логическая 1, транзистор T1 закрывается и переключает транзистор T2 в состояние насыщения. В этом случае на выходе элемента мы имеем логический 0.

Рис. 34.1. Логический элемент И-НЕ (ТТЛ-типа).

Логические элементы на полевых транзисторах

Логические схемы в настоящее время изготавливаются только в виде интегральных схем. Огромное количество логических элементов можно разместить на мельчайшем кристалле (чипе) кремния размером 1х2 мм. В силу своей простоты полевые транзисторы применяются чаще, чем биполярные транзисторы. Наиболее широко распространены логические элементы на основе так называемых КМОП-ячеек (здесь они не рассматриваются). На рис. 34.2 приведена схема логического элемента ИЛИ-НЕ на МОП-транзисторах, который работает на основе отрицательной логики. В этой схеме T1 и T2 — полевые МОП-транзисторы с каналом p-типа (работающие в режиме обогащения). Когда на обоих входах присутствует Уровень логического 0, транзисторы T1 и T2 находятся в состоянии отсечки и на выходе мы имеем логическую 1 (-VDD= -20 В). Когда на один или на оба входа подается логическая 1 (например, -20 В), открываются один или оба транзистора и на выходе мы получаем логический 0.

На рис. 34.2 приведена схема логического элемента ИЛИ-НЕ на МОП-транзисторах, который работает на основе отрицательной логики. В этой схеме T1 и T2 — полевые МОП-транзисторы с каналом p-типа (работающие в режиме обогащения). Когда на обоих входах присутствует Уровень логического 0, транзисторы T1 и T2 находятся в состоянии отсечки и на выходе мы имеем логическую 1 (-VDD= -20 В). Когда на один или на оба входа подается логическая 1 (например, -20 В), открываются один или оба транзистора и на выходе мы получаем логический 0.

Рис. 34.2. Логический элемент Рис. 34.3. Логический элемент на И-НЕ

ИЛИ-НЕ на МОП-транзисторах. МОП-транзисторах.

На рис. 34.3 показана схема логического элемента И-НЕ на основе полевых МОП-транзисторов с каналом п-типа. Поскольку используется источник питания положительной полярности, данный логический элемент работает на основе положительной логики. Транзистор T3 постоянно смещен в активную рабочую область напряжением VDD, подаваемым на затвор, и выполняет функцию активной нагрузки логического элемента. Когда на одном или на обоих входах присутствует логический 0, один или оба транзистора находятся в состоянии отсечки, выдавая логическую 1 на выходе. Ток через транзисторы будет протекать только в том случае, когда на оба входа будет подана логическая 1, и только в этом случае мы получим на выходе логический 0.

Транзистор T3 постоянно смещен в активную рабочую область напряжением VDD, подаваемым на затвор, и выполняет функцию активной нагрузки логического элемента. Когда на одном или на обоих входах присутствует логический 0, один или оба транзистора находятся в состоянии отсечки, выдавая логическую 1 на выходе. Ток через транзисторы будет протекать только в том случае, когда на оба входа будет подана логическая 1, и только в этом случае мы получим на выходе логический 0.

Булевы выражения

Функции, реализуемые отдельным логическим элементом или комбинацией логических элементов, могут быть выражены логическими формулами, называемыми булевыми выражениями. В булевой алгебре используются следующие обозначения логических функций (см. табл. 34.1):

• Функция И обозначается символом точки (·). Двухвходовый (входы А и В) логический элемент И вырабатывает на выходе сигнал, представляемый булевым выражением А · В.

• Функция ИЛИ обозначается символом (+). Двухвходовый логический элемент ИЛИ вырабатывает на выходе сигнал, представляемый булевым выражением А + В.

Двухвходовый логический элемент ИЛИ вырабатывает на выходе сигнал, представляемый булевым выражением А + В.

Таблица 34.1. Булевы выражения

|

Функция |

Обозначение в булевой алгебре |

|

И |

А·В |

|

или |

А+В

|

|

НЕ |

|

|

И-НЕ |

|

|

ИЛИ-НЕ |

|

|

Исключающее ИЛИ |

|

|

Исключающее ИЛИ-НЕ |

• Логическая функция НЕ обозначается символом черты над обозначением входного сигнала. Логическая схема НЕ с одним входом А вырабатывает на выходе сигнал, представляемый булевым выражением (читается «НЕ А»).

Логическая схема НЕ с одним входом А вырабатывает на выходе сигнал, представляемый булевым выражением (читается «НЕ А»).

Через эти простые функции можно выразить более сложные:

• Функция Н-НЕ записывается как .

• Функция ИЛИ-НЕ записывается как .

• Функция Исключающее ИЛИ записывается как . Ее можно также записать, используя специальное обозначение, .

• Функция Исключающее ИЛИ-НЕ записывается как . Ее можно также записать, используя специальное обозначение, .

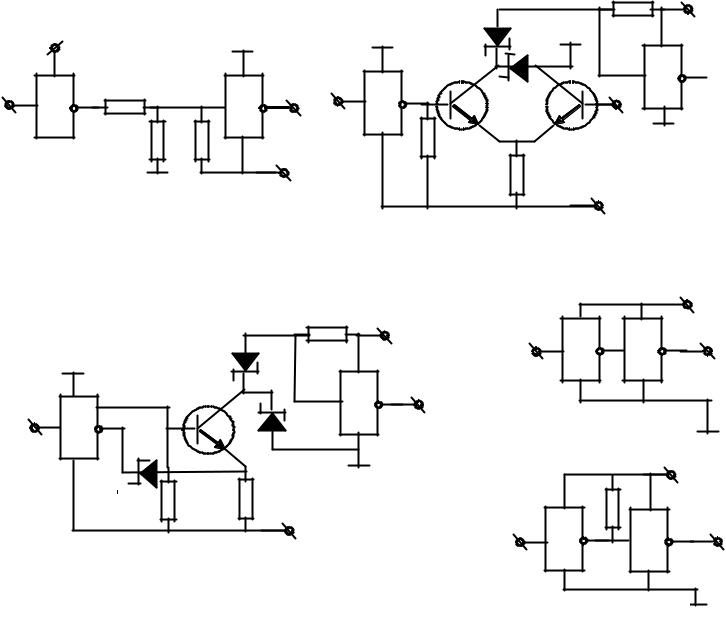

Комбинаторная логика

Рассмотрим логическую схему на рис. 34.4. Логическую функцию, выполняемую этой схемой, можно описать с помощью следующих булевых выражений.

Выходной сигнал логического элемента ИЛИ (i): A + В

Выходной сигнал логического элемента И-ИЕ (ii):

Выходной сигнал логического элемента ИЛИ (iii): (А + В) +

Пример 1

Обратимся к рис. 34.5.

34.5.

а) Найдите булево выражение для логической функции изображенной комбинации логических элементов.

б) Составьте таблицу истинности, показывающую логические состояния во всех точках схемы, и докажите, что эту схему можно свести к одному логическому элементу.

Решение

а) Булево выражение для точки С = .

Булево выражение для точки D= .

Булево выражение для точки F = ·.

б) Таблица истинности

|

Входы |

Точки |

Выход |

||

|

А

|

В

|

С

|

D

|

F

|

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

Как видно из таблицы истинности, приведенная комбинация логических элементов эквивалентна логическому элементу ИЛИ-НЕ.

Пример 2

Обратимся к рис. 34.6.

а) Найдите булево выражение для логической функции изображенной комбинации логических элементов.

б) Составьте таблицу истинности, показывающую логические состояния во всех точках схемы, и докажите, что эту схему можно свести к одному логическому элементу.

Решение

а) Булево выражение для точки С = .

Булево выражение для точки D = .

Булево выражение для точки F = +.

6) Таблица истинности

|

Входы |

Точки |

Выход |

||

|

А

|

В

|

С

|

D

|

F

|

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

0 |

Как видно из таблицы истинности, приведенная комбинация логических элементов эквивалентна логическому элементу И-НЕ.

Счетчики

Функцию счета в двоичном счетчике выполняет бистабильный мультивибратор, или делитель на 2, чаще называемый триггером. Цепочка из нескольких таких триггеров образует счетчик. На рис. 34.7 показан двоичный счетчик, состоящий из трех триггеров. Каждый триггер делит частоту поступающих импульсов на 2. Таким образом, два последовательных триггера обеспечивают деление на 4 (2 · 2), а три триггера – на 8 (2 · 2 · 2). Другими словами, на каждые восемь входных импульсов на выходе А появятся четыре импульса, на выходе В — два импульса и на выходе С — один импульс (рис. 34.7).

Как уже говорилось в гл. 32, бистабильный мультивибратор изменяет свое состояние только во время действия одного из фронтов входного импульса. Уровень входного импульса изменяется от 0 к 1 и обратно к 0, и так для каждого приходящего импульса. Обычно предполагается, что состояние триггера изменяется при приходе отрицательного фронта импульса (т. е. при переходе от 1 к 0).

Сигнал на выходе QА триггера А соответствует 20, или столбцу «единиц» в табл. 34.2, сигнал на выходе QB— 21, или столбцу «двоек», и наконец, сигнал на выходе QC — 22, или столбцу «четверок». После поступления 6 импульсов на вход счетчика он оказывается в следующем состоянии: А (число единиц) = 0, В (число двоек) = 1. С (число четверок) = 1; это состояние соответствует десятичному числу 6 (0 + 2 + 4).

Рис. 34.7. Двоичный счетчик на трех триггерах.

Таблица 34.2

|

Импульс |

QА единицы (20) |

QB двойки (21) |

QC четверки (22) |

|

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

|

2 |

0 |

1 |

0 |

|

3 |

1 |

1 |

0 |

|

4 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

|

7 |

1 |

1 |

1 |

|

8 |

0 |

0 |

0 |

В двоичном исчислении это число записывается как 110 при порядке следования двоичных разрядов СВА. Обратите внимание, что в счетчике двоичному разряду единиц соответствует выход первого триггера, начиная от входа счетчика, а в двоичном числе разряд единиц всегда является самым правым разрядом.

Обратите внимание, что в счетчике двоичному разряду единиц соответствует выход первого триггера, начиная от входа счетчика, а в двоичном числе разряд единиц всегда является самым правым разрядом.

Когда приходит седьмой импульс, на всех выходах счетчика устанавливается 1. Восьмой импульс сбрасывает все триггеры в 0. Еще раз отметим, что выходной сигнал каждого триггера представляет столбец в таблице двоичного кода. Сам двоичный код записывается в порядке СВА.

Обратная связь

Обратная связь вводится в двоичных счетчиках для изменения коэффициента деления частоты входного сигнала. Для примера рассмотрим действие обратной связи в счетчике на рис. 34.8(а), состоящем из трех триггеров. Процесс счета происходит обычным образом до прихода третьего импульса, когда счетчик находится в состоянии 011 (см. табл. 34.3).

Рис. 34.8. (а) Счетчик-делитель на 6 с обратной связью, охватывающей триггеры В и С.

(б) Замена петли обратной связи эквивалентным модулем деления на 3.

Таблица 34.3

|

Импульс |

QА |

QB |

QC |

|

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

|

2 |

0 |

1 |

0 |

|

3 |

1 |

1 |

0 |

|

Обратная связь |

(0) |

(0) |

(1) |

|

4 |

0 |

1 |

1 |

|

5 |

1 |

1 |

1 |

|

6 |

0 |

0 |

0 |

Четвертый импульс переключает сигнал на выходах А и В к 0 и на выходе С к 1. В отсутствие обратной связи счетчик переключился бы в состояние 100. Однако при включении обратной связи изменение сигнала на выходе С передается на вход триггера В, возвращая его выходной сигнал обратно к 1. Счетчик окажется в состоянии 110. Пятый импульс переключит все выходы к 1, и шестой импульс сбросит все триггеры в 0, т. е. получился счетчик-делитель на 6.

В отсутствие обратной связи счетчик переключился бы в состояние 100. Однако при включении обратной связи изменение сигнала на выходе С передается на вход триггера В, возвращая его выходной сигнал обратно к 1. Счетчик окажется в состоянии 110. Пятый импульс переключит все выходы к 1, и шестой импульс сбросит все триггеры в 0, т. е. получился счетчик-делитель на 6.

Вообще, можно показать, что петля обратной связи уменьшает коэффициент деления триггеров внутри петли на 1. В предыдущем примере внутри петли обратной связи находились триггеры В и С. Без обратной связи они осуществляли деление на 4. С обратной связью триггеры В и С образуют блок деления на 3 (= 4 – 1), как показано на рис. 34.8(б). С учетом триггера А вне петли обратной связи полный коэффициент деления счетчика равен 6 (= 2 · 3).

Десятичный счетчик

На рис. 34.9(а) изображена схема десятичного счетчика с двумя петлями обратной связи. Обратной связью охвачены : 1) блок 1, включающий триггеры С и D и обеспечивающий деление на 3 (= 4 – 1), и 2) блок 2, включающий блок 1 и триггер В. Из рис. 34.9(б) видно, что без обратной связи блок 2 делил бы на 6 (= 2 · 3). С обратной связью его коэффициент деления равен 5 (= 6 – 1). С учетом триггера А, не охваченного обратной связью, полный коэффициент деления счетчика равен 10 (= 2 · 5).

Из рис. 34.9(б) видно, что без обратной связи блок 2 делил бы на 6 (= 2 · 3). С обратной связью его коэффициент деления равен 5 (= 6 – 1). С учетом триггера А, не охваченного обратной связью, полный коэффициент деления счетчика равен 10 (= 2 · 5).

Регистр сдвига

Для передачи данных из одной части системы, например компьютера, в другую можно использовать два метода. Первый, более быстрый, заключается в одновременной передаче всех разрядов. При этом для передачи восьми разрядов требуется восемь отдельных линий. Для передачи информации на расстояния в несколько метров этот метод вполне пригоден, но при передаче на большие расстояния, например между городами, он становится слишком дорогим. В этом случае применяется второй, более медленный метод: данные передаются последовательно разряд за разрядом по одному проводу. Для одновременного сдвига всех двоичных разрядов влево или вправо применяется регистр сдвига. Он состоит из нескольких триггеров, способных передвигать двоичные разряды в последовательном порядке.

Рис. 34.9. Десятичный счетчик (а) и его представление в виде эквивалентных модулей (б).

Кольцевой счетчик

Кольцевой счетчик — это обычный счетчик, составленный из нескольких триггеров, в котором выходной сигнал подается обратно на вход, отсюда и происходит его название. Импульсы циркулируют по счетчику от входа к выходу и обратно на вход. В конце каждого цикла выходной сигнал кольцевого счетчика можно снять для переключения другого счетчика. Например, выходной сигнал десятичного, или декадного, счетчика можно использовать для переключения еще одного декадного счетчика, обеспечивая тем самым коэффициент пересчета, равный 100.

Фиксатор (триггер-защелка)

В гл. 32 рассматривались бистабильные мультивибраторы, или триггеры, построенные на дискретных компонентах. Триггеры — очень важные и нужные базовые элементы логических устройств. Они применяются в качестве делителей на 2, фиксаторов (одноразрядные ячейки памяти) и для других целей.

Базовый триггер, называемый RS-триггером, или триггером-защелкой, показан на рис. 34.10. Два выходных сигнала, снимаемые с выходов Q и (НЕ Q), находятся в противофазе друг к другу. Если Q = 1, то = 0, и наоборот. Таблица истинности для RS-триггера приведена на рис. 34.10(в). При подаче логической 1 на вход R (Reset — сброс) на выходе Q устанавливается уровень логического 0 (и уровень логической 1 на выходе ), при подаче логической 1 на вход S (Set — установка) на выходе Q устанавливается уровень логической 1 (и уровень логического 0 на выходе ).

|

S |

R |

|

|

0 |

0 |

Без изменений |

|

0 |

1 |

|

|

1 |

0 |

|

|

1 |

1 |

Неопределенное состояние |

(в)

Более сложным устройством по сравнению с простым RS-триггером является тактируемый JK-триггер, в котором имеется тактовый вход и отсутствует неопределенное состояние (рис. 34.11). Тактовый вход важен для синхронных систем, в которых переключение триггеров происходит лишь тогда, когда на тактовый вход подается логическая 1. При установке логической 1 на обоих входах J и К триггера его выход переключается из уровня логического 0 в логическую 1 при поступлении каждого тактового импульса.

34.11). Тактовый вход важен для синхронных систем, в которых переключение триггеров происходит лишь тогда, когда на тактовый вход подается логическая 1. При установке логической 1 на обоих входах J и К триггера его выход переключается из уровня логического 0 в логическую 1 при поступлении каждого тактового импульса.

|

Тактовый вход |

J

|

К

|

|

|

0 |

X |

X |

Без изменений |

|

1 |

0 |

0 |

Без изменений |

|

1 |

0 |

1 |

|

|

1 |

1 |

0 |

|

|

1 |

1 |

1 |

Переключение |

(а) (б)

Рис. 34.11. Условное обозначение (а) и таблица истинности (б) JK-триггера.

34.11. Условное обозначение (а) и таблица истинности (б) JK-триггера.

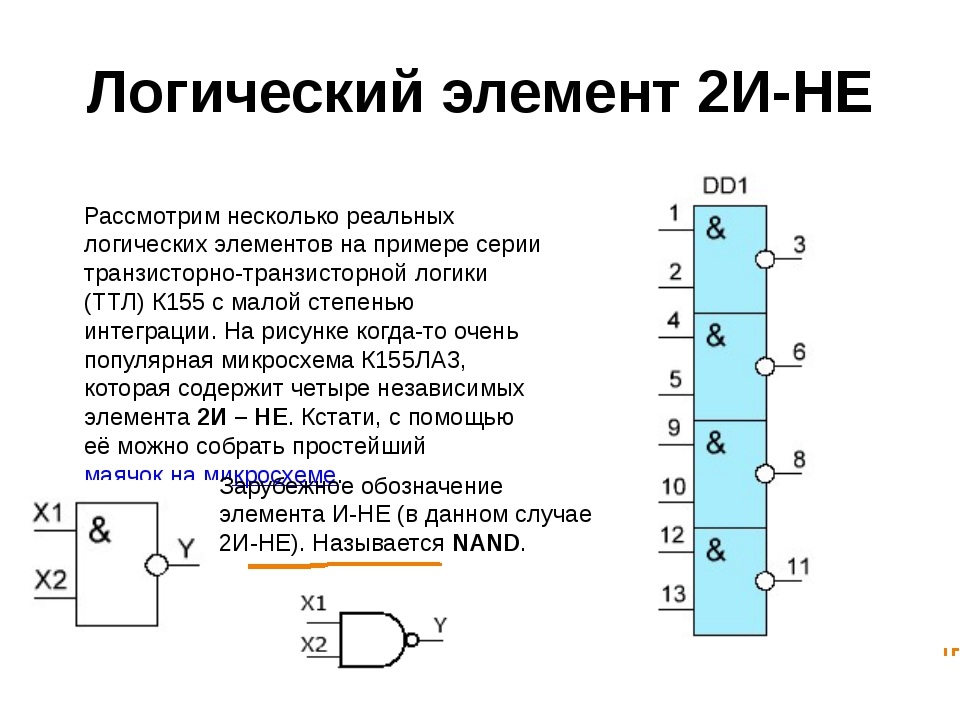

Логические элементы в виде ИС

Логические элементы изготавливаются в виде интегральных схем и выпускаются в виде модулей, содержащих большое число идентичных элементов на одном модуле (чипе). Известны два основных типа ИС: ИС ТТЛ и ИС КМОП. Примеры ИС ТТЛ приведены на рис. 34.12.

Рис. 34.12.

В этом видео рассказывается о элементах транзисторно-транзисторной логики:

Добавить комментарий

Элементы транзисторных логик: схемы, ТТЛ, ТТЛШ, КМОП

Для конкретной серии микросхем характерно использование типового электронного узла — базового логического элемента. Этот элемент является основой построения самых разнообразных цифровых электронных устройств.

Этот элемент является основой построения самых разнообразных цифровых электронных устройств.

Ниже рассмотрим особенности базовых логических элементов различных логик.

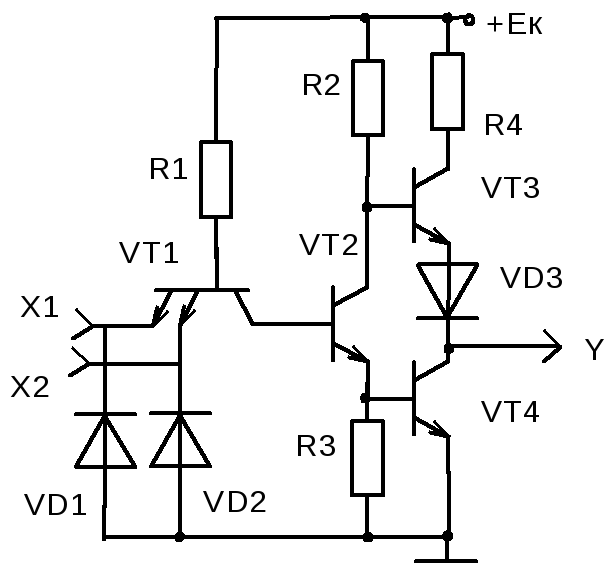

Элементы транзисторно-транзисторной логики

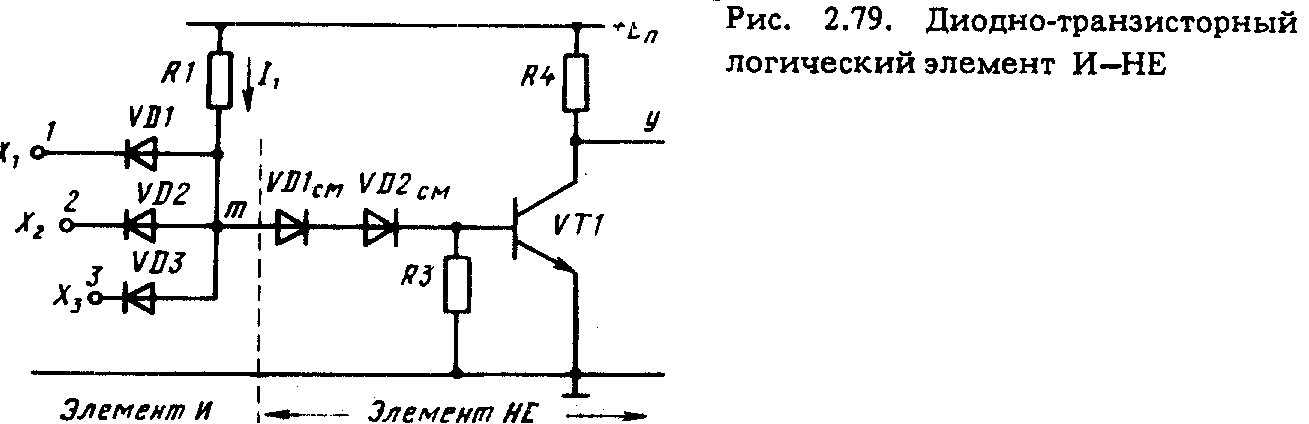

Характерной особенностью ТТЛ является использование многоэмиттерных транзисторов. Эти транзисторы сконструированы таким образом, что отдельные эмиттеры не оказывают влияния друг на друга. Каждому эмиттеру соответствует свой p-n-переход. В первом приближении многоэмиттерный транзисторможет моделироваться схемой на диодах (см. пунктир на рис. 3.27).

Васильев Дмитрий Петрович

Профессор электротехники СПбГПУ

Задать вопрос

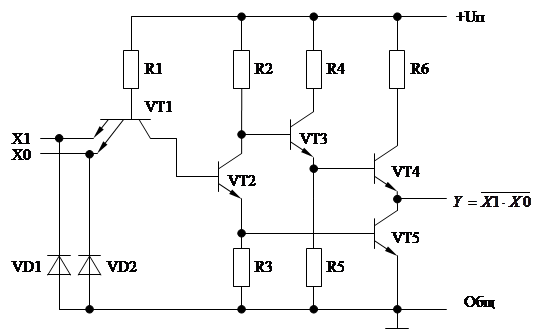

Упрощенная схема ТТЛ-элемента приведена на рис. 3.27. При мысленной замене многоэмиттерного транзистора диодами получаем элемент диодно-транзисторной логики «И-НЕ». Из анализа схемы можно сделать вывод, что если на один из входов или на оба входа подать низкий уровень напряжения, то ток базы транзистора Т2 будет равен нулю, и на коллекторе транзистора Т2 будет высокий уровень напряжения.

Если на оба входа подать высокий уровень напряжения, то через базу Т2 транзистора будет протекать большой базовый ток и на коллекторе транзистора Т2 будет низкий уровень напряжения, т. е. данный элемент реализует функцию И-НЕ:

uвых= u1· u2. Базовый элемент ТТЛ содержит многоэмиттерный транзистор, выполняющий логическую операцию И, и сложный инвертор (рис. 3.28).

Если на один или оба входа одновременно подан низкий уровень напряжения, то многоэмиттерный транзистор находится в состоянии насыщения и транзистор Т2 закрыт, а следовательно, закрыт и транзистор Т4, т. е. на выходе будет высокий уровень напряжения.

Васильев Дмитрий Петрович

Профессор электротехники СПбГПУ

Задать вопрос

Если на обоих входах одновременно действует высокий уровень напряжения, то транзистор Т2 открывается и входит в режим насыщения, что приводит к открытию и насыщению транзистора Т4 и запиранию транзистора Т3, т. е. реализуется функция И-НЕ.

е. реализуется функция И-НЕ.

Для увеличения быстродействия элементов ТТЛ используются транзисторы с диодами Шоттки (транзисторы Шоттки).

Логические элементы ТТЛШ (на примере серии К555)

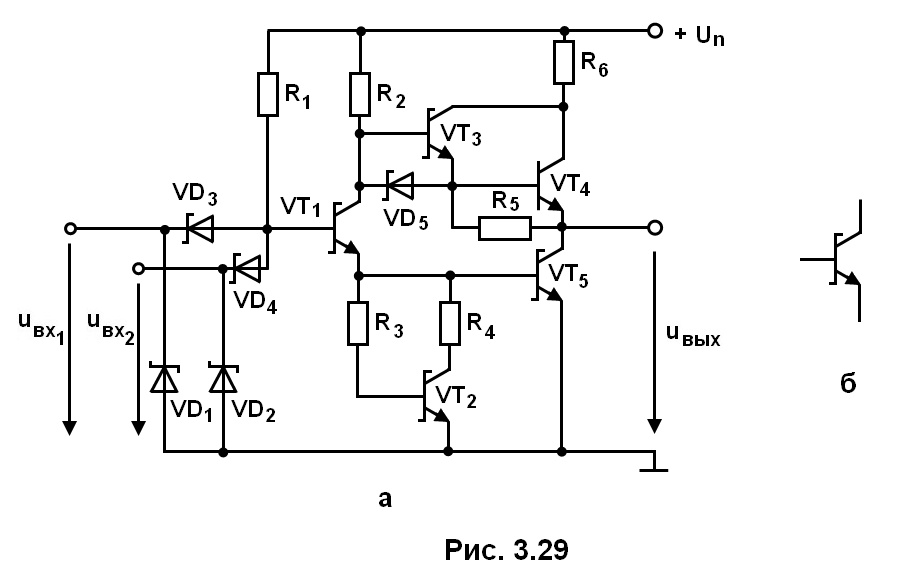

В качестве базового элемента серии микросхем К555 использован элемент И-НЕ. На рис. 3.29, а изображена схема этого элемента, а условное графическое обозначение транзистора Шоттки приведено на рис. 3.29, б.

Такой транзистор эквивалентен рассмотренной выше паре из обычного транзистора и диода Шоттки. ТранзисторVT4 — обычный биполярный транзистор.

Если оба входных напряжения uвх1и uвх2 имеют высокий уровень, то диодыVD3 и VD4 закрыты, транзисторы VT1,VT5 открыты и на выходе имеет место напряжение низкого уровня. Если хотя бы на одном входе имеется напряжение низкого уровня, то транзисторы VT1 и VT5 закрыты, а транзисторы VT3 и VT4 открыты, и на входе имеет место напряжение низкого уровня. Полезно отметить, что транзисторы VT3 и VT4 образуют так называемый составной транзистор (схему Дарлингтона).

Полезно отметить, что транзисторы VT3 и VT4 образуют так называемый составной транзистор (схему Дарлингтона).

Микросхемы ТТЛШ

Микросхемы ТТЛШ серии К555 характеризуются следующими параметрами:

- напряжение питания +5 В;

- выходное напряжение низкого уровня — не более 0,4 В;

- выходное напряжение высокого уровня — не менее 2,5 В;

- помехоустойчивость — не менее 0,3 В;

- среднее время задержки распространения сигнала — 20 нс;

- максимальная рабочая частота — 25 МГц.

Васильев Дмитрий Петрович

Профессор электротехники СПбГПУ

Задать вопрос

Микросхемы ТТЛШ обычно совместимы по логическим уровням, помехоустойчивости и напряжению питания с микросхемами ТТЛ. Время задержки распространения сигнала элементов ТТЛШ в среднем в два раза меньше по сравнению с аналогичными элементами ТТЛ.

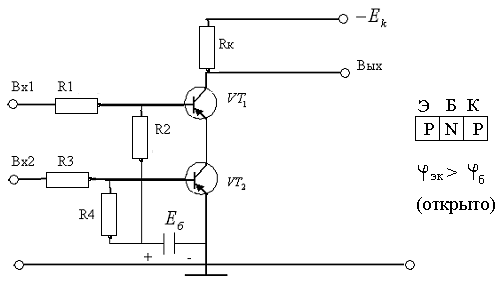

Особенности других логик

Основой базового логического элемента ЭСЛ является токовый ключ. Схема токового ключа (рис. 3.30) подобна схеме дифференциального усилителя.

Схема токового ключа (рис. 3.30) подобна схеме дифференциального усилителя.

Необходимо обратить внимание на то, что микросхемы ЭСЛ питаются отрицательным напряжением (к примеру, −4,5 В для серии К1500). На базу транзистора VT2 подано отрицательное постоянное опорное напряжение Uоп. Изменение входного напряжения uвх1 приводит к перераспределению постоянного тока iэ0, заданного сопротивлением Rэ между транзисторами, что имеет следствием изменение напряжений на их коллекторах.

Транзисторы не входят в режим насыщения, и это является одной из причин высокого быстродействия элементов ЭСЛ.

Микросхемы серий 100, 500 имеют следующие параметры:

- напряжение питания −5,2 В;

- потребляемая мощность — 100 мВт;

- коэффициент разветвления по выходу — 15;

- задержка распространения сигнала — 2,9 нс.

В микросхемах n-МОП и p-МОП используются ключи соответственно на МОП-транзисторах с n-каналом и динамической нагрузкой (рассмотрены выше) и на МОП-транзисторах с p-каналом.

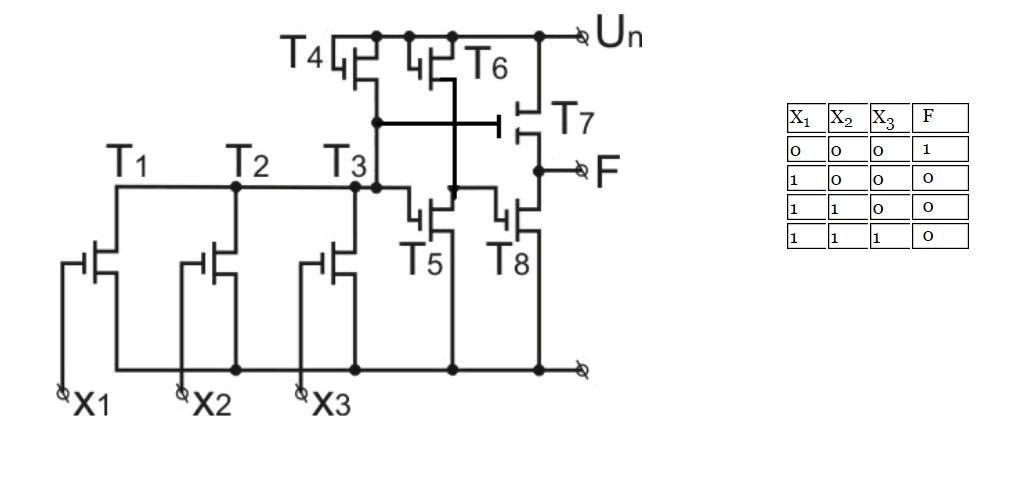

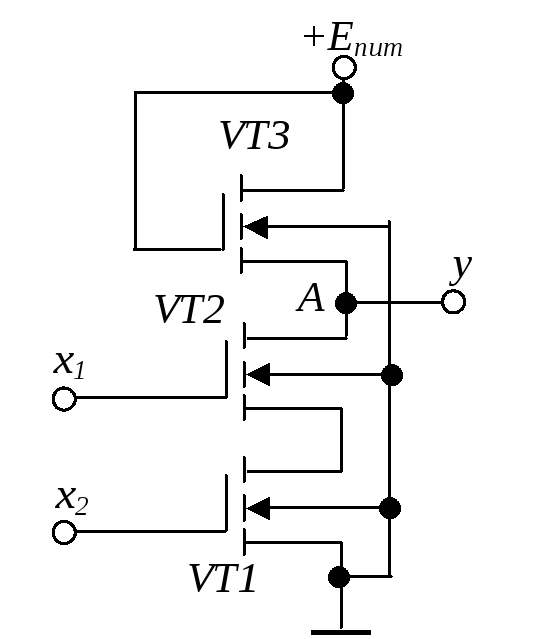

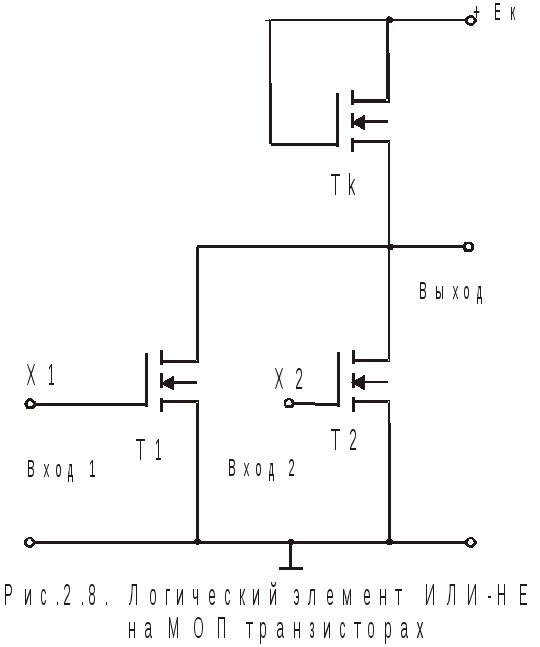

В качестве примера рассмотрим элемент логики n-МОП, реализующий функцию ИЛИ-НЕ (рис. 3.31).

Он состоит из нагрузочного транзистора Т3 и двух управляющих транзисторов Т1 и Т2. Если оба транзистора Т1 и Т2 закрыты, то на выходе устанавливается высокий уровень напряжения. Если одно или оба напряжения u1и u2 имеют высокий уровень, то открывается один или оба транзистора Т1 и Т2 и на выходе устанавливается низкий уровень напряжения, т. е. реализуется функция uвых= u1 + u2.

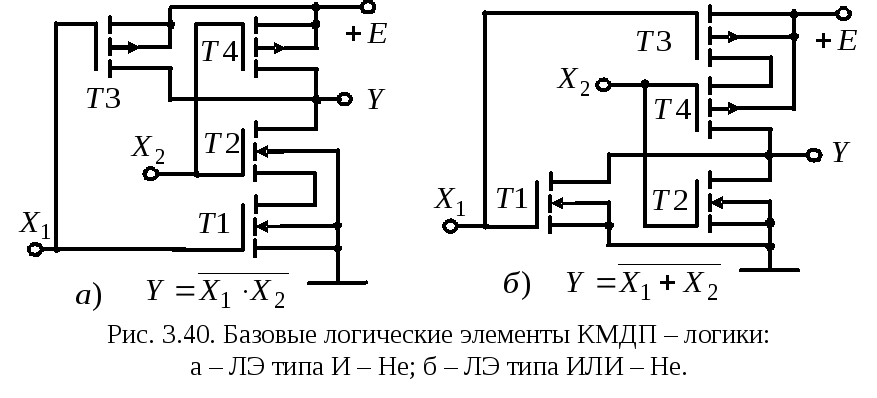

Для исключения потребления мощности логическим элементом в статическом состоянии используются комплементарные МДП — логические элементы (КМДП или КМОП-логика). В микросхемах КМОП используются комплементарные ключи на МОП-транзисторах. Они отличаются высокой помехоустойчивостью. Логика КМОП является очень перспективной. Рассмотренный ранее комплементарный ключ фактически является элементом НЕ (инвертором).

КМОП — логический элемент

Рассмотрим КМОП — логический элемент, реализующий функцию ИЛИ-НЕ (рис. 3.32).

Абрамян Евгений Павлович

Доцент кафедры электротехники СПбГПУ

Задать вопрос

Если входные напряжения имеют низкие уровни (u1и u2меньше порогового напряжения n-МОП-транзистора Uзи.порог.n), то транзисторы Т1 и Т2 закрыты, транзисторы Т3 и Т4 открыты и выходное напряжение имеет высокий уровень.

Если одно или оба входных напряжения u1и u2 имеют высокий уровень, превышающий Uзи.порог.n, то открывается один или оба транзистора Т1 и Т2, а между истоком и затвором одного или обоих транзисторов Т3 и Т4 устанавливается низкое напряжение, что приводит к запиранию одного или обоих транзисторов Т3 и Т4, а следовательно, на выходе устанавливается низкое напряжение.

Таким образом, этот элемент реализует функцию uвых= u1+u2 и потребляет мощность от источника питания лишь в короткие промежутки времени, когда происходит его переключение.

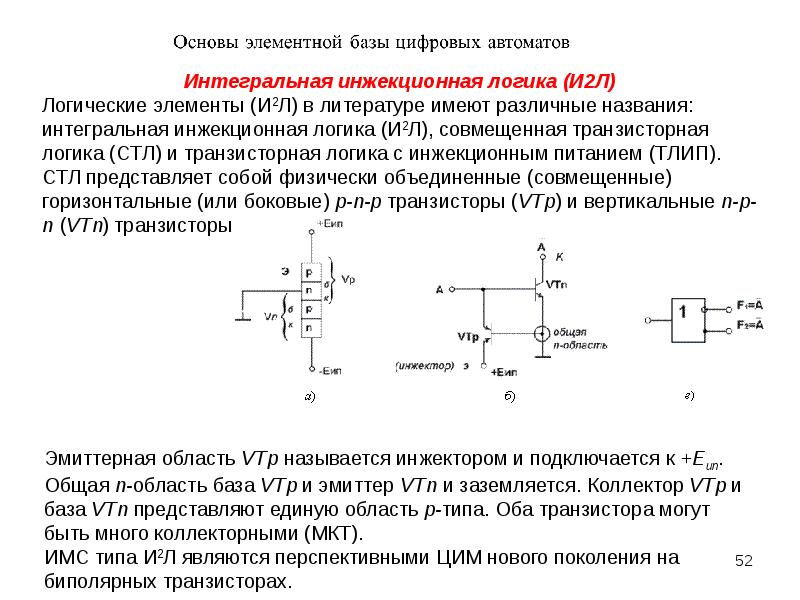

Интегральная инжекционная логика (ИИЛ или И2Л) построена на использовании биполярных транзисторов и применении оригинальных схемотехнических и технологических решений. Для нее характерно очень экономичное использование площади кристалла полупроводника. Элементы И2Л могут быть реализованы только в интегральном исполнении и не имеют аналогов в дискретной схемотехнике. Структура такого элемента и его эквивалентная схема приведены на рис. 3.33, из которого видно, что транзистор T1 (p-n-p) расположен горизонтально, а многоколлекторный транзистор Т2 (n-p n) расположен вертикально. Транзистор T1 выполняет роль инжектора, обеспечивающего поступление дырок из эмиттера транзистора T1 (при подаче на него положительного напряжения через ограничивающий резистор) в базу транзистора Т2.

Васильев Дмитрий Петрович

Профессор электротехники СПбГПУ

Задать вопрос

Если u1 соответствует логическому «0», то инжекционный ток не протекает по базе многоколлекторного транзистора Т2 и токи в цепях коллекторов транзистора Т2 не протекают, т. е. на выходах транзистора Т2 устанавливаются логические «1». При напряжении u1 соответствующем логической «1», инжекционный ток протекает по базе транзистора Т2 и на выходах транзистора Т2 — логические нули.

е. на выходах транзистора Т2 устанавливаются логические «1». При напряжении u1 соответствующем логической «1», инжекционный ток протекает по базе транзистора Т2 и на выходах транзистора Т2 — логические нули.

Рассмотрим реализацию элемента ИЛИ-НЕ на основе элемента, представленного на рис. 3.34 (для упрощения другие коллекторы многоколлекторных транзисторов Т3 и Т4 на рисунке не показаны). Когда на один или оба входа подается логический сигнал «1», то напряжение uвых соответствует логическому нулю. Если на обоих входах логические сигналы «0», то напряжение uвых соответствует логической единице.

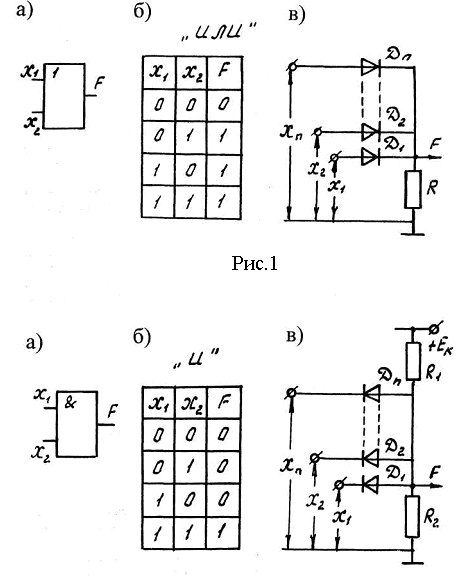

Логика на основе полупроводника из арсенида галлия GaAs характеризуется наиболее высоким быстродействием, что является следствием высокой подвижности электронов (в 3…6 раз больше по сравнению с кремнием). Микросхемы на основе GaAs могут работать на частотах порядка 10 ГГц и более.

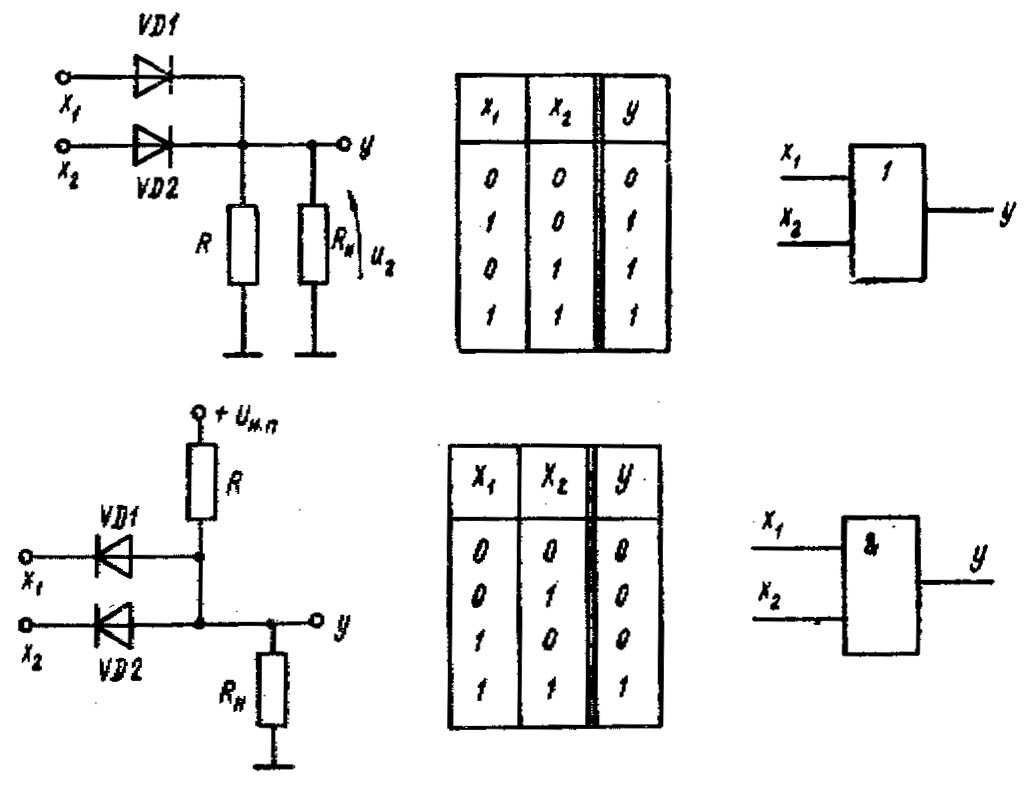

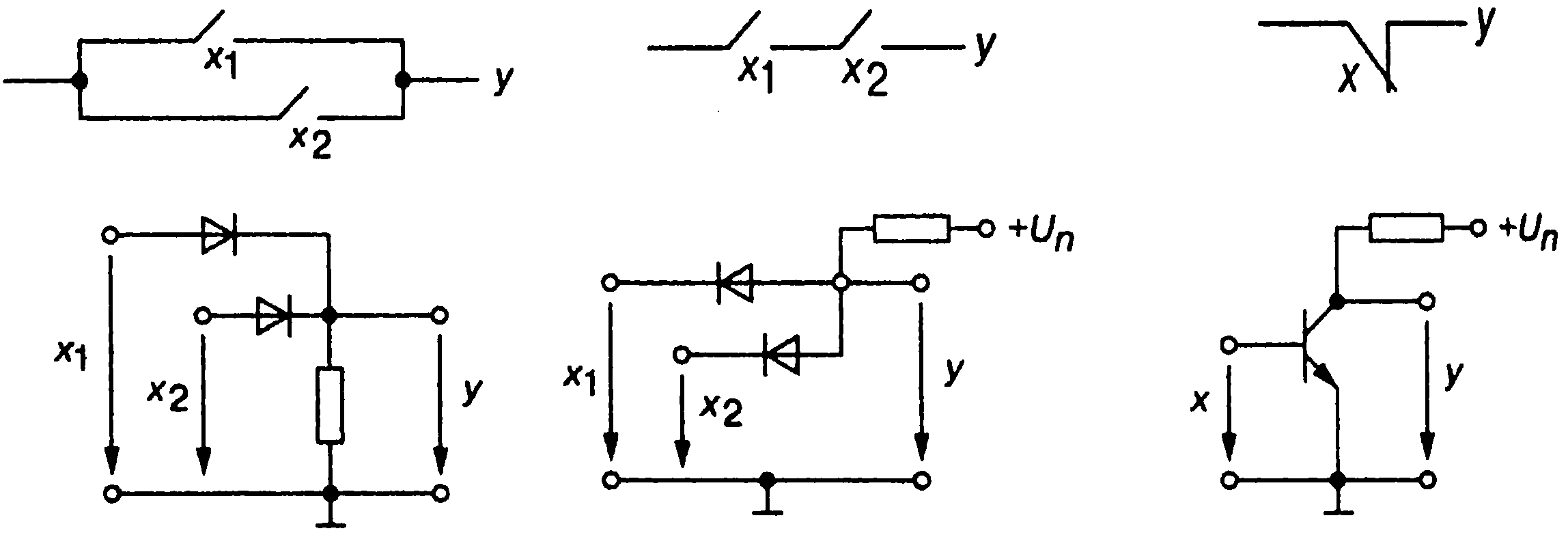

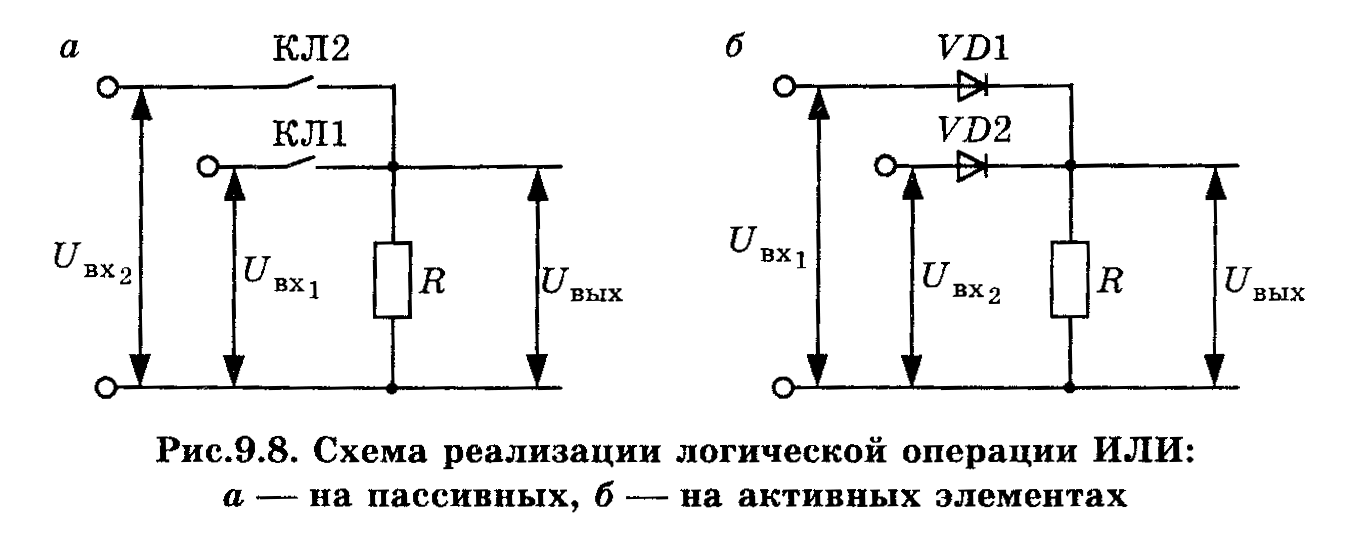

Наиболее простой логический элемент получается при помощи диодов (рис.

1, а)

1, а)Кафедра приема, передачи и

Лекция 1 ОСНОВНЫЕ ПОЛОЖЕНИЯ ТЕОРИИ И ТЕХНИКИ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ Логические функции Математический аппарат, описывающий действия дискретных и цифровых устройств, базируется на алгебре логики, или

ПодробнееЛекция 29. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

97 Лекция 9. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ План. Элементы транзисторно-транзисторной логики (ТТЛ).. Элементы КМОП-логики. 3. Основные параметры логических элементов. 4. Выводы.. Элементы транзисторно-транзисторной

Подробнее10.

2. ЭЛЕКТРОННЫЕ КЛЮЧИ

2. ЭЛЕКТРОННЫЕ КЛЮЧИ10.2. ЭЛЕКТРОННЫЕ КЛЮЧИ Общие сведения. Электронный ключ это устройство, которое может находиться в одном из двух устойчивых состояний: замкнутом или разомкнутом. Переход из одного состояния в другое в

Подробнее1.1 Усилители мощности (выходные каскады)

Лекция 7 Тема: Специальные усилители 1.1 Усилители мощности (выходные каскады) Каскады усиления мощности обычно являются выходными (оконечными) каскадами, к которым подключается внешняя нагрузка, и предназначены

Подробнее1.1 Усилители мощности (выходные каскады)

Лекция 9 Тема 9 Выходные каскады 1.1 Усилители мощности (выходные каскады) Каскады усиления мощности обычно являются выходными (оконечными) каскадами, к которым подключается внешняя нагрузка, и предназначены

ПодробнееЭкзаменационный билет 1

Теоретические вопросы к контролю знаний по дисциплине «Электроника» Вопросы в виде билетов (билеты 1-27 для ЗФО; билеты 1-30 для ОФО) Экзаменационный билет 1 1. Схемы ТЛЭС (транзисторной логики с эмиттерными

Схемы ТЛЭС (транзисторной логики с эмиттерными

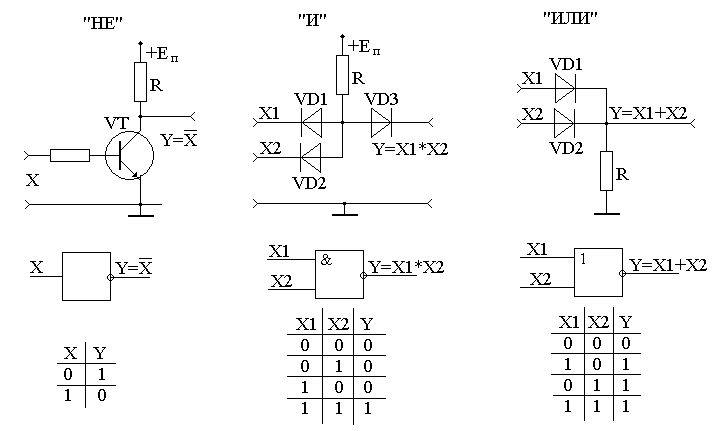

Источник: И.П. Степаненко, «Основы микроэлектроники», Лаборатория базовых знаний, 2003

Источник: И.П. Степаненко, «Основы микроэлектроники», Лаборатория базовых знаний, 2003 Реализация элементарных логических функций. Основные логические элементы: НЕ, И, И-НЕ, ИЛИ, ИЛИ-НЕ Таблица истинности:

ПодробнееОдновибраторы на дискретных элементах.

11.3. ОДНОВИБРАТОРЫ Одновибраторы используются для получения прямоугольных импульсов напряжения большой длительности (от десятков микросекунд до сотен миллисекунд), в качестве устройств задержки, делителей

ПодробнееРисунок 1 Частотная характеристика УПТ

Лекция 8 Тема 8 Специальные усилители Усилители постоянного тока Усилителями постоянного тока (УПТ) или усилителями медленно изменяющихся сигналов называются усилители, которые способны усиливать электрические

Подробнее11.

2. МУЛЬТИВИБРАТОРЫ

2. МУЛЬТИВИБРАТОРЫ11.2. МУЛЬТИВИБРАТОРЫ Мультивибраторы применяются для генерирования прямоугольных импульсов в тех случаях, когда нет жестких требований к их длительности и частоте повторения. Мультивибраторы на дискретных

Подробнее8. Интегральные логические элементы

8. Интегральные логические элементы Введение В логических элементах биполярные транзисторы могут использоваться в трёх режимах: режим отсечки оба p-n перехода транзистора закрыты, режим насыщения оба p-n

ПодробнееЦифровые устройства И ИЛИ НЕ F 1

Цифровые устройства Цифровые устройства это электронные функциональные узлы, которые обрабатывают цифровые сигналы. Цифровые сигналы представляются двумя дискретными уровнями напряжений: высоким и низким

ПодробнееЦифровые и импульсные устройства

Электроника и МПТ Цифровые и импульсные устройства Импульсные устройства устройства, предназначенные для генерирования, формирования, преобразования и неискаженной передачи импульсных сигналов (импульсов).

15.4. СГЛАЖИВАЮЩИЕ ФИЛЬТРЫ

15.4. СГЛАЖИВАЮЩИЕ ФИЛЬТРЫ Сглаживающие фильтры предназначены для уменьшения пульсаций выпрямленного напряжения. Их основным параметром является коэффициент сглаживания равный отношению коэффициента пульсаций

ПодробнееГлава 5. Дифференциальные усилители

Глава 5. Дифференциальные усилители 5. Дифференциальные усилители Дифференциальный усилитель это симметричный усилитель с двумя входами и двумя выходами, использующийся для усиления разности напряжений

ПодробнееЗадания для индивидуальной работы

Министерство науки и образования РФ САМАРСКИЙ ГОСУДАРСТВЕННЫЙ АЭРОКОСМИЧЕСКИЙ УНИВЕРСИТЕТ ИМЕНИ АКАДЕМИКА С.П. КОРОЛЕВА Кафедра «Радиотехнические устройства» Задания для индивидуальной работы Методические

ПодробнееЛекция 9 СТАБИЛИЗАТОРЫ НАПРЯЖЕНИЯ

84 Лекция 9 СТАБИЛИЗАТОРЫ НАПРЯЖЕНИЯ План 1. Введение 2. Параметрические стабилизаторы 3. Компенсационные стабилизаторы 4. Интегральные стабилизаторы напряжения 5. Выводы 1. Введение Для работы электронных

Введение 2. Параметрические стабилизаторы 3. Компенсационные стабилизаторы 4. Интегральные стабилизаторы напряжения 5. Выводы 1. Введение Для работы электронных

Вход Усилитель. Обратная связь

Лекция 5 Тема 5 Обратная связь в усилителях Обратной связью () называют передачу части энергии усиливаемого сигнала из выходной цепи усилителя во входную. На рисунке 4 показана структурная схема усилителя

ПодробнееТриггеры, одновибраторы, мультивибраторы

КЫРГЫЗСКО-РОССИЙСКИЙ СЛАВЯНСКИЙ УНИВЕРСИТЕТ ЕСТЕСТВЕННО-ТЕХНИЧЕСКИЙ ФАКУЛЬТЕТ Кафедра физических процессов горного производства П.И. ПАХОМОВ Триггеры, одновибраторы, мультивибраторы Методическое руководство

ПодробнееОСНОВЫ ЭЛЕКТРОНИКИ. Рисунок 1. Рисунок 2

ОСНОВЫ ЭЛЕКТРОНИКИ Методические указания по темам курса Изучение данного раздела целесообразно проводить, базируясь на курсе физики и руководствуясь программой курса. Усилители на биполярных транзисторах

Усилители на биполярных транзисторах

(51) МПК 7 G05D23/19, G05D23/24, H05B1/02

РОССИЙСКАЯ ФЕДЕРАЦИЯ (19) RU (11)2160920 (13) C2 (51) МПК 7 G05D23/19, G05D23/24, H05B1/02 ФЕДЕРАЛЬНАЯ СЛУЖБА ПО ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ, ПАТЕНТАМ И ТОВАРНЫМ ЗНАКАМ (12) ОПИСАНИЕ ИЗОБРЕТЕНИЯ К ПАТЕНТУ

ПодробнееРисунок 1 Частотная характеристика УПТ

Лекция 8 Тема: Интегральные усилители 1 Усилители постоянного тока Усилителями постоянного тока (УПТ) или усилителями медленно изменяющихся сигналов называются усилители, которые способны усиливать электрические

ПодробнееЛабораторная работа 1

Лабораторная работа 1 «Исследование работы транзисторного мультивибратора» Цель работы : Произвести расчет транзисторного мультивибратора на биполярных транзисторах» Цели занятия: 1. Развивающая Развитие

Развивающая Развитие

Схемы преобразователей частоты

Лекция номер 10 Схемы преобразователей Никитин Н.П. Классификация схем По типу гетеродина: с отдельным и с совмещённым гетеродином По типу прибора, на котором выполняется смеситель: транзисторные и диодные

Подробнее6.3. ДВУХТАКТНЫЕ УСИЛИТЕЛИ МОЩНОСТИ

6.3. ДВУХТАКТНЫЕ УСИЛИТЕЛИ МОЩНОСТИ Двухтактные УМ могут быть трансформаторными и бестрансформаторными. Двухтактный трансформаторный УМ представляет собой два однотактных каскада с общими цепями нулевого

Подробнее8. Генераторы импульсных сигналов

8. Генераторы импульсных сигналов Импульсными генераторами называются устройства, преобразующие энергию постоянного источника напряжения в энергию электрических импульсов. Наибольшее применение в импульсной

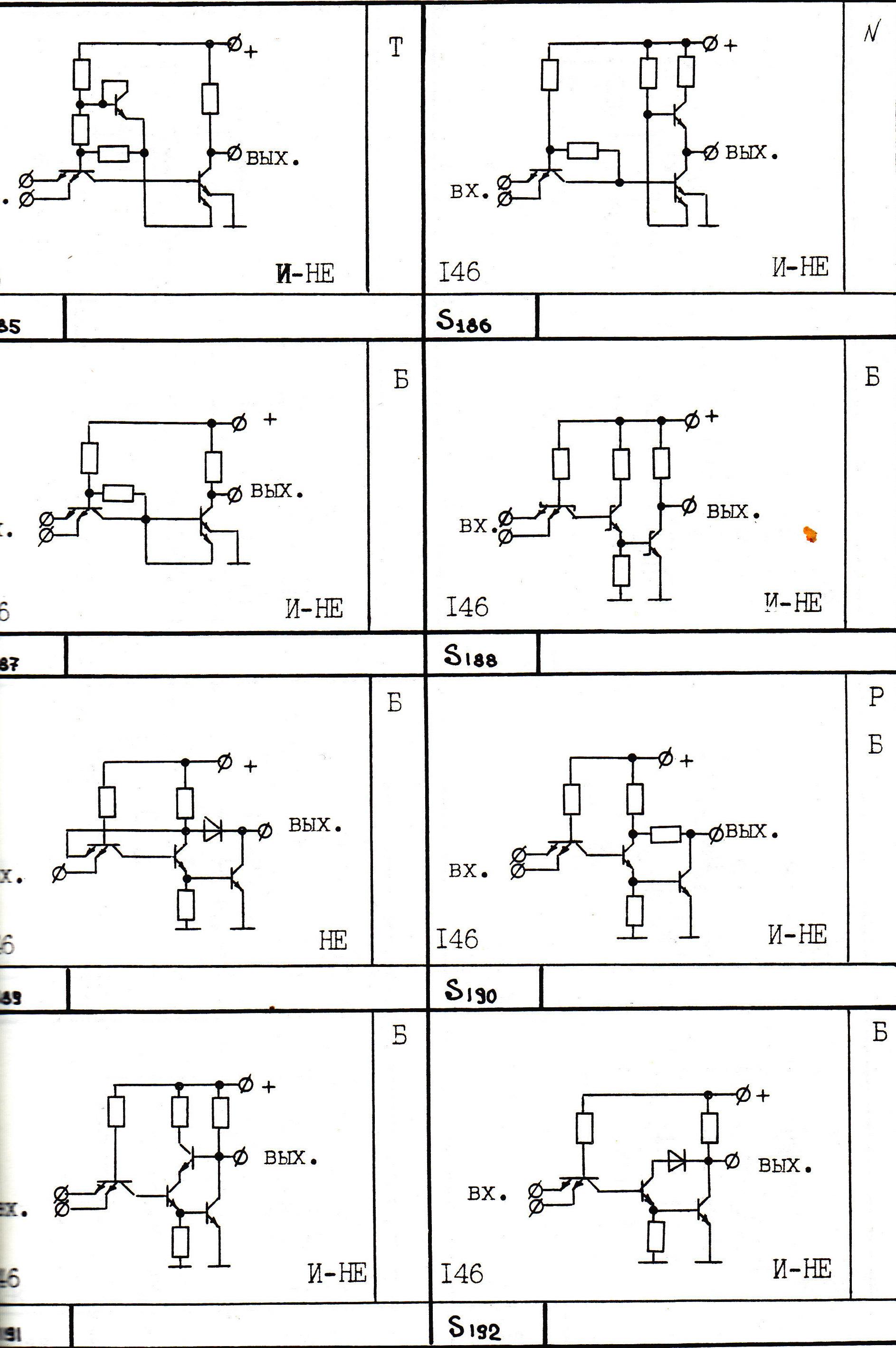

ПодробнееТранзисторные элементы серии «Логика-Т»

Транзисторные элементы серии «Логика-Т» В соответствии с ГОСТ. 2177 74 установлена следующая структура условного обозначения транзисторных элементов серии «Логика-Т»: Пример условного обозначения транзисторного

2177 74 установлена следующая структура условного обозначения транзисторных элементов серии «Логика-Т»: Пример условного обозначения транзисторного

Интегральные компараторы

Интегральные компараторы 1 Интегральные компараторы 1. Принцип действия и разновидности Компараторами называются специализированные ОУ с дифференциальным одом и логическим одом, предназначенные для сравнения

ПодробнееУправление амплитудой

с х е м о т е х н и к а Управление амплитудой мощных гармонических и импульсных сигналов Устройства ограничения, регулирования и модуляции амплитуды электрических сигналов используются во многих радиотехнических

Подробнее5.4. Биполярный транзистор

5.4. Биполярный транзистор Биполярный транзистор это полупроводниковый прибор с двумя p-nпереходами, имеющий три вывода. Управление протекающим через него током осуществляется с помощью управляющего тока.

Управление протекающим через него током осуществляется с помощью управляющего тока.

Генераторы прямоугольных импульсов

Генераторы прямоугольных импульсов Болотских Алексей Александрович 10 «А» класс МОУ «СОШ 6 с углубленным изучением отдельных предметов» Научный руководитель: Лавров Алексей Васильевич Изучить теорию и

ПодробнееГлава 5. УСИЛИТЕЛИ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ

Глава 5. УСИЛИТЕЛИ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ 5.1. ПРИНЦИП УСИЛЕНИЯ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ Назначение и классификация усилителей. Усилители переменного напряжения являются наиболее распространенным типом электронных

ПодробнееЦифровые устройства. Электроника и МПТ

Цифровые устройства Электроника и МПТ Цифровые устройства электронные схемы, которые служат для обработки и преобразования цифровых сигналов. Цифровой сигнал импульсы напряжения близкие по форме к прямоугольным.

Цифровой сигнал импульсы напряжения близкие по форме к прямоугольным.

А.А. Жигальский МИКРОЭЛЕКТРОНИКА

4 А.А. Жигальский МИКРОЭЛЕКТРОНИКА Методические указания по выполнению лабораторных работ по курсу микроэлектроника для студентов специальности 210104 «Микроэлектроника и твердотельная электроника» 5 ТОМСК

Подробнее1

Первый слайд презентации: Логические элементы на МОП-транзисторах

Изображение слайда

2

Слайд 2

Разновидности полевых транзисторов Карта входных и выходных полярностей МОП транзисторов

Изображение слайда

3

Слайд 3

МОП-транзисторы с каналом р-типа и их условные изображения: а ) — со встроенным каналом; б ) — с индуцированным каналом

Изображение слайда

4

Слайд 4

Характеристика n -МОП

Тип транзистора n- МОП

n -МОП

Выходные характеристики ПТ с управляющим переходом и каналом n -типа

Характеристики транзисторов p -типа имеют аналогичный вид, но отличаются напряжением на затворе и полярностью приложенных напряжений (зеркальное отображение в третьем квадранте).

Изображение слайда

5

Слайд 5

Характеристики n -МОП и p -МОП транзисторов

Изображение слайда

6

Слайд 6

p- МОП транзистор Передаточная характеристика Передаточная характеристика n- МОП транзистор

Изображение слайда

7

Слайд 7

р-МОП элемент 2ИЛИ-НЕ Реализация логического элемента 2ИЛИ-НЕ в интегральной схеме R K,Т1 ≥ 100 кОм R K,Т2,Т3 ≤ 1 кОм Логические элементы на p- МОП транзисторах

Изображение слайда

8

Слайд 8

Важнейшие параметры семейства p- МОП

Напряжение питания – -12В (от -9 В до -20 В)

Энергопотребление на вентиль – 6 мВт при H и 0 мВт при L

Быстродействие – 40 нс

Частота переключения – 10 МГц макс. Зазор помехоустойчивости – 5 В тип.

p- МОП логические элементы работают медленно, но устойчиво. Нуждаются в достаточно большом напряжении питания.

Применяются в схемах с низким быстродействием и высокой помехоустойчивостью.

Интегральные схемы обладают высокой плотностью упаковки элементов.

Зазор помехоустойчивости – 5 В тип.

p- МОП логические элементы работают медленно, но устойчиво. Нуждаются в достаточно большом напряжении питания.

Применяются в схемах с низким быстродействием и высокой помехоустойчивостью.

Интегральные схемы обладают высокой плотностью упаковки элементов.

Изображение слайда

9

Слайд 9

р-МОП элемент 2И-НЕ р-МОП элемент НЕ Диапазон напряжений

Изображение слайда

10

Слайд 10

Логические элементы на n- МОП транзисторах

n -МОП элементы

Диапазон напряжений

Напряжение питания – +5В

Энергопотребление – 2 мВт ( L )

0 мВт (Н)

Быстродействие – 5 нс

Максимальная частота – 80 МГц

Зазор помехоустойчивости – 2 В.

Изображение слайда

11

Слайд 11

Логические элементы на КМОП транзисторах

Схема КМОП НЕ-элемента

Принцип действия КМОП НЕ-элемента

Все КМОП-элементы устроены так, что в токовой ветви один транзистор всегда закрыт, а другой всегда открыт.

Энергопотребление КМОП-элементов крайне низко. Оно зависит в основном от количества переключений в секунду или частоты переключения.

Только во время переключения от источника питания потребляется небольшой ток, так как оба транзистора одновременно, но недолго открыты. Один из транзисторов переходит из открытого состояния в запертое и еще не полностью заперт, а другой — из запертого в открытое и еще не полностью открыт. Также должны перезарядиться транзисторные емкости.

Также должны перезарядиться транзисторные емкости.

Изображение слайда

12

Слайд 12

Изменение потребляемого тока в процессе переключения логического элемента КМОП Мощность изменения энергопотребления ЛЭ КМОП

Изображение слайда

13

Слайд 13

Схема КМОП ИЛИ-НЕ-элемента Схема КМОП И-НЕ-элемента Базовые логические элементы КМОП Схема КМОП НЕ-элемента с тремя состояниями выхода

Изображение слайда

14

Слайд 14

Передаточный логический элемент КМОП

(электронный ключ, переключатель)

Ключ на n -канальном МОП-транзисторе с индуцированным каналом

Принципиальная схема передаточного логического элемента

Передаточный элемент работает как переключатель. Рабочая таблица передаточного логического элемента

№

G 2

G 1

L ≈ 0 В, H ≈ +5В

1

L

H

R AZ — высокоомный

2

H

L

R AZ — низкоомный

Рабочая таблица передаточного логического элемента

№

G 2

G 1

L ≈ 0 В, H ≈ +5В

1

L

H

R AZ — высокоомный

2

H

L

R AZ — низкоомный

Изображение слайда

15

Слайд 15

Принципиальная схема

Передаточный логический элемент с управляющим элементом НЕ

Для того чтобы перевести коммутатор в состояние включено, нужно приложить к затвору нормально открытого МОП-транзистора VT 1 положительное управляющее напряжение U упр, равное, по меньшей мере 2Uo т c, а к затвору транзистора VT 2 – такое же напряжение, но противоположное по знаку. При малых величинах входного напряжения U вх оба МОП-транзистора будут открыты. При отрицательных значениях входного напряжения транзисторы VT 1 и VT2 меняются ролями.

Для того чтобы перевести коммутатор в состояние выключено, необходимо изменить полярность управляющего напряжения.

При отрицательных значениях входного напряжения транзисторы VT 1 и VT2 меняются ролями.

Для того чтобы перевести коммутатор в состояние выключено, необходимо изменить полярность управляющего напряжения.

Изображение слайда

16

Слайд 16

Важнейшие параметры семейства КМОП Передаточные характеристики КМОП U И.П. = +5В +10В (30 ÷ 40% от U И.П. )

Изображение слайда

17

Слайд 17

Специфические особенности микросхем КМОП структуры: чувствительность к статическим зарядам, диодно-резистивная охранная цепочка и малая токовая отдача требуют соблюдения правил предосторожности в применении и обращении. Емкость на выходе и входе. Если на выходе инвертора присутствует конденсатор, в моменты переключений через открытые транзисторы протекают токи заряда и разряда. При больших значениях ёмкости, открытый транзистор работает в режиме близком к короткому замыканию. В обычных условиях емкостная нагрузка не должна превышать 500 пФ. Если ёмкость больше, то надо использовать разрядный резистор для ограничения тока, чтобы был не более 1 ÷ 2 мА.

Защита входов от перегрузок. Входное напряжение микросхем КМОП с охранной диодно-резистивной цепочкой на входе для предотвращения отпирания входных диодов в прямом направлении не должно выходить за пределы –0,7В ≤ U вх ≤ U И.П. +0,7В. Иначе также надо использовать токоограничивающий резистор для ограничения тока уровнем 1 ÷ 2мА.

Особенности микросхем КМОП структуры

Диодно-резистивная охранная цепочка

Включение ограничивающих резисторов

Емкость на выходе и входе. Если на выходе инвертора присутствует конденсатор, в моменты переключений через открытые транзисторы протекают токи заряда и разряда. При больших значениях ёмкости, открытый транзистор работает в режиме близком к короткому замыканию. В обычных условиях емкостная нагрузка не должна превышать 500 пФ. Если ёмкость больше, то надо использовать разрядный резистор для ограничения тока, чтобы был не более 1 ÷ 2 мА.

Защита входов от перегрузок. Входное напряжение микросхем КМОП с охранной диодно-резистивной цепочкой на входе для предотвращения отпирания входных диодов в прямом направлении не должно выходить за пределы –0,7В ≤ U вх ≤ U И.П. +0,7В. Иначе также надо использовать токоограничивающий резистор для ограничения тока уровнем 1 ÷ 2мА.

Особенности микросхем КМОП структуры

Диодно-резистивная охранная цепочка

Включение ограничивающих резисторов

Изображение слайда

18

Слайд 18

Неиспользуемые входы КМОП. Их надлежит включать определённым образом, так, чтобы не нарушились условия работы микросхемы в целом.

Так же как и в ТТЛ свободные входы объединяют с + U И.П. или общим проводом в зависимости от функции элемента либо объединяют их с другими, задействованными входами.

а) б)

В случае варианта б) за счёт постоянного смещения отпирание n- канальных транзисторов происходит раньше и общее пороговое напряжение становится меньше, чем в случае а). Поэтому вариант а) более эффективен применительно к помехам, возникающим в общей шине, а вариант б) в отношении защиты от помех, возникающих в шине питания.

Входы КМОП микросхем (в отличие от ТТЛ) оставлять свободными недопустимо.

Если какой-нибудь вход окажется неподсоединён ным, на нём могут возникнуть непредсказуемые напряжения за счёт наводок и связей через паразитные ёмкости. Следствием этого может быть не только неверное действие микросхемы, но и её повреждение.

Их надлежит включать определённым образом, так, чтобы не нарушились условия работы микросхемы в целом.

Так же как и в ТТЛ свободные входы объединяют с + U И.П. или общим проводом в зависимости от функции элемента либо объединяют их с другими, задействованными входами.

а) б)

В случае варианта б) за счёт постоянного смещения отпирание n- канальных транзисторов происходит раньше и общее пороговое напряжение становится меньше, чем в случае а). Поэтому вариант а) более эффективен применительно к помехам, возникающим в общей шине, а вариант б) в отношении защиты от помех, возникающих в шине питания.

Входы КМОП микросхем (в отличие от ТТЛ) оставлять свободными недопустимо.

Если какой-нибудь вход окажется неподсоединён ным, на нём могут возникнуть непредсказуемые напряжения за счёт наводок и связей через паразитные ёмкости. Следствием этого может быть не только неверное действие микросхемы, но и её повреждение.

Изображение слайда

19

Последний слайд презентации: Логические элементы на МОП-транзисторах

Правила обращения с микросхемами КМОП

Микросхемы КМОП структуры нуждаются сравнительно с микросхемами других семейств в более бережном отношении. Это касается как условий монтажа микросхем на платах, так и правил хранения их и эксплуатации в аппаратуре.

При обращении с микросхемами КМОП следует соблюдать следующие меры предосторожности:

В процессе хранения и транспортировки отдельных микросхем выводы их должны быть соединены между собой;

Нельзя производить смену микросхем при включённом напряжении питания;

Допустимый электростатический потенциал на входах – не более 100В;

Плату со смонтированными микросхемами следует брать за торцы, не касаясь разъёмов;

При монтаже тело монтажника должно быть заземлено с помощью проводящего браслета, соединённого с контуром заземления через резистор 500 кОм или вначале коснуться общего провода питания;

Необходимо избегать одежды из синтетических материалов;

Микросхему следует устанавливать на плату после выполнения всех остальных соединений;

Пайку выводов следует вести в последовательности: «общий». «питание», остальные контакты.

Это касается как условий монтажа микросхем на платах, так и правил хранения их и эксплуатации в аппаратуре.

При обращении с микросхемами КМОП следует соблюдать следующие меры предосторожности:

В процессе хранения и транспортировки отдельных микросхем выводы их должны быть соединены между собой;

Нельзя производить смену микросхем при включённом напряжении питания;

Допустимый электростатический потенциал на входах – не более 100В;

Плату со смонтированными микросхемами следует брать за торцы, не касаясь разъёмов;

При монтаже тело монтажника должно быть заземлено с помощью проводящего браслета, соединённого с контуром заземления через резистор 500 кОм или вначале коснуться общего провода питания;

Необходимо избегать одежды из синтетических материалов;

Микросхему следует устанавливать на плату после выполнения всех остальных соединений;

Пайку выводов следует вести в последовательности: «общий». «питание», остальные контакты.

Изображение слайда

Транзисторно−транзисторная логика (ТТЛ) | Основы электроакустики

Характерной особенностью ТТЛ являются многоэмиттерные транзисторы. Эти транзисторы сконструированы таким образом, что не оказывают влияния друг на друга. Каждому эмиттеру соответствует свой p-n-переход. В первом приближении многоэмиттерный транзистор может моделироваться схемой на диодах (пунктир на рис. 18.8), в этом случае он работает как схема диодно-транзисторной логики И-НЕ.

Эти транзисторы сконструированы таким образом, что не оказывают влияния друг на друга. Каждому эмиттеру соответствует свой p-n-переход. В первом приближении многоэмиттерный транзистор может моделироваться схемой на диодах (пунктир на рис. 18.8), в этом случае он работает как схема диодно-транзисторной логики И-НЕ.

К достоинствам ТТЛ-логики можно отнести: высокое быстродействие (10 нс), надежность, радиационную стойкость.

Недостатками являются: наличие резисторов, большая площадь на кристалле, большая потребляемая мощность, наличие паразитных транзисторов.

Рис. 18.8. Схема ТТЛ-элемента с простым инвертором, выполняющая логическую операцию И-НЕ

Из анализа схемы можно сделать вывод, что если на один из входов или на оба входа подать низкий уровень напряжения, то ток базы транзистора VT2 будет равен нулю, и на коллекторе транзистора VT2 будет высокий уровень напряжения. Если на оба входа подать высокий уровень напряжения, то через базу VT2 транзистора будет протекать большой базовый ток и на коллекторе транзистора VT2 будет низкий уровень напряжения, т. е. данный элемент реализует функцию И-НЕ.

е. данный элемент реализует функцию И-НЕ.

Рис. 18.9. Базовый элемент ТТЛ со сложным инвертором, выполняющий логическую операцию И-НЕ

Если на один или оба входа одновременно подан низкий уровень напряжения, то многоэмиттерный транзистор находится в состоянии насыщения и транзистор VT2закрыт, а, следовательно, закрыти транзистор VT4, т. е. на выходе будет высокий уровень напряжения. Если на обоих входах одновременно действует высокий уровень напряжения, то транзистор VT2открывается и входит в режим насыщения, что приводит к открытию и насыщению транзистора VT4и запиранию транзистора VT3, т. е. реализуется функция И-НЕ.

Элементы с тремя состояниями и с открытым коллектором. Вентили ТТЛ и КМОП имеют двухтактные выходные схемы: ВЫСОКИЙ или НИЗКИЙ уровень подается на выход через открытый биполярный или МОП-транзистор. Такую схему, которая носит название активной нагрузки, а в ТТЛ называется также столбовым выходом, используют почти все логические элементы. Эта схема обеспечивает низкое выходное сопротивление в обоих состояниях, имеет малое время переключения и обладает более высокой помехоустойчивостью по сравнению с одиночным транзистором, который использует в качестве коллекторной нагрузки пассивный резистор.

Такую схему, которая носит название активной нагрузки, а в ТТЛ называется также столбовым выходом, используют почти все логические элементы. Эта схема обеспечивает низкое выходное сопротивление в обоих состояниях, имеет малое время переключения и обладает более высокой помехоустойчивостью по сравнению с одиночным транзистором, который использует в качестве коллекторной нагрузки пассивный резистор.

В случае КМОП применение активного выхода, помимо всего прочего, позволяет понизить рассеиваемую мощность. Однако существует ряд ситуаций, при которых активный выход, оказывается неудобным.

В качестве примера представим себе вычислительную систему, в которой должны обмениваться данными несколько функциональных блоков. Центральный процессор (ЦП), память, а также различные периферийные устройства должны иметь возможность передавать и принимать 16-разрядные слова, и было бы, мягко говоря, неудобно использовать для соединения каждого устройства с каждым индивидуальный 16-жильный кабель.

Для решения этой проблемы используется так называемая шина (или магистраль) данных (databus), т. е. один 16-жильный кабель, доступный для всех устройств. Такая структура аналогична телефонному каналу коллективного пользования: в каждый момент времени «говорить» («передавать данные») может только одно устройство, а остальные могут только «слушать» («принимать данные»). При использовании шинной системы необходимо иметь соглашение о том, кому разрешено «говорить». В связи с этим употребляются такие термины, как «арбитр шины», «ведущее устройство» и «устройство управления шиной».

Для возбуждения шины нельзя использовать вентили (или другие схемы) с активным выходом, поскольку их нельзя отключить от общих информационных линий (в любой момент времени выходы устройств, подключенные к шине, будут находиться в состоянии ВЫСОКОГО или НИЗКОГО уровня). Для этого случая необходим вентиль, выход которого может находиться в «обрыве», т. е. быть «открытым». Такие устройства выпускаются промышленностью и имеют две разновидности, которые носят названия «элементов с тремя состояниями»и «элементов с открытым коллектором». Начнем с рассмотрения последних, подразумевая, что все сказанное применимо также и к элементам с тремя состояниями.

Начнем с рассмотрения последних, подразумевая, что все сказанное применимо также и к элементам с тремя состояниями.

В выходной схеме вентиля с открытым коллектором отсутствует транзистор, являющийся активной нагрузкой (рис. 18.10).

Рис. 18.10. ТТЛ вентиль с открытым коллектором

При использовании таких элементов внешний нагрузочный резистор можно подключить к любому источнику. Величина этого резистора не является критичной: при малых значениях резистора обеспечиваются повышенные быстродействия и помехоустойчивость, однако повышаются рассеиваемая мощность и нагрузочный ток выходного каскада. Для ТТЛ типичные значения лежат в пределах от нескольких сотен до нескольких тысяч Ом. Как мы вскоре покажем, все, что далее будет говориться о вентилях с открытым коллектором, относится также и к вентилям с тремя состояниями.

Иногда возникает необходимость логического объединения выходов очень большого числа элементов. Например, для объединения 20 выходов потребовалось бы использовать логический элемент с 20 входами и вести к нему 20 отдельных проводов. Этого можно избежать, используя логические элементы с открытым коллектором. В качестве выходного каскада они содержат, как показано на рисунке 18.10, n-р-n-транзистор, эмиттер которого соединен с общей точкой. Выходы таких систем, в отличие от обычно используемых двухтактных выходных каскадов, могут подключаться к одному общему коллекторному резистору параллельно друг другу.

Этого можно избежать, используя логические элементы с открытым коллектором. В качестве выходного каскада они содержат, как показано на рисунке 18.10, n-р-n-транзистор, эмиттер которого соединен с общей точкой. Выходы таких систем, в отличие от обычно используемых двухтактных выходных каскадов, могут подключаться к одному общему коллекторному резистору параллельно друг другу.

Выходное напряжение имеет высокий уровень только тогда, когда все выходные транзисторы элементов заперты, следовательно, здесь реализуется функция ИЛИ. Так как логическая связь организуется с помощью внешнего монтажа, такое соединение условно называется «монтажное ИЛИ».

Другим применением схем с открытым коллектором является управление внешней нагрузкой, которая должна подключаться к источнику положительного напряжения, превышающего напряжение питания ИМС. Может, частности, потребоваться включить маломощную 12-вольтовую лампочку или сформировать перепад логических уровней напряжения 15 В с помощью резистора, установленного между выходом вентиля и источником +15 В (рис. 18.12).

18.12).

Рисунок 18.11 Реализация функции «монтажное ИЛИ»

Однако такая схема имеет существенный недостаток: переход в высокоомное (единичное) состояние из-за паразитных емкостей происходит всегда медленнее, чем в низкоомное (нулевое). Поэтому вместо элементов с открытым коллектором лучше использовать элементы с трехстабильным выходом. Они содержат обычный двухтактный выходной каскад, который, однако, может быть переведен в особое высокоомноесостояние (высокоимпедансное состояние или обрыв). Для управления выходным каскадом служит специальный вывод – разрешение выдачи данных.

Рис. 18.12. Подключение вентиля с открытым коллектором к источнику 15В

Соответствующая схема ТТЛ представлена на рис. 18.13.

Рис. 18.13. Трехстабильный ТТЛ вентиль

Если уровень управляющего напряжения UEнизкий, запираются обатранзистора и . При высоком уровне UE получим обычную логическую связь И-НЕ между входными сигналами и . Аналогичным образом можно перевести в высокоомное (безразличное) состояние и трехстабильный элемент КМОП.

При высоком уровне UE получим обычную логическую связь И-НЕ между входными сигналами и . Аналогичным образом можно перевести в высокоомное (безразличное) состояние и трехстабильный элемент КМОП.

Логические элементы — это… Что такое Логические элементы?

Логические элементы — устройства, предназначенные для обработки информации в цифровой форме (последовательности сигналов высокого — «1» и низкого — «0» уровней в двоичной логике, последовательность «0», «1» и «2» в троичной логике, последовательности «0», «1», «2», «3», «4», «5», «6», «7», «8» и «9» в десятичной логике). Физически логические элементы могут быть выполнены механическими, электромеханическими (на электромагнитных реле), электронными (на диодах и транзисторах), пневматическими, гидравлическими, оптическими и др.

С развитием электротехники от механических логических элементов перешли к электромеханическим логическим элементам (на электромагнитных реле), а затем к электронным логическим элементам на электронных лампах, позже — на транзисторах. После доказательства в 1946 г. теоремы Джона фон Неймана об экономичности показательных позиционных систем счисления стало известно о преимуществах двоичной и троичной систем счисления по сравнению с десятичной системой счисления. От десятичных логических элементов перешли к двоичным логическим элементам. Двоичность и троичность позволяет значительно сократить количество операций и элементов, выполняющих эту обработку, по сравнению с десятичными логическими элементами.

После доказательства в 1946 г. теоремы Джона фон Неймана об экономичности показательных позиционных систем счисления стало известно о преимуществах двоичной и троичной систем счисления по сравнению с десятичной системой счисления. От десятичных логических элементов перешли к двоичным логическим элементам. Двоичность и троичность позволяет значительно сократить количество операций и элементов, выполняющих эту обработку, по сравнению с десятичными логическими элементами.

Логические элементы выполняют логическую функцию (операцию) над входными сигналами (операндами, данными).

Всего возможно логических функций и соответствующих им логических элементов, где — основание системы счисления, — число входов (аргументов), — число выходов, то есть бесконечное число логических элементов. Поэтому в данной статье рассматриваются только простейшие и важнейшие логические элементы.

Всего возможны двоичных двухвходовых логических элементов и двоичных трёхвходовых логических элементов (Булева функция).

Кроме 16 двоичных двухвходовых логических элементов и 256 трёхвходовых двоичных логических элементов возможны 19 683 двухвходовых троичных логических элемента и 7 625 597 484 987 трёхвходовых троичных логических элементов (троичные функции).

Содержание

|

Логические операции (булева функция) своё теоретическое обоснование получили в алгебре логики.

Логические операции с одним операндом называются унарными, с двумя — бинарными, с тремя — тернарными (триарными, тринарными) и т. д.

Из возможных унарных операций с унарным выходом интерес для реализации представляют операции отрицания и повторения, причём, операция отрицания имеет большую значимость, чем операция повторения, так как повторитель может быть собран из двух инверторов, а инвертор из повторителей не собрать.

Отрицание, НЕ

Инвертор, НЕ| 0 | 1 |

| 1 | 0 |

Мнемоническое правило для отрицания звучит так: На выходе будет:

Повторение, ДА

| 0 | 0 |

| 1 | 1 |

Преобразование информации требует выполнения операций с группами знаков, простейшей из которых является группа из двух знаков. Оперирование с большими группами всегда можно разбить на последовательные операции с двумя знаками.

Из возможных бинарных логических операций с двумя знаками c унарным выходом интерес для реализации представляют 10 операций, приведённых ниже.

Конъюнкция (логическое умножение). Операция 2И. Функция min(A,B)

2И| ٨ | ||

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 1 | 1 |

Логический элемент, реализующий функцию конъюнкции, называется схемой совпадения. Мнемоническое правило для конъюнкции с любым количеством входов звучит так: На выходе будет:

- «1» тогда и только тогда, когда на всех входах действуют «1»,

- «0» тогда и только тогда, когда хотя бы на одном входе действует «0»

Дизъюнкция (логическое сложение). Операция 2ИЛИ. Функция max(A,B)

2ИЛИМнемоническое правило для дизъюнкции с любым количеством входов звучит так: На выходе будет:

- «1» тогда и только тогда, когда хотя бы на одном входе действует «1»,

- «0» тогда и только тогда, когда на всех входах действуют «0»

Инверсия функции конъюнкции. Операция 2И-НЕ (штрих Шеффера)

2И-НЕМнемоническое правило для И-НЕ с любым количеством входов звучит так: На выходе будет:

- «1» тогда и только тогда, когда хотя бы на одном входе действует «0»,

- «0» тогда и только тогда, когда на всех входах действуют «1»

Инверсия функции дизъюнкции. Операция 2ИЛИ-НЕ (стрелка Пирса)

2ИЛИ-НЕ| ↓ | ||

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Мнемоническое правило для ИЛИ-НЕ с любым количеством входов звучит так: На выходе будет:

- «1» тогда и только тогда, когда на всех входах действуют «0»,

- «0» тогда и только тогда, когда хотя бы на одном входе действует «1»

Эквивалентность (равнозначность), 2ИСКЛЮЧАЮЩЕЕ_ИЛИ-НЕ

ИСКЛ-ИЛИ-НЕ| ↔ | ||

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Мнемоническое правило эквивалентности с любым количеством входов звучит так: На выходе будет:

- «1» тогда и только тогда, когда на входе действует четное количество,

- «0» тогда и только тогда, когда на входе действует нечетное количество

Сложение по модулю 2 (2Исключающее_ИЛИ, неравнозначность). Инверсия равнозначности.

ИСКЛ-ИЛИВ англоязычной литературе 2XOR.

Мнемоническое правило для суммы по модулю 2 с любым количеством входов звучит так: На выходе будет:

- «1» тогда и только тогда, когда на входе действует нечётное количество ,

- «0» тогда и только тогда, когда на входе действует чётное количество

Импликация от A к B (прямая импликация, инверсия декремента, A<=B)

| → | ||

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Мнемоническое правило для инверсии декремента звучит так: На выходе будет:

- «0» тогда и только тогда, когда на «B» меньше «А»,

- «1» тогда и только тогда, когда на «B» больше либо равно «А»

Импликация от B к A (обратная импликация, инверсия инкремента, A>=B)

| → | ||

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Мнемоническое правило для инверсии инкремента звучит так: На выходе будет:

- «0» тогда и только тогда, когда на «B» больше «А»,

- «1» тогда и только тогда, когда на «B» меньше либо равно «А»

Декремент. Запрет импликации по B. Инверсия импликации от A к B

Мнемоническое правило для инверсии импликации от A к B звучит так: На выходе будет:

- «1» тогда и только тогда, когда на «A» больше «B»,

- «0» тогда и только тогда, когда на «A» меньше либо равно «B»

Инкремент. Запрет импликации по A. Инверсия импликации от B к A

Мнемоническое правило для инверсии импликации от B к A звучит так: На выходе будет:

- «1» тогда и только тогда, когда на «B» больше «A»,

- «0» тогда и только тогда, когда на «B» меньше либо равно «A»

Примечание 1. Элементы импликаций не имеют промышленных аналогов для функций с количеством входов, не равным 2.

Примечание 2. Элементы импликаций не имеют промышленных аналогов.

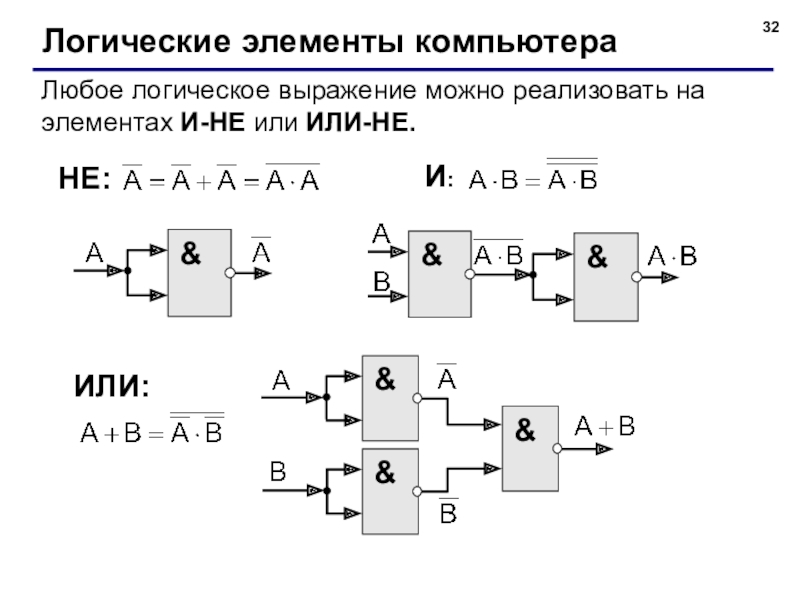

Этими простейшими логическими операциями (функциями), и даже некоторыми их подмножествами, можно выразить любые другие логические операции. Такой набор простейших функций называется функционально полным логическим базисом. Таких базисов 4:

- И, НЕ (2 элемента)

- ИЛИ, НЕ (2 элемента)

- И-НЕ (1 элемент)

- ИЛИ-НЕ (1 элемент).

Для преобразования логических функций в один из названых базисов необходимо применять Закон (правило) де-Моргана.

Физические реализации логических элементов

Физические реализации одной и той же логической функции в разных системах электронных и неэлектронных элементов отличаются друг от друга.

Классификация электронных транзисторных физических реализаций логических элементов

Логические элементы подразделяются и по типу использованных в них электронных элементов. Наибольшее применение в настоящее время находят следующие логические элементы:

- РТЛ (резисторно-транзисторная логика)

- ДТЛ (диодно-транзисторная логика)

- ТТЛ (транзисторно-транзисторная логика)

Обычно входной каскад логических элементов ТТЛ представляет собой простейшие компараторы, которые могут быть выполнены различными способами (на многоэмиттерном транзисторе или на диодной сборке). В логических элементах ТТЛ входной каскад, кроме функций компараторов, выполняет и логические функции. Далее следует выходной усилитель с двухтактным (двухключевым) выходом.

В логических элементах КМОП входные каскады также представляют собой простейшие компараторы. Усилителями являются КМОП-транзисторы. Логические функции выполняются комбинациями параллельно и последовательно включенных ключей, которые одновременно являются и выходными ключами.

Транзисторы могут работать в инверсном режиме, но с меньшим коэффициентом усиления. Это свойство используются в ТТЛ многоэмиттерных транзисторах. При подаче на оба входа сигнала высокого уровня (1,1) первый транзистор оказывается включенным в инверсном режиме по схеме эмиттерного повторителя с высоким уровнем на базе, транзистор открывается и подключает базу второго транзистора к высокому уровню, ток идёт через первый транзистор в базу второго транзистора и открывает его. Второй транзистор «открыт», его сопротивление мало и на его коллекторе напряжение соответствует низкому уровню (0). Если хотя бы на одном из входов сигнал низкого уровня (0), то транзистор оказывается включенным по схеме с общим эмиттером, через базу первого транзистора на этот вход идёт ток, что открывает его и он закорачивает базу второго транзистора на землю, напряжение на базе второго транзистора мало и он «закрыт», выходное напряжение соответствует высокому уровню. Таким образом, таблица истинности соответствует функции 2И-НЕ.

Для увеличения быстродействия логических элементов в них используются транзисторы Шоттки (транзисторы с диодами Шоттки), отличительной особенностью которых является применение в их конструкции выпрямляющего контакта металл-полупроводник вместо p-n перехода. При работе этих приборов отсутствует инжекция неосновных носителей и явления накопления и рассасывания заряда, что обеспечивает высокое быстродействие. Включение этих диодов параллельно коллекторному переходу блокирует насыщение выходных транзисторов, что увеличивает напряжения логических 0 и 1, но уменьшает потери времени на переключение логического элемента при том же потребляемом токе (или позволяет уменьшить потребляемый ток при сохранении стандартного быстродействия). Так, серия 74хх и серия 74LSxx имеют приблизительно равное быстродействие (в действительности, серия 74LSxx несколько быстрее), но потребляемый от источника питания ток меньше в 4-5 раз (во столько же раз меньше и входной ток логического элемента).

Эта логика, иначе называемая логикой на переключателях тока, построена на базе биполярных транзисторов, объединённых в дифференциальные каскады. Один из входов обычно подключён внутри микросхемы к источнику опорного (образцового) напряжения, примерно посредине между логическими уровнями. Сумма токов через транзисторы дифференциального каскада постоянна, в зависимости от логического уровня на входе изменяется лишь то, через какой из транзисторов течёт этот ток. В отличие от ТТЛ, транзисторы в ЭСЛ работают в активном режиме и не входят в насыщение или инверсный режим. Это приводит к тому, что быстродействие ЭСЛ-элемента при той же технологии (тех же характеристиках транзисторов) гораздо больше, чем ТТЛ-элемента, но больше и потребляемый ток. К тому же, разница между логическими уровнями у ЭСЛ-элемента намного меньше, чем у ТТЛ (меньше вольта), и, для приемлемой помехоустойчивости, приходится использовать отрицательное напряжение питания (а иногда и применять для выходных каскадов второе питание). Зато максимальные частоты переключения триггеров на ЭСЛ более, чем на порядок превышают возможности современных им ТТЛ, например, серия К500 обеспечивала частоты переключения 160—200 МГц, по сравнению с 10-15 МГц современной ей ТТЛ серии К155. В настоящее время и ТТЛ(Ш), и ЭСЛ практически не используются, так как с уменьшением проектных норм КМОП технология достигла частот переключения в несколько гигагерц.

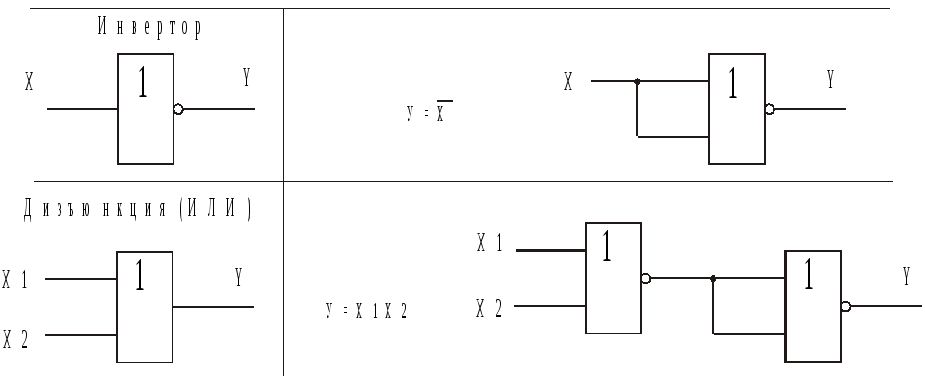

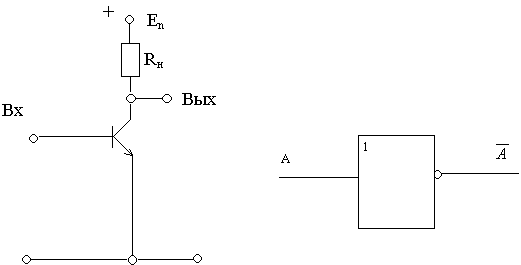

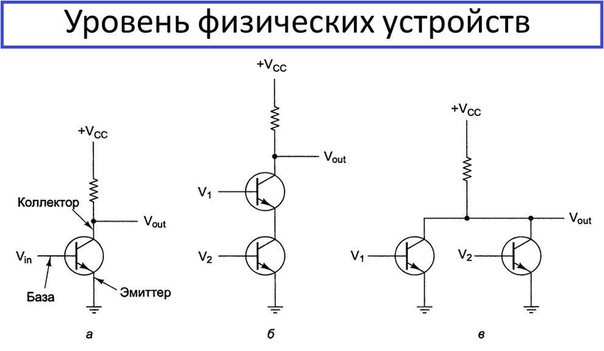

Инвертор

Одним из основных логических элементов является инвертор. Инвертирующими каскадами являются однотранзисторный каскад с общим эмиттером, однотранзисторный каскад с общим истоком, двухтранзисторный двухтактный выходной каскад на комплементарных парах транзисторов с последовательным включением транзисторов по постоянному току (применяется в ТТЛ и КМОП), двухтранзисторный дифференциальный каскад с параллельным включением транзисторов по постоянному току (применяется в ЭСЛ) и др. Но одного условия инвертирования недостаточно для применения инвертирующего каскада в качестве логического инвертора. Логический инвертор должен иметь смещённую рабочую точку на один из краёв проходной характеристики, что делает каскад неустойчивым в середине диапазона входных величин и устойчивым в крайних положениях (закрыт, открыт). Такой характеристикой обладает компаратор, поэтому логические инверторы строят как компараторы, а не как гармонические усилительные каскады с устойчивой рабочей точкой в середине диапазона входных величин. Таких каскадов, как и контактных групп реле, может быть два вида: нормально закрытые (разомкнутые) и нормально открытые (замкнутые).

Применение логических элементов

Логические элементы входят в состав микросхем, например ТТЛ элементы — в состав микросхем К155 (SN74), К133; ТТЛШ — 530, 533, К555, ЭСЛ — 100, К500 и т. д.

Комбинационные логические устройства

Комбинационными называются такие логические устройства, выходные сигналы которых однозначно определяются входными сигналами:

Все они выполняют простейшие двоичные, троичные или n-ичные логические функции.

Последовательностные цифровые устройства

Последовательностными называют такие логические устройства, выходные сигналы которых определяются не только сигналами на входах, но и предысторией их работы, то есть состоянием элементов памяти.

См. также

Ссылки

Литература

4. Базовые цифровые схемы — Введение в цифровые схемы