Логисторная логика / Хабр

Логисторная логика это набор концепций, применение которых может позволить ускорить вычисления, сократить затраты энергии на вычисления и увеличить плотность транзисторов на кристалле без существенного изменения техпроцесса. Она находится в разработке и статья ниже является лишь первичным результатом. Мы надеемся что она вызовет интерес в научных кругах и среди энтузиастов и разработка будет продолжена.

Логисторная логика предполагает:

Параллельно — последовательное , а не последовательное как в CMOS, выполнение операций на уровне логических элементов (альтернатива CMOS)

Не стандартный метод кодирования 0 и 1

Использование Логисторов (тип транзисторов)

Использование двуполярного питания

Использование «grid array» расположения гейтов (вертикально и горизонтально на виде сверху)

В процессорах математические операции описываются логическими схемами, которые представлены последовательным подключением CMOS транзисторных сборок.

Время выполнения этих операций определяется суммой времен выполнения каждой из последовательно подключенных транзисторных CMOS сборок

Чтобы продемонстрировать задержки, возникающие при последовательном подключении CMOS сборок представим симуляцию, выполненную в LTSpice на основе реальных spice моделей 10нм FinFET:

На графике ниже виден исходный сигнал (зеленый) и задержки, возникающие после двух (синий) и после 4-х инверторов (красный)

Предлагается новый тип транзистора — логистор:

В логисторе выходной сигнал (между Source и Drain) «изолирован» от управляющего сигнала — между Gate и Base, соответственно логисторы могут также использоваться вместо оптронов

В comsol semiconductor была произведена симуляция логистора, которая показала возникновение канала между Source и Drain при подаче положительного напряжения на Gate и отрицательного на Base. Ниже показан канал при отсутствии и наличии напряжения между Source и Drain:

Расчетная Вольт-Амперная характеристика логистора:

Благодаря двуполярному питанию, которое будет описано ниже, не требуется обеспечивать полное «запирание» логистора при закороченных Gate и Base, благодаря чему возможен подбор профиля допинга при котором логистор «качественнее» запирается и позволяет пропускать втрое большие токи чем NMOS при прочих равных.

Входные значения в ALU, построенном на базе логисторной логики должны иметь ниже описанный метод кодирования 0 и 1:

Где выходное значение — это напряжение между выходами и землей. Как видно, каждый бит передается по двум проводам.

Единичные логические операции в логисторной логике принципиально описываются следующим образом:

Где «результат» — наличие (1) или отсутствие (0) пути

В логисторной логике логические цепи отличны от CMOS, TTL и других технологий. В случае отсутствия ограничения степени параллельности (в «полной» логисторной логике) цепи строятся таким образом, чтобы при выполнении операции не возникало «to Gate» операций. Другими словами в ALU запрещена подача сигнала с Drain на Gate.

В результате операции выполняются параллельно а не последовательно как у CMOS

Пример построения «полной» логисторной схемы для сумматора двух 4-х битных чисел

A1, A2, A3, A4; B1, B2, B3, B4 — биты первого и второго числа; outputs — результат

Инвертированные входы представлены как проводящие ключи, не инвертированные — не проводящие

В логисторной логике формат выхода не регламентирован и может не совпадать с форматом входа, поэтому правая часть (комплиментарная) не обязательна и приведена для понимания метода составления комплиментарных схем.

В полной логисторной логике каждый выход должен иметь независимую логическую схему.

Ниже представлена симуляция в Logisim без комплиментарной части. справа сверху — стандартная схема сумматора; справа снизу — схема необходимая для построения полных логисторных схем

Далее представлена симуляция логисторного сумматора двух 3-х битных чисел в falstad:

Для подтверждения работоспособности логической части логисторной логики была запроектирована в EasyEDA и изготовлена на JLCPcb плата:

Виду того что логисторы не существуют, были использованы оптроны. Плата работает и выдает ожидаемые значения, что неопровержимо доказывает верность логической части логисторной логики.

Для достижения высокой плотности размещения логисторов рекомендуется объединить Base всех логисторов и разместить Base на обратной стороне Substrate. Gates рекомендуется располагать горизонтально и вертикально. Source и Drain соседних Логисторов необходимо объединять, так что к одному Source / Drain будут присоединяться 4 Gate

Стоит обратить особое внимание на то что в статье описана логисторная логика без ограничения степени параллельности (полная), где степень параллельности — примерное количество Gates которое может запитываться с одного Drain. Для увеличения производительности обязательно использование ограничения степени параллельности. При этом исчезает требование — использовать независимую схему для каждого выходного бита. Использование каскадирования перед логисторной логикой для увеличения токов для насыщения большого количества Gates — является очевидным, но наихудшим решением

Для увеличения производительности обязательно использование ограничения степени параллельности. При этом исчезает требование — использовать независимую схему для каждого выходного бита. Использование каскадирования перед логисторной логикой для увеличения токов для насыщения большого количества Gates — является очевидным, но наихудшим решением

По техническим причинам коллектив далее не может продолжать работу над проектом и описать оптимальное решение внедрения ограничения степени параллельности, а также не обладает ресурсами для реализации чипа на базе логисторной логики, поэтому материал передается в доработку научному сообществу и энтузиастам

Разработано в ЛНМО; Авторы: Артем Родичкин, Анна Евсеева, Полина Маслова, Семен Архипов, Инна Миронова, Чечулин Михаил

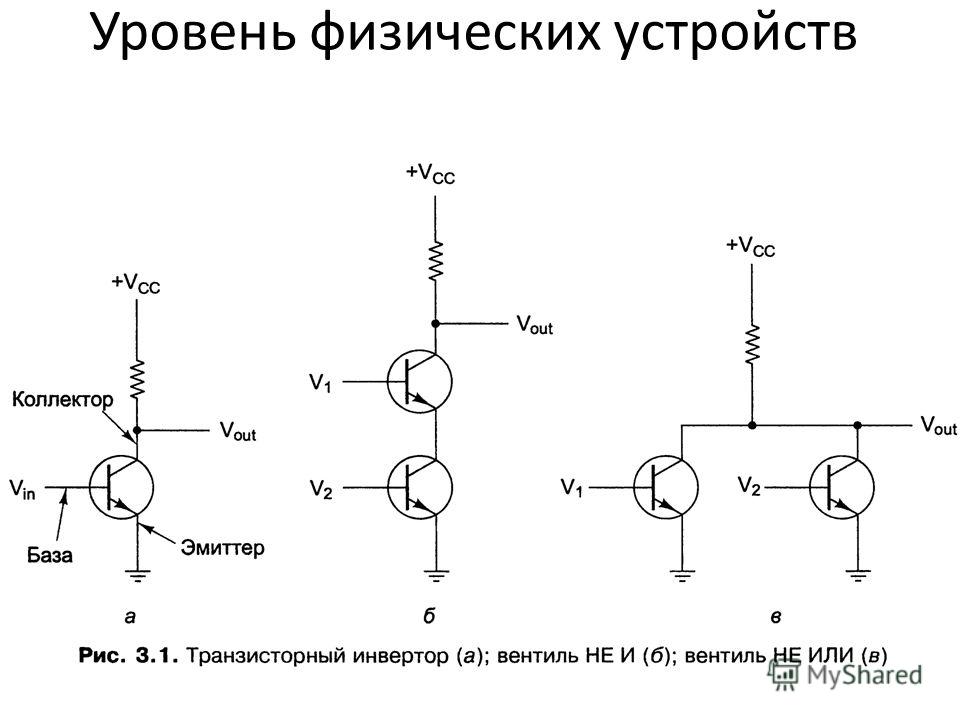

Основы микроэлектроники | Логические элементы с передачей тока или напряжения. Транзисторная логика с непосредственными связями

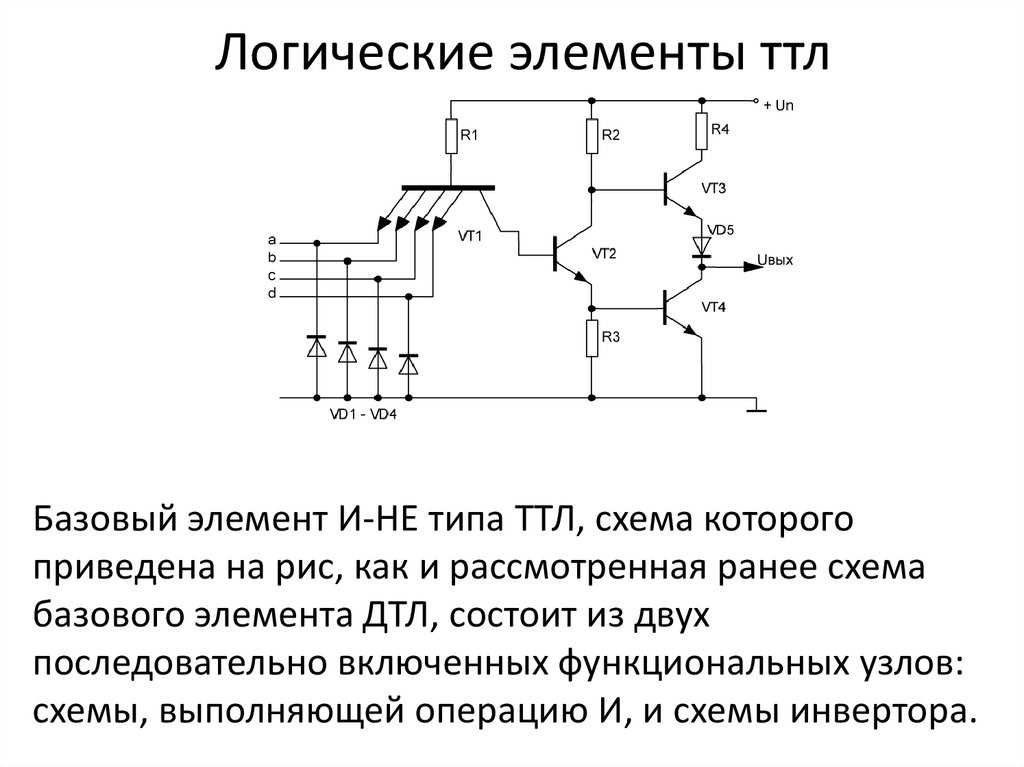

Транзисторная логика с непосредственными связями (ТЛНС) основана на параллельном (или последовательном) соединении транзисторных ключей и использовании общей коллекторной нагрузки (рис. 3.4). Конструктивно транзисторы Т1, Т2, T3 объединены по коллектору и подключены через резистор Rкк шине Ек. Входные сигналы подаются на базы транзисторов. Выходы подключены на входы таких же элементов. Схема рассчитывается так, чтобы при подаче высокого напряжения (соответствующей логической 1) на базу одного или нескольких транзисторов происходило насыщение транзисторов и выходной потенциал снижался до низкого уровня – остаточного потенциала U0= Uост.

3.4). Конструктивно транзисторы Т1, Т2, T3 объединены по коллектору и подключены через резистор Rкк шине Ек. Входные сигналы подаются на базы транзисторов. Выходы подключены на входы таких же элементов. Схема рассчитывается так, чтобы при подаче высокого напряжения (соответствующей логической 1) на базу одного или нескольких транзисторов происходило насыщение транзисторов и выходной потенциал снижался до низкого уровня – остаточного потенциала U0= Uост.

Рис. 3.4. Основная логическая схема ТЛНС

Выходной потенциал соответствует логическому нулю, и все нагрузочные транзисторы оказываются запертыми. При подаче на входы транзисторов T1, Т2, Т3низкого потенциала, соответствующего логическому 0, все транзисторы запираются, потенциал их коллектора повышается, стремясь достигнуть уровня Ек. В этом случае последующие транзисторы отпираются, потому что потенциал выходного напряжения соответствует потенциалу базы насыщенного транзистора. Этот потенциал также соответствует логической 1. Таким образом, в положительной логике ТЛНС выполняет операцию дизъюнкции, реализуя на выходе функцию

Этот потенциал также соответствует логической 1. Таким образом, в положительной логике ТЛНС выполняет операцию дизъюнкции, реализуя на выходе функцию

Эта соответствует логической схеме ИЛИ – НЕ. Основным преимуществом элемента ТЛНС является его простота. Принципиальным недостатком является сильная зависимость процессов от характеристик транзисторов. Это проявляется, прежде всего, в изменении уровней сигналов с изменением числа входов и нагрузки.

Базовые токи коллекторов распределяются неравномерно вследствие разброса параметров транзисторов. Происходит перехват токов транзисторов. При этом большая часть тока источника Ек будет поступать в базу одного из транзисторов, а остальные режима насыщения не достигнут. Работа схем ТЛНС становится ненадежной.

Резисторно-транзисторная логика

Ненадежность работы ТЛНС послужила причиной поиска более совершенных вариантов. Появилась транзисторная логика с резистивной связью (ТЛРС и РТЛ). Принципиальным отличием является включение в базовые цепи транзисторов и резисторов с сопротивлением порядка 102 Ом (рис. 3.5). Наличие резисторов позволяет выравнивать входные токи в базовые цепи. Сопротивления резисторов RБiдолжны быть большими для выравнивания входных характеристик и одновременно достаточно малыми, чтобы не препятствовать насыщению транзисторов вследствие уменьшения тока базы. Этим противоречивым требованиям удовлетворяет некоторое оптимальное отношение RБ/Rк, при котором нагрузочная способность становится максимальной.

3.5). Наличие резисторов позволяет выравнивать входные токи в базовые цепи. Сопротивления резисторов RБiдолжны быть большими для выравнивания входных характеристик и одновременно достаточно малыми, чтобы не препятствовать насыщению транзисторов вследствие уменьшения тока базы. Этим противоречивым требованиям удовлетворяет некоторое оптимальное отношение RБ/Rк, при котором нагрузочная способность становится максимальной.

Рис. 3.5. Логическая схема РТЛ

Следует заметить также, что введение резисторов RБiуменьшает быстродействие схемы вследствие возрастания длительности фронта в ключе.

Схема реализует функцию

Резисторно-емкостная транзисторная логика

Для ослабления влияния сопротивления на быстродействие элемента целесообразно его шунтировать конденсатором небольшой емкости. Логика, в которой реализован этот принцип, получила название резистивно-емкостной транзисторной логики (РЕТЛ) (рис. 3.6).

3.6).

Рис. 3.6. Логическая схема РЕТЛ

Конструктивно такой конденсатор получают в виде обратносмещенного р–n-перехода. Во время переключения конденсатор закорачивает высокоомный резистор RБ, что приводит к образованию всплеска тока базы. Этот прием обеспечивает быстрейшее отпирание и запирание транзисторов. Оптимальное значение составляет при выполнении условия RБopt / Rк³10, что требует создания высокоомного резистора с большой площадью. Такие схемы использовались на первом этапе развития микроэлектроники. В итоге они оказались бесперспективными вследствие большого числа резисторов и емкостей, которые занимали большую площадь.

В результате было предложено все элементы, формирующие ток в базу, заменить одним инжектором (рис. 3.7).

Рис. 3.7. Эволюция ТЛНС (а) в И2Л путем подключения генераторов тока в базы (б)

Интегральная инжекционная логика

В ходе развития дискретной полупроводниковой электроники возникла принципиально новая ранее не известная логика – интегральная инжекционная логика (И2Л). В основе интегральной инжекционной логики лежат функционально интегрированные транзисторные структуры (рис. 3.8). Транзистор Т1называют токозадающим. Он состоит из инжектора И, который эмитирует носители заряда-дырки в эмиттерную область многоколлекторного транзистора Т3. Транзистор Т1представляет собой p1–n1–р2 и расположен горизонтально. Многоколлекторный инвертирующий транзистор Т3n2–р2–n1-типа расположен вертикально и имеет общий эмиттер Э. Эмиттерная область представляет собой сильно легированное основание подложки. Эмиттерная область транзистора Т3 одновременно служит базой токозадающего транзистора Т1.

В основе интегральной инжекционной логики лежат функционально интегрированные транзисторные структуры (рис. 3.8). Транзистор Т1называют токозадающим. Он состоит из инжектора И, который эмитирует носители заряда-дырки в эмиттерную область многоколлекторного транзистора Т3. Транзистор Т1представляет собой p1–n1–р2 и расположен горизонтально. Многоколлекторный инвертирующий транзистор Т3n2–р2–n1-типа расположен вертикально и имеет общий эмиттер Э. Эмиттерная область представляет собой сильно легированное основание подложки. Эмиттерная область транзистора Т3 одновременно служит базой токозадающего транзистора Т1.

Рис. 3.8. Конструкция (а) и схема (б) И2Л элемента логики

Инвертор включается тогда, когда ток инжектора Т1отбирается из базы многоколлекторного транзистора Т3в другую цепь, например предшествующей структуры в схеме. Такое включение может быть обеспечено за счет соответствующего уменьшения входного напряжения Uвx. Это напряжение одновременно управляет смещением на эмиттерном переходе инвертора Т3.

Это напряжение одновременно управляет смещением на эмиттерном переходе инвертора Т3.

Элемент И2Л обычно реализует функции ИЛИ – НЕ. Функция И – НЕ может быть реализована при условии использования коллекторных выходов в качестве независимых входов И для последующих логических элементов. Наличие многоколлекторного инвертора позволяет осуществить логическую развязку без дополнительных схемных элементов.

Логические уровни и логический перепад в схеме И2Л описываются как в ТЛНС и имеют подобные характеристики. Оригинальность схемотехнического решения сочетается с оригинальностью технологического решения.

Инжектор реализуется в виде длинной р-полоски, выполненной на этапе базовой диффузии. Базой р–n–р-транзистора является эпитаксиальный n-слой, а коллекторами – базовые слои n–р–n-транзисторов. Расположение р–n–р-транзисторов относительно инжектора может быть как перпендикулярным, так и параллельным.

Преимуществом И2Л является отсутствие изолирующих карманов и резисторов, приводящих к экономии площади, уменьшение напряжения питания, мощности и времени задержки. Малая емкость коллектора, малое остаточное напряжение на насыщенных транзисторах обусловлено низкоомным слоем n+-коллектора. Структуры с инжекционным питанием достаточно универсальны. Они могут использоваться для построения арифметических устройств, устройств памяти, логики. И2Л-схемы хорошо согласуются с ТТЛ и ДТЛ-схемами.

Малая емкость коллектора, малое остаточное напряжение на насыщенных транзисторах обусловлено низкоомным слоем n+-коллектора. Структуры с инжекционным питанием достаточно универсальны. Они могут использоваться для построения арифметических устройств, устройств памяти, логики. И2Л-схемы хорошо согласуются с ТТЛ и ДТЛ-схемами.

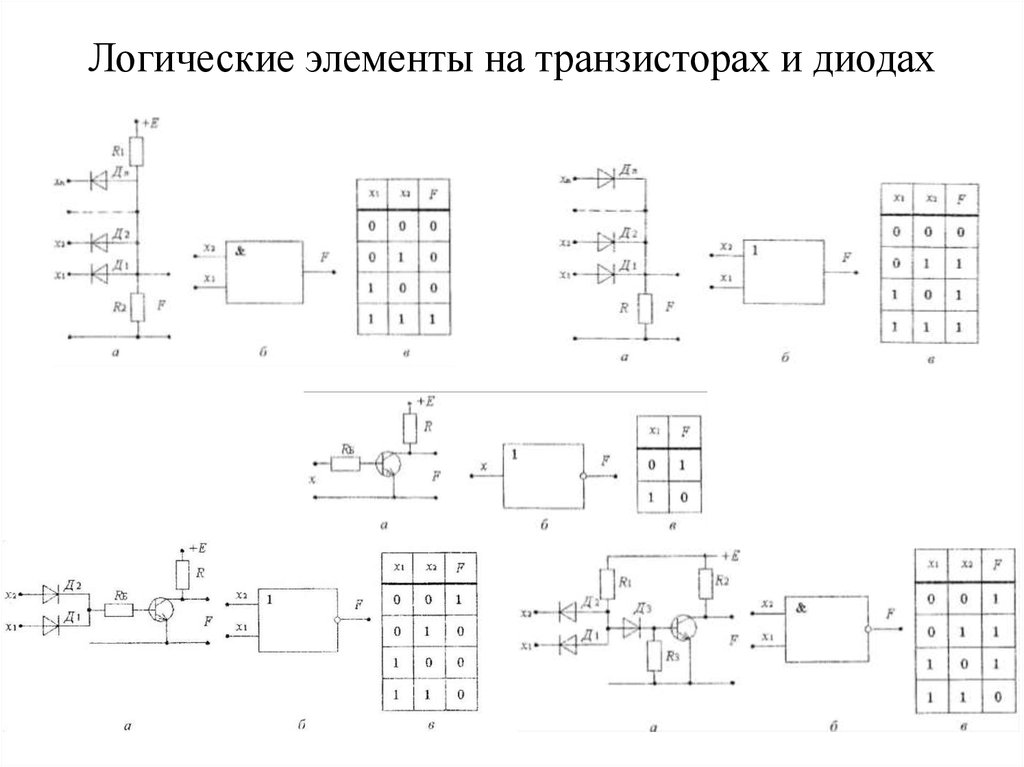

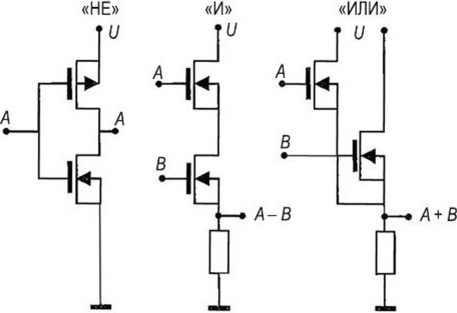

Как сделать логические элементы с использованием транзисторов

В этом посте мы узнаем, как создавать логические элементы НЕ, И, И-НЕ, ИЛИ и ИЛИ-НЕ с использованием дискретных транзисторов. Основное преимущество использования транзисторных логических элементов заключается в том, что они могут работать даже при напряжении до 1,5 В.

В некоторых электронных приложениях доступное напряжение может быть недостаточным для питания ТТЛ или даже КМОП ИС. Особенно это касается гаджетов, которые работают от батареек. Без сомнения, у вас всегда есть опция 3-вольтовой логической ИС. Тем не менее, они не всегда легко доступны для энтузиастов или экспериментаторов, и они не работают при напряжениях ниже определенных спецификаций (обычно ниже 2,5 вольт постоянного тока).

Кроме того, в приложении с батарейным питанием может быть место только для одной 1,5-вольтовой батареи. Ну, тогда что ты собираешься делать? Обычно логические вентили ИС могут быть заменены транзисторными логическими вентилями. Для каждого конкретного логического элемента обычно требуется всего пара транзисторов, а для типичной логики инвертора вентиля НЕ требуется всего один транзистор.

Содержание

Преимущества логических элементов на транзисторах

- Основные преимущества логических элементов на транзисторах можно резюмировать следующим образом:

- Транзисторы дешевле микросхем.

- Транзисторные логические элементы могут работать при напряжении всего 1,5 В, в то время как аналогам на ИС требуется минимум 3 В.

- Транзисторные логические элементы могут быть адаптированы для управления более тяжелыми нагрузками, чего логические элементы на основе ИС сделать не могут.

Полевые транзисторы по сравнению с биполярными транзисторами

Полевые транзисторы по сравнению с биполярными транзисторами: какой вариант лучше для низковольтных транзисторных логических схем? Одной из замечательных особенностей полевых транзисторов является то, что их сопротивление во включенном состоянии невероятно низкое. Кроме того, им нужен очень низкий ток включения затвора.

Кроме того, им нужен очень низкий ток включения затвора.

Однако у них есть одно ограничение в приложениях с крайне низким напряжением. Как правило, предел напряжения затвора составляет один вольт или около того. Кроме того, доступное напряжение может упасть ниже оптимального рабочего диапазона полевого транзистора, если к затвору подключен токоограничивающий или подтягивающий резистор.

И наоборот, биполярные переключающие транзисторы имеют преимущество в чрезвычайно низковольтных приложениях с одной батареей, поскольку для включения им требуется всего 0,6–0,7 В.

Кроме того, большинство распространенных полевых транзисторов, которые обычно продаются в пузырчатых упаковках в ближайшем магазине электроники, часто дороже, чем биполярные транзисторы. Кроме того, большой пакет биполярных транзисторов обычно можно было купить по цене пары полевых транзисторов.

Обращение с полевыми транзисторами требует значительно большей осторожности, чем обращение с биполярными транзисторами. Электростатические и общие экспериментальные ошибки делают полевые транзисторы особенно подверженными повреждениям. Сгоревшие компоненты могут испортить приятный творческий вечер экспериментов или инноваций, не говоря уже об эмоциональной боли отладки.

Электростатические и общие экспериментальные ошибки делают полевые транзисторы особенно подверженными повреждениям. Сгоревшие компоненты могут испортить приятный творческий вечер экспериментов или инноваций, не говоря уже об эмоциональной боли отладки.

Основы переключения транзисторов

В примерах логических схем, описанных в этой статье, используются биполярные NPN-транзисторы, поскольку они доступны по цене и не требуют специального обращения. Во избежание повреждения устройства или частей, поддерживающих его, перед подключением цепи необходимо принять соответствующие меры безопасности.

Несмотря на то, что наши схемы в основном основаны на транзисторах с биполярным переходом (BJT), они с таким же успехом могли бы быть построены с использованием технологии FET.

Базовая схема переключателя представляет собой простое приложение на транзисторе, которое является одной из самых простых конструкций.

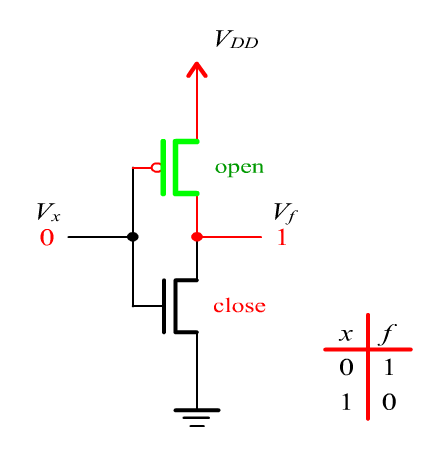

Создание вентиля НЕ с одним транзистором

Схема транзисторного переключателя показана на рис. 1. В зависимости от того, как он реализован в конкретном приложении, переключатель может рассматриваться либо как поддерживающий низкий уровень, либо как нормально разомкнутый.

1. В зависимости от того, как он реализован в конкретном приложении, переключатель может рассматриваться либо как поддерживающий низкий уровень, либо как нормально разомкнутый.

Простой инверторный логический элемент НЕ может быть создан с помощью простой схемы переключения, показанной на рис. 1 (где точка А является входом). Вентиль НЕ работает таким образом, что если на базу транзистора (точка A; Q1) не подается смещение постоянного тока, он останется закрытым, что приведет к высокому уровню или логической 1 (равному уровню V+) на выходе ( пункт Б).

Однако транзистор активируется, когда на базу Q1 подается надлежащее смещение, переводя выход схемы в низкий уровень или в логический 0 (почти равный нулю потенциал). Транзистор, обозначенный Q1, представляет собой биполярный транзистор общего назначения, или BC547, который обычно используется в маломощных коммутаторах и усилителях.

Подойдет любой эквивалентный ему транзистор (например, 2N2222, 2N4401 и т. д.). Значения резисторов R1 и R2 были выбраны для достижения компромисса между низким потреблением тока и совместимостью. Во всех конструкциях резисторы все 1/4 Вт, 5% единиц.

Во всех конструкциях резисторы все 1/4 Вт, 5% единиц.

Напряжение питания регулируется в диапазоне от 1,4 до 6 вольт постоянного тока. Обратите внимание, что схема может работать как буфер, когда нагрузочный резистор и выходное соединение смещены к эмиттеру транзистора.

Изготовление буферного затвора с использованием одного BJT BC547

Повторитель напряжения или буферный усилитель представляет собой тип конфигурации логического переключения, идентичный показанному на рис. 2. Следует отметить, что нагрузочный резистор и выходная клемма в этой схеме смещены с коллектора транзистора на его эмиттер. что является основным отличием этой конструкции от конструкции, показанной на рис. 1.

Функционирование транзистора также можно «перевернуть», переместив нагрузочный резистор и выходную клемму на другой конец биполярного транзистора.

Другими словами, когда на вход схемы не подается смещение, выход схемы остается низким; однако, когда на вход схемы подается смещение соответствующего напряжения, выход схемы становится высоким. (Это прямо противоположно тому, что происходит в предыдущей схеме.)

(Это прямо противоположно тому, что происходит в предыдущей схеме.)

Проектирование логических элементов с двумя входами с использованием транзисторов

Схема И с использованием двух транзисторов

На рис. пару буферов вместе с таблицей истинности для этого вентиля. Таблица истинности показывает, какими будут выходные результаты для каждого отдельного набора входных данных. Точки A и B используются как входы схемы, а точка C служит выходом схемы.

Из таблицы истинности важно отметить, что только один набор входных параметров приводит к высокому логическому выходному сигналу, тогда как все другие входные комбинации приводят к низкому логическому выходному сигналу. Выход логического элемента И на рисунке 3 остается немного ниже V+ после того, как он становится высоким.

Это происходит из-за падения напряжения между двумя транзисторами (Q1 и Q2).

Вентиль И-НЕ с использованием двух транзисторов

Другой вариант схемы на рис. 3 и соответствующая таблица истинности показаны на рис. 4. Схема превращается в вентиль И-НЕ путем сдвига выхода (точка C) и выходного резистора к верхнему транзистору ( Q1) коллектор.

4. Схема превращается в вентиль И-НЕ путем сдвига выхода (точка C) и выходного резистора к верхнему транзистору ( Q1) коллектор.

Поскольку и Q1, и Q2 должны быть включены, чтобы соединить низкий вывод резистора R1 с землей, потеря напряжения на выходе C незначительна.

Если для транзисторных логических элементов И или транзисторных логических элементов И-НЕ требуется более двух входов, в показанных конструкциях вполне можно подключить больше транзисторов, чтобы обеспечить три, четыре и т. д. входных логических элементов И или НЕ-И.

Однако, чтобы компенсировать потери напряжения на отдельных транзисторах, необходимо соответственно увеличить V+.

Логический элемент ИЛИ с использованием двух транзисторов

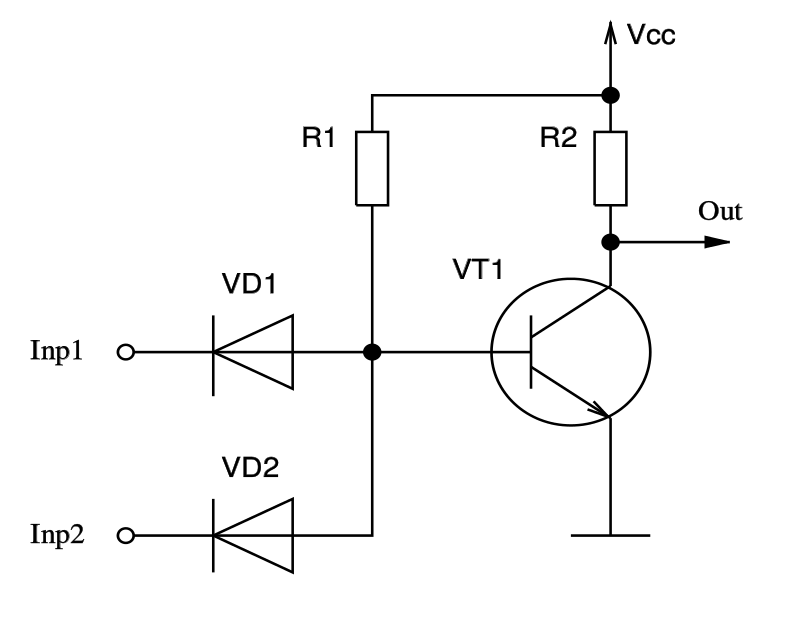

Другую форму логической схемы с двумя входами можно увидеть на рисунке 5 вместе с таблицей истинности схемы логического элемента ИЛИ.

На выходе схемы высокий уровень, когда на вход A или на вход B подается высокий уровень, однако из-за каскадного включения транзисторов падение напряжения превышает 0,5 В. Опять же, отображаемые цифры показывают, что напряжения и тока достаточно для работы следующего затвора транзистора.

Опять же, отображаемые цифры показывают, что напряжения и тока достаточно для работы следующего затвора транзистора.

Вентиль ИЛИ-НЕ с использованием двух транзисторов

На рис. 6 показан следующий вентиль в нашем списке, вентиль ИЛИ-НЕ с двумя входами, вместе с его таблицей истинности. Подобно тому, как вентили И и НЕ-И реагируют друг на друга, схемы ИЛИ и ИЛИ-НЕ делают то же самое.

Каждый из отображаемых затворов способен обеспечить достаточное количество энергии для активации по крайней мере одного или нескольких соседних транзисторных затворов.

Применение транзисторных логических вентилей

Что вы будете делать с описанными выше цифровыми схемами, которыми вы теперь владеете? Все, что вы могли бы сделать с обычными вентилями TTL или CMOS, но не беспокоясь об ограничениях напряжения питания. Вот несколько применений транзисторно-логических вентилей в действии.

Цепь демультиплексора

Демультиплексор 1-из-2 с тремя логическими элементами НЕ и двумя схемами НЕ-И показан на рис. 7. Соответствующий выход выбирается с использованием однобитового «адресного ввода», который может быть либо ВЫХОД1, либо ВЫХОД2, в то время как управляющая информация подается на схему с помощью входа DATA.

7. Соответствующий выход выбирается с использованием однобитового «адресного ввода», который может быть либо ВЫХОД1, либо ВЫХОД2, в то время как управляющая информация подается на схему с помощью входа DATA.

Схема работает наиболее эффективно, когда скорость передачи данных поддерживается ниже 10 кГц. Функциональность схемы проста. На вход DATA подается требуемый сигнал, который включает Q3 и инвертирует входящие данные на коллекторе Q3.

На выходе Q1 устанавливается высокий уровень, если на входе ADDRESS низкий уровень (заземлен или сигнал отсутствует). На коллекторе Q1 высокий выход делится на два пути. В первом пути выход Q1 подается на базу Q5 (одна из двух входных ветвей логического элемента И-НЕ), включая его и, следовательно, «активируя» логический элемент И-НЕ, состоящий из Q4 и Q5.

Во втором пути высокий уровень с выхода Q1 одновременно подается на вход другого вентиля НЕ (Q2). После двойной инверсии выход Q2 становится низким. Этот низкий уровень подается на базу Q7 (одна клемма второго логического элемента И-НЕ, состоящего из Q6 и Q7), тем самым отключая схему И-НЕ.

Любая информация или сигнал, подаваемые на вход ДАННЫЕ, поступают на ВЫХОД1 при этих обстоятельствах. В качестве альтернативы, ситуация обратная, если на вход ADDRESS подается сигнал высокого уровня. Это означает, что любая информация, предоставленная схеме, будет отображаться на ВЫХОДЕ2, поскольку логический элемент И-НЕ Q4/Q5 отключен, а логический элемент И-НЕ Q6/Q7 включен.

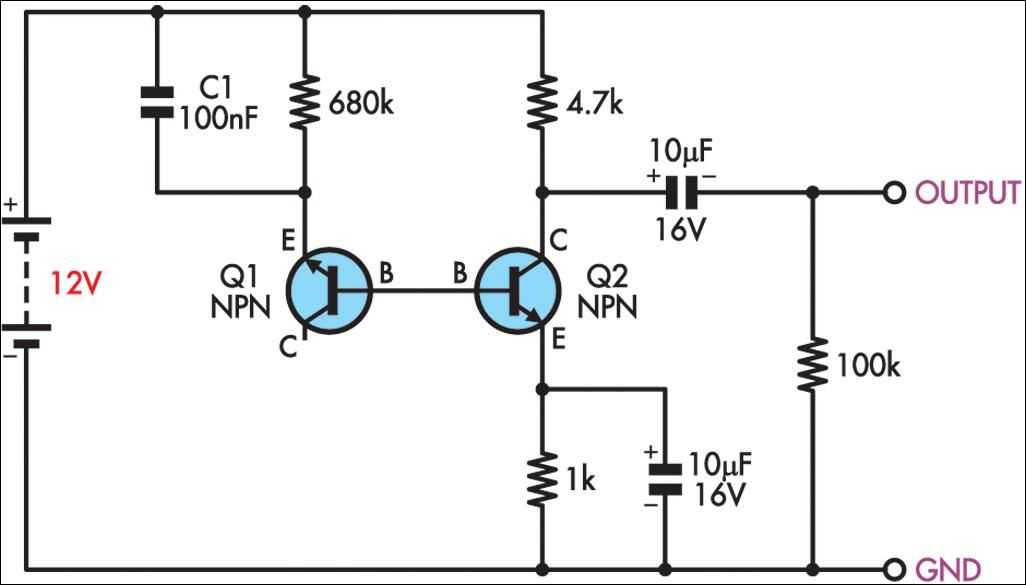

Генераторная схема (тактовый генератор)

Наше следующее применение транзисторного логического элемента, показанное на рис. 8, представляет собой базовый тактовый генератор (также известный как осциллятор), состоящий из трех обычных инверторов затвора НЕ (один из которых смещен с помощью резистор обратной связи R2, который переводит его в аналоговую область).

Для выравнивания выходного сигнала включен третий логический элемент НЕ (Q3), который обеспечивает дополнение к выходному сигналу генератора. Значение C1 может быть увеличено или уменьшено для изменения рабочей частоты схемы. Выходной сигнал имеет частоту около 7 кГц с напряжением V+ 1,5 В постоянного тока при использовании указанных значений компонентов.

Выходной сигнал имеет частоту около 7 кГц с напряжением V+ 1,5 В постоянного тока при использовании указанных значений компонентов.

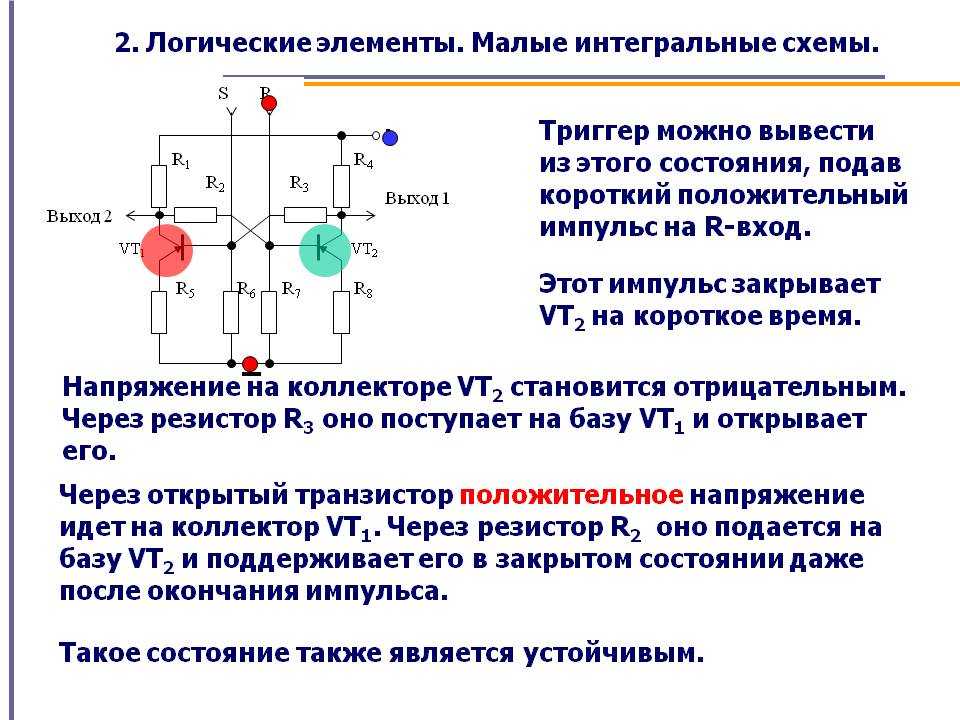

Схема защелки RS

На рис. 9 показана наша последняя прикладная схема, защелка RS, состоящая из двух логических элементов NOR. Чтобы обеспечить исправную выходную мощность на выходах Q и Q, резисторы R3 и R4 настроены на 1 кОм.

Таблица истинности защелки RS отображается рядом со схемой. Это всего лишь несколько иллюстраций нескольких надежных низковольтных цифровых схем с логическими элементами, которые могут быть созданы с использованием отдельных транзисторов.

Для схем, использующих транзисторную логику, требуется слишком много деталей

Многие проблемы можно решить, используя все эти низковольтные логические схемы на транзисторах. Однако использование слишком большого количества этих транзисторных затворов может привести к новым проблемам.

Количество транзисторов и резисторов может стать довольно большим, если приложение, которое вы создаете, содержит большое количество вентилей, занимающих ценное пространство.

Использование массивов транзисторов (множество транзисторов, заключенных в пластик) и резисторов SIP (Single Inline Package) вместо отдельных блоков является одним из способов решения этой проблемы.

Описанный выше подход может сэкономить массу места на печатной плате, сохраняя при этом производительность, равную производительности их полноразмерных аналогов. Транзисторные массивы предлагаются в корпусах для поверхностного монтажа, 14-выводных сквозных отверстий и четырехъядерных упаковках.

Для большинства схем смешивание типов транзисторов может быть вполне приемлемым.

Тем не менее, рекомендуется, чтобы экспериментатор работал с одним типом транзистора для построения транзисторных логических схем (имеется в виду, что если вы создаете секцию логического элемента с помощью BC547, то попробуйте использовать тот же биполярный транзистор для создания других оставшихся схем). .

Причина в том, что различные варианты транзисторов могут иметь несколько разные свойства и, следовательно, вести себя по-разному.

Например, для одного транзистора базовый предел включения может быть больше или меньше другого, или общий коэффициент усиления по току может быть немного больше или меньше.

С другой стороны, стоимость покупки большой коробки одного типа транзистора также может быть ниже. Производительность ваших схем повысится, если ваши логические элементы будут построены с использованием соответствующих транзисторов, и в конечном итоге проект в целом будет более полезным.

Транзисторная логика с прямой связью (DCTL) — Логические вентили

Логические вентили

Транзисторные цифровые схемы в основном выполняют три логических

функции стробирования И (или НЕ-И), стробирования ИЛИ (или НЕ-ИЛИ) и инверсии сигнала

(НЕ ворота). Дополнительная функция

обычно выполняемая, хотя и не логическая по своему характеру, но тем не менее практическая

необходимостью является усиление сигнала. Другие логические блоки, такие как NOR, NAND,

и триггеры, легко получить, используя эти три фундаментальных функционала

блоки. Для этих целей можно использовать несколько различных конфигураций цепей.

функциональные блоки. Обычно эти цепи классифицируются в соответствии с

элементы, используемые для межкаскадной связи или связи между затворами и инверторами

и усилители. Наиболее часто используемыми элементами связи являются диоды,

резисторы, комбинации резистор-конденсатор и сами транзисторы.

Также можно проектировать и использовать схемы без какой-либо из этих связей.

элементы. Такие схемы называются транзисторно-логическими с прямой связью.

цепи или, чаще, DCTL. Есть несколько преимуществ и некоторые

недостатки DCTL, и мы рассмотрим их после обсуждения того, как этот тип

конфигурационных работ.

Для этих целей можно использовать несколько различных конфигураций цепей.

функциональные блоки. Обычно эти цепи классифицируются в соответствии с

элементы, используемые для межкаскадной связи или связи между затворами и инверторами

и усилители. Наиболее часто используемыми элементами связи являются диоды,

резисторы, комбинации резистор-конденсатор и сами транзисторы.

Также можно проектировать и использовать схемы без какой-либо из этих связей.

элементы. Такие схемы называются транзисторно-логическими с прямой связью.

цепи или, чаще, DCTL. Есть несколько преимуществ и некоторые

недостатки DCTL, и мы рассмотрим их после обсуждения того, как этот тип

конфигурационных работ.

Инверторы DCTL

На рисунке ниже показаны три инвертора DCTL в каскаде. В этой цепи

коллекторные резисторы R 1 , R 2 ,

и R 3 служат источниками постоянного тока.

Они подают ток на коллекторы соответствующих транзисторов, когда

они включены или к базе следующего транзистора, когда они выключены.

Инверторы DCTL в каскаде.

При входном напряжении В в на базе Q 1 находится близко к земле, то есть на V CE(SAT) предыдущего каскада на транзисторе — напряжение v C1 стремится приблизиться к напряжению питания В СС . Подается ток к основанию Q 2 через R 1 , и получается Q 2 вкл. Зажимное действие диода база-эмиттер Q 2 вмещает v C1 при значении, определяемом В ВЕ2 . Так как Q 2

В таком случае v C1 будет поддерживать Q 2 выключение, что в свою очередь

включит Q 3 . Из этого краткого описания несколько

заметны важные моменты. Низкий

В таком случае v C1 будет поддерживать Q 2 выключение, что в свою очередь

включит Q 3 . Из этого краткого описания несколько

заметны важные моменты. Низкий Затвор серии DCTL

На рисунке ниже показаны три транзистора, соединенные последовательно, чтобы сформировать вентиль И-НЕ. для положительных входных сигналов A, B и C. Если какой-либо из трех транзисторов выключен,

выходное напряжение на D будет напряжением питания ( В СС ) в

ненагруженном состоянии. В нагруженных условиях напряжение на D будет зависеть

на резисторе Р Л и В БЭ(ОН) транзистор следующей ступени. Когда все три транзистора открыты, потенциал на D

будет ближе к земле, чем в предыдущем случае, и будет

сумма

для положительных входных сигналов A, B и C. Если какой-либо из трех транзисторов выключен,

выходное напряжение на D будет напряжением питания ( В СС ) в

ненагруженном состоянии. В нагруженных условиях напряжение на D будет зависеть

на резисторе Р Л и В БЭ(ОН) транзистор следующей ступени. Когда все три транзистора открыты, потенциал на D

будет ближе к земле, чем в предыдущем случае, и будет

сумма

.

DCTL Параллельный вентиль

На рисунке ниже показан параллельный вентиль DCTL, который на самом деле был ранее считается «инверторным» каскадом с тремя транзисторами, имеющими отдельные входы вместо одного транзистора. Очевидно, что эта конфигурация схема NOR. Если какой-либо вход любого из трех транзисторов имеет высокий уровень, его коллектор будет потреблять ток через нагрузочный резистор, в результате чего на выходе идти низко.

Параллельный шлюз DCTL.

Недостатки DCTL

Current Hogging

Одной из наиболее нежелательных особенностей DCTL является то, что обычно называют

токосъем, и это явление возникает из-за распространения в

Если транзисторы Q 1 , Q 2 , и Q 3 на рисунке ниже (вид A) имеют входные характеристики как

показано на рисунке ниже (вид Б), совершенно ясно, что выходное напряжение

размах В

Инвертор DCTL, управляющий разветвлением трех ворот. (А) Цепь. (B) Входные характеристики транзисторов разветвления.

Проблема перекрестных помех или шума

В любой высокоскоростной системе импульсы с быстрым

разность потенциалов в системе заземления в основном из-за индуктивности заземления.

Эти напряжения могут мешать стабильной работе системы.

Системы DCTL очень чувствительны к этим шумовым напряжениям, потому что

рабочее и сигнальное напряжения в этих системах, естественно, низкие. Если

несколько транзисторов на одном конце системы заземления включены,

результирующий импульс, генерируемый в наземной системе, может дать положительный

или отрицательный импульс (в зависимости от полярности), что может привести к неисправности

включение или выключение других транзисторов дальше по земле

система. Одним из решений является установка транзисторов очень близко друг к другу,

тем самым сводя к минимуму индуктивность заземления. Помимо шума от земли, DCTL также

уязвим к шуму в источниках питания и постороннему шуму, возникающему при подключении

ведет.