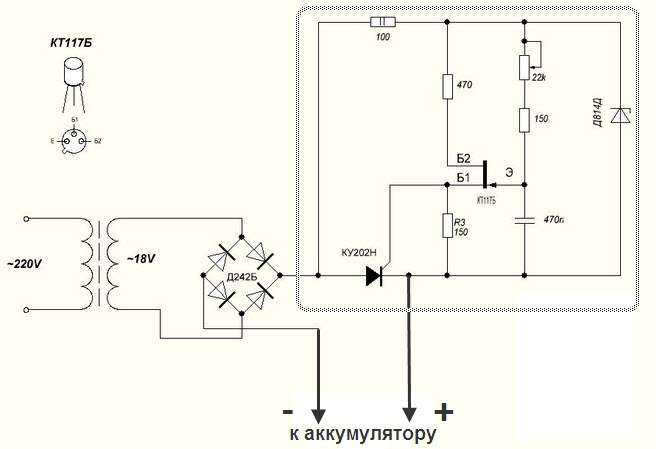

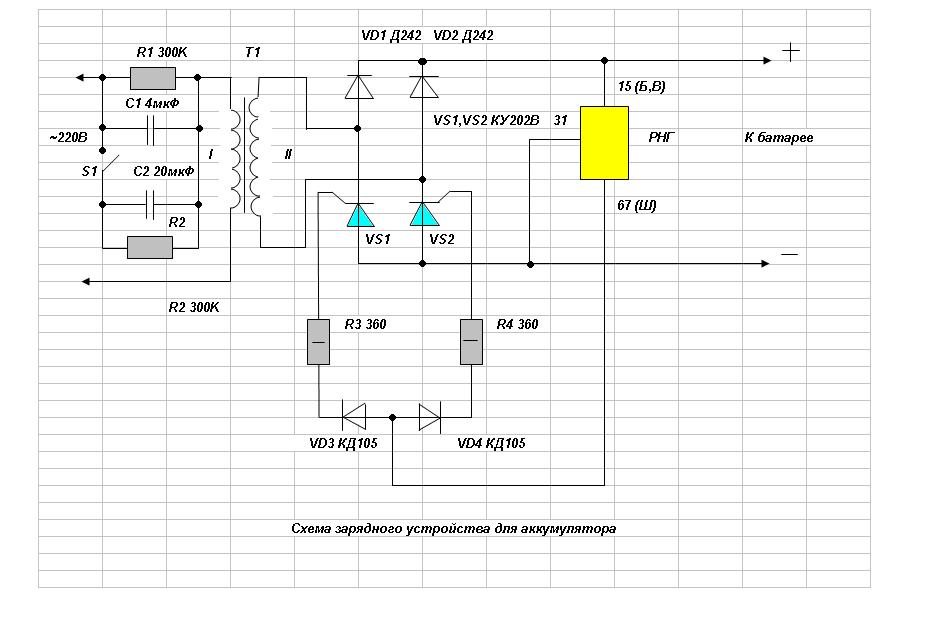

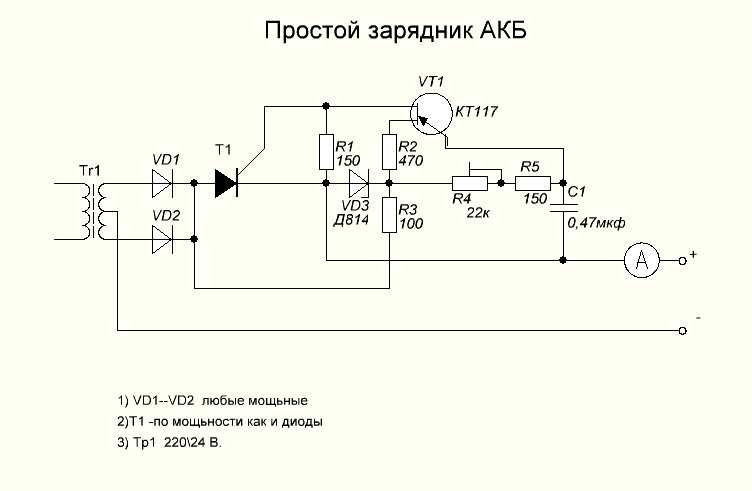

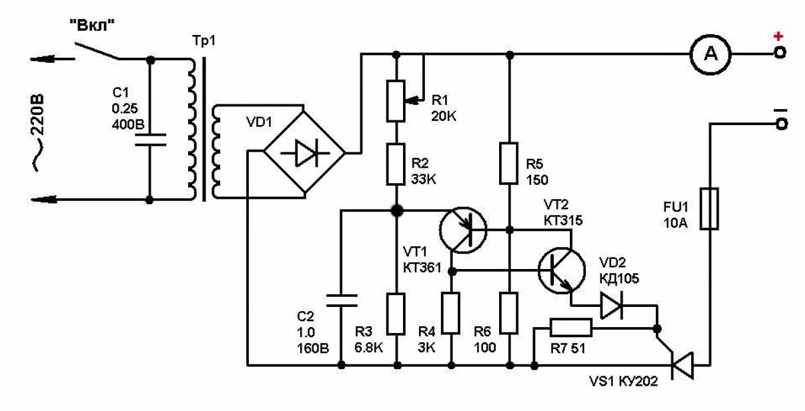

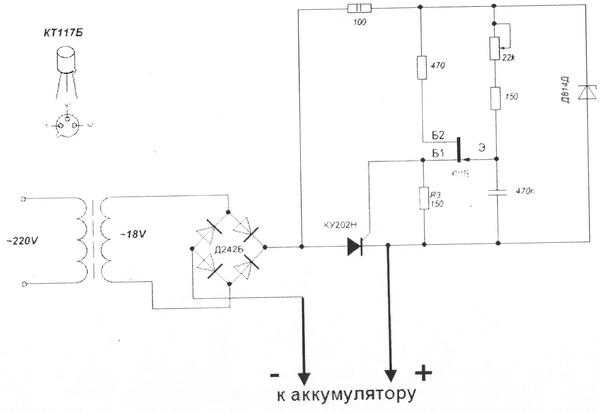

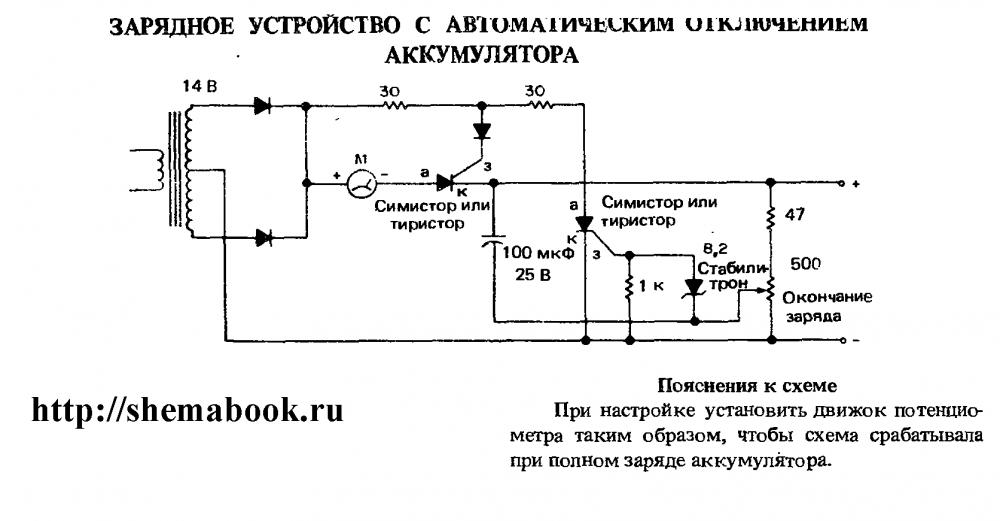

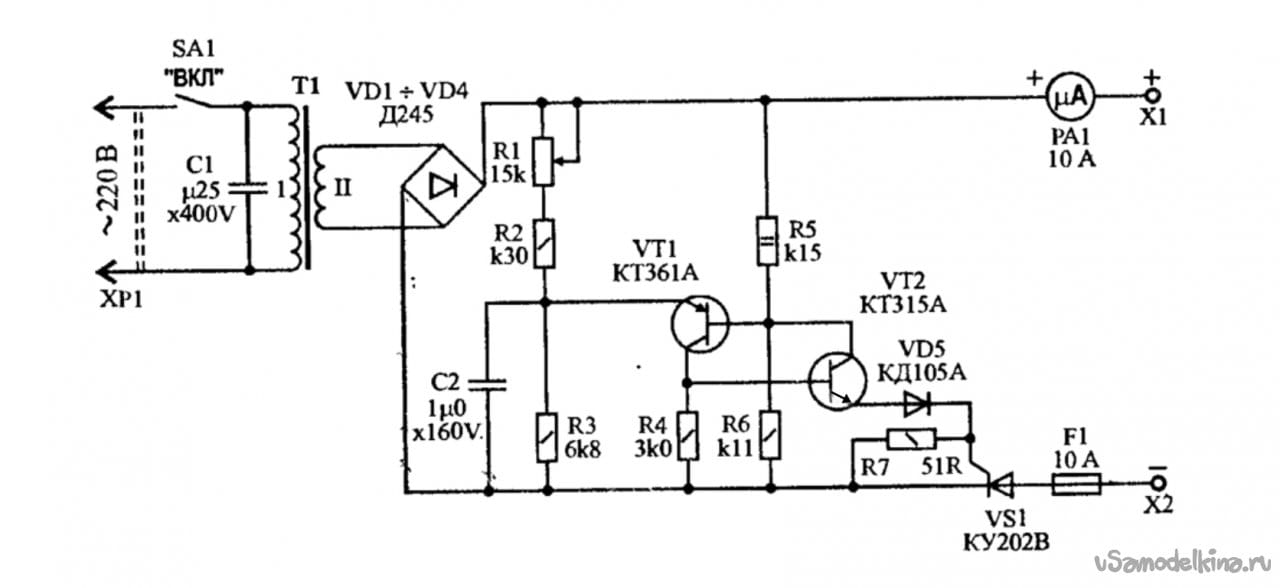

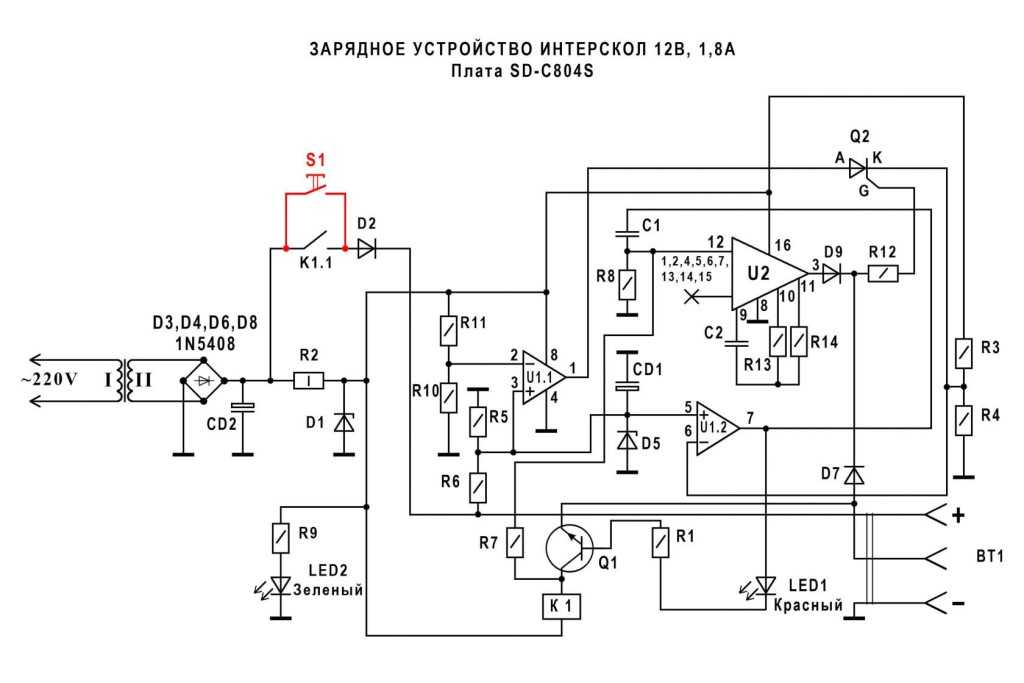

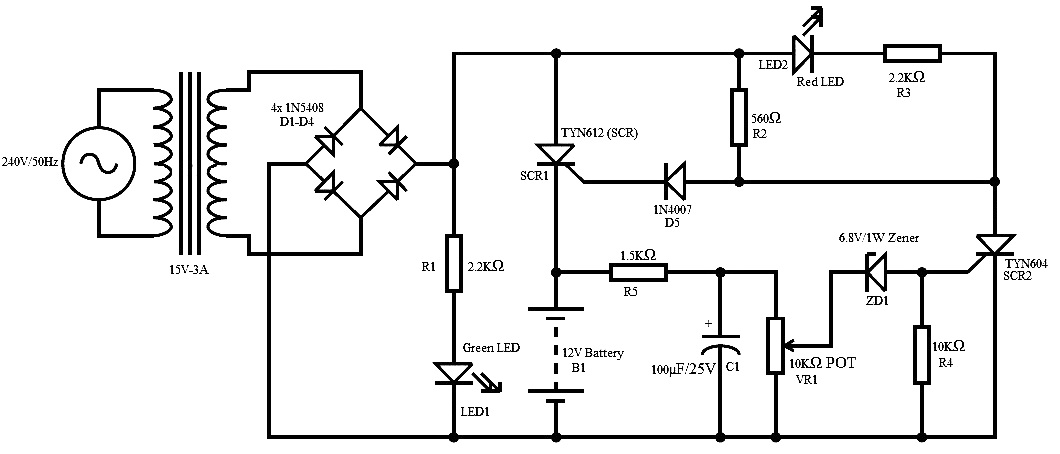

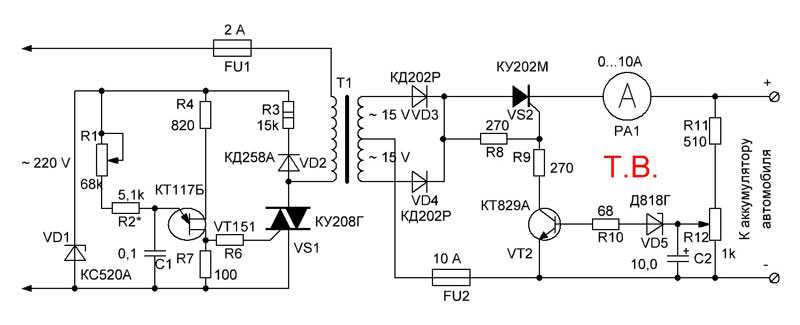

Схема зарядного устройства

Зарядное устройство для аккумуляторов – сложное высокотехнологичное устройство. Давайте рассмотрим его начинку на примере ЗУ от GoPower

Назначение

Казалось бы – ну что тут расписывать. Восстанавливает емкость АКБ. Все. Но не в случае с зарядными устройствами фирмы GoPower. У бренда есть профессиональное кредо – выпускать актуальную (и качественную при этом!) продукцию, востребованную на рынке. А для этого модели тех же ЗУ должны быть если и не универсальными, то уж точно – с расширенным функционалом. Зарядные от GoPower способны на многое:

· Сами отключают зарядный ток при наборе аккумулятором пиковой емкости.

· Предотвращают выгорание внутренних цепей от КЗ и при переполюсовке.

· При избыточном нагреве или превышающей номинал нагрузке отключают АКБ от сети.

· Ограничивают продолжительность зарядки по времени.

· Выполняют тренировочный цикл заряд/разряд для восстановления емкости старых аккумуляторов.

· Самостоятельно определяют тип батареи и многое другое.

При этом поддерживается работа с разными типами АКБ (зависит от моделей ЗУ). Краткий список форматов и конструкций аккумуляторов, которые можно заряжать с помощью GoPower:

|

Серия ЗУ |

Тип АКБ |

Формфактор батарей |

|

ProLab |

Свинцово-кислотные |

корпусные AGM VRLA |

|

iClever |

Ni-Cd, Ni-MH |

АА, ААА |

|

Basic |

Ni-Cd, Ni-MH |

АА, ААА |

|

LiCharger |

Ni-Cd, Ni-MH, Li-ion IMR/INR/ICR |

28 популярных типоразмеров |

|

Genius |

Ni-Cd, Ni-MH, Li-ion IMR/INR/ICR, LiFePO4 |

28 популярных типоразмеров |

Универсальность двух последних серий реализована благодаря подпружиненному разъему.

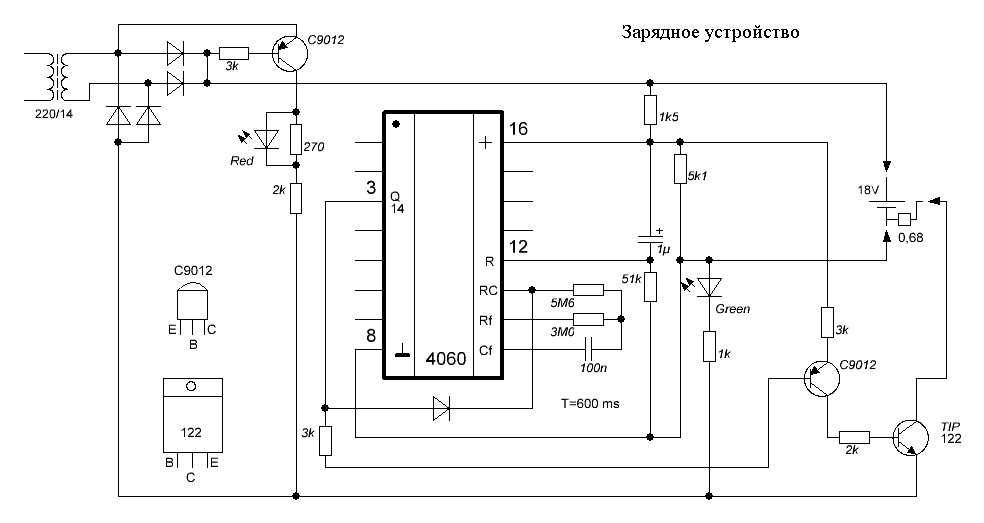

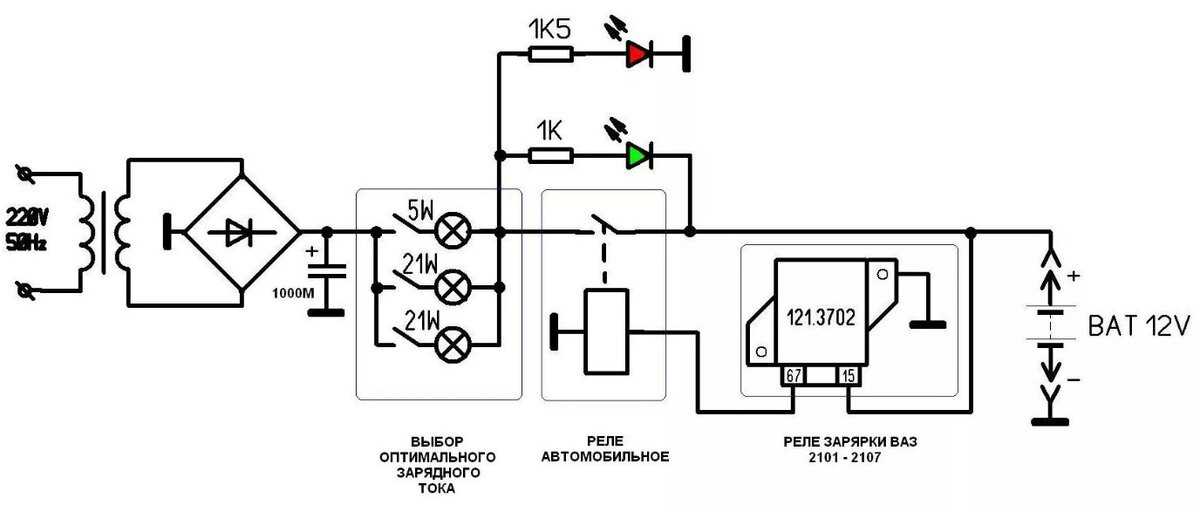

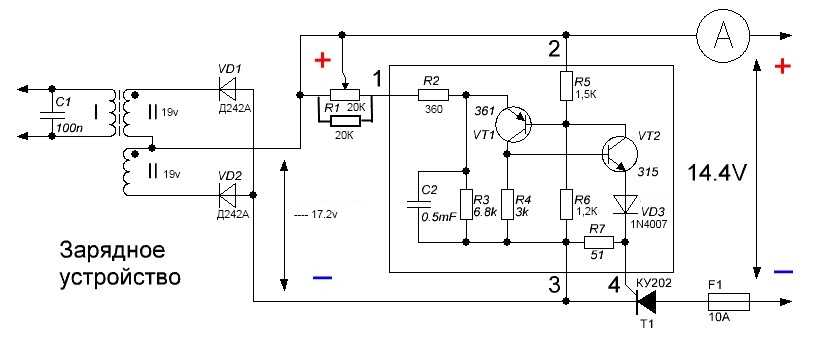

Как устроено ЗУ – схема

Только серия ProLab имеет подключение к бытовой электросети. Всем остальным зарядным для эффективной работы достаточно DC 5 В. Сегодня эти параметры есть у порта USB, который сейчас встречается повсеместно, даже в автомобилях. В этом случае подключение осуществляется с помощью дата-кабеля micro-USB или Type C.

В любом случае напряжение и ток преобразуются в соответствующие величины. За это отвечает встроенный контроллер, собранный на микросхемах. Во всех ЗУ также присутствуют необходимые защитные контуры, препятствующие порче АКБ от перезаряда, КЗ и перегрева.

Во всех приборах есть диодный сигнализатор процесса зарядки, за исключением Genius. Это самая передовая модель бренда, в ней реализован информативный дисплей, отображающий:

· длительность процесса;

· тип выполняемой операции;

· текущие параметры АКБ;

· температуру элемента и др.

Чтобы заказать зарядное устройство фирмы, перейдите в соответствующий каталог GoPower и сделайте выбор. Вас порадуют цены от производителя, наличие гарантии (18 месяцев) и качество продукта.

Взрыв-схема и запчасти для зарядного устройства УЗ 15

Скачать

Скачать Каталог Elitech 2023

Скачать Каталог Elitech Promo 2022

Скачать Расходные материалы и оснастка 2022

Заявка на запчасти Осторожно, мошенники!

Отправить заявку на заказ запчастейЗаказ запчастей Elitech

Ваше имя*

Имя контактного лица

Ваш телефон*

Телефон для связи

Перечень запчастей*

Список запчастей для заказа, через запятую

Ваш Email*

Адрес электронной почты

Город*

Информация об адресе заказа

Список взрыв схем и запчастей| № | Код Elitech | Наименование | Описание (англ. ) ) | Комплектация | Совместимость |

| 1 | 1901.000100 | Винт | SCREW | 2 | УЗ10, УЗ20/12, УЗ30/20, УЗ50/30 |

| 2 | 1901.000200 | Шайба | PLAINWASHER | 4 | УЗ10, УЗ20/12, УЗ30/20, УЗ50/30 |

| 3 | 1901.005000 | Накладка передней панели | PALSTIC PANEL | 1 | УЗ20/12 |

| 4 | 1901.005100 | Кобельный ввод | RUBBER | 2 | УЗ20/12, УЗ30/20, УЗ50/30 |

| 5 | 1901.000500 | Амперметр | AMPEREMETER | 1 | УЗ10, УЗ20/12 |

| 6 | 1901.000600 | Гнездо предохранителя | FUSE HOLD | 1 | УЗ10, УЗ20/12 |

| 7 | 1901.002500 | Зажимы | CLAMP | 2 | УЗ10, УЗ20/12, УЗ30/20, УЗ50/30 |

| 8 | 1901.002600 | Электрокабель питания | PLUG CABLE | 1 | УЗ10 |

| 9 | 1901. 005200 005200 | Панель передняя | FRONT PANEL | 1 | |

| 10 | 1901.000800 | Выключатель | SWITCH | 1 | УЗ10, УЗ20/12, УЗ30/20, УЗ50/30 |

| 11 | 1901.000900 | Винт | SCREW | 2 | УЗ10, УЗ20/12, УЗ30/20, УЗ50/30 |

| 12 | 1901.001000 | Мост выпрямительный | BRIDGE RECTIFIER | 1 | УЗ10 |

| 13 | 1901.001100 | Шайба пружинная | SPRING WASHER | 2 | УЗ10, УЗ20/12, УЗ30/20, УЗ50/30 |

| 14 | 1901.001200 | Гайка | SCREW | 2 | УЗ10, УЗ20/12, УЗ30/20, УЗ50/30 |

| 15 | 1901.001300 | Винт | SCREW | 3 | УЗ10, УЗ20/12, УЗ30/20, УЗ50/30 |

| 16 | 1901.001400 | Ручка | HANDLE BELT | 1 | УЗ10, УЗ20/12, УЗ30/20, УЗ50/30 |

| 17 | 1901.001500 | Крепления ручки | HANDLE BUTTON | 2 | УЗ10, УЗ20/12, УЗ30/20, УЗ50/30 |

| 18 | 1901. 005300 005300 | Корпус | TOP COVER | 1 | |

| 19 | 1901.001700 | Винт | SCREW | 10 | УЗ10, УЗ20/12, УЗ30/20, УЗ50/30 |

| 20 | 1901.001800 | Панель задняя | BACK PANEL | 1 | УЗ10 |

| 21 | 1901.005400 | Трансформатор | TRANSFORMER | 1 | |

| 22 | 1901.005500 | Винт | SCREW | 4 | УЗ20/12, УЗ30/20, УЗ50/30 |

| 23 | 1901.005600 | Шайба пружинная | SPRING WASHER | 4 | УЗ20/12, УЗ30/20, УЗ50/30 |

| 24 | 1901.005700 | Шайба | PLAINWASHER | 4 | УЗ20/12, УЗ30/20, УЗ50/30 |

| 25 | 1901.005800 | Винт | SCREW | 4 | УЗ20/12, УЗ30/20,УЗ50/30, УПЗ30/120, УПЗ50/180, УПЗ320/180, УПЗ 400/240, УПЗ600/540 |

| 26 | 1901.005900 | Ножка резиновая | BASE RUBBER | 4 | УЗ10, УЗ20/12 |

| 27 | 1901. 002300 002300 | Винт | SCREW | 2 | УЗ10 |

| 28 | 1901.006000 | Основание | BASE PANEL | 1 |

Схемы памяти — справочник Digilent

Компания NI

- Внутренние инструменты

Содержание

- Схемы памяти

- Бистабильная схема

- Важные идеи

Схемы памяти функционируют, сохраняя напряжение, присутствующее во входном сигнале, всякий раз, когда они запускаются управляющим сигналом. Они сохраняют это сохраненное напряжение до следующего утверждения управляющего (или триггерного) сигнала. Между утверждениями управляющего сигнала входной сигнал игнорируется, а выход приводится к последнему сохраненному напряжению.

Сегодня используются два основных семейства схем памяти: динамическая память и статическая память. Ячейки динамической памяти используют небольшой конденсатор для хранения напряжения сигнала, и они используются в самых маленьких и дешевых схемах памяти. Поскольку напряжение на конденсаторе со временем снижается, ячейки динамической памяти необходимо периодически обновлять, иначе они потеряют свое сохраненное значение. Хотя это требование обновления приводит к значительным накладным расходам, ячейки динамической памяти очень малы, поэтому они стали наиболее широко используемыми из всех схем памяти.

Многие электронные устройства содержат цифровые системы, которые используют схемы памяти для определения своего рабочего состояния. На самом деле любое электронное устройство, которое может создать последовательность событий или отреагировать на нее, должно иметь память. Примеры таких устройств включают часы и таймеры, контроллеры бытовой техники, игровые устройства и вычислительные устройства. Если цифровая система содержит N устройств памяти, и каждое устройство памяти хранит «1» или «0», то рабочее состояние системы может быть определено N-битным двоичным числом. Кроме того, цифровая система с N запоминающими устройствами должна находиться в одном из 2N состояний, где каждое состояние однозначно идентифицируется двоичным числом, созданным из совокупного содержимого всех запоминающих устройств в системе.

Примеры таких устройств включают часы и таймеры, контроллеры бытовой техники, игровые устройства и вычислительные устройства. Если цифровая система содержит N устройств памяти, и каждое устройство памяти хранит «1» или «0», то рабочее состояние системы может быть определено N-битным двоичным числом. Кроме того, цифровая система с N запоминающими устройствами должна находиться в одном из 2N состояний, где каждое состояние однозначно идентифицируется двоичным числом, созданным из совокупного содержимого всех запоминающих устройств в системе.

В любой момент времени двоичное число, хранящееся во внутренней памяти устройства, определяет текущее состояние цифровой системы. Входные данные, которые поступают в цифровую систему, могут вызвать изменение состояния содержимого одного или нескольких запоминающих устройств (с «1» на «0» или наоборот), тем самым вызывая изменение состояния цифровой системы. Таким образом, изменение состояния цифровой системы или переход состояния происходит всякий раз, когда изменяется двоичное число, хранящееся во внутренней памяти.

Бистабильная схема

В цифровой инженерии мы имеем дело с двухуровневыми или бистабильными схемами памяти. Бистабильные схемы имеют два стабильных рабочих состояния: состояние, когда на выходе есть логическая «1» (или Vdd), и состояние, когда на выходе есть «0» (или  Схемы памяти спроектированы таким образом, что они не могут бесконечно оставаться в нестабильном состоянии; как только они входят в нестабильное состояние, они немедленно пытаются восстановить одно из двух стабильных состояний.

Схемы памяти спроектированы таким образом, что они не могут бесконечно оставаться в нестабильном состоянии; как только они входят в нестабильное состояние, они немедленно пытаются восстановить одно из двух стабильных состояний.

Рисунок 1 выше дает адекватную аналогию. Здесь шарик представляет значение, хранящееся в памяти, а «холм» представляет нестабильную область, которую необходимо пересечь, прежде чем схема памяти сможет перейти к сохранению противоположного значения. Обратите внимание, что в этой аналогии существует третье потенциальное стабильное состояние — с нужным количеством энергии можно было бы сбалансировать мяч прямо на вершине холма. Точно так же схемы памяти также имеют третье потенциально стабильное состояние, где-то между двумя стабильными состояниями. Когда схемы памяти переходят между двумя стабильными состояниями, важно убедиться, что в схему передается достаточно энергии, чтобы обеспечить пересечение нестабильной области.

Оба состояния «0» и «1» в бистабильной схеме легко поддерживаются после их достижения. Управляющий сигнал, который заставляет схему изменять состояния, должен передавать некоторое минимальное количество энергии, чтобы перевести схему в нестабильное состояние. Если вход, вызывающий переход из одного устойчивого состояния в другое, обеспечивает энергию, превышающую минимально необходимую, то переход происходит очень быстро. Если управляющий сигнал выдает меньше минимально необходимой энергии, то схема возвращается в исходное стабильное состояние. Но если на вход подается неправильное количество энергии — достаточное, чтобы начать переход, но недостаточное, чтобы быстро протолкнуть его через нестабильную область, — тогда схема может временно «застрять» в нестабильной области. Схемы памяти спроектированы таким образом, чтобы свести к минимуму эту возможность и уменьшить количество времени, в течение которого схема может оставаться в нестабильном состоянии, если она туда попадет (по аналогии, представьте себе остроконечную вершину в нестабильной области с очень высокой скоростью).

Управляющий сигнал, который заставляет схему изменять состояния, должен передавать некоторое минимальное количество энергии, чтобы перевести схему в нестабильное состояние. Если вход, вызывающий переход из одного устойчивого состояния в другое, обеспечивает энергию, превышающую минимально необходимую, то переход происходит очень быстро. Если управляющий сигнал выдает меньше минимально необходимой энергии, то схема возвращается в исходное стабильное состояние. Но если на вход подается неправильное количество энергии — достаточное, чтобы начать переход, но недостаточное, чтобы быстро протолкнуть его через нестабильную область, — тогда схема может временно «застрять» в нестабильной области. Схемы памяти спроектированы таким образом, чтобы свести к минимуму эту возможность и уменьшить количество времени, в течение которого схема может оставаться в нестабильном состоянии, если она туда попадет (по аналогии, представьте себе остроконечную вершину в нестабильной области с очень высокой скоростью). Крутые склоны). Если запоминающее устройство застревает в нестабильном состоянии слишком долго, его выходной сигнал может колебаться или оставаться на полпути между «0» и «1», что приводит к непреднамеренному и часто непредсказуемому поведению цифровой системы. Устройство памяти, застрявшее в нестабильной области, называется метастабильным, а все устройства памяти страдают от возможности перехода в метастабильное состояние (подробнее о метастабильности будет сказано позже).

Крутые склоны). Если запоминающее устройство застревает в нестабильном состоянии слишком долго, его выходной сигнал может колебаться или оставаться на полпути между «0» и «1», что приводит к непреднамеренному и часто непредсказуемому поведению цифровой системы. Устройство памяти, застрявшее в нестабильной области, называется метастабильным, а все устройства памяти страдают от возможности перехода в метастабильное состояние (подробнее о метастабильности будет сказано позже).

Схема со статической памятью требует обратной связи, а любая схема с обратной связью имеет память (до сих пор мы имели дело только с комбинационными схемами с прямой связью без памяти). Любая логическая схема может иметь обратную связь, если выходной сигнал просто «подается обратно» и подключается к входу. Большинство цепей обратной связи не будут демонстрировать полезного поведения — они будут либо моностабильными (т. е. застрявшими в выходном состоянии «1» или «0»), либо будут бесконечно колебаться. Некоторые схемы обратной связи будут бистабильными и управляемыми, и эти схемы являются кандидатами на роль простых схем памяти. Простые схемы обратной связи показаны на рис. 2 ниже, и они помечены как управляемые/неуправляемые и бистабильные/небистабильные.

Простые схемы обратной связи показаны на рис. 2 ниже, и они помечены как управляемые/неуправляемые и бистабильные/небистабильные.

Важные идеи

Любое электронное устройство, которое может создавать или реагировать на последовательность событий, должно иметь память.

Изменение состояния цифровой системы или переход состояния происходит всякий раз, когда изменяется двоичное число, хранящееся во внутренней памяти. Именно посредством направленных переходов из одного состояния в другое цифровые системы могут создавать последовательности событий или реагировать на них.

Бистабильные схемы имеют два стабильных рабочих состояния: состояние, когда на выходе есть логическая «1» (или Vdd), и состояние, когда на выходе есть «0» (или 9).0034 ЗЕМЛЯ ). Когда бистабильная схема памяти находится в одном из двух стабильных состояний, требуется некоторое количество энергии, чтобы перевести ее из этого состояния в другое стабильное состояние.

При переходе между состояниями выходной сигнал должен проходить через область, в которой он нестабилен. Схемы памяти устроены так, что они не могут оставаться в нестабильном состоянии бесконечно — как только они входят в нестабильное состояние, они немедленно пытаются восстановить одно из двух стабильных состояний.

Любая логическая схема может иметь обратную связь, если выходной сигнал просто «подается обратно» и подключается к входу.

узнать, основы, схемы, схемы памяти

ЭКГ 721 Схема схемы памяти

ЭКГ 721 Память

Схема проектирования

Весна 2017 г. , Университет Невады, Лас

Vegas

Курсовая лекция заметки и видео находятся здесь

Домашнее задание задания, сроки выполнения и информация о проекте находятся здесь

Текущие оценки расположены здесь.

В этом курсе мы будем широко использовать LTspice.

Примеры из лекций находятся в ecg721_s17.zip.

Учебник : CMOS Circuit Design, Layout and Simulation, Third Edition (Главы 16–19), а также раздаточные материалы

Инструктор: Р. Джейкоб Бейкер (см. офис часов по этой ссылке)

Ассистент преподавателя: Шада Шариф

Время : предлагается в качестве онлайн-курса для студентов UNLV на территории кампуса

Курс даты : со среды, 18 января, по среду, 3 мая.

Местоположение : предлагается в качестве онлайн-курса для студентов UNLV на территории кампуса.0081 Время заключительного экзамена : Понедельник, 8 мая, с 18:00 до 20:00 в SEB-1240, открытая книга и закрытые записи

Содержание курса Практическое введение в Транзисторное проектирование схем памяти. Технологии памяти, включая DRAM, Будут обсуждаться Flash, MRAM, Glass и SRAM.

Обязательное условие EE 421 или ЭКГ 621

Оценка

25% Промежуточный срок — среда, 15 марта, с 17:30 до 18:45 в TBE B-350, открытая книга и закрытые заметки

25% Домашнее задание

25%

Курсовой проект

25% Финал — понедельник, 8 мая, с 18:00 до 20:00 в SEB-1240, открытая книга и закрытые заметки

Правила курса

- Ноутбуки или интернет-устройства, такие как смартфоны, запрещены.

используется во время экзаменов.

используется во время экзаменов. - На экзаменах Open Book можно использовать только учебник курса (не электронные книги, PDF-файлы и т. д., старые/международные издания или фотокопии).

- Домашние задания не принимаются. Все назначенные домашние задания должны быть выполнены в 17:00 в день, когда они должны быть выполнены.

- Итоговый экзамен не будет сдан в конце семестр, даже временно для вас, чтобы просмотреть.

- Обман или плагиат приведут к автоматической оценке F в курс (так что делайте свою домашнюю работу и проекты!)

- Вопросы по электронной почте следует отправлять в CMOSedu Группа Google (не напрямую для инструктора) по адресу [email protected].

- Вопросы инструктору (только) задавать лично (не по электронной почте).

После заполнив ЭКГ 721, учащиеся смогут:

1. Обсудить разницу между открытым и закрытым массивом DRAM. архитектура

2. Разработайте для DRAM усилитель n- и p-чувств, строки и декодеры столбцов, путь чтения/записи данных

3.

используется во время экзаменов.

используется во время экзаменов.