Полевой транзистор с управляющим p-n переходом: принцип работы и применение

Александр Кораблев

В статье кратко описано устройство полевых транзисторов с управляемым p—n-переходом и приведены схемы их использования. Статья предназначена для ознакомления с транзисторами, а не для подробного изучения их особенностей и схемотехники.

Идея создания полевых транзисторов с управляющим p-n-переходом (JFET) принадлежит американским инженерам Джорджу Дейси (George Clement Dacey) и Йену Россу (Ian Munro Ross). В 1953 г. они создали лабораторный образец такого транзистора, однако технологические проблемы производства смогли преодолеть только в 1960 г. — наверное, с этой даты и следует отсчитывать начало внедрения в практику полевых транзисторов с p-n-переходом.

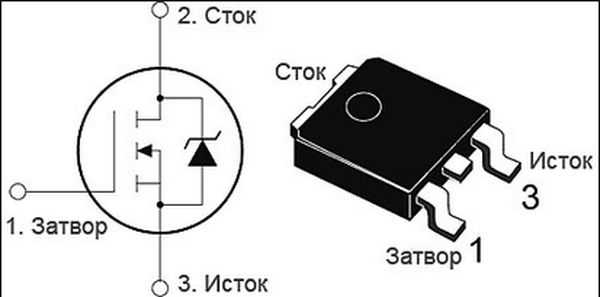

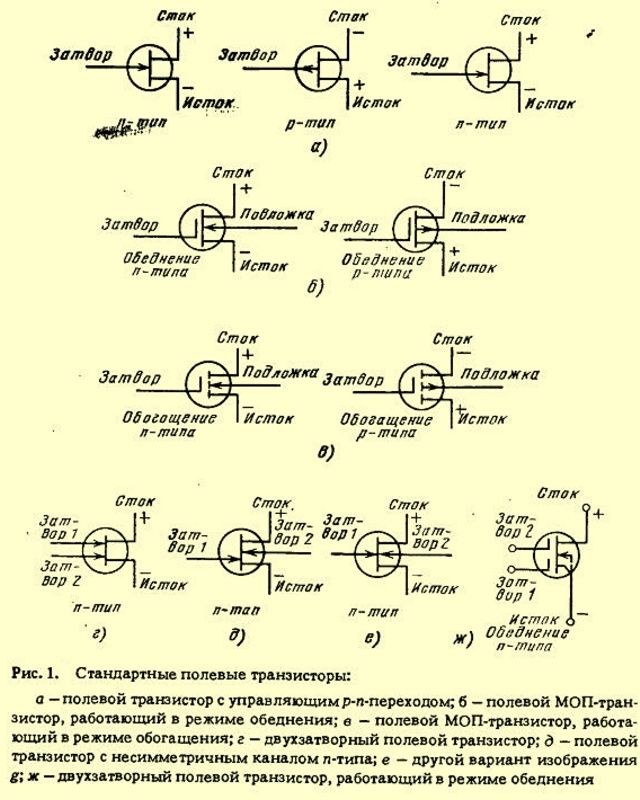

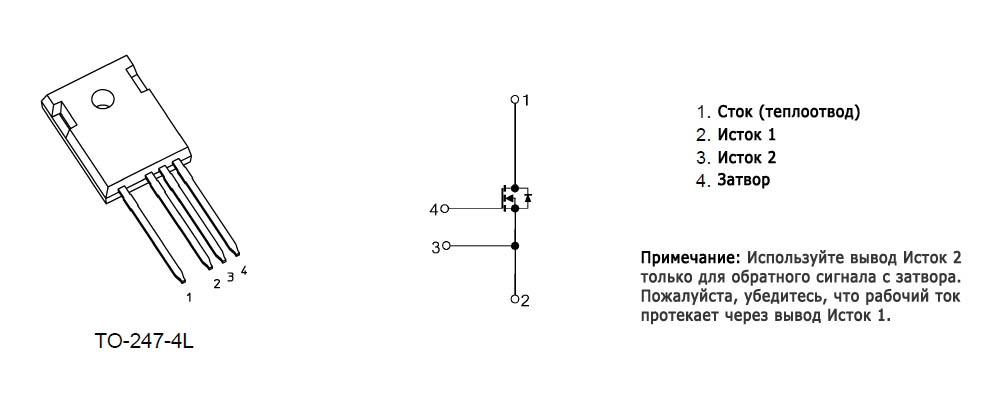

Рис. 1. Схематическое изображение транзисторов с управляющим p-n-переходом

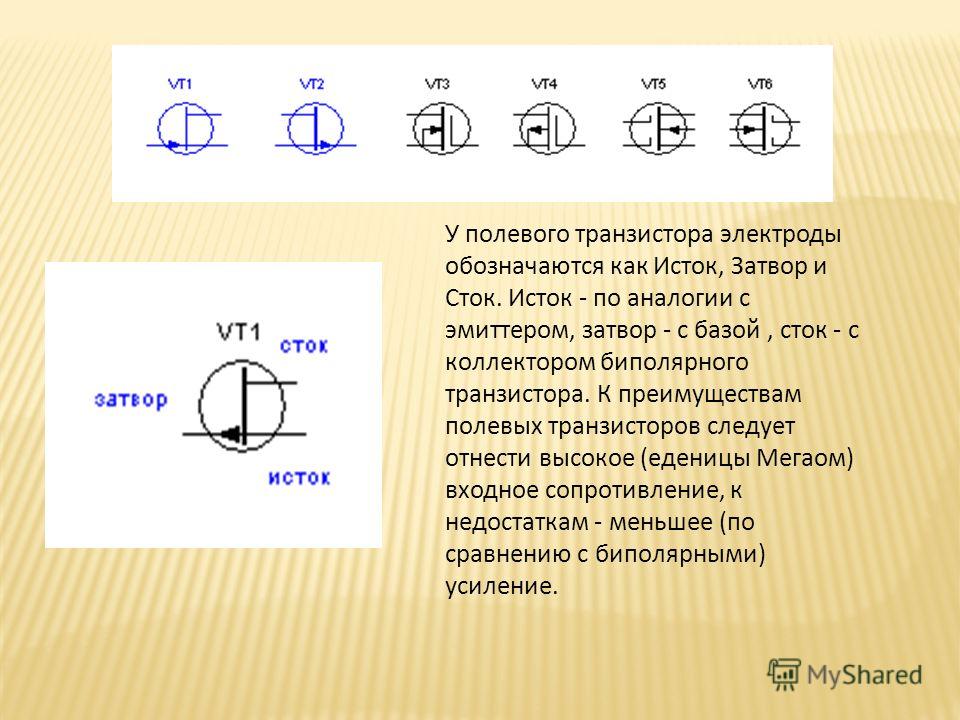

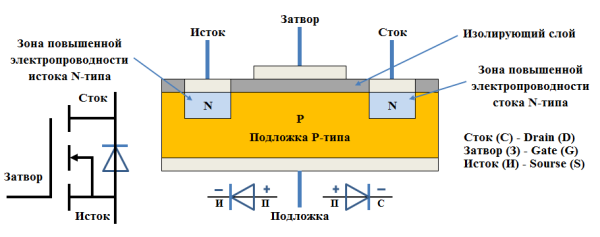

Существуют два типа транзисторов с управляющим p-n-переходом: с p-каналом и n-каналом. Их схематическое изображение показано на рис. 1, а на рис. 2 представлено упрощенное изображение конструкции n-канального транзистора. В областях, прилегающих к стоку и истоку транзистора, посредством дополнительного легирования созданы повышенные концентрации электронов, что уменьшает сопротивление канала в открытом состоянии.

Их схематическое изображение показано на рис. 1, а на рис. 2 представлено упрощенное изображение конструкции n-канального транзистора. В областях, прилегающих к стоку и истоку транзистора, посредством дополнительного легирования созданы повышенные концентрации электронов, что уменьшает сопротивление канала в открытом состоянии.

Рис. 2. Упрощенная конструкция транзистора с управляющим p-n-переходом

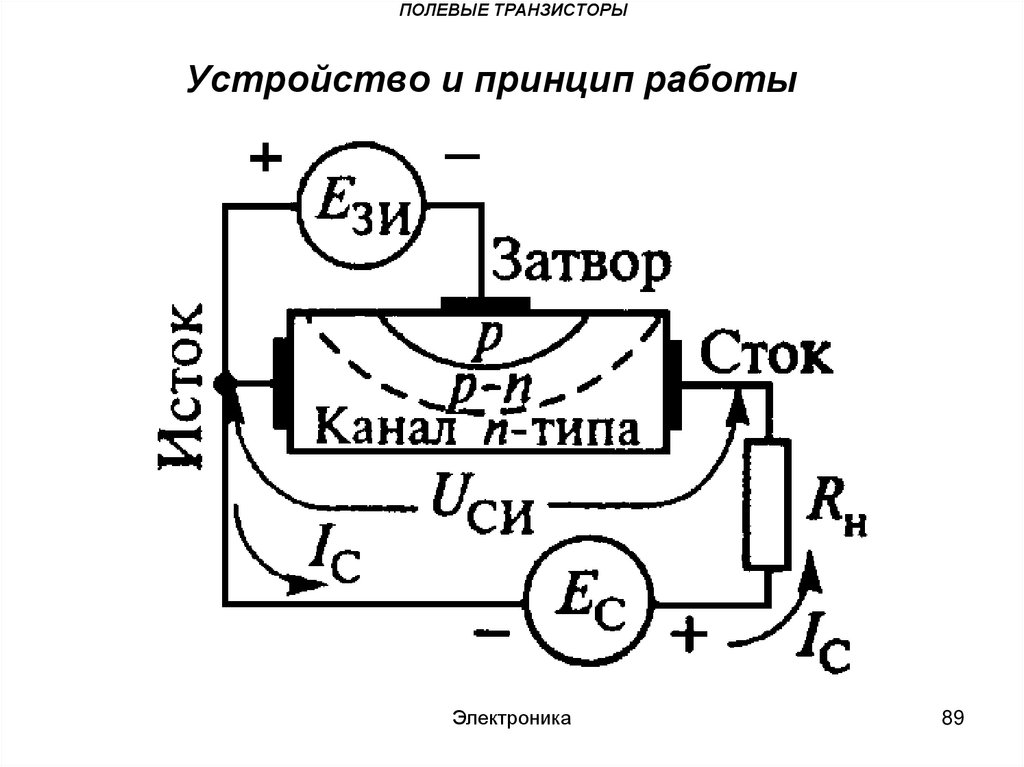

Рис. 3. Принцип работы полевого транзистора на примере n-канального транзистора

Принцип работы полевого транзистора на примере n-канального транзистора иллюстрируется рис. 3. При управляющем напряжении затвор-исток UЗИ = 0 канал находится в проводящем состоянии, основные носители (электроны) обозначены на рис. 3 точками. По мере увеличения напряжения сток-исток UСИ будет возрастать и ток стока I C через канал, транзистор работает в омической области.

Дальнейшее увеличение напряжения сток-исток UСИ приводит к уменьшению свободных электронов, возникает обедненный слой. Область обедненного слоя наиболее велика вблизи стока, поскольку к стоку подключено питающее напряжение и напряженность поля там наиболее высока. Появление обедненного слоя приводит к сужению проводящего канала, поэтому при дальнейшем возрастании напряжения ток увеличивается незначительно, транзистор переходит в область насыщения. Обе области, насыщения и омическая, показаны на вольт-амперной характеристике слева на рис. 3.

Область обедненного слоя наиболее велика вблизи стока, поскольку к стоку подключено питающее напряжение и напряженность поля там наиболее высока. Появление обедненного слоя приводит к сужению проводящего канала, поэтому при дальнейшем возрастании напряжения ток увеличивается незначительно, транзистор переходит в область насыщения. Обе области, насыщения и омическая, показаны на вольт-амперной характеристике слева на рис. 3.

Если прикладывать к затвору отрицательное напряжение UЗИ, область p-n-перехода расширяется в сторону канала, что приводит к сужению проводящего канала и уменьшению тока через него. При дальнейшем увеличении абсолютного значения напряжения затвора канал полностью перекрывается, проводимость прекращается, транзистор переходит в режим отсечки. Напряжение UЗИ, при котором наступает режим отсечки, называется напряжением отсечки UОТС.

Рис. 4. Вольт-амперные характеристики полевого транзистора с p-n-переходом при различных управляющих напряжениях UЗИ

На рис. 4 показаны вольт-амперные характеристики полевого транзистора с p-n-переходом при различных управляющих напряжениях UЗИ и соблюдении соотношений:

4 показаны вольт-амперные характеристики полевого транзистора с p-n-переходом при различных управляющих напряжениях UЗИ и соблюдении соотношений:

|UЗИ4| > |UЗИ3| > |UЗИ2| >|UЗИ1| > 0 В. (1)

Ток стока при управляющем напряжении затвор-исток UЗИ = 0 называется начальным током стока IC0. В большинстве случаев вольт-амперная характеристика полевого транзистора с p-n-переходом хорошо описывается выражением:

IC = IC0 ∙ [1 – (UЗИ/UОТС)]2. (2)

Усиление полевого транзистора характеризуется крутизной GM, которая определяется из формулы (3) с учетом соотношения (2):

GM = dIC/dUЗИ = –2IC0 ∙ [(UОТС – ( U ЗИ)/ UОТС2]. (3)

В справочных данных обычно значение крутизны полевого транзистора указывают при UЗИ = 0. В этом случае выражение (3) принимает следующий вид:

В этом случае выражение (3) принимает следующий вид:

GM = –2IC0 / UОТС. (4)

Преимуществом полевых транзисторов с управляющим p-n-переходом является высокое входное сопротивление, ток обратно смещенного p-n-перехода очень мал и не превышает нескольких микроампер, но следует учитывать, что при возрастании температуры на 10 °С ток затвора удваивается.

К достоинствам полевого транзистора с управляющим p-n-переходом также относятся отличные частотные свойства. Полевые транзисторы униполярны, в них отсутствуют неосновные носители, а следовательно, и процесс рассасывания неосновных носителей, который заметно ухудшает частотные свойства биполярных транзисторов.

Рис. 5. Схемы включения полевых транзисторов с p-n-переходом: а) с общим истоком; б) с общим затвором; в) с общим стоком

Существуют три схемы включения полевых транзисторов. Все они изображены на рис. 5. Часто используется схема с общим истоком (рис. 5а), которая позволяет усилить мощность сигнала. Схема с общим затвором (рис. 5б) имеет низкое входное сопротивление и не усиливает сигнал, поэтому она применяется редко. Схема с общим стоком или истоковый повторитель (рис. 5в) имеет большое входное сопротивление, но коэффициент усиления напряжения практически равен 1.

5а), которая позволяет усилить мощность сигнала. Схема с общим затвором (рис. 5б) имеет низкое входное сопротивление и не усиливает сигнал, поэтому она применяется редко. Схема с общим стоком или истоковый повторитель (рис. 5в) имеет большое входное сопротивление, но коэффициент усиления напряжения практически равен 1.

В инженерной практике полевые транзисторы с управляющим p-n-переходом чаще всего применяют в аналоговых трактах совместно с операционными усилителями или в силовых схемах в качестве ключей. Вкратце рассмотрим несколько примеров применения полевых транзисторов с p-n-переходом в практических схемах.

На рис. 6 показана схема фотодиодного усилителя. Полевой транзистор с p-n-переходом используется здесь в качестве повторителя: он изолирует фотодиод от транзистора, поэтому емкость фотодиода приблизительно равная 3000 пФ «отрезается» от инвертирующего входа операционного усилителя, за счет чего заметно возрастает полоса пропускания.

Коэффициент передачи шума в рассматриваемой схеме определяется выражением:

КШ = 1 + СВХ/СВЫХ. (5)

(5)

За счет уменьшения входной емкости использование полевого транзистора позволяет также снизить шум схемы. Кроме того, полевой транзистор увеличивает входное сопротивление схемы, следовательно, уменьшает коэффициент усиления входного смещения, который определяется выражением:

КУСМ = 1 + RОС/RВХ. (6)

Рис. 6. Схема фотодиодного усилителя

Недостаток схемы (рис. 6) заключается в том, что к фотодиоду прикладывается отрицательное напряжение, из-за чего возрастает его темновой ток, который к тому же зависит от температуры. Если пользователей интересует только переменная составляющая сигнала фотодиода, указанным недостатком можно пренебречь. Если же важна и постоянная составляющая сигнала, следует воспользоваться улучшенной схемой фотодиодного усилителя (рис. 7). В этой схеме используются два согласованных полевых транзистора в одном корпусе. Нижний транзистор является источником тока, величина тока задается сопротивлением R2 в цепи истока и выбирается таким образом, чтобы потенциал катода фотодиода был близок к нулю. Для более точной подстройки нулевого смещения можно добавить потенциометры R4 и R6.

Для более точной подстройки нулевого смещения можно добавить потенциометры R4 и R6.

Рис. 7. Улучшенная схема фотодиодного усилителя

Полевые транзисторы с p-n-переходом удобно использовать в качестве переменных сопротивлений, управляемых напряжением в схемах усилителя с управляемым коэффициентом усиления, или аттенюаторов. Последний вариант изображен на рис. 8. В этой схеме использован p-канальный полевой транзистор, на его затвор подается напряжение с потенциометра VR1, таким образом задается коэффициент ослабления. Возможно и иное решение, например, в качестве управляющего напряжения вместо потенциометра VR1 можно использовать пульсирующее напряжение, в этом случае мы получим простой и экономичный модулятор.

Рис. 8. Схема аттенюатора

Благодаря использованию карбида кремния (SiC) удалось получить полупроводниковые приборы с широкой запрещенной зоной, а следовательно, с повышенным нормируемым рабочим напряжением, что позволило применять их в силовых преобразователях. Сегодня производятся полевые транзисторы с нормируемым напряжением вплоть до 1700 В.

Сегодня производятся полевые транзисторы с нормируемым напряжением вплоть до 1700 В.

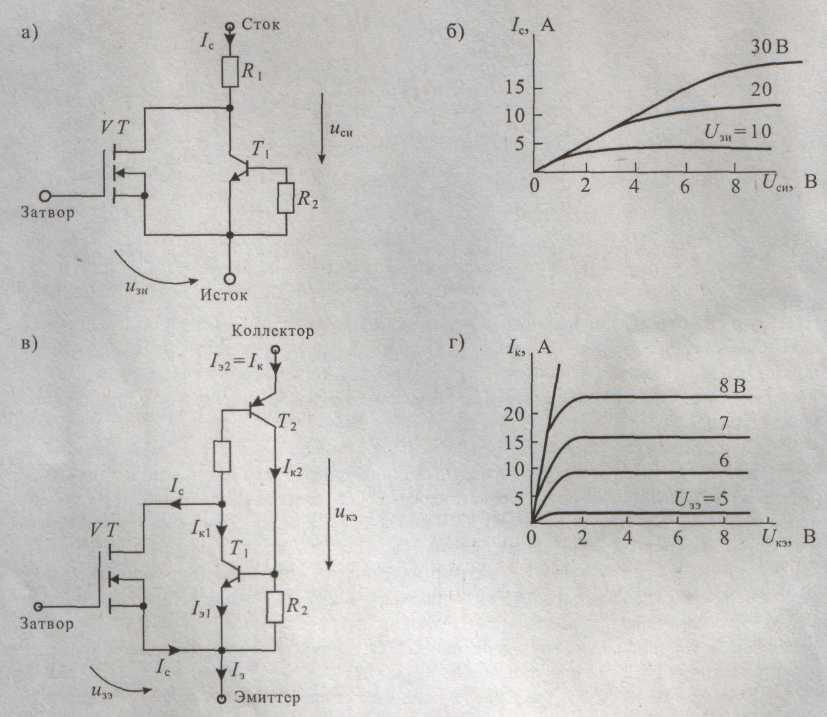

Рис. 9. Каскод c SiC полевыми транзисторами с p-n-переходом

В силовых преобразователях с полевыми SiC-транзисторами с управляемым p-n-переходом последние строятся по хорошо известной еще с ламповых времен схеме каскода (рис. 9). В этой схеме к относительно дорогостоящему высоковольтному SiC-транзистору добавлен обычный низковольтный недорогой кремниевый MOSFET стоимостью «пятачок на пучок». На этом же рисунке можно видеть описание режимов работы каскода.

Рис. 10. Схема суперкаскода с SiC полевыми транзисторами с p-n-переходом

Увеличения нормируемого рабочего напряжения можно достичь с помощью последовательного включения нескольких полевых SiC-транзисторов с p-n-переходом. На рис. 10 показана образованная таким методом схема суперкаскода с нормируемым напряжением 6500 В. В схеме суперкаскода последовательно соединены пять полевых SiC транзисторов с управляемым p-n-переходом с рабочим напряжением 1700 В.

7

Download 483 Kb.

|

Bog’liq

2-Amaliy, Metod birlashma 2020, 9, 8, 6, 13. Учебная лилитература, 5-sinf-matematika-imtihon-javoblari

- Bu sahifa navigatsiya:

- Ключевые слова

| ЛЕКЦИЯ №7. ПОЛЕВЫЕ ТРАНЗИСТОРЫ. План лекции:

Ключевые слова. Полевой тразистор, сток, исток, затвор, подлжка, диэлектрик, полупроводник, канал, p-n переход, параметры ПТ, характеристики ПТ, МДП-транзисторов.

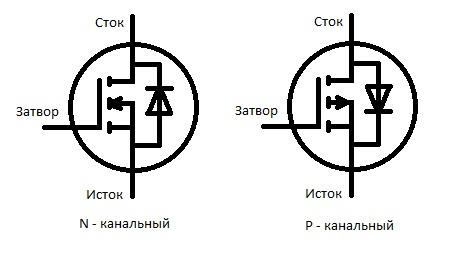

Каналом называется центральная область транзистора. Электрод, из которого в канал входят носители заряда, называется истоком, а электрод, через который основные носители уходят из канала – стоком. Электрод, служащий для регулирования поперечного сечения канала, называется затвором. Так как в полевых транзисторах ток определяется движением носителей только одного знака, ранее их называли униполярными, что подчеркивало движение носителей заряда одного знака. Главное достоинство полевых транзисторов – высокое входное сопротивление. Идея устройства полевого транзистора с управляющим p-n-переходом принадлежит У. Шокли (1952 г.), а транзистора с изолированным затвором – М. Атолле и Д. Кангу (1960 г.). Классификация и условные графические обозначения полевых транзисторов приведены на рис.  7.1 7.1

Рис. 7.1 Классификация и условные графические обозначения

Полевой транзистор с управляющим p-n-переходом Полевой транзистор с управляющим p-n-переходом – это транзистор, у которого затвор электрически отделен от канала закрытым p-n-переходом. В транзисторе с n-каналом (рис. 6.28) основными носителями заряда в канале являются электроны, которые движутся вдоль канала от истока с низким потенциалом к стоку с более высоким потенциалом, образуя ток стока Iс. Между затвором и истоком приложено напряжение, запирающее p-n-переход, образованный n-областью канала и р-областью затвора. В полевом транзисторе с n-каналом полярности приложенных напряжений должны быть следующие: U В транзисторе с p-каналом основными носителями зарядов являются дырки, которые движутся в направлении снижения потенциала, поэтому полярности приложенных напряжений должны быть иными: Uси 0, Uзи 0.

Работа полевого транзистора с n-каналом, а соответственно и изменение поперечного сечения канала происходит при подаче определенных напряжений на электроды транзистора. а б

Рассмотрим работу транзистора на примере трех рисунков. При подаче запирающего (обратного) напряжения Uзи на p-n-переход, между затвором и каналом на границах канала возникает равномерный слой (рис. 7.3), обедненный носителями зарядов и обладающий высоким удельным сопротивлением. Это приводит к уменьшению проводящей ширины канала. Рис. 7.3. Формирование равномерного обедненного слоя в транзисторе с управляющим p-n-переходом при подаче запирающего напряжения Uзи Напряжение, приложенное между стоком и истоком, приводит к появлению неравномерного обедненного слоя (рис. 7.4), так как разность потенциалов между затвором и каналом увеличивается в направлении от истока к стоку и наименьшее сечение канала расположено вблизи стока. Рис. 7.4. Формирование неравномерного обедненного слоя

Если одновременно подать напряжения Uси > 0 и Uзи 0 (рис. 7.5), то толщина обедненного слоя, а следовательно и минимальное сечение канала будут определяться действием этих двух напряжений. Когда суммарное напряжение достигнет значения напряжения запирания: U Рис. 7.5. Формирование неравномерного обедненного слоя в транзисторе с управляющим p-n-переходом при подаче напряжений Uси > 0 и Uзи 0 Включение полевых транзисторов (как и биполярных) может быть произведено по трем схемам: с общим истоком (ОИ), общим стоком (ОС) и общим затвором (ОЗ). Чаще применяется схема с общим истоком (рис. 7.6). В схеме с ОИ цепь сток-исток (с n-типом электропроводности) является выходной цепью усилительного каскада. Эта цепь питается от источника U Рис. 7.6. Схема включения полевого транзистора с общим истоком Download 483 Kb. Do’stlaringiz bilan baham: |

Ma’lumotlar bazasi mualliflik huquqi bilan himoyalangan ©fayllar.org 2023

ma’muriyatiga murojaat qiling

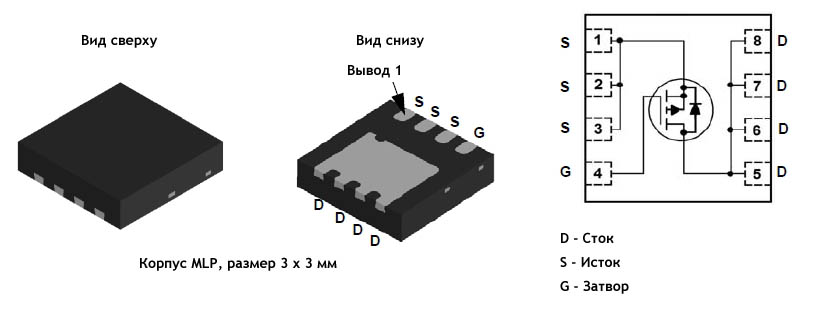

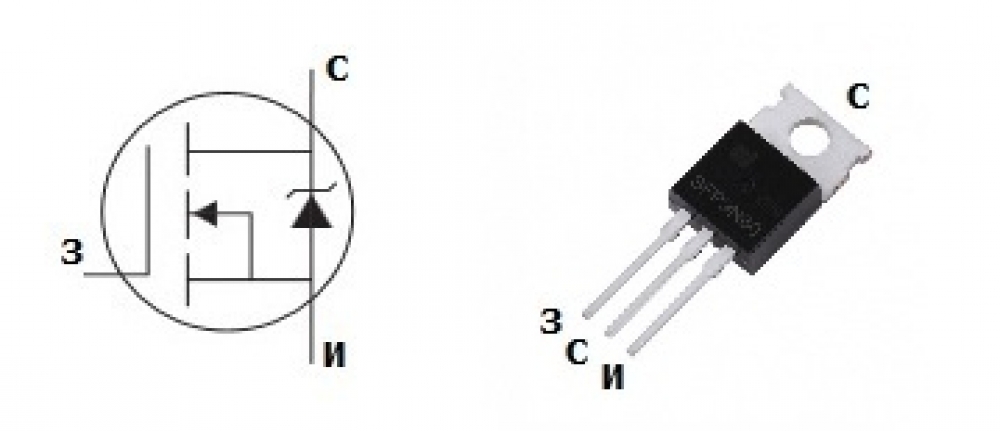

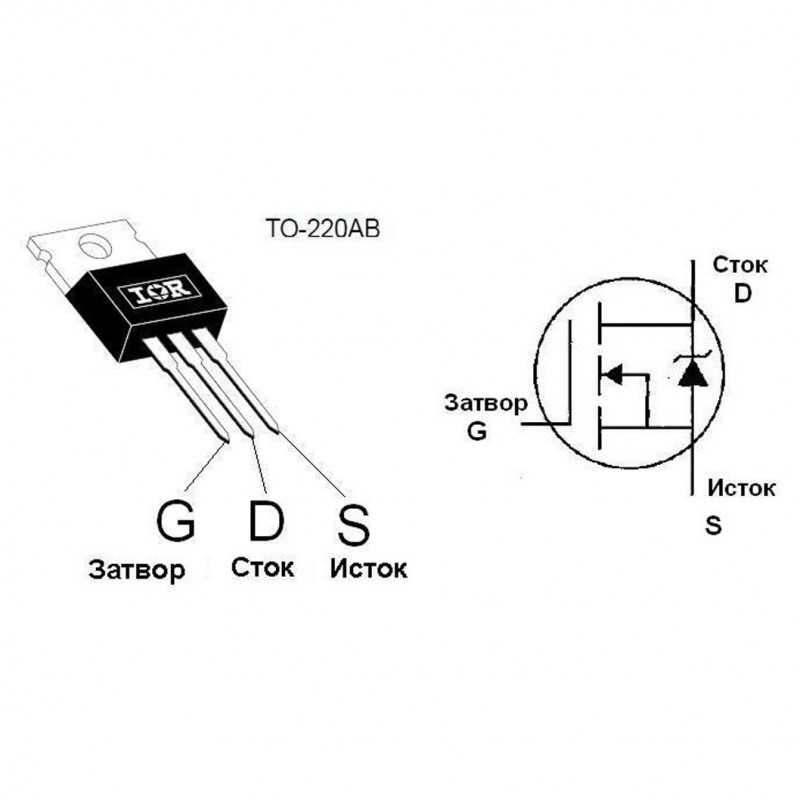

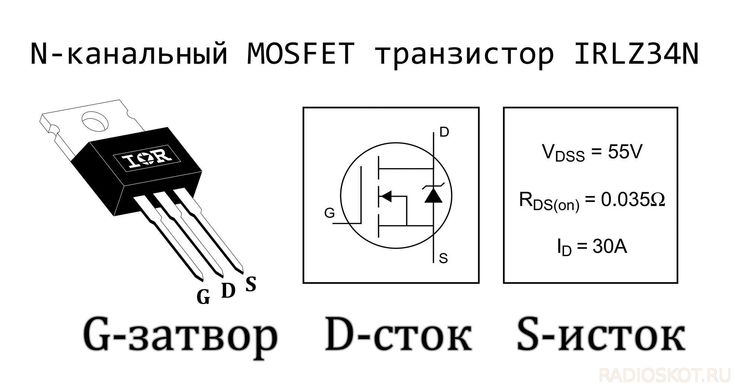

Как прочитать символ MOSFET? — Учебники по электронике

Опубликовано

В обращении находится более дюжины различных схематических символов MOSFET, и между различными символами, которые представляют одно и то же, и множеством различных типов MOSFET, которые необходимо представить, это может стать невероятно запутанным. В этом руководстве мы поможем вам узнать разницу между различными символами MOSFET, с которыми вы сталкиваетесь. Хотя мы считаем, что это будет очень полезно, существует достаточно личных и корпоративных вариантов, и мы не можем гарантировать, что время от времени все еще будет возникать путаница. Существуют также разные требования при работе с дискретными МОП-транзисторами или МОП-транзисторами в интегральной схеме. Однако мы рассмотрим стандартные символы IEEE, и это должно помочь в подавляющем большинстве ситуаций.

Прежде чем мы приступим к этому, важно понять разницу между полевыми транзисторами NMOS и PMOS, а также разницу между полевыми транзисторами режима истощения и улучшения.

Начнем с сокращенного обозначения NMOS и PMOS FET в расширенном режиме.

Полевой транзистор обычно имеет три точки подключения — сток, исток и затвор. Мы представляем, что дизайнеры символов создали два прямых угла, чтобы напомнить канал, который разделяет исток и сток, с воротами, прикрепленными к середине этого канала. Обратите внимание, что PMOS имеет кружок на входе, напоминающий нотацию цифровой логики, где инверсия обозначается кружком. Хотя PMOS не инвертирует сигнал, его работа в некотором роде обратна по сравнению с NMOS.

Теперь давайте посмотрим на сокращенное обозначение NMOS и PMOS FET в режиме истощения.

Сокращенное обозначение Устройство в режиме истощения NMOS Сокращенное обозначение Устройство в режиме истощения PMOSСокращенные символы будут работать в большинстве ситуаций, но во многих случаях потребуются более сложные символы.

Начнем снова с NMOS и PMOS FET в расширенном режиме.

Устройство NMOS Enhancement-Mode DevicePMOS Enhancement-Mode Device На этот раз на входе нет инвертирующего пузырька — вместо этого он связан с направлением стрелки между каналом и подложкой. В отличие от нашей сокращенной записи, мы не предполагаем, что подложка связана с источником с помощью этих символов. Лучше всего запомнить это с помощью двух фактов:

Лучше всего запомнить это с помощью двух фактов:

- Символ диода указывает от P до N PN-перехода.

- Подложка и канал в полевом МОП-транзисторе образуют PN-переход.

Зная это, стрелка очень похожа на символ диода. В NMOS, где он имеет N-канал, стрелка указывает от подложки P-типа к каналу N-типа. В случае PMOS стрелка указывает от подложки N-типа к каналу P-типа. И, наконец, обратите внимание, что линия, представляющая канал, заштрихована. Это будет иметь смысл, когда мы перейдем к символам для режима истощения NMOS и PMOS FETS.

Устройство NMOS в режиме истощения PMOS Устройство в режиме истощения Обратите внимание, что единственная разница между полевыми транзисторами в режиме истощения и режиме улучшения в этом стиле заключается в том, что пунктирная линия теперь сплошная. Нам это кажется интуитивно понятным: полевые транзисторы с режимом истощения, естественно, имеют много несущих в канале, представленном сплошной линией. Полевые транзисторы режима расширения, несущие в канале которых есть только при наличии напряжения на затворе, представлены пунктирной линией.

Наконец, последние представления, предлагаемые стандартом IEEE, предполагают, что подложка и источник подключены.

3-выводные NMOS-транзисторы3-выводные PMOS-транзисторыОн сохраняет стандарт сплошной и пунктирной линии, чтобы различать полевые транзисторы режима истощения и улучшения, но меняет положение со стрелками. Вместо того, чтобы быть похожим на символ диода, стрелка на истоке символа указывает текущее направление потока устройства. В NMOS ток течет от стока к истоку, а в PMOS ток течет от истока к стоку.

Всегда будет некоторая путаница, когда дело доходит до символов MOSFET, но мы надеемся, что этот обзор сделает различные части менее случайным месивом линий. Кроме того, этот обзор помогает нам понять наиболее важные и отличительные аспекты MOSFET. Если у вас есть какие-либо вопросы, не стесняйтесь задавать их в комментариях ниже!

Автор:

Джош Бишоп

Интересуясь встраиваемыми системами, туризмом, кулинарией и чтением, Джош получил степень бакалавра электротехники в Университете штата Бойсе. Проработав несколько лет офицером CEC (Seabee) в ВМС США, Джош уволился и в конце концов начал работать над CircuitBread с кучей замечательных людей. В настоящее время Джош живет на юге Айдахо с женой и четырьмя детьми.

Проработав несколько лет офицером CEC (Seabee) в ВМС США, Джош уволился и в конце концов начал работать над CircuitBread с кучей замечательных людей. В настоящее время Джош живет на юге Айдахо с женой и четырьмя детьми.

Часто задаваемые вопросы по EE

Получите новейшие инструменты и учебные пособия, только что из тостера.

Области работы МОП-транзисторов

А

Металлооксидные полупроводниковые полевые транзисторы (MOSFET, или просто MOS)

четырехконтактное устройство. На рисунке 1 ниже показано общее представление

N-MOS (для PMOS просто замените N регионов на P и наоборот). МОС — это

Источник тока, управляемый напряжением, поскольку ток через МОП-транзистор зависит от

относительные уровни напряжения на его клеммах. Относительные напряжения затвора, стока

и клеммы источника (при условии, что объем или подложка находятся под тем же напряжением, что и

источник) определяют величину тока, протекающего в МОП. В каждом из этих

областей, мы можем представить ток как функцию напряжения затвор-исток

(В GS ) и напряжение сток-исток (V DS ).

| МОП-транзистор — 4-транзисторный прибор |

В МОП-устройстве токи при образовании канала носителей между истоком и стоком терминалы. Для этого напряжение на выводе затвора должно быть таким, чтобы оно притягивало носителей соответствующего типа по отношению к себе. Когда достаточно носителей притягивается к воротам, говорят, что образовался канал. Значит, течет ток между клеммами истока и стока в зависимости от уровней напряжения этих терминалы. Уровень напряжения подложки также влияет на величину тока. так как он также определяет уровень несущих в канале.

Для устройства N-MOS

канал образован электронами. Таким образом, для притяжения электронов напряжение на затворе должно быть

больше, чем напряжение источника. Для формирования канала

разница между V G и V S (V G – V S )

должно быть больше V ом (пороговое напряжение МОП).

Пороговое напряжение определяется как минимальная разница в напряжении затвор-исток, необходимая для формирование канала в МОП устройстве. Для NMOS, V -й положителен, т.к. для формирования канала затвор должен быть на более высоком напряжении, как объяснялось выше. Сходным образом, для PMOS V th является отрицательным, так как затвор должен быть при более низком напряжении, чем источник для формирования канала.

При увеличении напряжения на затворе за пороговым напряжением ток через МОП увеличивается с увеличением затвора Напряжение. Кроме того, если мы увеличим напряжение стока, сохранив напряжение затвора постоянным, ток увеличивается до определенного напряжения на стоке. После этого увеличивается слив напряжение не влияет на ток. В зависимости от относительных напряжений его терминалы, MOS, как говорят, работает в любой из отсечки, линейной или область насыщения.

- Вырезать

off region — Говорят, что MOS-устройство работает

когда напряжение затвор-исток меньше V th .

Таким образом, для МОС

находиться в области отсечки, необходимое условие –

Таким образом, для МОС

находиться в области отсечки, необходимое условие –

0 < В ГС < V th — для NMOS

0 > V GS > V th — для PMOS (поскольку пороговое напряжение PMOS отрицательное)

Отключение

область также известна как подпороговая область. В этом регионе зависимость

ток на напряжении затвора экспоненциален. Величина протекающего тока

через МОП в зоне отсечки пренебрежимо мал, так как канала нет.

проводимость, происходящая в этой области, известна как подпороговая проводимость.

- Линейный или область ненасыщения — для NMOS, как напряжение затвора увеличивается выше порогового напряжения, канал формируется между клеммы истока и стока. Теперь, если есть разница в напряжении между источником и сток, ток будет течь. Величина тока увеличивается линейно с увеличение напряжения стока до определенного напряжения стока, определяемого следующие отношения –

В ГС ≥ В й

В ДС < В ГС – В -й

то ток представляется как линейная функция от затвора к истоку и

напряжения сток-исток. Вот почему говорят, что МОП работает в линейном режиме.

область, край. Линейное отношение напряжения к току определяется следующим образом:

Вот почему говорят, что МОП работает в линейном режиме.

область, край. Линейное отношение напряжения к току определяется следующим образом:

Id(Linear) = µ Cox W/L (Vgs – Vth – Vds/2) Vds.

Аналогично, для транзистора P-MOS условие для того, чтобы P-MOS находилась в линейной области, представлено как:

V GS < V th ИЛИ V SG > |V th |

И V DS > V GS + V th ИЛИ V SD < V SG — |V th |

- Насыщенность

Регион — для NMOS, у определенных ворот.

и напряжение истока, существует определенный уровень напряжения для стока, за пределами

что увеличение напряжения стока, по-видимому, не влияет на ток. Когда MOS

работает в этом регионе, говорят, что он находится в состоянии насыщения.

Таким образом, для МОС

находиться в области отсечки, необходимое условие –

Таким образом, для МОС

находиться в области отсечки, необходимое условие –