Исследование полевого транзистора | Лаборатория Электронных Средств Обучения (ЛЭСО) СибГУТИ

Лабораторная работа выполняется с помощью учебного лабораторного стенда LESO3.

- Исследование передаточной характеристики полевого транзистора.

- Исследование выходных характеристик ПТ.

- Исследование усилителя на полевом транзисторе в схеме с общим истоком.

С помощью учебного лабораторного стенда LESO3 ознакомиться с принципом действия полевого транзистора (ПТ). Изучить его характеристики. Изучить простейший усилитель на ПТ

2. Задание к работе2.1 Исследовать передаточную характеристику полевого транзистора

Для исследования следует выбирать транзистор с начальным током стока Ic0 не более 10 мА, напряжение отсечки не должно превышать 10 В.

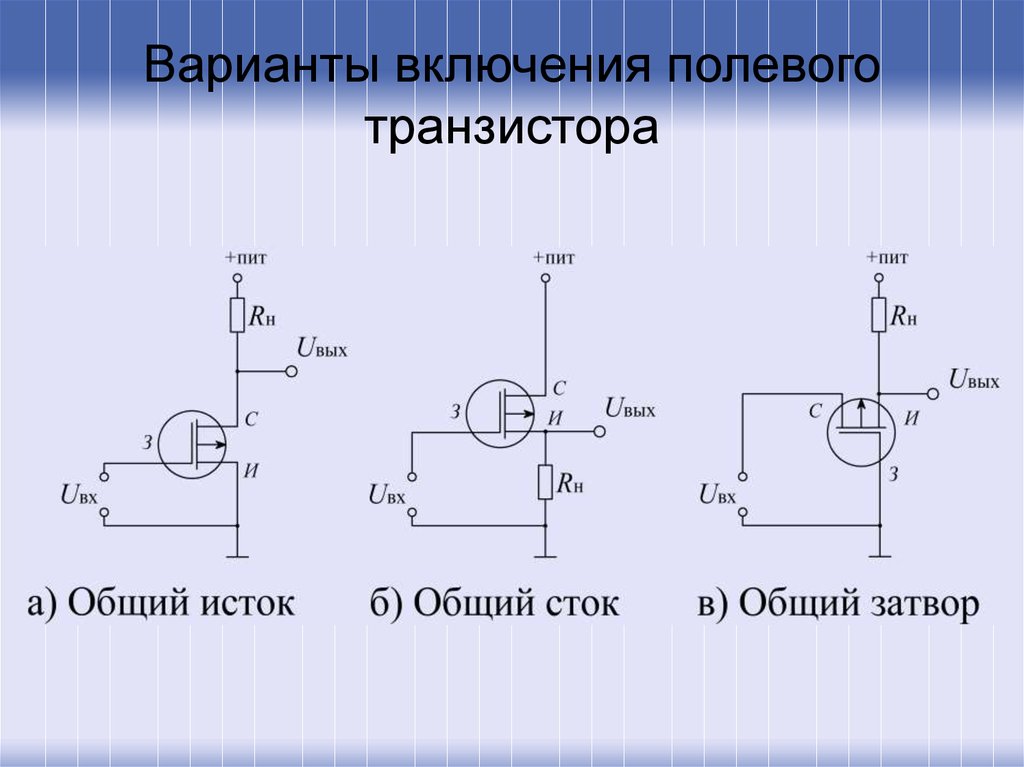

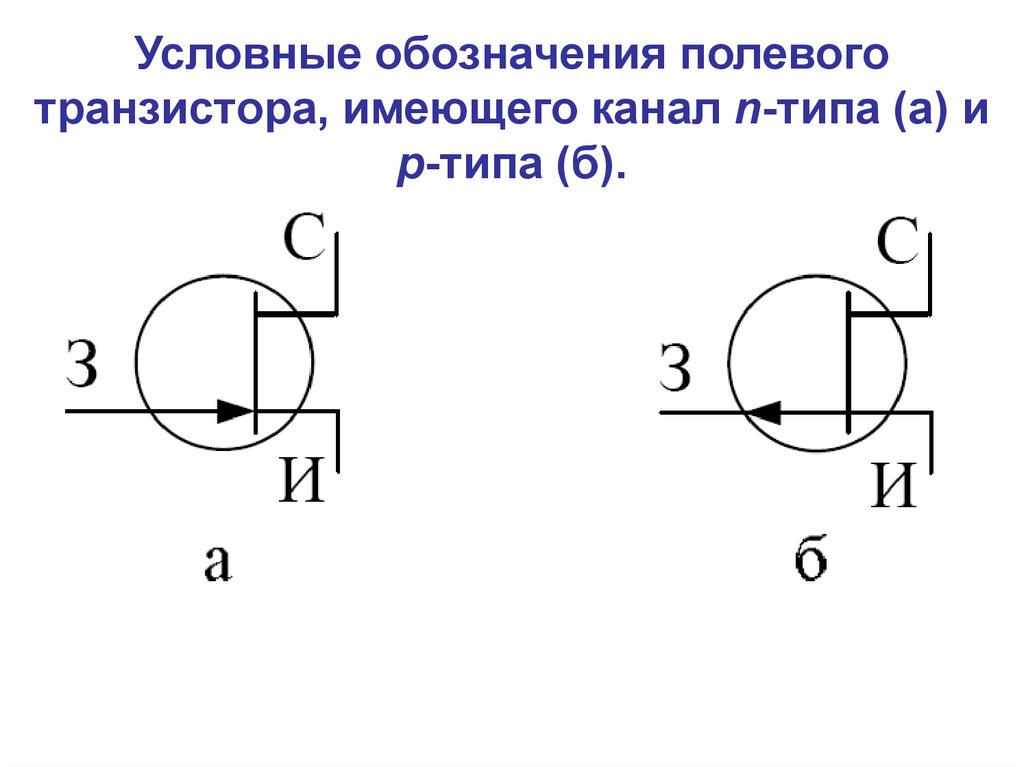

2.1.1 Собрать схему исследования выходных характеристик ПТ. На рисунке 1 приведена схема исследования. В дальнейшей работе предполагается, что исследуется полевой транзистор с затвором на основе p-n перехода и каналом n-типа. При исследовании транзистора с каналом p типа следует изменить полярности источников напряжения и знак предела шкалы графопостроителя.

В дальнейшей работе предполагается, что исследуется полевой транзистор с затвором на основе p-n перехода и каналом n-типа. При исследовании транзистора с каналом p типа следует изменить полярности источников напряжения и знак предела шкалы графопостроителя.

2.1.2 Экспериментальным путем определить напряжение отсечки Uз0 и начальный ток стока Ic0. Для этого следует установить с помощью источника E1 напряжение на затворе 0 В и напряжение на стоке 10 В. Напряжение на стоке устанавливается регулятором E2. Напряжение на затворе контролируется вольтметром V1, напряжение на стоке вольтметром V2. По миллиамперметру mA1 определить начальный ток стока Ic0.

Плавно увеличивая отрицательное напряжение на затворе с помощью регулятора E1 добиться падения тока стока (контролируется по mA1) до ~10 мкА. При необходимости можно переключить шунт амперметра для измерения микротоков, для этого следует нажать кнопку .

При необходимости можно переключить шунт амперметра для измерения микротоков, для этого следует нажать кнопку .

Показание вольтметра V1, при котором ток стока уменьшится до ~10 мкА, будет соответствовать напряжению отсечки.

2.1.3 Построение передаточной характеристики Ic = f(Uзи). Установить по вертикальной оси графопостроителя mA1, по горизонтальной V1. По вертикальной оси установить диапазон: нижняя граница 0, верхняя +10мА; по горизонтальной оси левый предел следует выбрать исходя из напряжение отсечки, рекомендуется округлить Uз0 в большую сторону; правый предел 1В. Изменяя напряжение на затворе с помощью регулятора E1 в диапазоне от Uз0 до 0,5 В получить график передаточной характеристики полевого транзистора.

2.1.4 Сохранить результат.

Образец характеристики показан на рисунке ниже:

Образец.

Образец.2.2 Исследовать выходные характеристики ПТ

2.2.1 Собрать схему исследования выходных характеристик аналогичную предыдущей схеме (см. рисунок 1).

2.2.2 Установить диапазон регулирования источника E1 Uз0..+1 В, источника E2 0..+10 В. По вертикальной оси графопостроителя выбрать миллиамперметр mA1, диапазон: нижняя граница 0, верхняя +10 мА, по горизонтальной оси графопостроителя выбрать V2, диапазон: левая граница 0, правая граница +10 В. Пределы вертикальной шкалы можно скорректировать после измерения характеристик.

2.2.3 Снять семейство выходных характеристик полевого транзистора Iс = f(UСИ) в пологой области для различных фиксированных напряжений затвора Uзи. Рекомендуется выбрать: Uзи1 = 0, Uзи2 = 0,2•Uз0 и Uз3 = 0,4•Uз0, Uзи4 = 0,6•Uзи, Uзи5 = 0,8•Uзи, Uзи6 = Uзи, Uзи7 = -0,2•Uзи и Uзи8 = -0,4•Uзи. Последние две характеристики допустимо снимать, только если Uзи< 0,5 В. Выходная характеристика получается путем регулирования E2 от 0 до 10 В.

Последние две характеристики допустимо снимать, только если Uзи< 0,5 В. Выходная характеристика получается путем регулирования E2 от 0 до 10 В.

2.2.4 Сохранить результат. Пример выходных характеристик полевого транзистора показан на рисунке ниже:

2.2.5 Исследовать выходные характеристики полевого транзистора в крутой области. Здесь транзистор ведет себя как сопротивление, управляемое напряжением Uзи.

Не очищая результат предыдущего исследования изменить масштаб графика таким образом, что бы выходные характеристики были представлены в крутой области. При необходимости повторить измерение для тех же значений Uзи, что и в предыдущем пункте, но более точно выставить диапазон регулирования E2, например, от 0 В до 1 В.

2.2.6 Сохранить результат исследования. Пример выходных характеристик в крутой области показан на рисунке ниже:

Образец

Образец2.2.5 Для каждой характеристики определить сопротивление канала.

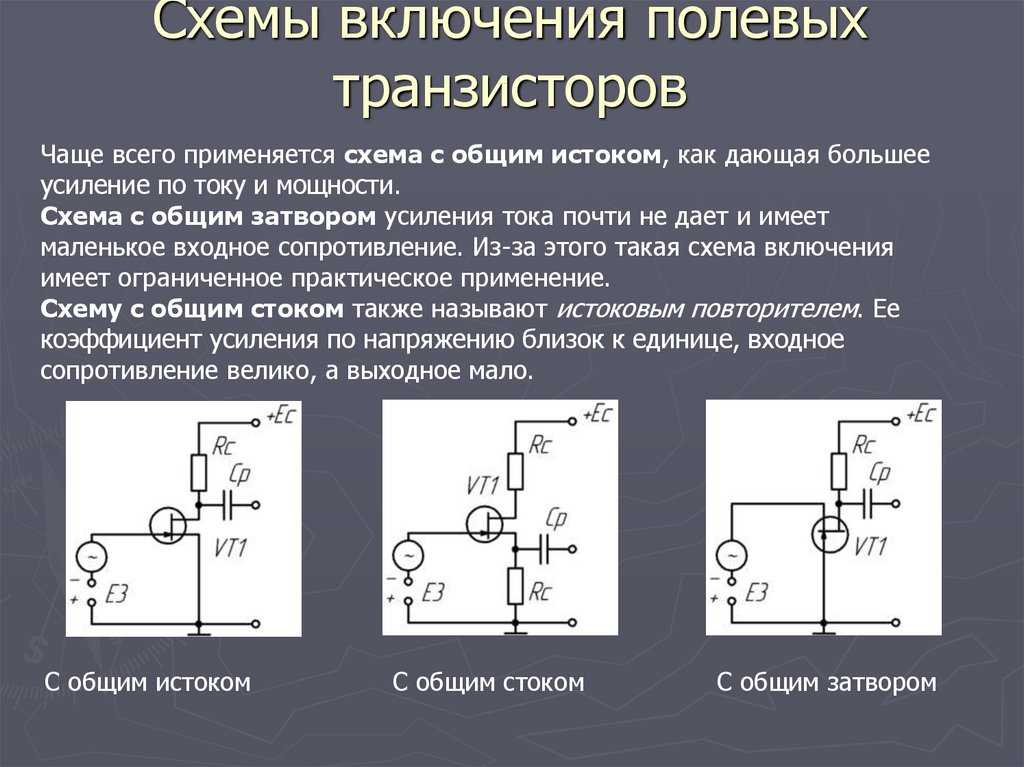

2.3 Исследовать усилитель на полевом транзисторе в схеме с общим истоком

2.3.1 Собрать схему, показанную на рисунке 6. В этой схеме генератор E2 задает напряжение питание, переменная компонента его должна быть уменьшена до нуля. Генератор E1 задает входной сигнал и постоянное напряжение для формирования рабочей точки схемы.

2.3.2 Перевести графопостроитель в режим временных характеристик.

2.3.3 Установить диапазон регулирования E2 от Uз0 до 1 В. Выбрать по вертикальной оси верхнего экрана графопостроителя V1, здесь будет отображаться входной сигнал. Выбрать по вертикальной оси нижнего экрана графопостроителя V2, здесь будет отображаться выходной сигнал, диапазон следует установить 0. .+10 В.

.+10 В.

2.3.4 Задать рабочий режим. Для этого установить напряжение источника питания усилителя E2 = 10 В. Переменную компоненту генератора E1 установить в ноль. Вращая ручку регулятора постоянной компоненты источника E1 установить напряжение на стоке транзистора равным половине напряжения питания, напряжение контролируется по вольтметру V2.

2.3.5 Регулируя амплитуду источник E1 подобрать такие параметры синусоидального входного сигнала, что бы на выходе был неискаженный синусоидальный сигнал с максимально возможной амплитудой. При этом следует следить, чтобы входной сигнал не превышал напряжение 0,5 В. Скорректировать масштаб верхнего графика. Затем можно сохранить полученные графики.

2.3.6 Изменяя постоянную составляющую входного сигнала, анализируя искажения синусоиды по осциллограмме выходного сигнала установить режим работы транзистора вблизи отсечки и вблизи насыщения. Установить рабочую точку транзистора посередине рабочего участка подать на вход усилителя такой сигнал, что бы были видны ограничения сигнала на выходе снизу и сверху. Для каждого случая сохранить полученные графики.

Установить рабочую точку транзистора посередине рабочего участка подать на вход усилителя такой сигнал, что бы были видны ограничения сигнала на выходе снизу и сверху. Для каждого случая сохранить полученные графики.

- Схемы исследования.

- Передаточная характеристика полевого транзистора.

- По передаточной характеристике определить крутизну S для различных напряжений Uзи.

- Семейство выходных характеристик. Каждая характеристика должна быть подписана.

- На выходных характеристиках выделить крутую и пологую области.

- Семейство выходных характеристик ПТ в крутой области. Для каждой характеристики определить сопротивление канала.

- Построить график зависимости сопротивления канала в пологой области от напряжения на затворе Uзи.

- Результаты исследования усилителя.

- По осциллограммам усилителя определить коэффициент усиления усилителя по напряжению.

4.30. Линейный переключатель на полевом транзисторе с p-n

Операционные усилители

Некоторые типичные схемы с операционными усилителями

Подразделы: 4.28 4.29 4.30 4.31 4.32

В гл. 3 мы более или менее подробно рассмотрели линейные переключатели на полевых МОП — транзисторах. В качестве линейных переключателей можно также использовать полевые транзисторы с p-n — переходом. Однако в связи с тем что затвор не должен проводить ток, нужно проявлять особое внимание к сигналам, поступающим на него. Типичная схема показана на рис. 4.76. Для того, чтобы транзистор находился в режиме отсечки, потенциал затвора поддерживается на уровне ниже потенциала земли.

Pиc. 4.76.

Эта схема, конечно, нескладна, и может быть поэтому в линейных преобразователях чаще используют полевые МОП — транзисторы. Однако если воспользоваться операционным усилителем, то можно сделать красивый линейный переключатель и на основе полевого транзистора с р-n — переходом. В этом случае на суммирующем переходе инвертирующего усилителя можно подключить исток транзистора мнимому потенциалу земли. Теперь для того, чтобы включить транзистор, достаточно сделать напряжение на затворе равным потенциалу земли. Еще одно преимущество такой схемы состоит в том, что она обеспечивает возможность полного устранения ошибок, обусловленных конечной величиной сопротивления R

Еще одно преимущество такой схемы состоит в том, что она обеспечивает возможность полного устранения ошибок, обусловленных конечной величиной сопротивления R

Рис. 4.77. Переключатель на полевых транзисторах с р-n — переходом, использующий в своем составе ОУ, с компенсацией Rвкл.

Следует особо отметить два свойства этой схемы: (а) Когда транзистор Т1 находится в состоянии ВКЛ (затвор заземлен), схема представляет собой инвертор с идентичными импедансами во входной цепи и в цепи обратной связи. В результате устраняются все эффекты, связанные с конечным или нелинейным сопротивлением транзистора в состоянии ВКЛ, при условии, что полевые транзисторы согласованы по R гл. 8 и 9). Если исток транзистора T1 подключен к мнимой земле (суммирующий вход), то инвертирующая конфигурация упрощает работу схемы, так как в состоянии ВКЛ на исток T1 не поступает никаких сигналов. Когда Т1 находится в состоянии ВЫКЛ, диод Д1 препятствует включению транзистора при положительных входных сигналах. Когда переключатель закрыт, влияние диода Д

гл. 8 и 9). Если исток транзистора T1 подключен к мнимой земле (суммирующий вход), то инвертирующая конфигурация упрощает работу схемы, так как в состоянии ВКЛ на исток T1 не поступает никаких сигналов. Когда Т1 находится в состоянии ВЫКЛ, диод Д1 препятствует включению транзистора при положительных входных сигналах. Когда переключатель закрыт, влияние диода Д

Существуют p- канальные полевые транзисторы с p-n — переходом с низкими напряжениями отсечки, удобной конфигурации и с приемлемой пеной. Например, в семейство IH5009 — IH5024 входят такие схемы, в которых в одном транзисторном корпусе размешаются четыре полевых транзистора плюс один полевой транзистор для устранения ошибок; для них Rвкл составляет 100 Ом, а цена не превышает двух долларов. Подключите еще ОУ и несколько резисторов и вы получите мультиплексор на 4 входа. Следует отметить, что подобный трюк с Rвкл можно оделать и в переключателе на полевых МОП — транзисторах.

Подразделы: 4.28 4.29 4.30 4.31 4.32

Частотная коррекция усилителей с обратной связью

Как устранить неполадки в цепях FET

Привет, друзья! Надеюсь, у вас все хорошо. В сегодняшнем уроке мы рассмотрим Как устранить неполадки в цепях FET. FET расшифровывается как полевой транзистор — это категория транзисторов, которые управляют током через электрическое поле. Как и BJT, этот транзистор также имеет три вывода: затвор, сток и исток. Этот электронный компонент регулирует движение тока с помощью напряжения на клемме затвора, что в результате изменяет проводимость между стоком и истоком.

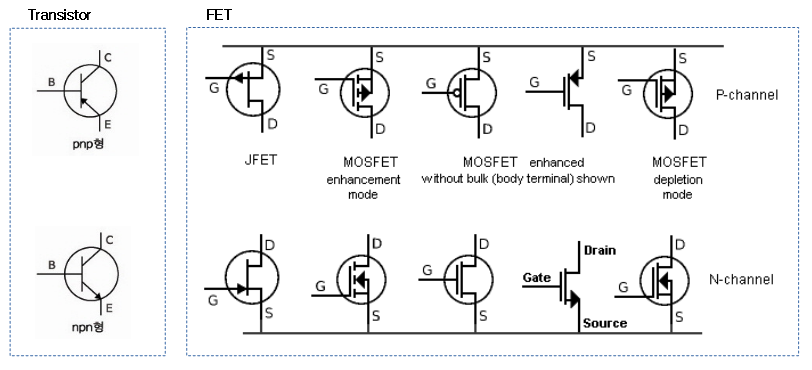

Существует два основных типа полевых транзисторов: первый — это JFET (полевой транзистор с переходом), а второй — MOSFET (полевой транзистор на основе оксида металла). МОП-транзистор далее делится на два типа E-MOSFET и D-MOSFET, которые мы подробно описали в предыдущем руководстве. В сегодняшнем посте мы подробно рассмотрим его устранение неполадок и связанные с ним параметры. Итак, давайте начнем с Как устранить неполадки в цепях FET.

Итак, давайте начнем с Как устранить неполадки в цепях FET.

Первый симптом: VD=VDD

- В этой ситуации значение тока стока должно быть равно нулю, так как потери напряжения равны нулю. Это показано на рисунке, обозначенном буквой «а».

- Для любой схемы хорошим методом устранения неполадок является поиск обрыва или потери связи, а также сгоревших сопротивлений.

- После этого отключите источник питания и рассчитайте предполагаемое сопротивление для обрыва цепи.

- Если это хорошо, тогда будут проблемы с

- Приведенные ниже ошибки могут вызывать этот симптом.

- Нет клеммы заземления при сопротивлении Rs.

- Сопротивление Rs открыто.

- Открыто соединение сливного провода.

- Соединение провода источника открыто.

- FET открыт внутри между стоком и истоком.

2 nd Признак: VD меньше нормального значения

- Для этого состояния, если напряжение питания меньше, чем должно быть, ток стока должен быть больше нормального значения, поскольку падение напряжения относительно сопротивления RD большой.

- Цифра, обозначенная буквой «b», объясняет это состояние.

- Эти нижеприведенные ошибки могут вызвать этот симптом.

- Сопротивление RG открыто

- Поводок ворот открыт

- FET открыт изнутри на воротах.

- Любая неисправность из этих 3 устранит область истощения JFET, поэтому ток стока ограничивается только сопротивлением RD, RS и меньшим значением сопротивления канала.

- Основная неисправность, которую трудно найти, это открытый затвор в D-MOSFET с нулевым смещением.

- Для D-MOSFET с нулевым смещением напряжение между затвором и истоком равно нулю в идеальном случае, когда в схеме затвора существует разомкнутая цепь.

- Таким образом, ток стока не изменяется, а смещение выглядит нормально, как показано на рисунке ниже.

- Тем не менее, статический заряд из-за открытой банки приводит к неравномерному действию тока стока

- В схеме E-MOSFET с конфигурацией смещения делителя напряжения открытое сопротивление R1 приводит к тому, что напряжение затвора становится равным нулю.

- Из-за этого транзистор выключен и ведет себя как разомкнутая цепь переключателя, поскольку для включения транзистора требуется пороговое напряжение затвор-исток, превышающее 0.

- Эта ситуация поясняется на рисунке, обозначенном буквой «а». Если сопротивление R2 открыто, напряжение затвора равно +VDD, а сопротивление канала очень меньше транзистора или устройство работает как замкнутый ключ.

- Ток стока ограничен сопротивлением RD. Это состояние поясняется на рисунке, обозначенном буквой «b».

Итак, это подробный пост об устранении неполадок в схемах FET, если у вас есть какие-либо вопросы, задавайте их в комментариях. Спасибо за прочтение. Хорошего дня.

Новое поступление алюминиевых плит, всего 2 доллара США

Автор: Henry

http://www. theengineeringknowledge.com

theengineeringknowledge.com

Я профессиональный инженер, выпускник известного инженерного университета, также имею опыт работы инженером в различных известных отраслях. Я также являюсь автором технического контента, мое хобби — исследовать новые вещи и делиться ими с миром. Через эту платформу я также делюсь своими профессиональными и техническими знаниями со студентами инженерных специальностей.

Моделирование устройства на уровне схемы на графеновых полевых транзисторах

Умо, Име Дж. (2014) Моделирование устройств на уровне схемы на графеновых полевых транзисторах. Саутгемптонский университет, Факультет физических и инженерных наук, докторская диссертация , 190 стр.

Тип записи: Тезис (Докторская)

Abstract

В данной диссертации представлены модели полевого транзистора на основе графена (GFET). Графеновый материал широко изучался с момента его синтеза в 2004 году, и этот материал обещает быть использованным в электронных приложениях следующего поколения. Поэтому возникает необходимость моделирования его характеристик устройства.

Поэтому возникает необходимость моделирования его характеристик устройства.

В этом отношении представленные здесь материалы представляют собой, во-первых, SPICE-совместимую модель графеновых транзисторов как с двойным, так и с одним затвором. Вывод переноса носителей как дырочной, так и электронной проводимости приводит к набору аналитических уравнений. Эти выводы охватывают три идентифицированные области работы, а также условия граничного напряжения, которые определяют области. Показано, что элементы якобиана непрерывны через границы области.

Во-вторых, модель уровней схемы однослойного GFET и многослойного GFET подходит для прямой реализации в SPICE. В этом вкладе получено более точное пороговое напряжение по сравнению с другими моделями. Этот вклад также показывает, как модели могут быть расширены до такого количества слоев, которое имеет транзистор с графеновым каналом.

Наконец, введение термоэлектронного сопротивления, которое моделируется параллельно с сопротивлением из-за индуцированных затвором зарядов, обеспечивает модель сопротивления канала, зависящего от температуры. Вклад идет дальше, чтобы вывести уравнения между током отключения и вертикальными электрическими полями. Таким образом, это дает хорошую оценку настраиваемой ширины запрещенной зоны в графене.

Вклад идет дальше, чтобы вывести уравнения между током отключения и вертикальными электрическими полями. Таким образом, это дает хорошую оценку настраиваемой ширины запрещенной зоны в графене.

Модели в этом вкладе проверены на основе экспериментально измеренных характеристик транзисторов, которые были выполнены другими исследовательскими группами, и модели показывают хорошее соответствие во всех проверенных случаях. В диссертации также представлено использование плавающего затвора для оптимизации характеристик транзисторов. Чтобы проиллюстрировать этот вклад, алгоритмы моделей были реализованы в следующих инструментах САПР, HSPICE, VHDL-AMS и Berkeley SPICE. В ходе этой работы были опубликованы один журнальный и пять докладов на конференциях.

Текст

Умох.pdf — Другое

Загрузить (8MB)

Дополнительная информация

Дата публикации: июнь 2014 г.

Организации: Университет Саутгемптона, EEE

Идентификаторы

Идентификатор локальной электронной печати: 369980

URI: http://eprints.