Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

Схемы, выходное состояние которых однозначно определяется только комбинацией входных сигналов, называют комбинационными. Закон функционирования КС определяется системой переключательных (логических) функций:

Синтез (построение) комбинационной схемы состоит в построении схемы на основе заданного закона ее функционирования в виде системы переключательных функций (ПФ) или таблиц истинности. При синтезе комбинационной схемы чаще всего необходимо построить схему с использованием минимального числа элементов в заданном элементном базисе, например, на элементах И-НЕ.

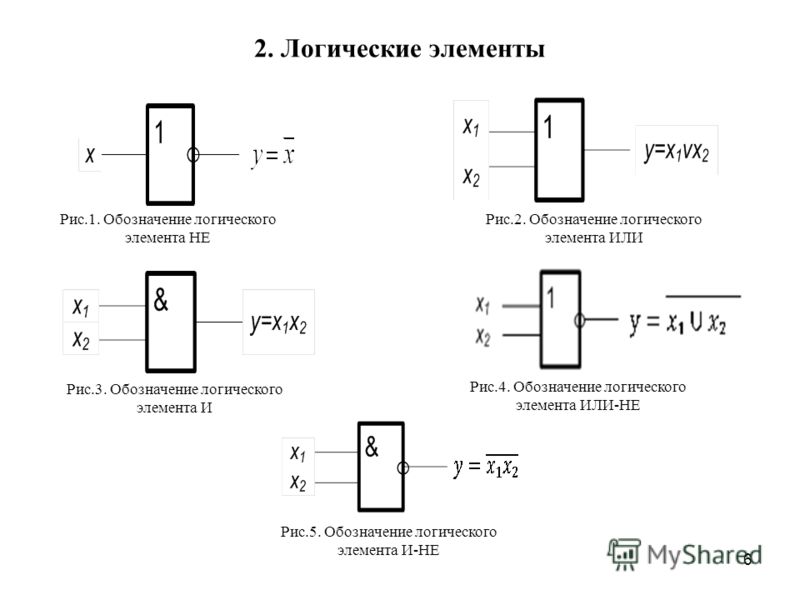

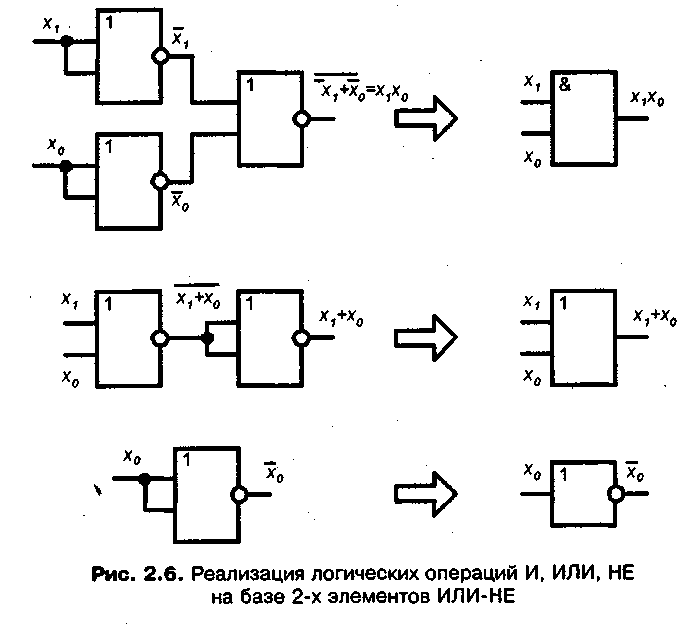

Комбинационные

схемы строятся из элементарных логических

элементов И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и других.

Соединяют эти элементы так, как это

следует из логической формулы, т.е. вход

одного элемента, в котором часть

аргументов обработана как указано в

формуле, подключается ко входу другого,

где выполняется дальнейшая обработка

логической функции.

Пример: Пусть дана логическая функция

Комбинационная схема представлена на рисунке.

Этапы синтеза:

Задание логической функции словесно, с помощью таблиц истинности или булевых выражений.

Минимизация логической функции с помощью алгебраического или графического метода (диаграммы Вейча, карты Карно).

Запись булевого выражения минимизированной переключательной функции.

Преобразование булевого выражения минимизированной ПФ для реализации её в заданном базисе И-НЕ или ИЛИ-НЕ.

Составление функциональной схемы, т.е. изображение нужных логических элементов и связей между ними.

Технологии

минимизации.

Минимизацией называют процедуру упрощения аналитического

выражения, представляющего переключательную

(логическую) функцию, направленную на

то, чтобы булево выражение ПФ содержало

минимальное количество членов с

минимальным числом переменных. Способы

минимизации:

алгебраический; с помощью диаграмм

Вейча (карт Карно).

Способы

минимизации:

алгебраический; с помощью диаграмм

Вейча (карт Карно).

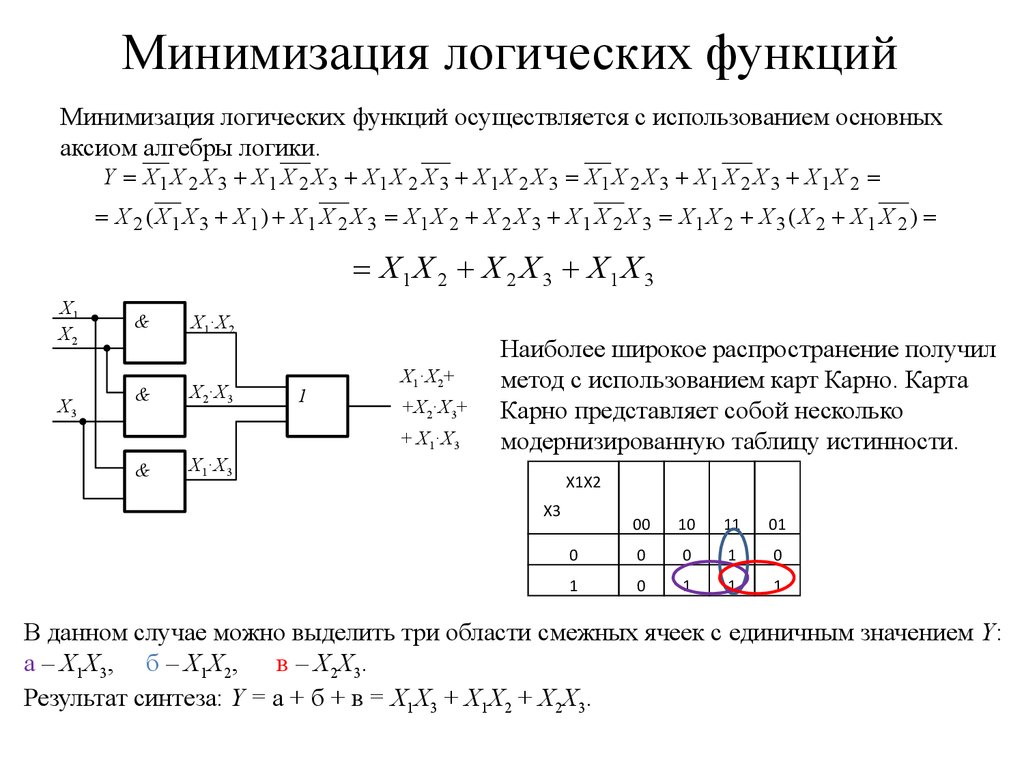

Алгебраический способ минимизации ПФ — используя тождества и теоремы булевой алгебры.

Пример 1. Исходное булево выражение:

Применяя теорему склеивания , получим булево выражение, которое равносильно (эквивалентно) исходному, но значительно проще его.

Диаграммы Вейча построены так, что их соседние клетки содержат члены исходной ПФ, отличающиеся значением одной переменной: один член содержит эту переменную в прямой форме, а другой – в инверсной. Благодаря этому возникает наглядное представление о различных вариантах склеивания смежных членов.

Исходным продуктом для применения диаграмм Вейча является представление ПФ таблицей истинности, в которой возможные наборы переменных упорядочены по возрастанию или по убыванию их десятичных эквивалентов.

Вид

диаграмм Вейча зависит от числа переменных

минимизируемой ПФ — n и от того, как упорядочены наборы

переменных в таблице. Если наборы

упорядочены по возрастанию их десятичных

эквивалентов, то диаграммы Вейча для n=2,3,4 имеют вид, приведенный на рисунке.

Если наборы

упорядочены по возрастанию их десятичных

эквивалентов, то диаграммы Вейча для n=2,3,4 имеют вид, приведенный на рисунке.

Число клеток диаграммы равно количеству наборов переменных: Nкл=Nнаб=2n.

Каждая клетка соответствует определенному набору переменных и имеет номер, одинаковый с номером набора.

Строки и столбцы диаграммы, помеченные чертой, определяют наборы, в которых переменные принимают единичные значения (входят в прямой форме). Строки и столбцы, не помеченные чертой, соответствуют наборам, в которых те же переменные принимают нулевые значения (входят в инверсной форме). В клетки записываются значения ПФ на соответствующем наборе (нулевое или единичное). Если на каком-то наборе функция не определена, то в клетке диаграммы ставится прочерк (или x).

ПФ считается неопределенной, если:

1) данный набор переменных в реальном логическом устройстве невозможен;

2)

значение функции на данном наборе

безразлично.

После заполнения диаграммы можно приступить непосредственно к минимизации, которую производят по единицам или нулям. В первом случае результатом минимизации будет булево выражение в ДНФ, а во втором – в КНФ.

Краткий алгоритм:

Функция, выраженная в СДНФ (СКНФ), записывается в диаграмму Вейча путём проставления единиц (нулей) в соответствующие координаты.

Производится объединение единиц (нулей), стоящих рядом, в так называемые m-кубы. Можно объединять единицы (нули), которые образуют правильный прямоугольник, содержащий 2, 4, 8, 16 единиц (нулей).

Замечание. Необходимо объединять максимально возможное количество смежных клеток, содержащих единицы (нули).

Замечание. Одна и та же единица (нуль) может охватываться несколько раз разными кубами.

Замечание. Верхняя и нижняя строки – смежные (можно

объединить). Левый и правый столбцы –

смежные. Угловые клетки – тоже смежные

(диаграмму можно мысленно свернуть в

тор).

Замечание. Перед выполнением минимизации в клетки, содержащие прочерки (где ПФ не определена), можно записать дополнительные единицы (нули), что способствует получению более простого конечного булевого выражения. При этом следует помнить, что хотя бы один раз необходимо объединить лишь основные единицы (нули). Дополнительные единицы (нули) могут увеличивать суммарное число единиц (нулей), входящих в куб, то есть уменьшать число переменных в результирующих конъюнкциях (дизъюнкциях).

Выписываются координаты получившихся m-кубов.

Объединённая дизъюнкция (конъюнкция) конъюнктивных (дизъюнктивных) координат всех m-кубов и есть минимальная форма.

Целью минимизации является получение минимальной ДНФ или КНФ, содержащей минимум членов с минимальным количеством входящих в них переменных.

Преобразование из базисов СДНФ и СКНФ в базис «Штрих Шеффера» и «Стрелка Пирса» (проверить, работает ли это как для Шеффера, так и для Пирса, сам алгоритм расписан вроде как только для Шеффера

Проставляются скобки;

Все знаки конъюнкции и дизъюнкции заменяются на Штрих Шеффера.

Исключение: если вся функция состоит из одной импликанты, то она берётся с отрицанием.

Исключение: В состав функции входит импликанта из одной буквы – эта импликанта берётся с отрицанием.

Построение — комбинационная схема — Большая Энциклопедия Нефти и Газа, статья, страница 1

Cтраница 1

Построение комбинационной схемы на элементах Вебба, реализующей заданную ( возможно, не полностью определенную) функцию f ( x) и содержащую минимально возможное число элементов, сводится в [131] вначале к нелинейной целочисленной задаче, а затем с помощью искусственного приема, увеличивающего число переменных, к задаче линейного целочисленного программирования. Постановка задачи [131] позволяет также учитывать ограничения по числу связей, числу уровней и числу активных элементов. Однако количество параметров управления в моделях из [131] не позволяет надеяться на получение конструктивных методов экономного синтеза схем из элементов Вебба при булевых функциях сколько-нибудь заметного числа — переменных, встречающихся в практике проектирования.

При построении комбинационных схем

Набор логических элементов для построения комбинационных схем является функционально полным, если реализуемые эт ми элементами булевы функции образуют функционально полную систему функций. [3]

| Синтез произвольного триггерного устройства на базе универсального.| Синтез произвольного триггерного устройства на базе универсального. [4] |

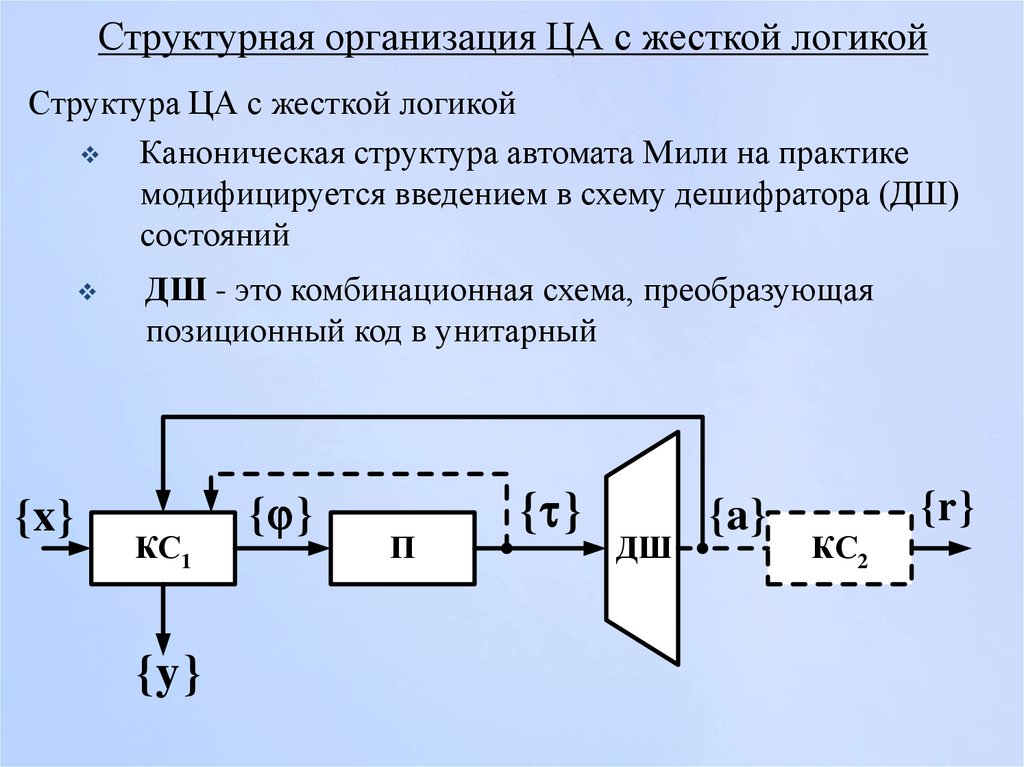

Задача синтеза заключается в построении комбинационной схемы, вырабатывающей сигнал yn Dn, обеспечивающий требуемый закон функционирования. [5]

| Условные обозначения основных логических элементов. [6] |

При полном наборе логических элементов построение комбинационной схемы осуществляется в такой последовательности. По таблице соответствия входных и выходных кодовых сигналов схемы каким-либо способом ( например, при помощи одной из совершенных нормальных форм) подлежащая реализации функция или система функций представляется в виде суперпозиции функций, реализуемых логическими элементами. В соответствии с полученным выражением производится соединение логических элементов, которые и образуют подлежащую построению схему.

[7]

По таблице соответствия входных и выходных кодовых сигналов схемы каким-либо способом ( например, при помощи одной из совершенных нормальных форм) подлежащая реализации функция или система функций представляется в виде суперпозиции функций, реализуемых логическими элементами. В соответствии с полученным выражением производится соединение логических элементов, которые и образуют подлежащую построению схему.

[7]

| Примеры реализации переключательной функции / в ( х, у на различных логических элементах. [8] |

При полном наборе логических элементов построение комбинационной схемы осуществляется в такой последовательности. [9]

Так называемая общая задача комбинационного синтеза состоит в разработке методов построения корректных комбинационных схем, реализующих любые заданные выходные системы булевых функций из логических элементов любых фиксированных типов, при условии, что на входные узлы схемы могут подаваться лишь входные переменные. При этом как в данной задаче, так и в других задачах комбинационного синтеза необходимо заботиться о минимизации числа логических элементов, используемых при построении любой данной схемы.

[10]

При этом как в данной задаче, так и в других задачах комбинационного синтеза необходимо заботиться о минимизации числа логических элементов, используемых при построении любой данной схемы.

[10]

| Двухвходовая схема НЕЧЕТ, построенная из элементов НЕ, И — — ИЛИ ( а и из элементов И — НЕ ( б. [11] |

Проверка на четность параллельного кода осуществляется сложнее и требует для своей реализации построения специальной комбинационной схемы с п входами. [12]

Комплекс элементов обладает функциональной полнотой для построения цифровых автоматов, если он содержит функционально полный набор логических элементов для построения комбинационных схем и элементарный автомат с полной системой выходов и переходов. [13]

Из сказанного следует, что система элементов, обладающая функциональной полнотой для построения цифровых автоматов, должна содержать: во-первых, набор логических элементов, обладающий функциональной полнотой для построения комбинационных схем, и во-вторых, запоминающий элемент или, иначе говоря, элементарный автомат с двумя состояниями. Этот элементарный автомат должен иметь полные системы выходов и переходов с тем, чтобы можно было различить состояние элементарного автомата и применить его в устройствах, где используются все возможные переходы эле-ментарных автоматов.

[14]

Этот элементарный автомат должен иметь полные системы выходов и переходов с тем, чтобы можно было различить состояние элементарного автомата и применить его в устройствах, где используются все возможные переходы эле-ментарных автоматов.

[14]

Из сказанного следует, что система элементов, обладающая функциональной полнотой для построения цифровых автоматов, должна содержать: во-первых, набор логических элементов, обладающий функциональной полнотой для построения комбинационных схем, и во-вторых, запоминающий элемент или, иначе говоря, элементарный автомат с двумя состояниями. Этот элементарный автомат должен иметь полные системы выходов и переходов с тем, чтобы можно было различить состояние элементарного автомата и применить его в устройствах, где используются все возможные переходы элементарных автоматов. [15]

Страницы: 1 2

Построение комбинационных схем

Определение 1

Построение комбинационных схем — это реализация схемы при помощи набора логических элементов на основе таблицы истинности.

Введение

Формирование выходного сигнала на основании обработки входных данных в любом компьютерном оборудовании выполняется формирователями или цифровыми автоматами двух типов:

- Выполненными на основе комбинационных схем.

- Выполненными на основе схем с памятью.

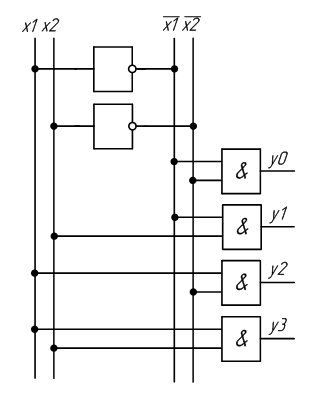

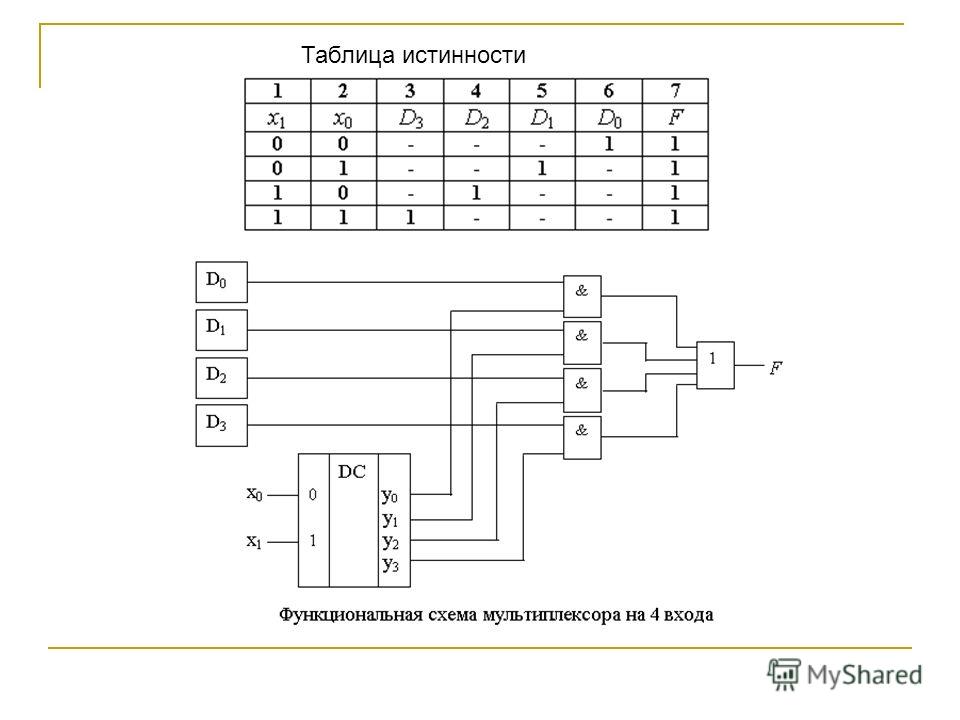

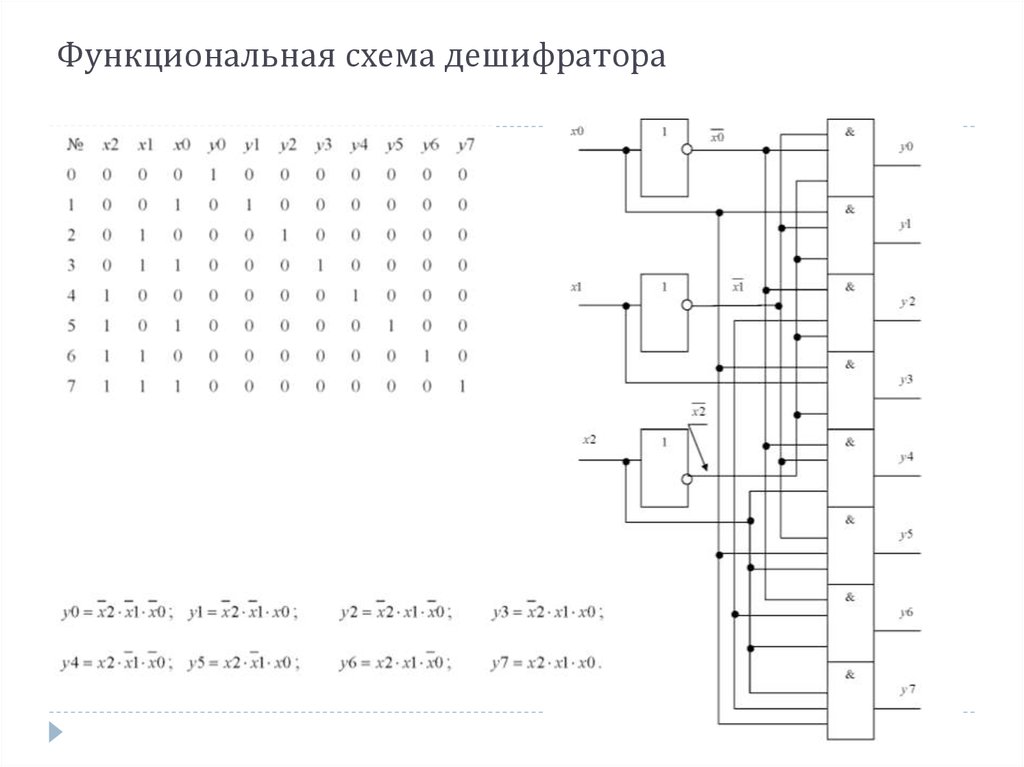

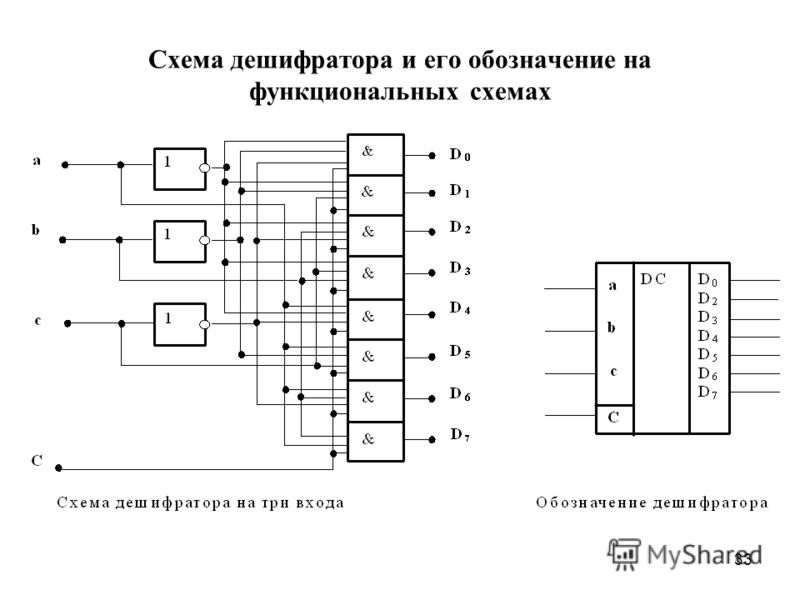

Комбинационными схемами называются схемы, у которых сигналы на выходе $Y = (у_1, у_2,…, у_m)$ в каждый дискретный временной промежуток единообразно задаются набором сигналов на входе $X = (x_1, х_2,…, х_n)$, поступивших в этот же временной момент t. Используемый в комбинационных схемах метод информационной обработки является комбинационным, так как итоги обработки имеют зависимость только лишь от комбинационного набора входных сигналов и они образуются сразу при появлении сигналов на входе. И это обстоятельство объясняет главное достоинство комбинационных схем, а именно высокое быстродействие. Информационные преобразования могут быть однозначно описаны функциями логики типа Y = f(X). n$ выходов. Одиночный сигнал, сформированный на каком либо из m выходов, является однозначным соответствием комбинированного набора входных сигналов. К примеру, рассмотрим структуру дешифратора при n = 3, согласно таблице истинности, приведённой на рисунке ниже:

n$ выходов. Одиночный сигнал, сформированный на каком либо из m выходов, является однозначным соответствием комбинированного набора входных сигналов. К примеру, рассмотрим структуру дешифратора при n = 3, согласно таблице истинности, приведённой на рисунке ниже:

Рисунок 1. Таблица истинности. Автор24 — интернет-биржа студенческих работ

Дешифраторы повсеместно применяются в компьютерном оборудовании для того, чтобы выбрать информацию по заданному адресу, расшифровать код операции и так далее. Ниже приведены логические формулы данного дешифратора:

Рисунок 2. Логические формулы дешифратора. Автор24 — интернет-биржа студенческих работ

Данный дешифратор может быть реализован на основе логических элементов (И, НЕ), где кружки на выходе логических элементов обозначают логическое отрицание функций, которые реализуют элементы. Структурная схема дешифратора приведена на рисунке ниже и там же показано, как он отображается на принципиальной схеме электронной вычислительной машины:

Рисунок 3. Схема ЭВМ. Автор24 — интернет-биржа студенческих работ

Схема ЭВМ. Автор24 — интернет-биржа студенческих работ

Шифраторы осуществляют решение задачи, обратной дешифрации, то есть по нумерации сигнала на входе выполняется формирование однозначного комбинационного набора сигналов на выходе.

Сумматоры

Комбинационные сумматоры тоже считаются часто применяемым в компьютерном оборудовании элементом. Структурная организация и принцип действия сумматора определяются законами бинарного сложения. Принцип работы многоразрядного сумматора базируется на правилах одноразрядного суммирования двоичных чисел. Рассмотрим пример сумматора, который выполняет суммирование двух одноразрядных чисел аi и bi при отсутствии переноса из предыдущих разрядов. То есть, это может быть, к примеру, суммирование младшего разряда в бинарном коде. Таблица истинности для такой операции суммирования, приведена ниже:

Рисунок 4. Таблица истинности. Автор24 — интернет-биржа студенческих работ

Логические формулы сумматора:

Рисунок 5. Логические формулы сумматора. Автор24 — интернет-биржа студенческих работ

Логические формулы сумматора. Автор24 — интернет-биржа студенческих работ

Здесь $S_i$ является функцией суммы одного разряда, а $Р_i$ является функцией наличия переноса. Она принимает значение, равное единице, то есть присутствует перенос в следующий разряд, когда $a_i = 1$ и $b_i = 1$.

Схема такого полусумматора (а) и его обозначение в схеме компьютера (б) представлены на следующем рисунке:

Рисунок 6. Схема полусумматора. Автор24 — интернет-биржа студенческих работ

Формулы, заложенные в основание одноразрядных сумматоров, применяются и при реализации сумматоров, рассчитанных на большое количество разрядов. Отличие таблиц истинности одноразрядного сумматора (полусумматора) от таблицы истинности сумматоров, которые учитывают переносы, заключается в наличии дополнительного входа р, являющегося обозначением переноса из предыдущего разряда.

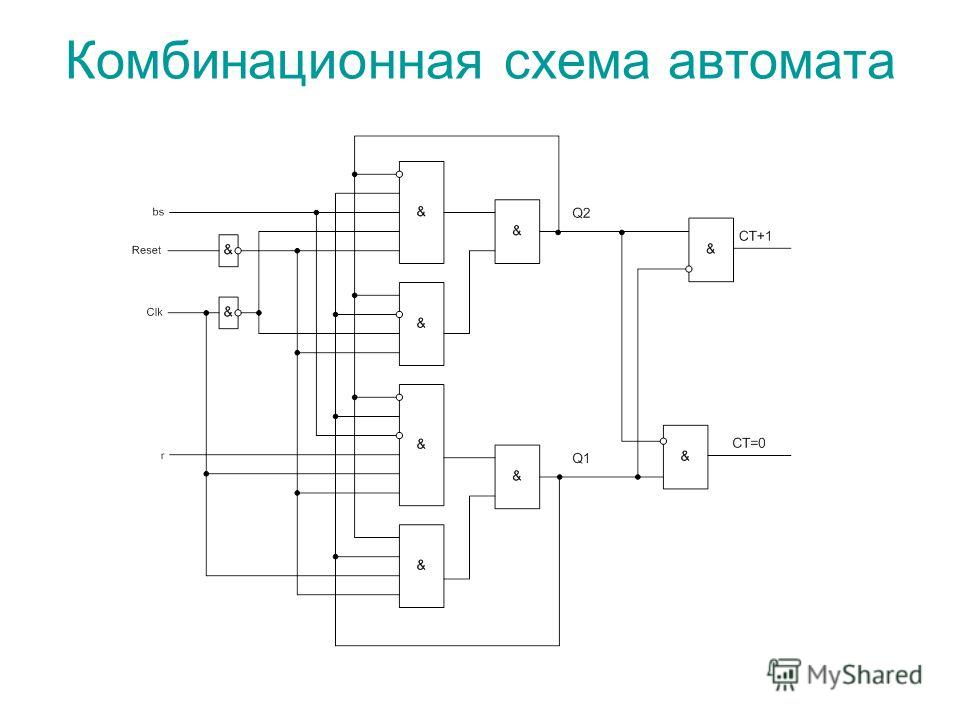

Схемы с памятью

Схемы с памятью считаются более сложными информационными преобразователями. Присутствие элемента памяти в схемной организации даёт возможность запоминания промежуточных состояний работы с сигналами и учёта их величин при последующих действиях. Формирование выходных сигналов $Y = (y_1,y_2,…,y_m)$ в таких схемных организациях осуществляется, помимо учёта набора входных сигналов $X = (х_1,х_2,…,х_п)$, ещё и с учётом набора состояний схем памяти $Q = (q_1,q_2,…,q_k)$. Для правильного учёта этого обстоятельства, вводится отличие текущего дискретного момента времени t и следующего временного момента (t+1). Обобщённая структурная организация схемы, имеющей внутреннюю память, представлена на рисунке ниже.

Присутствие элемента памяти в схемной организации даёт возможность запоминания промежуточных состояний работы с сигналами и учёта их величин при последующих действиях. Формирование выходных сигналов $Y = (y_1,y_2,…,y_m)$ в таких схемных организациях осуществляется, помимо учёта набора входных сигналов $X = (х_1,х_2,…,х_п)$, ещё и с учётом набора состояний схем памяти $Q = (q_1,q_2,…,q_k)$. Для правильного учёта этого обстоятельства, вводится отличие текущего дискретного момента времени t и следующего временного момента (t+1). Обобщённая структурная организация схемы, имеющей внутреннюю память, представлена на рисунке ниже.

Рисунок 7. Обобщённая структурная организация схемы, имеющей внутреннюю память. Автор24 — интернет-биржа студенческих работ

Осуществление передачи величины Q между временными моментами t и (t+1) выполняется, как правило, с использованием памяти, имеющей две ступени, и специальных синхроимпульсов. Простейшим элементом памяти в компьютерном оборудовании являются триггерные схемы. В своё время эти компоненты заменили в электронных вычислительных машинах запоминающие элементы памяти, работающие на основе остаточной намагниченности ферритовых сердечников.

В своё время эти компоненты заменили в электронных вычислительных машинах запоминающие элементы памяти, работающие на основе остаточной намагниченности ферритовых сердечников.

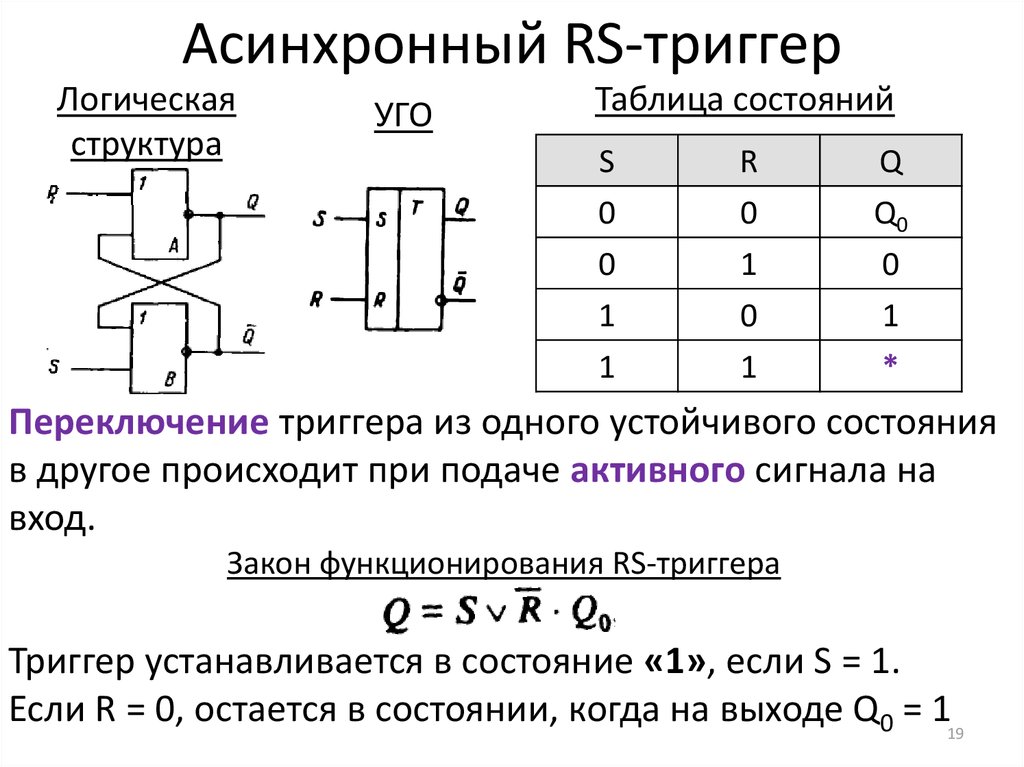

Рассмотрим пример построения элемента памяти на триггерной основе, который имеет два входа:

- R (Reset, что означает сброс), предназначенный для сброса триггера в исходное состояние.

- S (Set, что означает установка), предназначенный для перевода триггера в состояние запоминания единицы.

Если на триггер не поступают входные сигналы, то он обязан в том же состоянии до момента, пока не поступит сигнал на один из входов. На рисунке а) показана схема триггера, на рисунке б) обозначение на общих схемах и на рисунке в) диаграмма работы триггера.

Рисунок 8. Схемы и диаграмма. Автор24 — интернет-биржа студенческих работ

Проектирование комбинационных логических схем

Несмотря на то, что инструменты САПР используются на практике для создания комбинационных логических схем, важно, чтобы цифровая

дизайнер должен научиться генерировать логическую схему из спецификации. Понимание этого процесса позволяет

дизайнеру лучше использовать инструменты САПР и, при необходимости, вручную проектировать важные логические подсхемы.

Понимание этого процесса позволяет

дизайнеру лучше использовать инструменты САПР и, при необходимости, вручную проектировать важные логические подсхемы.

Процедура проектирования

Процедура проектирования комбинационных логических схем начинается со спецификации задачи и включает следующие шаги:

- Определить необходимое количество входов и выходов из спецификаций.

- Получите таблицу истинности для каждого из выходных данных на основе их отношения к входным данным.

- Упростите логическое выражение для каждого выхода. Используйте Карты Карно или Булеву алгебру.

- Нарисуйте логическую схему, представляющую упрощенное логическое выражение. Проверьте конструкцию, проанализировав или имитация цепи.

Примеры

Ввод больше или равен 5?

Спецификация

Разработайте схему с 3-битным двоичным входом и одним выходом (Z), указанными ниже:

- Z = 0, если вход меньше 5 10

- Z = 1, иначе

Определить входы и выходы

- Обозначьте входы (3 бита) как A, B, C

- A — старший бит

- C — младший бит

- Выход (1 бит) Z

- Z = 1 -> 101 2 , 110 2 , 111 2

- Z = 0 -> другие входы

- Обозначьте входы (3 бита) как A, B, C

Получить таблицу истинности

Упростить логическое выражение

Из таблицы истинности мы используем один из следующих 2 методов для получения упрощенного логического выражение

- Используйте карту Карно, чтобы свести к минимуму логику или

- Из таблицы истинности найдите каноническую сумму

Логическое выражение продуктов.

Z = А * ~ В * С + А * В * ~ С + А * В * С

Используйте булеву алгебру, чтобы упростить

логическое выражение для: Z = (В + С) * А

Z = А * ~ В * С + А * В * ~ С + А * В * С

Используйте булеву алгебру, чтобы упростить

логическое выражение для: Z = (В + С) * А

Нарисуйте логическую схему

Нарисуйте логическую схему, представляющую упрощенное логическое выражение. Проверьте дизайн по анализ или моделирование схемы.

BCD в 7-сегментный декодер

Спецификация

Разработка схемы декодера из двоично-десятичного кода в 7 сегментов для сегмента e который имеет 4-битный двоичный вход и один выход (7e), заданный таблицей истинности

Определить входы и выходы

- Обозначьте входы (4 бита) как A, B, C, D

- D — старший бит

- A — младший значащий бит

- Выход (1 бит) 7e — сегмент e 7-сегментного дисплея

- Обозначьте входы (4 бита) как A, B, C, D

Получить таблицу правды

Получено от BCD до 7-сегментного декодера истины стол.

Обратите внимание, что 7e получено из столбца e.

Обратите внимание, что 7e получено из столбца e.Упростить логическое выражение

Из таблицы истинности мы используем один из следующих 2 методов для получения упрощенного логического выражение

- Использование логической алгебры для упрощения канонической суммы произведений boolean выражение, полученное из таблицы истинности или

- Используйте карту Карно, чтобы свести к минимуму логику. Из карты Карно мы получили следующее логическое выражение: 7e = ~D*B*~A + ~C*~B*~A

Нарисуйте логическую схему

Нарисуйте логическую схему, представляющую упрощенное логическое выражение.

Проверьте дизайн по

анализ или моделирование схемы.

Проверьте дизайн по

анализ или моделирование схемы.

Другие примеры

Сигнализация банка

Банк хочет установить систему сигнализации с 3 датчиками движения.

Для предотвращения ложных срабатываний при срабатывании одного датчика, тревога будет срабатывать только при наличии хотя бы двух датчики срабатывают одновременно.

Детектор простых чисел

Разработайте схему с 3-битным двоичным входом и одним выходом,

- выведите 1, если это простое число. например, 2 10 , 3 10 , 5 10 , 7 10

- , иначе выведите 0.

Сравните два однобитовых числа

Имея два входных бита A и B, выведите три выходных значения X, Y и Z так, чтобы

- X равно 1 только тогда, когда A > B,

- Y равен 1, только когда A Z равен 1, только когда A = B

Узнать больше примеров

Введение в комбинационные логические схемы

Цифровые сигналы обрабатываются цифровой системой, которая может быть построена с использованием различных логических элементов. Эти логические схемы состоят из различных логических вентилей, соединяя их в определенных комбинациях, чтобы получить требуемый результат. Цифровые логические схемы в основном подразделяются на два типа: последовательные логические схемы и комбинационные логические схемы. Эта статья дает краткое представление о комбинационных логических схемах.

Эти логические схемы состоят из различных логических вентилей, соединяя их в определенных комбинациях, чтобы получить требуемый результат. Цифровые логические схемы в основном подразделяются на два типа: последовательные логические схемы и комбинационные логические схемы. Эта статья дает краткое представление о комбинационных логических схемах.

[адсенс1]

Краткое описание

Комбинационные логические схемы

Комбинационная логическая схема — это схема , в которой текущее состояние комбинации логических входов определяет выход . Термин комбинированная логика означает объединение двух или более логических вентилей для формирования требуемой функции, где выход в данный момент времени зависит только от входа.

Логические элементы являются основными строительными блоками комбинационной схемы. Используя комбинацию логических вентилей, можно реализовать более сложные комбинационные схемы, такие как мультиплексоры и демультиплексоры, компараторы, сумматоры и вычитатели и т. д.

д.

Комбинированная схема состоит из входных переменных, логических вентилей и выходных переменных. Логические элементы принимают входы и в зависимости от типа функционирования логических элементов формируются выходные сигналы.

Требуемые выходные данные получаются из этого процесса путем преобразования двоичной информации, заданной на входе. На рисунке ниже показано схематическое представление обобщенной комбинационной логической схемы, состоящей из n входных переменных и m выходных переменных.

На приведенном выше рисунке имеется n входных переменных и, следовательно, на входе будет 2n возможных комбинаций битов. Булевым выражением входных переменных выражается каждый выход. Таким образом, результат вышеприведенной обобщенной комбинационной логической схемы может быть выражен m булевыми выражениями.

На приведенном выше рисунке схема принимает двоичные переменные и в зависимости от логической комбинации вентилей генерирует выходные данные.

Наверх

[адсенс2]

Процедура проектирования комбинационных логических схем

Комбинационная схема может быть разработана с использованием следующих шагов.

- Идентификация и определение количества доступных входных переменных и требуемых выходных переменных.

- Представление символов (алфавитов) для всех без исключения входных и выходных переменных.

- Выражение отношения входной и выходной переменных.

- Построение таблицы истинности, указывающей взаимосвязь между входными и выходными переменными.

- Получение логического выражения для каждой выходной переменной через входные переменные.

- Минимизация логических выражений различных выходных переменных.

- Получение логической схемы реализацией минимизированных логических выражений.

Для минимизации логических выражений доступны различные методы упрощения, позволяющие уменьшить количество логических элементов и, следовательно, снизить стоимость реализации. Эти методы включают теоремы и тождества булевой алгебры, карты Карно (K-карты), табулирование Куинна-МакКласки и т. Д. Для аппаратной реализации комбинационной схемы в основном предпочтительны следующие рекомендации.

- Реализация схемы должна быть такой, чтобы она имела минимальное количество элементов, имеющих минимальное количество входов.

- Количество взаимосвязей между шлюзами должно быть минимальным, а время распространения должно быть минимальным.

- Всегда должно быть ограничение на проходимость ворот.

Это простой, эффективный и традиционный метод проектирования комбинационной схемы для малых цепей. Если схема более сложная, требуется больше вентилей, а также требуется большее количество проводов между ними. Следовательно, проектирование таких схем может быть менее надежным и трудоемким.

Чтобы преодолеть эти проблемы, большинство комбинационных схем доступны в виде интегральных схем (ИС), которые широко используются при разработке цифровых систем. В зависимости от интеграционных возможностей вентилей эти ИС подразделяются на малые, средние, большие и очень большие ИС.

Для выполнения определенных цифровых функций, таких как сложение, мультиплексирование, демультиплексирование, кодирование, декодирование, сравнение и т. д., в цифровых системах в основном используются интегральные схемы среднего масштаба (MSI).

д., в цифровых системах в основном используются интегральные схемы среднего масштаба (MSI).

Вернуться к началу

Пример комбинационной логической схемы

Утверждение. Разработайте комбинационную логическую схему с тремя входными переменными так, чтобы она выдавала на выходе логическую 1, когда одна или две входные переменные равны логической 1, но не все три.

Решение: Следуйте приведенным выше пунктам, чтобы разработать логическую схему в соответствии с данным утверждением. В данном операторе есть три входных переменных и одна выходная переменная. В качестве второго шага назначьте входным переменным буквенные символы как A, B, C и выходным как Y. Затем можно свести в таблицу взаимосвязь между входными и выходными переменными, построив таблицу истинности, как показано ниже.

Теперь упрощенное логическое выражение для приведенной выше таблицы истинности для получения выходных данных Y получается с использованием упрощения K-карты как

Применяя приведенное выше логическое уравнение, мы получаем логическую диаграмму как

Назад наверх

Классификация комбинационных логических схем

Комбинационные схемы используются в самых разных приложениях, включая калькуляторы, цифровые измерительные приборы, компьютеры, цифровую обработку, автоматическое управление машинами, промышленную обработку, цифровую связь и т. д.

д.

Различные типы комбинационных логических схем используются для различных приложений. В зависимости от функции используемой логической схемы, комбинационные логические схемы в основном подразделяются на три типа, а именно арифметические и логические схемы, схемы передачи данных и схемы преобразователя кода.

Арифметические и логические схемы

Арифметические операции являются одной из основных функций большинства компьютеров и калькуляторов. Эти операции выполняются логическими элементами или просто комбинационными схемами, которые объединяют несколько логических элементов для выполнения требуемой функции. Эти арифметические функции комбинационных схем включают сложение, вычитание, умножение и т. д.

Некоторые из комбинационных схем, используемых для этих операций: полусумматор, полный сумматор, полувычитатель, полный вычитатель, сумматор-вычитатель, компаратор, PLD (программируемое логическое устройство) и т. д.

Цепи передачи данных

наиболее часто используемыми комбинационными схемами являются мультиплексоры и демультиплексоры. Логическая схема мультиплексора принимает несколько входных данных и пропускает один из них через выход за раз. Они используются для выбора данных, параллельного последовательного преобразования, приложений маршрутизации данных в цифровых системах.

Логическая схема мультиплексора принимает несколько входных данных и пропускает один из них через выход за раз. Они используются для выбора данных, параллельного последовательного преобразования, приложений маршрутизации данных в цифровых системах.

Схема демультиплексора выполняет операцию, обратную мультиплексору. Он принимает один вход и распределяет его на несколько выходов. Они используются в распределителях, а также в последовательно-параллельных преобразователях.

Другие важные схемы передачи данных включают кодеры и декодеры. Логическая схема декодера преобразует n-битный двоичный входной код в 2n выходных строк. Каждая выходная линия активируется только для одной из возможных комбинаций входов.

Они используются в демультиплексировании данных, цифро-аналоговых преобразователях и цифровых дисплеях. Цифровая схема энкодера преобразует активный входной сигнал в закодированный выходной сигнал как операцию, обратную декодеру. Они используются в приложениях для сжатия битов.

Схемы преобразователя кодов

В некоторых приложениях требуется сопряжение двух цифровых блоков с разными системами кодирования. Таким образом, между такими схемами используется схема преобразования для преобразования информации. Некоторые из этих преобразователей представляют собой двоичный код в код Грея, код Грея в двоичный, двоично-десятичный код в код избытка-3, избыток-3 в код в двоично-десятичном коде и схемы преобразователя семисегментного кода.

Вернуться к началу

DIGITAL BASIC — 1.4: Комбинированные схемы |Концепции СБИС

Алфавитный указатель

!doctype>

DIGITAL BASIC — 1.4: Комбинационные схемы

ВведениеЦифровые схемы бывают двух типов:

- Комбинационные схемы (также известные как независимая от времени логика)

- Комбинированные цифровые схемы — это схемы, в которых выход является функцией только текущего входа.

- Последовательные цепи

- Вывод зависит не только от текущего ввода, но и от истории ввода

Давайте обсудим эти схемы в формате сравнительной таблицы.

Комбинационные циклы | последовательные цирки | ||

nomable (no no unmement).0003 | |||

Выход является функцией Текущего входа. Выход = ƒ(In) | Выход является функцией текущего + предыдущего ввода. Выход = ƒ(In, предыдущий In) | ||

Для проектирования используются базовые вентили (И, ИЛИ, НЕ) или универсальные вентили (НЕ-И, ИЛИ-НЕ) | основной строительный блок во всех цифровых схемах, а также в схемах памяти и других устройствах. | ||

Примеры комбинационных цифровых схем: Полусумматор, Полный сумматор, Полувычитатель, Полный вычитатель, Преобразователь кода, Декодер, Мультиплексор, Демультиплексор, Кодировщик, ПЗУ и т. д. | 9029 Примеры для цифровых последовательностей схемы: Регистры, регистры сдвига, счетчики и т. д. | ||

Построение комбинационной логики обычно выполняется одним из двух методов:

| Построение последовательной логики обычно выполняется с использованием таблиц состояний. | ||

быстрее, потому что задержка между входом и выходом обусловлена более медленной цепи | . | Легко спроектировать | Сравнительно сложно спроектировать |

Классификация комбинационных логических схем:

- 10 Арифметические и логические функции

- Добавители

- Вычитатели

- Компараторы

- PLD

- Передача данных

- Мультиплексоры

- Демультиплексоры

- Декодеры

- Энкодеры

- Преобразователи кодов

- Двоичный преобразователь

- BCD преобразователь

- 7-сегментный дисплей

Классификация последовательных цепей

- Синхронных цепей

- Асинхронные цепи

Синхронные последовательные цепи | Асинхронные последовательные цепи | 0329 Элементы памяти представляют собой триггеры с тактовой частотой | Элементы памяти представляют собой либо нетактируемые триггеры, либо элементы с временной задержкой |

Изменение входного сигнала может повлиять на элементы памяти при активации тактового сигнала | 9092 входной сигнал может воздействовать на элементы памяти в любой момент времени.|

Максимальная рабочая скорость часов зависит от задействованной временной задержки | Из-за отсутствия часов асинхронные схемы могут работать быстрее, чем синхронные. |

Легко в проектировании | Более сложно разработать |

. СОСТОЯНИЕ СОСТОЯНИЕ ВРЕМЕНИ ДЕЙСТВИЯ ВРЕМЕНИ В Ответ на такси 43334797 |

Комбинированные схемы:

Давайте обсудим некоторые детали комбинационной схемы (например, блок-схему, принципиальную схему и таблицу истинности). Я не буду подробно обсуждать принципиальную схему здесь, потому что она очень проста. В некоторых случаях, если у вас возникнет путаница, вы можете обратиться к любым книгам по основам электроники. Или вы можете использовать K-карту, чтобы выяснить уравнения, которые упоминаются либо в блок-схеме, либо в принципиальной схеме.

Я не буду подробно обсуждать принципиальную схему здесь, потому что она очень проста. В некоторых случаях, если у вас возникнет путаница, вы можете обратиться к любым книгам по основам электроники. Или вы можете использовать K-карту, чтобы выяснить уравнения, которые упоминаются либо в блок-схеме, либо в принципиальной схеме.

Circuit name | Block diagram | Circuit Diagram | Truth table | |||||||||||||||||||||||||||

Half Adder | | | ||||||||||||||||||||||||||||

Full Adder | |

| ||||||||||||||||||||||||||||

Half Subtractor | ||||||||||||||||||||||||||||||

Decoder (Active high) |

| |||||||||||||||||||||||||||||

Decoder (Active low) |

| |||||||||||||||||||||||||||||

De-Multiplexer | |

| ||||||||||||||||||||||||||||

Multiplexer | |

Важные моменты:

- Полусумматор можно преобразовать в полувычитатель с помощью дополнительного инвертора.

- Полный сумматор может быть реализован с использованием двух половинных сумматоров и вентиля ИЛИ.

- Полный вычитатель может быть реализован с использованием двух половинных вычитателей и вентиля ИЛИ.

- Полный сумматор может быть преобразован в полный вычитатель с помощью дополнительного инвертора.

- Полный сумматор 2 типа

- Сумматор переноса пульсации.

- Упреждающий сумматор переноса

- Четырехбитный двоичный параллельный сумматор может быть построен с использованием

- 3 полных сумматора и 1 полусумматор или

- 4 полных сумматора с входным переносом младшего значащего бита полный сумматор равен нулю.

| 4 бит FA: Использование 4 полных сумматора (младший бит переноса FA = 0)0341 |

| 4 бит FA: 3 полных сумматора + 1 полусумматор |

Важные моменты:

- Декодер

- Преобразует двоичную информацию из «n» входных строк в максимум 2 n уникальных выходных строк.

Z = А * ~ В * С + А * В * ~ С + А * В * С

Используйте булеву алгебру, чтобы упростить

логическое выражение для: Z = (В + С) * А

Z = А * ~ В * С + А * В * ~ С + А * В * С

Используйте булеву алгебру, чтобы упростить

логическое выражение для: Z = (В + С) * А  Обратите внимание, что 7e получено из столбца e.

Обратите внимание, что 7e получено из столбца e. Проверьте дизайн по

анализ или моделирование схемы.

Проверьте дизайн по

анализ или моделирование схемы.

0328

0328