Логические микросхемы. Часть 2 — логические элементы

Логические элементы, работают как самостоятельные элементы в виде микросхем малой степени интеграции, так и входят в виде компонентов в микросхемы более высокой степени интеграции.

Логические элементы, работают как самостоятельные элементы в виде микросхем малой степени интеграции, так и входят в виде компонентов в микросхемы более высокой степени интеграции. Таких элементов можно насчитать не один десяток.

Но сначала расскажем только о четырех из них — это элементы И, ИЛИ, НЕ, И-НЕ. Основными элементами являются первые три, а элемент И-НЕ это уже комбинация элементов И и НЕ. Эти элементы можно назвать «кирпичиками» цифровой техники. Для начала следует рассмотреть, какова же логика их действия?

Вспомним первую часть статьи о цифровых микросхемах. Там было сказано, что напряжение на входе (выходе) микросхем в пределах 0…0,4В это уровень логического нуля, или напряжение низкого уровня. Если же напряжение в пределах 2,4…5,0В, то это уровень логической единицы или напряжение высокого уровня.

Рабочее состояние микросхем серии К155 и других микросхем с напряжением питания 5В характеризуется именно такими уровнями. Если на выходе микросхемы напряжение находится в диапазоне 0,4…2,4В (например 1,5 или 2,0В), то можно уже задуматься о замене данной микросхемы.

Практический совет: чтобы убедиться, что неисправна по выходу именно эта микросхема, следует отсоединить от нее вход следующей за ней микросхемы (или несколько входов, подключенных к выходу данной микросхемы). Эти входы могут просто «подсаживать» (перегружать) микросхему по выходу.

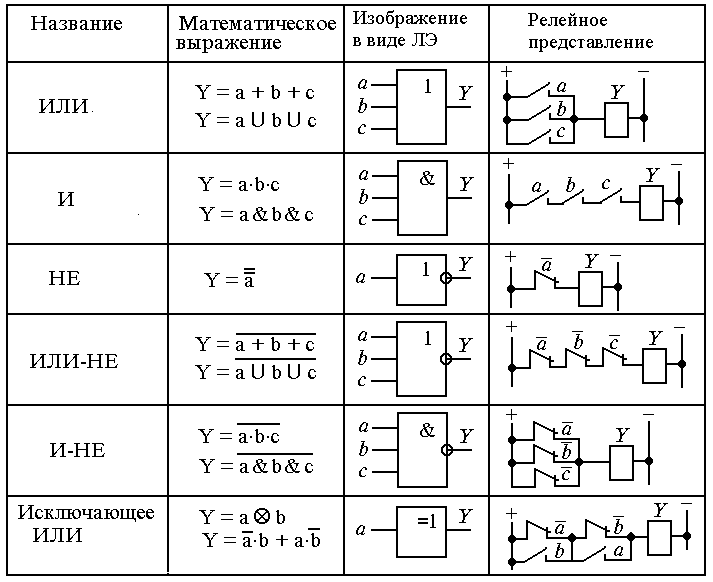

Условные графические обозначения

Условные графические обозначения представляют собой прямоугольник, содержащий входные и выходные линии. Входные линии элементов располагаются слева, а выходные справа. То же касается и целых листов со схемами: с левой стороны все сигналы входные, с правой выходы. Это как в книжке строка, — слева направо, так будет проще запомнить. Внутри прямоугольника находится условный символ, обозначающий функцию, выполняемую элементом.

Логический элемент И

Рассмотрение логических элементов начнем с элемента И.

Рисунок 1. Логический элемент И

Его графическое обозначение показано на рисунке 1а. Условным обозначением функции И служит английский символ «&», который в английском языке заменяет союз «и», ведь все-таки, вся эта «лженаука» изобреталась в проклятом буржуинстве.

Входы элемента обозначены как X с индексами 1 и 2, а выход, как выходная функция, буквой Y. Просто, как в школьной математике, например, Y = K*X или, в общем случае, Y = f(x) . Входов у элемента может быть и больше, чем два, что ограничивается только сложностью решаемой задачи, но, выход может быть только один.

Логика работы элемента следующая: напряжение высокого уровня на выходе Y будет лишь тогда, когда И-на входе X1 И-на входе X2 будет напряжение высокого уровня. Если входов у элемента будет 4 или 8, то указанное условие (наличие высокого уровня), должно выполняться на всех входах: И-на входе 1, И-на входе 2, И-на входе3 …. .И-на входе N. Лишь в этом случае на выходе будет также высокий уровень.

.И-на входе N. Лишь в этом случае на выходе будет также высокий уровень.

Для того, чтобы было проще разобраться в логике работы элемента И, на рисунке 1б представлен его аналог в виде контактной схемы. Здесь выход элемента Y представлен лампой HL1. Если лампа светится, то это соответствует высокому уровню на выходе элемента И. Часто такие элементы называют 2-И, 3-И, 4-И, 8-И. Первая цифра указывает на количество входов.

В качестве входных сигналов X1 и X2 используются обычные «звонковые» кнопки без фиксации. Разомкнутое состояние кнопок это состояние низкого уровня, а замкнутое, естественно, высокого. В качестве источника питания на схеме показана гальваническая батарея. Пока кнопки находятся в незамкнутом состоянии, лампа, конечно, не светит. Лампа включится лишь только тогда, когда будут нажаты сразу обе кнопки, т.е. И-SB1, И-SB2. Такова логическая связь между входными и выходным сигналом элемента И.

Наглядное представление о работе элемента И можно получить глядя на временную диаграмму, показанную на рисунке 1в. Сначала сигнал высокого уровня появляется на входе X1, но на выходе Y ничего не произошло, там по-прежнему сигнал низкого уровня. На входе X2 сигнал появляется с некоторой задержкой относительно первого входа, и на выходе Y появляется сигнал высокого уровня.

Сначала сигнал высокого уровня появляется на входе X1, но на выходе Y ничего не произошло, там по-прежнему сигнал низкого уровня. На входе X2 сигнал появляется с некоторой задержкой относительно первого входа, и на выходе Y появляется сигнал высокого уровня.

Когда на входе X1 сигнал принимает низкий уровень, на выходе также устанавливается сигнал низкого уровня. Или, если сказать по-другому, сигнал высокого уровня на выходе удерживается до тех пор, пока на обоих входах присутствуют сигналы высокого уровня. То же самое можно сказать и о более многовходовых элементах И: если это будет 8-И, то чтобы на выходе получить высокий уровень, высокий же уровень должен удерживаться сразу на всех восьми входах.

Чаще всего в справочной литературе состояние выхода логических элементов в зависимости от входных сигналов приводится в виде таблиц истинности. Для рассматриваемого элемента 2-И таблица истинности приведена на рисунке 1г.

Таблица несколько похожа на таблицу умножения, только поменьше. X2 .

X2 .

Логический элемент ИЛИ

Следующим мы рассмотрим логический элемент ИЛИ.

Рисунок 2. Логический элемент ИЛИ

Его графическое обозначение похоже на только что рассмотренный элемент И, за исключением того, что вместо знака &, обозначающего функцию И, внутри прямоугольника вписана цифра 1, как показано на рисунке 2а. В данном случае она обозначает функцию ИЛИ. Слева расположены входы X1 и X2, которых, как и в случае функции И может быть и больше, а справа выход, обозначенный буквой Y.

В виде формулы булевой алгебры функция ИЛИ записывается так Y = X1 + X2.

Согласно этой формуле Y будет истинным тогда, когда ИЛИ на входе X1, ИЛИ на входе X2, ИЛИ на обоих входах сразу будет высокий уровень.

Понять только что сказанное поможет контактная схема, представленная на рисунке 2б: нажатие на любую из кнопок (высокий уровень) или на обе кнопки сразу, приведет к свечению лампочки (высокий уровень). В данном случае кнопки это входные сигналы X1 и X2, а лампочка выходной сигнал Y. Чтобы сказанное было проще запомнить, на рисунках 2в и 2г приведены временная диаграмма и таблица истинности соответственно: достаточно проанализировать работу показанной контактной схемы с диаграммой и таблицей, как все вопросы исчезнут.

Чтобы сказанное было проще запомнить, на рисунках 2в и 2г приведены временная диаграмма и таблица истинности соответственно: достаточно проанализировать работу показанной контактной схемы с диаграммой и таблицей, как все вопросы исчезнут.

Логический элемент НЕ, инвертор

Как говорил один преподаватель, — в цифровой технике нет ничего сложнее инвертора. Пожалуй, так и есть на самом деле.

В алгебре логики операция НЕ называется инверсией, что в переводе с английского означает отрицание, то есть уровень сигнала на выходе с точностью до наоборот соответствует входному сигналу, что в виде формулы выглядит как Y = /X

(Косая черта перед X обозначает собственно инверсию. Обычно вместо косой используется подчеркивание сверху, хотя вполне допустимо и такое обозначение.).

Условное графическое обозначение элемента НЕ представляет собой квадрат или прямоугольник, внутри которого вписана цифра 1.

Рисунок 3. Инвертор

В данном случае она обозначает, что этот элемент – инвертор. Он имеет всего один вход X и выход Y. Линия выхода начинается маленьким кружком, собственно который и говорит о том, что этот элемент инвертор.

Он имеет всего один вход X и выход Y. Линия выхода начинается маленьким кружком, собственно который и говорит о том, что этот элемент инвертор.

Как только что было сказано – инвертор самая сложная схема цифровой техники. И это подтверждает его контактная схема: если до этого было достаточно лишь только кнопок, то теперь к ним добавилось реле. Пока кнопка SB1 не нажата (логический ноль на входе) реле K1 обесточено и его нормально-замкнутые контакты включают лампочку HL1, что соответствует логической единице на выходе.

Если же нажать кнопку (подать на вход логическую единицу), то реле включится, контакты K1.1 разомкнутся, лампочка погаснет, что соответствует логическому нулю на выходе. Сказанное подтверждают временная диаграмма на рисунке 3в и таблица истинности на рисунке 3г.

Логический элемент И-НЕ

Логический элемент И-НЕ есть не что иное, как сочетание логического элемента И с элементом НЕ.

Рисунок 4. Логический элемент И-НЕ

Логический элемент И-НЕ

Поэтому на его условном графическом обозначении присутствует знак & (логическое И), а линия выхода начинается с кружочка, указывающего на наличие в составе элемента инвертора.

Контактный аналог логического элемента показан на рисунке 4б, и, если присмотреться, очень похож на аналог инвертора показанного на рисунке 3б: лампочка включена также через нормально-замкнутые контакты реле К1. Собственно это и есть инвертор. Реле управляется кнопками SB1 и SB2, которые соответствуют входам X1 и X2 логического элемента И-НЕ. На схеме видно, что реле будет включено только тогда, когда будут нажаты обе кнопки: в данном случае кнопки выполняют функцию & (логическое И). При этом лампа на выходе погаснет, что соответствует состоянию логического нуля.

Если же не нажаты обе кнопки, или хотя бы одна из них, то реле отключено, и лампочка на выходе схемы горит, что соответствует уровню логической единицы.

Из всего сказанного можно сделать следующие выводы:

Во-первых, если хотя бы на одном входе присутствует логический нуль, то на выходе будет логическая единица. То же состояние на выходе будет и в случае, когда нули присутствуют сразу на обоих входах. Это весьма ценное свойство элементов И-НЕ: если соединить оба входа, то элемент И-НЕ становится инвертором, — просто выполняет функцию НЕ. Такое свойство позволяет не ставить специальную микросхему, содержащую сразу шесть инверторов, когда требуется всего один или два.

То же состояние на выходе будет и в случае, когда нули присутствуют сразу на обоих входах. Это весьма ценное свойство элементов И-НЕ: если соединить оба входа, то элемент И-НЕ становится инвертором, — просто выполняет функцию НЕ. Такое свойство позволяет не ставить специальную микросхему, содержащую сразу шесть инверторов, когда требуется всего один или два.

Во-вторых, нуль на выходе можно получить только в том случае, если «собрать» на всех входах единички. В данном случае уместно было бы назвать рассматриваемый логический элемент 2И-НЕ. Двойка говорит о том, что этот элемент двухвхододый. Практически во всех сериях микросхем существуют также 3-х, 4-х и восьмивходовые элементы. При этом каждый из них имеет только один выход. Однако, базовым элементом во многих сериях цифровых микросхем считается элемент 2И-НЕ.

При различных вариантах соединения входов можно получить еще одно чудесное свойство. Например, соединив между собой три входа восьмивходового элемента 8И-НЕ получим элемент 6И-НЕ. А если соединить вместе все 8 входов, получится просто инвертор, о чем было сказано чуть выше.

А если соединить вместе все 8 входов, получится просто инвертор, о чем было сказано чуть выше.

На этом знакомство с логическими элементами закончим. В следующей части статьи будут рассмотрены простейшие опыты с микросхемами, внутреннее устройство микросхем, простые устройства, например генераторы импульсов.

По материалам electrik.info

Построение логических схем в заданном базисе (Рекомендации по выполнению лабораторной работы № 1), страница 3

Информатика и выч. техника \ Компьютерная электроника

В следующей таблице приведены логические элементы со

стандартным выходом, выпускаемые в сериях ИМС ТТЛ и КМОП. Поскольку в

современных устройствах из всех серий ТТЛ чаще всего применяются микросхемы

серии 74ALS, в данной работе они также используются

везде, где это возможно. Тем не менее, применены и некоторые ИМС из других

серий, поскольку они не были выпущены в серии 74ALS

(например, 7425). Случай с элементами И‑ИЛИ‑НЕ в различных сериях вообще

заслуживает отдельного разговора.

Логические элементы | ИМС серий ТТЛ | ИМС серий КМОП | ||

Серия 4000 | Серия 74HC | |||

И | 2И x4 | 74ALS08 | 4081B | 74HC08 |

3И x3 | 74ALS11 | 4073B | 74HC11 | |

4И x2 | 74ALS21 | 4082B | 74HC21 | |

ИЛИ | 2ИЛИ x4 | 74ALS32 | 4071B | 74HC32 |

3ИЛИ x3 | — | 74HC4075 | ||

4ИЛИ x2 | — | 4072B | — | |

НЕ | НЕ x6 | 74ALS04 | 4069UB | 74HC04 |

И-НЕ | 2И-НЕ x4 | 74ALS00 | 4011B | 74HC00 |

3И-НЕ x3 | 74ALS10 | 4023B | 74HC10 | |

4И-НЕ x2 | 74ALS20 | 4012B | 74HC20 | |

8И-НЕ x1 | 74ALS30 | 4068B | 74HC30 | |

13И-НЕ x1 | 74ALS133 | — | 74HC133 | |

ИЛИ-НЕ | 2ИЛИ-НЕ x4 | 74ALS02 | 4001B | 74HC02 |

3ИЛИ-НЕ x3 | 74ALS27 | 4025B | 74HC27 | |

4ИЛИ-НЕ x2 | 7425 *1 | 4002B | 74HC4002 | |

5ИЛИ-НЕ x2 | 74LS260 | — | — | |

8ИЛИ-НЕ x1 | — | 4078B | 74HC4078 | |

Искл. | Искл. ИЛИ x4 | 4030B | 74HC86 | |

Инверсия искл. ИЛИ x4 | 74ALS810 | 4077B | — | |

*1 Микросхема 7425 содержит два логических элемента 4ИЛИ-НЕ с входом разрешения. Пользуясь обозначениями входов, принятыми в Micro-Cap, функцию, которую реализует такой элемент, можно записать так: .

Большинство приведённых микросхем имеют аналоги в сериях производства стран СНГ (соответственно, 74ALS — КР1533, 4000B — КР1561, 74HC — 1564 и т.д.) Поскольку в библиотеке Micro-Cap не предусмотрены ИМС этих серий, в таблице они также не показаны.

На следующем рисунке показаны логические элементы И‑ИЛИ‑НЕ и

И-ИЛИ, выпускаемые в различных сериях микросхем ТТЛ и КМОП. К сожалению, среди

некоторых микросхем И‑ИЛИ‑НЕ в сериях ТТЛ существуют отклонения от общих правил

наименования.

7451, 74H51, 74S51 — два элемента 2-2И-ИЛИ-НЕ

74LS51, 74F51, 74HC51 — элемент 3-3И-ИЛИ-НЕ и элемент 2-2И-ИЛИ-НЕ

7454 — элемент 2-2-2-2И-ИЛИ-НЕ

74H54 — элемент 2-2-3-2И-ИЛИ-НЕ

74LS54 — элемент 2-3-3-2И-ИЛИ-НЕ

74LS55 — элемент 4-4И-ИЛИ-НЕ

74F64 — элемент 4-3-2-2И-ИЛИ-НЕ

4085B — два элемента (см. рис.)

4086B — элемент (см. рис.)

74HC58 — элемент 3-3И-ИЛИ и элемент 2-2И-ИЛИ

К сожалению, по условным обозначениям логических элементов И‑ИЛИ‑НЕ,

принятым в стандартной библиотеке программы Micro-Cap, нелегко догадаться, где какой вход. Поэтому в данной

работе и в дальнейшем мы будем использовать отредактированную библиотеку

элементов, в которой их условные обозначения приведены к доступному для

восприятия виду.

Скачать файл

Выбери свой ВУЗ

- АлтГТУ 419

- АлтГУ 113

- АмПГУ 296

- АГТУ 267

- БИТТУ 794

- БГТУ «Военмех» 1191

- БГМУ 172

- БГТУ 603

- БГУ 155

- БГУИР 391

- БелГУТ 4908

- БГЭУ 963

- БТЭУ ПК 689

- БрГУ 179

- ВНТУ 120

- ВГУЭС 426

- ВлГУ 645

- ВМедА 611

- ВолгГТУ 235

- ВНУ им. Даля 166

- ВЗФЭИ 245

- ВятГСХА 101

- ВятГГУ 139

- ВятГУ 559

- ГГДСК 171

- ГомГМК 501

- ГГМУ 1966

Сухого 4467

Сухого 4467- ГГУ им. Скорины 1590

- ГМА им. Макарова 299

- ДГПУ 159

- ДальГАУ 279

- ДВГГУ 134

- ДВГМУ 408

- ДВГТУ 936

- ДВГУПС 305

- ДВФУ 949

- ДонГТУ 498

- ДИТМ МНТУ 109

- ИвГМА 488

- ИГХТУ 131

- ИжГТУ 145

- КемГППК 171

- КемГУ 508

- КГМТУ 270

- КировАТ 147

- КГКСЭП 407

- КГТА им.

Дегтярева 174

Дегтярева 174 - КнАГТУ 2910

- КрасГАУ 345

- КрасГМУ 629

- КГПУ им. Астафьева 133

- КГТУ (СФУ) 567

- КГТЭИ (СФУ) 112

- КПК №2 177

- КубГТУ 138

- КубГУ 109

- КузГПА 182

- КузГТУ 789

- МГТУ им. Носова 369

- МГЭУ им. Сахарова 232

- МГЭК 249

- МГПУ 165

- МАИ 144

- МАДИ 151

- МГИУ 1179

- МГСУ 331

- МГУ 273

- МГУКИ 101

- МГУПИ 225

- МГУПС (МИИТ) 637

- МГУТУ 122

- МТУСИ 179

- ХАИ 656

- ТПУ 455

- НИУ МЭИ 640

- НМСУ «Горный» 1701

- ХПИ 1534

- НТУУ «КПИ» 213

- НУК им.

Макарова 543

Макарова 543 - НВ 1001

- НГАВТ 362

- НГАУ 411

- НГАСУ 817

- НГМУ 665

- НГПУ 214

- НГТУ 4610

- НГУ 1993

- НГУЭУ 499

- НИИ 201

- ОмГТУ 302

- ОмГУПС 230

- СПбПК №4 115

- ПГУПС 2489

- ПГПУ им. Короленко 296

- ПНТУ им. Кондратюка 120

- РАНХиГС 190

- РОАТ МИИТ 608

- РТА 245

- РГГМУ 117

- РГПУ им.

Герцена 123

Герцена 123 - РГППУ 142

- РГСУ 162

- «МАТИ» — РГТУ 121

- РГУНиГ 260

- РЭУ им. Плеханова 123

- РГАТУ им. Соловьёва 219

- РязГМУ 125

- РГРТУ 666

- СамГТУ 131

- СПбГАСУ 315

- ИНЖЭКОН 328

- СПбГИПСР 136

- СПбГЛТУ им. Кирова 227

- СПбГМТУ 143

- СПбГПМУ 146

- СПбГПУ 1599

- СПбГТИ (ТУ) 293

- СПбГТУРП 236

- СПбГУ 578

- ГУАП 524

- СПбГУНиПТ 291

- СПбГУПТД 438

- СПбГУСЭ 226

- СПбГУТ 194

- СПГУТД 151

- СПбГУЭФ 145

- СПбГЭТУ «ЛЭТИ» 379

- ПИМаш 247

- НИУ ИТМО 531

- СГТУ им.

Гагарина 114

Гагарина 114 - СахГУ 278

- СЗТУ 484

- СибАГС 249

- СибГАУ 462

- СибГИУ 1654

- СибГТУ 946

- СГУПС 1473

- СибГУТИ 2083

- СибУПК 377

- СФУ 2424

- СНАУ 567

- СумГУ 768

- ТРТУ 149

- ТОГУ 551

- ТГЭУ 325

- ТГУ (Томск) 276

- ТГПУ 181

- ТулГУ 553

- УкрГАЖТ 234

- УлГТУ 536

- УИПКПРО 123

- УрГПУ 195

- УГТУ-УПИ 758

- УГНТУ 570

- УГТУ 134

- ХГАЭП 138

- ХГАФК 110

- ХНАГХ 407

- ХНУВД 512

- ХНУ им.

Каразина 305

Каразина 305 - ХНУРЭ 325

- ХНЭУ 495

- ЦПУ 157

- ЧитГУ 220

- ЮУрГУ 309

Сервисный центр GE HealthCare

text.skipToContenttext.skipToNavigation

- Магазин

- Части

- Доставка анестезии

- Общие детали

- Интервенционные системы визуального контроля

- Магнитно-резонансная томография

- Маммография

- Уход за матерями и младенцами

- Молекулярная визуализация и ядерная медицина

- Мобильные C-дуги OEC

- ПЭТ-радиофармация

- ПЭТ/КТ

- Мониторинг пациента

- Респираторная помощь

- Рабочие станции (AW)

- УЗИ

-  Управление ультразвуковыми датчиками

- Трубки

- Рентген

- Компьютерная томография (КТ)

- Диагностическая ЭКГ

- Зачем покупать запасные части

- Принадлежности для обработки изображений

- Здоровье костей

- Компьютерная томография (КТ)

- Интервенционная

- Магнитно-резонансная томография

- Маммография

- Мультимодальность

- Ядерная медицина

- Мобильные C-дуги OEC

- ПЭТ/КТ

- Хирургическая визуализация/OEC

- УЗИ

- Рентген

- Клинические принадлежности

- Доставка анестезии

- Диагностическая ЭКГ

- Уход за матерью и ребенком

- Мониторинг пациента

- Респираторная помощь

- Рекомендуемые пакеты

- Образование

- Биомедицинская клиническая инженерия

- Клиническая подготовка

- Цифровой эксперт

- ИТ в здравоохранении

- Уход за матерями и младенцами

- Обучение пациентов и безопасности

- Технолог Образование

- Путешествия и проживание

- Электронный мониторинг сердечного ритма плода

- Техническое обучение

- Анестезия и респираторная

- Компьютерная томография

- Диагностическая кардиология

- Запись гемодинамики

- Лунар – здоровье костей

- Магнитный резонанс

- Маммография

- Уход за матерью и ребенком

- Молекулярная визуализация – ПЭТ

- Сетевая инфраструктура и протоколы

- Ядерная медицина

- Системы мониторинга пациентов

- ПЭТ Радиоаптека

- Рентгенография и рентгеноскопия

- Хирургия

- УЗИ – расширенный

- УЗИ – Proficient

- Сосудистый

- Виртуальное обучение

- Обучение на месте

- Программное обеспечение

- Приложения

- Обновления и пакеты обновлений

- Клиренс

- Рекомендуемые наборы

- Альфа-источник

- Сименс

- Другое

- Тошиба

- Филипс

- GE Healthcare

- Цепь пациента (EUA)

- Части

- Подключить

- Ремонт

- Служебные ключи и документы

- Поиск ремонтных центров Часто задаваемые вопросы по устранению неполадок оборудования

- Поддержка вентилятора

- Узнать

Регистрация

Войти

- Вопросы для рассмотрения

2+2=4? Microchip анонсирует PolarFire 2; Вы делаете математику — EEJournal

Компания Microchip анонсировала свое семейство SoC FPGA среднего класса PolarFire 2 на саммите RISC-V в прошлом месяце в двух презентациях, включая основной доклад Брюса Вейера, корпоративного вице-президента компании по FPGA. Хотя компания предоставила очень мало подробностей о продукте, она сделала много намеков. На самом деле так много намеков, что я могу дать вам информацию, которую я собрал на основе этих намеков, рассказать вам, что я думаю, и позволить вам сделать свои собственные выводы. Я поставлю вам «двойки» и позволю вам проверить мою математику, но тогда вам нужно будет самостоятельно сложить «двойки», чтобы получить «четверки». Мы узнаем, правы ли мы, примерно через шесть месяцев на конференции Mi-V в этом году для партнеров Microchip по экосистеме RISC-V для ее ПЛИС PolarFire SoC.

Хотя компания предоставила очень мало подробностей о продукте, она сделала много намеков. На самом деле так много намеков, что я могу дать вам информацию, которую я собрал на основе этих намеков, рассказать вам, что я думаю, и позволить вам сделать свои собственные выводы. Я поставлю вам «двойки» и позволю вам проверить мою математику, но тогда вам нужно будет самостоятельно сложить «двойки», чтобы получить «четверки». Мы узнаем, правы ли мы, примерно через шесть месяцев на конференции Mi-V в этом году для партнеров Microchip по экосистеме RISC-V для ее ПЛИС PolarFire SoC.

Первоначальное семейство ПЛИС PolarFire SoC впервые появилось в 2017 году, а затем в 2019 году Microchip анонсировала версию семейства SoC с усиленным микропроцессорным ядром RISC-V. (См. «Microchip PolarFire использует RISC (-V)») семейство FPGA среднего уровня с логическими элементами (LE) от 25 000 до 460 000 и приемопередатчиками SerDes со скоростью передачи данных 12,7 Гбит/с, что ставит его прямо в категорию FPGA среднего уровня.

SoC членов исходного семейства PolarFire включают в себя многоядерную микропроцессорную подсистему, состоящую из одного процессорного ядра SiFive E51 RISC-V и четырех процессорных ядер SiFive U51 RISC-V, подключенных через когерентный коммутатор шины к встроенному чипу, 2 -Мбайт кэш-памяти L2. Структура программируемой логики PolarFire SoC подключается к ядрам процессора через несколько 64-битных интерфейсных портов AXI4 через коммутатор AMBA, подключенный к коммутатору согласованной шины. Пока мы не знаем, как выглядит микропроцессорная подсистема SoC PolarFire 2, но на рисунке 1 показана блок-схема микропроцессорного комплекса оригинальной SoC PolarFire. Микропроцессорная подсистема SoC PolarFire 2, несомненно, будет больше и лучше.

Рисунок 1. Члены SoC исходного семейства PolarFire включают многоядерную микропроцессорную подсистему, состоящую из одного процессорного ядра SiFive E51 RISC-V и четырех процессорных ядер SiFive U51 RISC-V. Изображение предоставлено: Microchip

Вариант SONOS процесса производства полупроводников, используемый для изготовления FPGA и SoC PolarFire, обеспечивает возможность энергонезависимой памяти, которую исходная матрица FPGA PolarFire использует для памяти конфигурации. Поскольку в SoC PolarFire используются энергонезависимые ячейки памяти SONOS SRAM для памяти конфигурации, как и в FPGA и SoC среднего уровня от AMD/Xilinx и Intel, они невосприимчивы к радиационно-индуцированным SEU (одиночным сбоям), что делает их наиболее предпочтительными. FPGA для использования в космических кораблях. В настоящее время SoC Polarfire летают по всей Солнечной системе. По крайней мере, одна система на кристалле PolarFire облетела Луну во время недавней космической миссии НАСА «Орион-1».

Поскольку в SoC PolarFire используются энергонезависимые ячейки памяти SONOS SRAM для памяти конфигурации, как и в FPGA и SoC среднего уровня от AMD/Xilinx и Intel, они невосприимчивы к радиационно-индуцированным SEU (одиночным сбоям), что делает их наиболее предпочтительными. FPGA для использования в космических кораблях. В настоящее время SoC Polarfire летают по всей Солнечной системе. По крайней мере, одна система на кристалле PolarFire облетела Луну во время недавней космической миссии НАСА «Орион-1».

Мы еще не знаем, какой технологический процесс Microchip будет использовать для производства FPGA и SoC PolarFire 2, но в предварительном обзоре семейства PolarFire 2 Microchip заявила, что это удвоит энергоэффективность матрицы FPGA, а также удвоит энергопотребление. производительность ткани. Ткань PolarFire 2 FPGA снова будет защищена от SEU, как и исходное семейство PolarFire, и будет иметь функции защиты от несанкционированного доступа и кибербезопасности «военного уровня». Компания также заявила, что утроит производительность вычислительных элементов SoC PolarFire 2 в тесте CoreMark по сравнению с производительностью исходного семейства PolarFire и увеличит максимальную производительность TOPS в колоссальные 15 раз. Он пообещал, что более подробная информация будет представлена на саммите компании Mi-V в конце этого года. Mi-V — это экосистема RISC-V от Microchip. Вот и все, что Microchip сказал о новом семействе PolarFire 2.

Компания также заявила, что утроит производительность вычислительных элементов SoC PolarFire 2 в тесте CoreMark по сравнению с производительностью исходного семейства PolarFire и увеличит максимальную производительность TOPS в колоссальные 15 раз. Он пообещал, что более подробная информация будет представлена на саммите компании Mi-V в конце этого года. Mi-V — это экосистема RISC-V от Microchip. Вот и все, что Microchip сказал о новом семействе PolarFire 2.

Новая технология обработки

Хотя Microchip не предоставил много подробностей о семействе Polarfire 2, он дал много прямых и косвенных подсказок. Как я уже говорил в начале этой статьи, я не могу гарантировать вам, что моя арифметика верна, поэтому я предлагаю вам сложить эти подсказки самостоятельно.

Начнем с техпроцесса. Небольшое гугление привело меня к техническому документу Microchip под названием «Семейство энергонезависимых FPGA PolarFire обеспечивает новаторскую ценность: оптимизация затрат, минимальное энергопотребление, устойчивость к SEU и высокий уровень безопасности», в котором описывается, как UMC производит оригинальные устройства PolarFire для Microchip с использованием планарный 28-нм техпроцесс SONOS (кремний-оксид-нитрид-оксид-кремний). SONOS — это технологический процесс, который добавляет в микросхему энергонезависимую память путем вставки тонкого слоя из нитрида кремния, улавливающего заряд, в затвор полевого транзистора. Слой, улавливающий заряд, служит памятью с двумя состояниями: отрицательно заряженным и положительно заряженным (истощенный электронами, производящий дырки). Электроны могут перемещаться в этот слой и из него с помощью явления, называемого туннелированием Фаулера-Нордгейма. Полупроводниковые процессы SONOS существуют с конца 19 века.70-е годы.

SONOS — это технологический процесс, который добавляет в микросхему энергонезависимую память путем вставки тонкого слоя из нитрида кремния, улавливающего заряд, в затвор полевого транзистора. Слой, улавливающий заряд, служит памятью с двумя состояниями: отрицательно заряженным и положительно заряженным (истощенный электронами, производящий дырки). Электроны могут перемещаться в этот слой и из него с помощью явления, называемого туннелированием Фаулера-Нордгейма. Полупроводниковые процессы SONOS существуют с конца 19 века.70-е годы.

Удвоение эффективности энергопотребления и производительности матриц FPGA устройств PolarFire 2 означает, что Microchip потребуется использовать более совершенный технологический узел. Любой узел, более продвинутый, чем 28 нм, скорее всего, будет использовать FinFET вместо планарных FET. UMC, нынешний кремниевый литейный завод Microchip FPGA, использует 14-нм техпроцесс FinFET, который обещает на 50% меньше энергопотребления, чем планарный 28-нм техпроцесс. Тем не менее, на веб-сайте UMC относительно мало информации об этом 14-нм техпроцессе, поэтому невозможно сказать, имеет ли этот технологический процесс возможность энергонезависимой памяти, необходимую для производства чипов PolarFire 2.

Тем не менее, на веб-сайте UMC относительно мало информации об этом 14-нм техпроцессе, поэтому невозможно сказать, имеет ли этот технологический процесс возможность энергонезависимой памяти, необходимую для производства чипов PolarFire 2.

Еще немного Google сказал мне, что мы знали, что можно добавить слой улавливания заряда к FinFET (в отличие от планарных FET) с использованием шагов процесса SONOS с 2005 года, благодаря нескольким авторам в TSMC, которые опубликовали документ на эта тема была представлена на Международной встрече IEEE по электронным устройствам, состоявшейся в том же году в Вашингтоне, округ Колумбия. Однако эти улики ничего не доказывают. Возможно, Microchip даже не планирует использовать UMC для производства чипов PolarFire 2, поэтому вам придется сложить два и два, чтобы решить, какой технологический процесс Microchip будет использовать для производства устройств PolarFire 2. Мы даже не знаем, будет ли Microchip использовать энергонезависимые SONOS FinFET для памяти конфигурации, но память конфигурации SONOS оригинального семейства PolarFire оказалась успешной, так почему бы и нет?

Я думаю, что более вероятно, что компания будет придерживаться энергонезависимых ячеек памяти SONOS, а не чего-то более экзотического, такого как резистивная RAM или магнитная RAM, потому что NASA JPL (Лаборатория реактивного движения НАСА) объявила в августе прошлого года, что она решила сотрудничать с Microchip в тесно связанном проекте HPSC (High Performance Spaceflight Computing). У Microchip уже есть множество FPGA, SoC и других готовых к запуску в космос компонентов, летающих в космосе, поэтому неудивительно, что NASA JPL выбрало Microchip для разработки и производства HPSC, что является попыткой NASA JPL принять одну стандартизированную многоядерную вычислительную платформу. для всех будущих космических проектов и повысить производительность существующих космических вычислений как минимум в 100 раз. JPL хочет погрузиться в глобальную экосистему для своего процессора HPSC и хочет привлечь большое количество программистов, знакомых с конкретной архитектурой процессора.

У Microchip уже есть множество FPGA, SoC и других готовых к запуску в космос компонентов, летающих в космосе, поэтому неудивительно, что NASA JPL выбрало Microchip для разработки и производства HPSC, что является попыткой NASA JPL принять одну стандартизированную многоядерную вычислительную платформу. для всех будущих космических проектов и повысить производительность существующих космических вычислений как минимум в 100 раз. JPL хочет погрузиться в глобальную экосистему для своего процессора HPSC и хочет привлечь большое количество программистов, знакомых с конкретной архитектурой процессора.

Согласно основному докладу Вейера, этот выбор, по крайней мере, косвенно повлияет на то, как может выглядеть микропроцессорная подсистема PolarFire 2, поскольку он сказал, что FPGA SoC PolarFire 2 будут иметь комплекс ядра, совместимый с HPSC, так что версии SoC PolarFire 2 FPGA семья также может быть использована для космических приложений. Поскольку это проект НАСА и поскольку НАСА любит летать на оборудовании, которое уже летало, экзотические энергонезависимые запоминающие устройства, такие как MRAM и RRAM, с меньшей вероятностью появятся на новых чипах, направляющихся в космос. Во всяком случае, не в ближайшем будущем.

Во всяком случае, не в ближайшем будущем.

Хотя Microchip не предоставила прямой информации о микропроцессорной подсистеме в ПЛИС PolarFire 2 SoC, компания спрятала подсказки в разных местах. Согласно пресс-релизу SiFive от 6 сентября 2022 года, чип HPSC будет использовать восемь 64-битных процессорных ядер SiFive X280 RISC-V с 512-битными векторными расширениями и четыре дополнительных ядра RISC-V от SiFive. Процессорные ядра SiFive X280 также включают в себя то, что SiFive называет своими «расширениями интеллекта», которые представляют собой настраиваемые инструкции, разработанные SiFive для ускорения операций AI/ML.

Вейер прямо не заявил, что микропроцессорная подсистема PolarFire 2 SoC FPGA будет основана на восьми процессорных ядрах SiFive X280 плюс еще четыре ядра SiFive, которые будут названы позже, например, HPSC, но он приложил все усилия во время своего основного доклада для указать, что:

- Microchip работает с SiFive с 2015 года

- Компания предлагает три программных ядра RISC-V в своей библиотеке FPGA

- Существующие ПЛИС PolarFire SoC включают одно процессорное ядро SiFive E51 и четыре процессорных ядра SiFive U54

- Микропроцессорная подсистема, используемая в ПЛИС PolarFire 2 SoC, будет «совместима» с процессором HPSC ASIC .

Еще раз, вы можете сделать математику, но я думаю, что довольно ясно, где Microchip возьмет подсистему микропроцессора в PolarFire SoC FPGA. Он может иметь столько же экземпляров процессорных ядер SiFive, сколько и HPSC, а может и не иметь. Мы пока не знаем.

Безопасность военного уровня

Наконец, Вейер из Microchip упомянул, что устройства PolarFire 2 будут включать «защиту военного уровня». В наши дни такого рода утверждения настоятельно предполагают включение постквантовой криптографии, особенно для новых устройств, предназначенных для использования в течение 30 лет и рассчитанных на несколько десятилетий в этой области. Я полностью ожидаю, что к тому времени такие компании, как IBM, будут иметь работающие квантовые компьютеры для коммерческого использования. В настоящее время постквантовая криптография находится в постоянном движении. NIST (Национальный институт стандартов и технологий США) находится в середине программы по разработке, квалификации и принятию новых стандартов безопасности, основанных на постквантовой криптографии. (Для получения дополнительной информации см. «Надвигающийся криптокризис связан с квантовыми вычислениями».)

(Для получения дополнительной информации см. «Надвигающийся криптокризис связан с квантовыми вычислениями».)

Хотя Microchip не предоставила никаких дополнительных сведений о том, что подразумевается под безопасностью военного уровня, другой разговор, который у меня состоялся на саммите RISC-V с вице-президентом PQShield по инженерным вопросам Грэмом Хики, предполагает одно направление, в котором может двигаться Microchip. PQShield — стартап-компания, созданная группой специалистов по криптографии из Оксфордского университета в Великобритании. 1 июня 2022 года PQShield объявила, что Microchip лицензировала свои IP-ядра постквантовой криптографии «для использования в своем портфолио продуктов в ближайшие годы». По словам Хики, программная библиотека постквантового шифрования PQShield поддерживает всех кандидатов NIST для квантово-безопасных схем шифрования на основе решетки, включая Kyber, Dilithium и Falcon. Аппаратная IP-реализация PQShield в настоящее время поддерживает Kyber и Dilithium и включает защиту от атак по сторонним каналам.

Я особенно спросил Хикки о квантово-безопасных криптографических схемах на основе решетки, потому что другой кандидат NIST под названием SIKE (Supersingular Isogeny Key Encapsulation, произносится как «ключ вздоха») был недавно взломан двумя людьми с портативным компьютером. Томас Декру и Воутер Кастрик из Католического университета Лёвена в Бельгии взломали схему за один или два дня на основе теоремы, опубликованной математиком Эрнстом Кани в 1997 году. Сотрите SIKE, по крайней мере, на данный момент.

Чтобы лучше понять текущее состояние постквантовой криптографии, я связался с Сильвио Драгоне, сотрудником исследовательского центра IBM в Цюрихе. Драгон опубликовал блог под названием «Как мы обеспечили квантовую защиту IBM z16», который появился в октябре прошлого года на веб-сайте IBM. Мейнфреймы IBM zSystem уже давно включают карты криптографических сопроцессоров, называемые аппаратными модулями безопасности (HSM), а HSM мейнфрейма IBM z16 содержит аппаратное обеспечение, которое реализует кандидаты постквантовых криптографических алгоритмов CRYSTALS Dilithium и Kyber.

Драгоне объяснил, что IBM решила ускорить HSM мейнфрейма z16 с помощью аппаратных реализаций алгоритмов Dilithium и Kyber на основе исследований постквантовой криптографии, проведенных IBM в Цюрихе. Это исследование было основано на хорошо изученной математической проблеме и показало, что эти алгоритмы обеспечивают наилучшую производительность в среде мэйнфреймов. Он сказал, что красота постквантовой конкуренции NIST заключается в том, что она позволяет мировому сообществу криптографических экспертов анализировать эти алгоритмы, чтобы выявить любые недостатки. Именно это произошло с SIKE.

Компания Microchip не объявила, что означает «безопасность военного уровня» в контексте своих устройств PolarFire 2, но я предоставил подсказки, которые собрал на саммите RISC-V. Еще раз, я предлагаю, чтобы вы могли сделать математику.

Итоговый рейтинг FPGA среднего уровня

На саммите RISC-V компания Microchip заявила, что оригинальные FPGA PolarFire «вдвое эффективнее по энергопотреблению», чем конкурирующие FPGA среднего уровня, и что устройства PolarFire 2 еще удвоят эту эффективность. снова. Вам нужно будет оценить это утверждение самостоятельно, когда инструменты и чипы станут доступны. Мой опыт говорит о том, что энергопотребление сильно зависит от конструкции, реализуемой в FPGA. Тем не менее, Microchip еще предстоит описать устройства PolarFire 2, не говоря уже о том, чтобы их изготовить, поэтому PolarFire 2 должен войти в эфирную категорию будущих FPGA вместе с несколькими более новыми FPGA среднего уровня, которые также еще не созданы. В эту категорию входят недавно анонсированные Intel Agilex серии D и Sundance Mesa FPGA и SoC, которые планируется производить с использованием процесса Intel 7. Это процесс, ранее известный как 10-нм Enhanced SuperFin, 10-нм SuperFin++ или что-то в этом роде; он менялся несколько раз. (См. «Intel представляет два монолитных семейства Agilex FPGA и SoC» и «Intel приветствует вас в эпоху Angstrom».)

снова. Вам нужно будет оценить это утверждение самостоятельно, когда инструменты и чипы станут доступны. Мой опыт говорит о том, что энергопотребление сильно зависит от конструкции, реализуемой в FPGA. Тем не менее, Microchip еще предстоит описать устройства PolarFire 2, не говоря уже о том, чтобы их изготовить, поэтому PolarFire 2 должен войти в эфирную категорию будущих FPGA вместе с несколькими более новыми FPGA среднего уровня, которые также еще не созданы. В эту категорию входят недавно анонсированные Intel Agilex серии D и Sundance Mesa FPGA и SoC, которые планируется производить с использованием процесса Intel 7. Это процесс, ранее известный как 10-нм Enhanced SuperFin, 10-нм SuperFin++ или что-то в этом роде; он менялся несколько раз. (См. «Intel представляет два монолитных семейства Agilex FPGA и SoC» и «Intel приветствует вас в эпоху Angstrom».)

В качестве еще одного дополнения к будущему FPGA-дерби среднего класса компания Lattice Semiconductor недавно представила свою платформу Avant FPGA среднего класса, основанную на 16-нм техпроцессе TSMC FinFET, и первое семейство, основанное на платформе Avant, под названием Avant-E.

ИЛИ

ИЛИ Сухого 4467

Сухого 4467 Дегтярева 174

Дегтярева 174 Макарова 543

Макарова 543 Герцена 123

Герцена 123 Гагарина 114

Гагарина 114 Каразина 305

Каразина 305