8. Деление частоты | Техническая библиотека lib.qrz.ru

Деление частоты

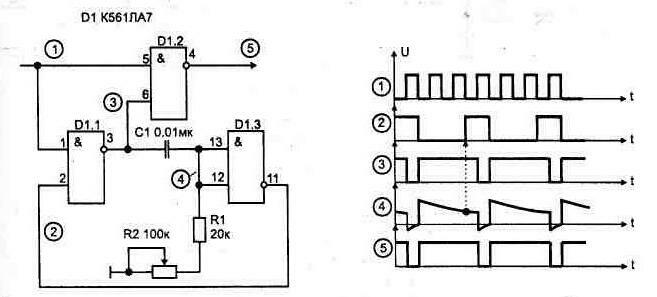

Наиболее часто для этого используют счетчики, хотя можно разделить частоту с помощью ждущего мультивибратора, ограничив число проходящих на выход импульсов. Пример такой схемы показан на рис. 1.60. Как только импульс входной частоты поступает на выход 5, ждущий мультивибратор D1.1, D1.3 запирает элемент D1.2 на время, определяемое резистором R1. Когда ждущий мультивибратор возвращается в исходное состояние, на выход поступает следующий импульс и цикл возобновляется. Схему можно усовершенствовать, заменив потенциометр полевым транзистором, что позволит управлять коэффициентом деления с помощью напряжения.

Рис. 1.60 Делитель частоты с использованием ждущего мультивибратора

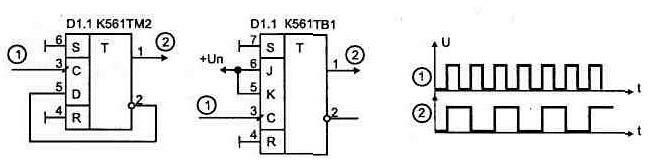

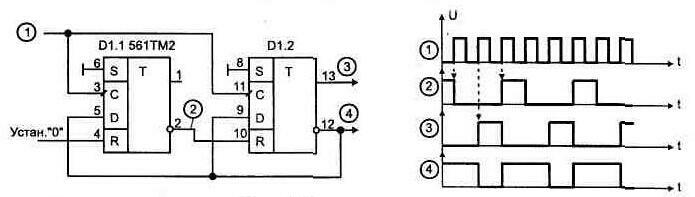

Делитель на 2 можно собрать из простейших ЛЭ, рис. 1.61. Схемы делителей без использования RC-цепей имеют лучшую помехоустойчивость и болееширокий диапазон входной частоты сигнала. Основным элементом всех счетчиков является триггер с так называемым счетным входом, рис. 1.62. Таблица 1.4

Таблица 1.4

Сигналы на входах | Состояние выхода | ||||

С | D | S | R | Q | NOT Q |

х | х | 0 | 1 | 0 | 1 |

х | х | 1 | 1 | 0 | |

_/ | 0 | 0 | 0 | 0 | 1 |

_/ | 1 | 0 | 0 | 1 | 0 |

\_ | х | 0 | 0 | Q | NOT Q |

Рис. 1.62. Делитель частоты на 2

Рис. 1.63. Делитель на 3

Рис. 1.64. а) Делитель на 10 на RS-триггерах; б) делитель на 10 на JK-триггерах

поясняет логику работы триггера 561ТМ2 в зависимости от управляющих сигналов (х — безразлично состояние на данном входе; состояние, когда на входах S и R микросхемы одновременно действует лог. «1», является запрещенным).

Комбинационное включение триггеров позволяет получать счетчик с нужным коэффициентом деления входной частоты.

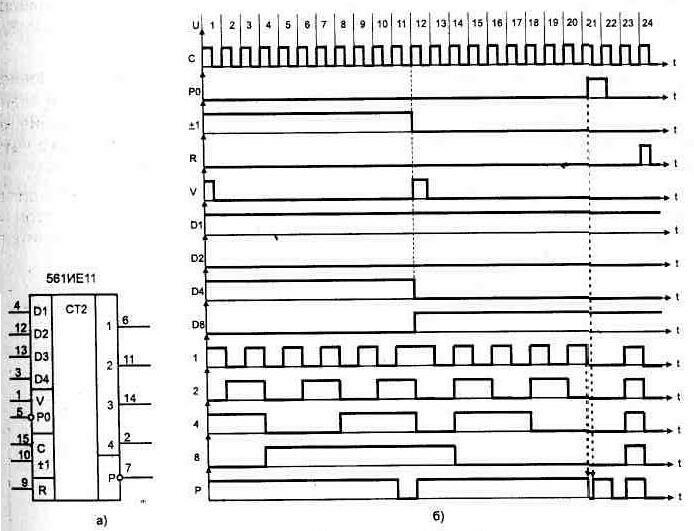

Промышленность выпускает универсальные счетчики, которые в зависимости от управляющих сигналов могут переключаться по переднему или заднему фронту входного сигнала, а также менять направление счета (сложение или вычитание). В качестве примера приведена диаграмма работы двоичного четырехразрядного реверсивного счетчика на микросхеме 561ИЕ11, рис. 1.66.

Таблица истинности (табл. 1.5) поясняет назначение управляющих сигналов и логику управления микросхемой (1 — лог. «1»; 0 — лог. «0»; х — состояние безразлично, т. е. 0 или 1). Счетчик предусматривает возможность загрузить по входам D1, D2, D4, D8 параллельный код.

Рис. 1 65. Схема делителя на 60

Таблица 1.5

Вход | Сложение, | Разрешен. | Установка | Действие |

1 | х | 0 | 0 | нет счета |

0 | 1 | 0 | 0 | работа на сложение |

0 | 0 | 0 | 0 | работа на вычитание |

х | х | 1 | 0 | установка по парал. вх. |

х | х | х | 1 | установка нуля |

Для получения нужного коэффициента деления можно использовать микросхемы двоичных счетчиков, соединяя соответствующие выходы с помощью ЛЭ, рис. 1.67, или же применить счетчик с программируемым

Рис. 1. 66. а) Универсальный реверсивный счетчик,

б) диаграмма напряжении микросхемы

Pис 1.67. Делитель на 1000

Делитель частоты на микросхемах

Генераторы

В радиолюбительской практике часто бывают необходмы

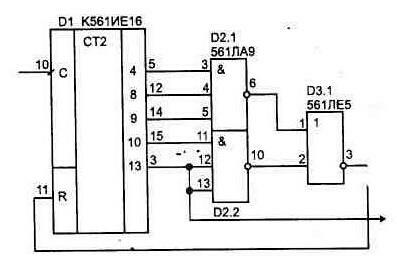

Я предлагаю делитель с программируемым коэффициентом деления (от 10 до 15000), выполненный на широко распространенных микросхемах К561ИЕ16 (К561ИЕ20), представляющих собой двоичные счетчики с коэффициентом деления 214 и 212 соответственно. При несколько необычном включении на их основе можно собрать делитель с изменяемым коэффициентом деления (К561ИЕ16 — от 200 до 15000, К561ИЕ20 — от 10 до 4000).

Рис.1 Делитель частоты с программируемым коэффициентом деления

Для примера на рисунке показан делитель с коэффициентом деления 10000, предназначенный для электронных часов на основе ИМС LM8560 и аналогичных, использующих в качестве образцовой частоту сети (50 Гц). Как видно из рисунка, микросхема будет считать импульсы генератора до тех пор, пока на ее выходах не установится код 10011100010000, что в десятичном счислении равно 10000.

Как только она «досчитает» до этого числа, все диоды VD1… VD5 закроются, и на входе R (вывод 11) DD2 сформируется короткий положительный импульс, который “обнулит” все триггеры счетчика. В итоге на выводах 8, 9 DD1.3 будут короткие положительные импульсы с частотой 500000:10000 = 50 (Гц). Элемент DD1.4 вместе с R3, VD6, С1 используется для расширения импульсов. При неустойчивой работе микросхемы часов на выходе DD1.4 следует включить конденсатор С2 емкостью порядка сотен пикофарад.

По этому же принципу, с помощью подключаемых диодов между выходами и входом сброса R микросхемы DD2, можно получить любой коэффициент деления. Например, если подключить диоды к выводам 6, 7, 13, то получится коэффициент деления 200. Однако для получения некоторых коэффициентов деления, например, 100, у К561ИЕ16 не хватает «пропущенных» выходов 2 и 4. В этих случаях следует применять ИМС К561ИЕ20. Цоколевка этих двух микросхем одинаковая. Чтобы узнать, к каким выходам следует подключить диоды, нужно складывать коэффициенты деления на соответствующих выходах микросхемы DD2, пока не получится требуемый коэффициент деления. Какие цифры при этом пришлось сложить, к тем выходам и следует подключать диоды При увеличении выходной частоты в несколько раз следует во столько же раз уменьшить соотношение R3, С1.

А. Колдунов

Деление частоты Справочник по микросхемам ТТЛ и КМОП Любительская Радиоэлектроника

Деление частоты

Наиболее часто для этого используют счетчики, хотя можно разделить частоту с помощью ждущего мультивибратора, ограничив число проходящих на выход импульсов. Пример такой схемы показан на рис. 1.60. Как только импульс входной частоты поступает на выход 5, ждущий мультивибратор D1.1, D1.3 запирает элемент D1.2 на время, определяемое резистором R1. Когда ждущий мультивибратор возвращается в исходное состояние, на выход поступает следующий импульс и цикл возобновляется. Схему можно усовершенствовать, заменив потенциометр полевым транзистором, что позволит управлять коэффициентом деления с помощью напряжения.

Рис. 1.60 Делитель частоты с использованием ждущего мультивибратора

Делитель на 2 можно собрать из простейших ЛЭ, рис. 1.61. Схемы делителей без использования RC-цепей имеют лучшую помехоустойчивость и более широкий диапазон входной частоты сигнала. Основным элементом всех счетчиков является триггер с так называемым счетным входом, рис. 1.62. Таблица 1.4

Таблица 1.4

| Сигналы на входах | Состояние выхода | ||||

| С | D | S | R | Q | NOT Q |

| х | х | 0 | 1 | 0 | 1 |

| х | х | 1 | 0 | 1 | 0 |

| _/ | 0 | 0 | 0 | 0 | 1 |

| _/ | 1 | 0 | 0 | 1 | 0 |

| \_ | х | 0 | 0 | Q | NOT Q |

Рис. 1.62. Делитель частоты на 2

Рис. 1.63. Делитель на 3

поясняет логику работы триггера 561ТМ2 в зависимости от управляющих сигналов (х _ безразлично состояние на данном входе; состояние, когда на входах S и R микросхемы одновременно действует лог. «1», является запрещенным).

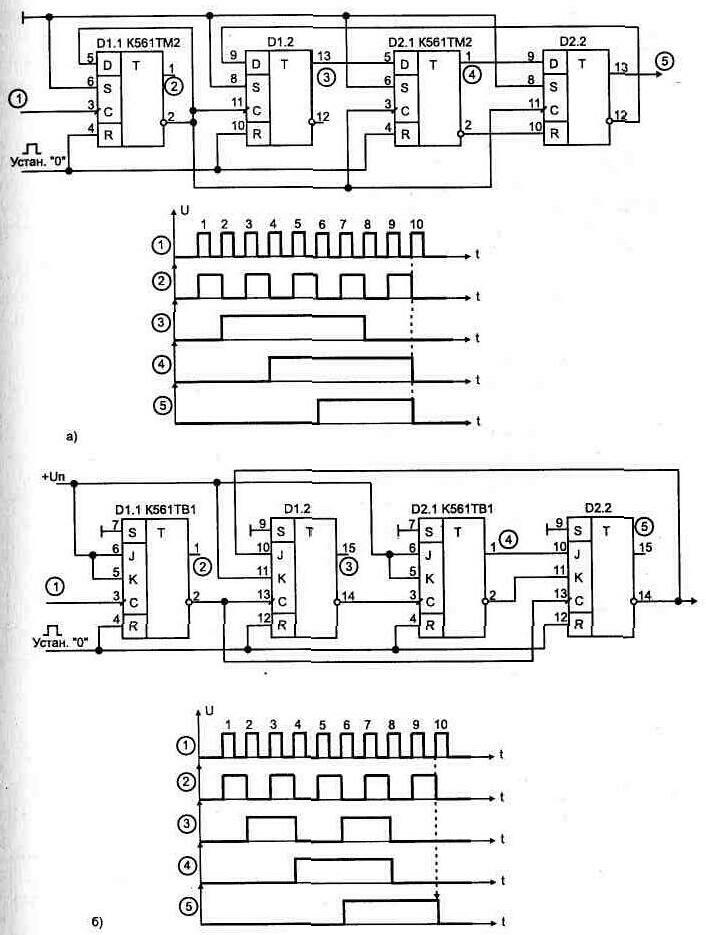

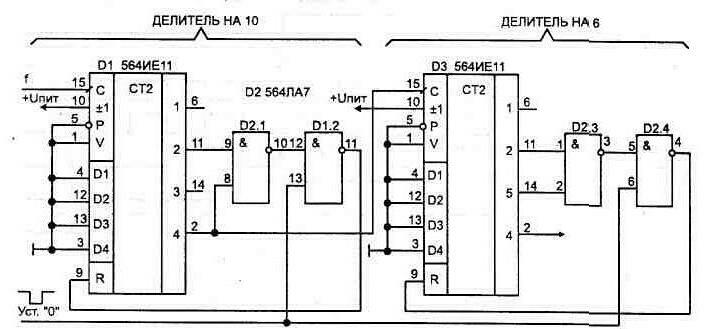

Комбинационное включение триггеров позволяет получать счетчик с нужным коэффициентом деления входной частоты. На рис. 1.62…1.65 приведены примеры включения элементов микросхем для получения деления на 2, 3, 6, 10 и 60.

Промышленность выпускает универсальные счетчики, которые в зависимости от управляющих сигналов могут переключаться по переднему или заднему фронту входного сигнала, а также менять направление счета (сложение или вычитание). В качестве примера приведена диаграмма работы двоичного четырехразрядного реверсивного счетчика на микросхеме 561ИЕ11, рис. 1.66.

Таблица истинности (табл. 1.5) поясняет назначение управляющих сигналов и логику управления микросхемой (1 _ лог. «1»; 0 _ лог. «0»; х _ состояние безразлично, т. е. 0 или 1). Счетчик предусматривает возможность загрузить по входам D1, D2, D4, D8 параллельный код.

Рис. 1 65. Схема делителя на 60

Таблица 1.5

| Вход переноса РО | Сложение, вычитание +-1 | Разрешен. установки V | Установка нуля R | Действие |

| 1 | х | 0 | 0 | нет счета |

| 0 | 1 | 0 | 0 | работа на сложение |

| 0 | 0 | 0 | 0 | работа на вычитание |

| х | х | 1 | 0 | установка по парал. вх. |

| х | х | х | 1 | установка нуля |

Для получения нужного коэффициента деления можно использовать микросхемы двоичных счетчиков, соединяя соответствующие выходы с помощью ЛЭ, рис. 1.67, или же применить счетчик с программируемым коэффициентом деления 564ИЕ15, см. рис. 1.26.

Рис. 1. 66. а) Универсальный реверсивный счетчик,

б) диаграмма напряжении микросхемы

Pис 1.67. Делитель на 1000

Микросхемы счётчиков КМОП-логики

Цифровые микросхемы ТТЛ-серий обеспечивают построение самых различных цифровых устройств, работающих на частотах до

80 МГц, однако их существенными недостатками являются большая потребляемая мощность и низкая помехозащищѐнность. Последнее имеет важное значение при разработке систем автоматизации технологических процессов. В большинстве случаев этим системам не нужно такое высокое быстродействие, а требуется высокая помехозащищѐнность. Немаловажным параметром, с точки зрения экономической эффективности, является низкая потребляемая мощность.

Именно по этой причине современные системы автоматизации выполняются в основном на микросхемах КМОП–технологий. Поэтому рассмотрим более подробно счѐтчики, выполненные именно по этой технологии.

Микросхема К176ИЕ1 шестиразрядный двоичный счетчик, работающий в коде 1-2-4-8-16-32. Микросхема имеет два входа: вход R установки триггеров счетчика в ноль и вход С вход для подачи счетных импульсов. Установка в ноль происходит при подаче логической единицы на вход R. Переключение триггеров микросхемы происходит по спаду импульсов, подаваемых на вход С. При построении многоразрядных счѐтчиков или делителей частоты входы С последующих микросхем следует подключать к выходам 32 предыдущих.

Рис. 14. Микросхема К176ИЕ1

Рис. 15. Микросхема К176ИЕ2

Микросхема К176ИЕ2 пятиразрядный счетчик, который может работать как двоичный в коде 1-2-4-8-16 при подаче логической единицы на управляющий вход А, или как декада с подключенным к выходу декады триггером при логическом нуле на входе А. Во втором случае код работы счетчика 1-2-4-8-10, общий коэффициент деления 20. Вход R служит для установки триггеров счетчика в 0 подачей на этот вход логической 1.

Первые четыре триггера счетчика могут быть установлены в единичное состояние подачей логической единицы на входы S1 … S8, причѐм эти входы являются приоритетными над входом R.

Микросхема К176ИЕ2 встречается двух разновидностей. Одна из разновидностей имеет входы СР и CN для подачи тактовых импульсов положительной и отрицательной полярности соответственно, включенные по ИЛИ. При подаче на вход СР импульсов положительной полярности на входе CN должна быть логическая единица, при подаче на вход CN импульсов отрицательной полярности на входе СР должен быть логический ноль. В обоих случаях счетчик переключается по спадам импульсов.

Другая разновидность имеет два равноправных входа для подачи тактовых импульсов (выводы 2 и 3), собранных по И. Счет происходит по спадам импульсов положительной полярности, подаваемых на любой из этих входов, причем на второй из этих входов должна быть подана логическая единица. Можно подавать импульсы и на объединенные выводы 2 и 3.

Если на вывод 3 микросхемы К176ИЕ2 подать логическую единицу, обе разновидности микросхем по входу СР (вывод 2) работают одинаково.

При логическом нуле на входе А порядок работы триггеров соответствует временной диаграмме, приведенной на рис. 16.

Рис. 16. Временная диаграмма работы микросхемы К176ИЕ2

В этом режиме на выходе Р, представляющем собой выход элемента «И-НЕ», входы которого подключены к выходам 1 и 8 счетчика, выделяются импульсы отрицательной полярности, фронты которых совпадают со спадом каждого девятого входного импульса, спады со спадом каждого десятого.

При соединении микросхем К176ИЕ2 в многоразрядный счетчик входы СР последующих микросхем следует подключать к выходам 8 или 16/10 непосредственно, на входы CN подавать логическую единицу.

Микросхемы К176ИЕЗ и К176ИЕ4 разработаны специально для использования в электронных часах с семисегментными индикаторами.

Рис. 17. Микросхемы К176ИЕЗ и К176ИЕ4

Микросхемы имеют три входа вход R, установка триггеров счетчика в ноль, которая происходит при подаче логической единицы на этот вход, вход С – входные импульсы, переключение триггеров происходит по спаду импульсов. Сигнал на входе S управляет полярностью выходных сигналов.

На выходах а, b, с, d, e, f, g выходные сигналы, обеспечивающие формирование цифр на семисегментном индикаторе, соответствующих состоянию счетчика. При подаче логического нуля на управляющий вход S логическая единица на выходах а, b, с, d, e, f, g соответствует включению соответствующего сегмента. Если же на вход S подать логическую единицу, включению сегментов будет соответствовать логический ноль на выходах а, b, с, d, e, f, g. Возможность переключения полярности выходных сигналов существенно расширяет область применения микросхем. Выход Р микросхемы выход переноса.

Микросхема К176ИЕЗ имеет коэффициент пересчета 6, т.е. спад имульса на выходе Р происходит при переходе счѐтчика из состояния 6 в состояние 0. Кроме того логическая единица на выходе

2 появляется при установке счетчика в состояние 2.

Микросхема К176ИЕ4 представляет собой декаду. Спад импульса на выходе Р формируется в момент перехода счетчика из состояния 9 в состояние 0, а логическая единица на выходе 4 появляется при установке счетчика в состояние 4.

Следует иметь в виду, что разводка выводов а, b, с, d, e, f, g в паспорте микросхемы и в некоторых справочниках приведена для нестандартного расположения сегментов индикаторов. На рис. 17 дана разводка выводов для стандартного расположения сегментов.

Микросхема К176ИЕ5 содержит кварцевый генератор с внешним резонатором на 32768 Гц и подключенным к нему девятиразрядным делителем частоты и шестиразрядный делитель частоты, структура микросхемы и типовая схема включения приведена на рисунке 18. К выводам Z и Z подключаются кварцевый резонатор, резисторы R1 и R2, конденсаторы С1 и С2. Выходной сигнал кварцевого генератора может быть проконтролирован на выходах K и K .

Сигнал с частотой 32768 Гц поступает на вход девятиразрядного

двоичного делителя частоты, с его выхода 9 сигнал с частотой 64 Гц может быть подан на вход 10 шестиразрядного делителя. На выходе 14 пятого разряда этого делителя формируется частота 2 Гц, на выходе 15 шестого разряда 1 Гц.

Рис. 18. Микросхема К176ИЕ5

Сигнал с частотой 64Гц может использоваться для подключения жидкокристаллических индикаторов к выходам микросхем К176ИЕЗ и К176ИЕ4. Вход R служит для сброса триггеров второго делителя и установки исходной фазы колебаний на выходах микросхемы. При подаче логической единицы на вход R на выходах 14 и

15 – логический ноль, после снятия логической единицы на этих выходах появляются импульсы с соответствующей частотой, спад первого импульса на выходе 15 происходит через 1с после снятия логической единицы.

При подаче логической единицы на вход S происходит установка всех триггеров второго делителя в состояние логической единицы, после снятия логической единицы с этого входа спад первого импульса на выходах 14 и 15 происходит практически сразу. Обычно вход S постоянно подключают к общему проводу.

Конденсаторы С1 и С2 служат для точной установки частоты кварцевого генератора. Емкость первого из них может находиться в пределах от единиц до ста пикофарад, емкость второго – 30 … 100 пФ. При увеличении емкости конденсаторов частота генерации уменьшается. Точную установку частоты удобнее производить при помощи подстроечных конденсаторов, подключенных параллельно С1 и С2. При этом конденсатором, подключенным параллельно С2, осуществляют грубую настройку, подключенным параллельно С1 точную.

Сопротивление резистора R1 может находиться в пределах

4,7…68 МОм, однако при его значении менее 10 МОм возбуждаются не все кварцевые резонаторы.

Рис. 19. Микросхема К176ИЕ5

На микросхеме К176ИЕ5 можно выполнить ждущий мультивибратор, обладающий большой выдержкой вырабатываемого импульса.

Работа этого ждущего мультивибратора основана на задержке времени, которая обеспечивается подсчѐтом импульсов, вырабатываемых генератором.

Генератор выполнен на инверторах, предназначенных для кварцевого генератора микросхемы. Для запрета его работы логическая единица с выхода 15 микросхемы подается на вход цепочки инверторов генератора через диод VD1. При подаче импульса на

вход запуска логический ноль с выхода 15 микросхемы закрывает диод VD1, и он не мешает нормальной работе генератора.

Длительность формируемого импульса составляет 214 периода задающего генератора, который задаѐтся параметрами элементов R1, С1.

На выходе 14 счетчика формируется импульс положительной полярности вдвое меньшей длительности, на выходе 9 пачка из 32 импульсов.

Микросхемы К176ИЕ8 и К561ИЕ8 десятичные счетчики Джонсона с дешифратором. Микросхемы имеют три входа вход установки исходного состояния R, вход для подачи счетных импульсов отрицательной полярности CN и вход для подачи счетных импульсов положительной полярности СР. Установка счетчика в 0 происходит при подаче на вход R логической единицы, при этом на выходе 0 появляется логическая единица, а на выходах 1 … 9 – логический ноль.

Рис. 20. Микросхема К176ИЕ8

Переключение счетчика происходит по спадам импульсов отрицательной полярности, подаваемых на вход CN, при этом на входе СР должен быть логический ноль. Можно также подавать импульсы положительной полярности на вход СР, переключение будет происходить по их спадам. На входе CN при этом должна быть логическая единица. Временная диаграмма работы микросхемы приведена на рис. 21.

Микросхема К561ИЕ9 счетчик с дешифратором, работа которой аналогична работе микросхем К561ИЕ8 и К176ИЕ8, но коэффициент пересчета и число выходов дешифратора 8, а не 10.

Рис. 21. Временная диаграмма работы микросхемы

Рис. 22. Микросхема К561ЕИ9

Так же, как и микросхема К561ИЕ8, данная микросхема является счѐтчиком Джонсона (т.е. построена на основе сдвигающего регистра с перекрестными связями). При подаче напряжения питания и отсутствии импульса сброса триггеры этих микросхем могут установиться в произвольное состояние, не соответствующее разрешенному состоянию счетчика. Однако в указанных микросхемах есть специальная цепь формирования разрешенного состояния счетчика, и при подаче тактовых импульсов счетчик через несколько тактов перейдет в нормальный режим работы. Поэтому в делителях частоты, в которых точная фаза выходного сигнала неважна, допустимо не подавать на входы R микросхем К176ИЕ8, К561ИЕ8 и К561ИЕ9 импульсы начальной установки.

Временная диаграмма работы микросхемы приведена на рис. 23.

Рис. 23. Временная диаграмма работы микросхемы

Микросхемы К176ИЕ8, К561ИЕ8, К561ИЕ9 можно объединять в многоразрядные счетчики с последовательным переносом, соединяя выход переноса Р предыдущей микросхемы с входом CN последующей и подавая на вход СР логический ноль. Возможно также соединение старшего выхода дешифратора (7 или 9) со входом СР следующей микросхемы и подача на вход CN логической единицы. Однако такие способы соединения приводят к накоплению задержек в многоразрядном счетчике. Максимальная рабочая частота многоразрядных счетчиков не снижается относительно частоты работы отдельной микросхемы.

На рис. 24 приведена схема таймера с использованием микросхем К176ИЕ8 или К561ИЕ8.

В момент пуска на вход CN микросхемы DD1 начинают поступать счетные импульсы. Когда микросхемы счетчика установятся в положения, набранные на переключателях SA1, SA2, на всех входах элемента «И-НЕ» DD3 получается логическая единица, что приведет к появлению логической единицы на выходе инвертора DD4, сигнализирующей об окончании заданного временного интервала.

Микросхемы К561ИЕ8 и К561ИЕ9 удобно использовать в делителях частоты с переключаемым коэффициентом деления. На рис. 25 приведен пример двухдекадного делителя частоты. Переключателем SA1 устанавливают единицы необходимого коэффициента пересчета, переключателем SA2 десятки. При достижении счетчиками DD1, DD2

состояния, соответствующего положениям переключателей, на все входы элемента DD3.1 приходит логическая единица.

Рис. 24. Схема таймера с использованием микросхем К176ИЕ8 или К561ИЕ8

Благодаря этому триггер на элементах DD3.2 и DD3.3 устанавливается в состояние, при котором на выходе элемента DD3.3 появляется логическая единица, сбрасывающая счетчики DD1, DD2 в исходное состояние. В результате на выходе элемента DD3.1 также получается логическая единица, и следующий входной импульс устанавливает триггер DD3.2, DD3.3 в исходное состояние, сигнал сброса со входов R микросхем DD1, DD2 снимается, и описанная выше процедура повторяется.

Триггер на элементах DD3.2 и DD3.3 гарантирует сброс микросхем DD1, DD2 при достижении счетчиком нужного состояния. При его отсутствии и большом разбросе порогов переключения микросхем DD1, DD2 по входам R возможен случай, когда одна из этих микросхем устанавливается в 0 и снимает сигнал сброса со входов R остальных микросхем ранее, чем сигнал сброса достигнет порога их переключения. Однако такой случай маловероятен, и обычно можно обойтись без триггера, точнее, без элемента DD3.2.

Рис. 25. Двухдекадный делитель частоты

Для получения коэффициента пересчета менее 10 для микросхемы К561ИЕ8 и менее 8 для К561ИЕ9 можно соединить выход дешифратора с номером, соответствующим необходимому коэффициенту пересчета, со входом R микросхемы непосредственно.

Микросхемы К561ИЕ10 и КР1561ИЕ10 содержат по два раздельных четырехразрядных двоичных счетчика, каждый из которых имеет входы СР, CN, R.

Установка триггеров счетчиков в исходное состояние происходит при подаче на вход R логической единицы. Логика работы входов СР и CN отлична от работы аналогичных входов микросхем К561ИЕ8 и К561ИЕ9. Триггеры микросхем К561ИЕ10 и КР1561ИЕ10 срабатывают по спаду импульсов на входе СР при логическом нуле на входе CN (для К561ИЕ8 и К561ИЕ9 на входе CN должна быть логическая единица).

|

Рис. 26. Микросхема К561ИЕ10

Возможна работа по фронтам импульсов на входе CN, при этом на входе СР должна быть логическая единица (для К561ИЕ8 и К561ИЕ9 – логический ноль). Таким образом, входы СР и CN в микросхемах К561ИЕ10 и КР1561ИЕ10 объединены по схеме элемента

«И», а в микросхемах К561ИЕ8 и К561ИЕ9 – по «ИЛИ».

При соединении микросхем в многоразрядный счетчик с последовательным переносом выходы 8 предыдущих счетчиков соединяют со входами СР последующих, а на входы CN подают логический ноль.

Один счетчик микросхемы может быть использован для построения делителей частоты с коэффициентом деления от 2 до 16. Для примера на рис. 27 приведена схема счетчика с коэффициентом пересчета 10.

Для получения коэффициентов пересчета 3, 5, 6, 9,12 можно воспользоваться той же схемой, соответствующим образом выбрав выходы счетчика для подключения ко входам DD2.1. Для получения коэффициентов пересчета 7, 11, 13, 14 элемент DD2.1 должен иметь три входа, для коэффициента 15 четыре входа.

Рис. 27. Схема счетчика с коэффициентом пересчета

Рис. 28. Микросхема К567ИЕ11

Микросхема К561ИЕ11 – двоичный четырѐхразрядный реверсивный счѐтчик.

Входы, выходы и режимы работы этой микросхемы были рассмотрены в разделе, посвящѐнном реверсивным счѐтчикам, поэтому остановимся только на каскадировании.

Для соединения микросхем в счетчик с последовательным переносом необходимо объединить между собой все входы С, выходы Р микросхем соединить со входами P1 следующих, а на вход P1 младшего разряда подать логический ноль. Выходные сигналы всех микросхем счетчика изменяются одновременно, однако максимальная частота работы счетчика меньше, чем отдельной микросхемы из-за накопления задержек в цепи переноса.

Особенности построения микросхемы К561ИЕ11 требуют, чтобы изменение сигнала направления счета на входе U происходило в паузе между счетными импульсами на входе С, то есть при логической единице на этом входе, или по спаду этого импульса.

Рис. 29. Схема счетчика

Рис. 30. Микросхема К176ИЕ12

Микросхема К176ИЕ12 предназначена для использования в электронных часах или других устройствах, функционирующих по временным параметрам.

В ее состав входят кварцевый генератор G с внешним кварцевым резонатором на частоту 32768 Гц и два делителя частоты на

32768 и на 60.

При подключении к микросхеме кварцевого резонатора, по приведѐнной схеме, она обеспечивает получение частот 32768,

1024, 128, 2, 1, 1/60Гц. Импульсы с частотой 128Гц формируются на выходах микросхемы Т1 … Т4, их скважность равна 4, сдвинуты они между собой на четверть периода. Эти импульсы предназначены для коммутации знакомест индикатора часов при динамической индикации. Импульсы с частотой 1/60Гц подаются на счетчик минут, импульсы с частотой 1Гц могут использоваться для подачи на счетчик секунд и для обеспечения мигания разделительной точки, для установки показаний часов могут использоваться импульсы с частотой 2Гц. Частота 1024Гц предназначена для звукового сигнала будильника и для опроса разрядов счетчиков при динамической индикации, выход частоты 32768 Гц контрольный.

Особенностью работы микросхемы является то, что первый спад на выходе минутных импульсов М появляется спустя 59 с после снятия сигнала установки нуля с входа R. Это заставляет при пуске часов отпускать кнопку, формирующую сигнал установки нуля, спустя одну секунду после шестого сигнала поверки времени. Фронты и спады сигналов на выходе М синхронны со спадами импульсов на входе С.

Сопротивление резистора R1 может иметь ту же величину, что и для микросхемы К176ИЕ5. Конденсатор С3 служит для точной подстройки частоты, С4 для грубой. В большинстве случаев конденсатор С2 может быть исключен.

Микросхема К176ИЕ13 предназначена для построения электронных часов с будильником. Она содержит счетчики минут и часов, регистр памяти будильника, цепи сравнения и выдачи звукового сигнала, цепи динамической выдачи кодов цифр для подачи на индикаторы. Обычно микросхема К176ИЕ13 используется совместно с К176ИЕ12.

Микросхема К561ИЕ14 двоичный и двоично-десятичный четырехразрядный счетчик.

Принцип его работы практически полностью повторяет принцип работы микросхемы К561ИЕ11. Отличие заключается в замене входа R на вход В вход переключения модуля счета.

Рис. 31. Микросхема К561ИЕ14

При логической единице на входе В микросхема К561ИЕ14 производит двоичный счет, так же, как и К561ИЕ11, при логическом нуле на входе В осуществляется двоично–десятичный счѐт. Назначение остальных входов, режимы работы и правила включения для этой микросхемы такие же, как и для К561ИЕ11.

Микросхема К561ИЕ16 14-разрядный двоичный счетчик с последовательным переносом.

Рис. 32. Микросхема К561ИЕ16

У микросхемы имеются два входа вход установки начального состояния R и вход для подачи тактовых импульсов С. Установка триггеров счетчика в 0 производится при подаче на вход R логической единицы, счет по спадам импульсов, подаваемых на вход С.

Счетчик имеет выходы не всех разрядов отсутствуют выходы разрядов 2 и 4, поэтому, если необходимо иметь сигналы со всех двоичных разрядов счетчика, следует использовать еще один счетчик, работающий синхронно и имеющий выходы 1, 2, 4, 8, например половину микросхемы К561ИЕ10.

Коэффициент деления одной микросхемы К561ИЕ16 составляет 214 = 16384, при необходимости получения большего коэффициента деления можно выход 8192 микросхемы соединить со входом еще одной такой же микросхемы или со входом СР любой другой микросхемы счетчика. Если вход второй микросхемы К561ИЕ16 подключить к выходу 1024 предыдущей, можно за счет уменьшения разрядности счетчика получить недостающие выходы двух разрядов второй микросхемы как показано на рис. 33.

Подключая ко входу микросхемы К561ИЕ16 половину микросхемы К561ИЕ10, можно не только получить недостающие выходы, но и увеличить разрядность счетчика на единицу, что позволяет и обеспечить коэффициент деления 215 = 32768.

Рис. 33. Выходы двух разрядов

Рис. 34. Микросхема К561ИЕ16

Рис. 35. Микросхема К561ИЕ10

Микросхема К176ИЕ17 представляет собой календарь. Она содержит счѐтчик дней недели, чисел месяца и месяцев.

Рис. 36. Микросхема К561ИЕ19

Микросхема К176ИЕ18 по своему построению во многом напоминает К176ИЕ12. Ее основным отличием является выполнение выходов Т1 … Т4 с открытым стоком, что позволяет подключать сетки вакуумных люминесцентных индикаторов к этой микросхеме без согласующих ключей. Кроме того данная микросхема имеет специальный формирователь звукового сигнала, выход которого выполнен с открытым стоком и позволяет подключать излучатели с сопротивлением 50Ом и выше между этим выходом и плюсом питания без эмиттерного повторителя.

Микросхемы К176ИЕ12, К176ИЕ13, К176ИЕ17, К176ИЕ18 допускают напряжение питания такое же, как и микросхемы серии К561 – от 3 до 15В.

Микросхема К561ИЕ19 пятиразрядный сдвигающий регистр с возможностью параллельной записи информации, предназначенный для построения счетчиков с программируемым модулем счета.

Микросхема имеет пять информационных входов для параллельной записи D1 … D5, вход информации для последовательной записи D0, вход параллельной записи S, вход сброса R, вход для подачи тактовых импульсов С и пять инверсных выходов 1 … 5.

Вход R является преобладающим при подаче на него логической единицы все триггеры микросхемы устанавливаются в ноль, на всех выходах появляется логическая единица независимо от сигналов на других входах. При подаче на вход R логического нуля, а на вход S логической единицы происходит запись информации со входов D1 … D5 в триггеры микросхемы, на выходах 1 … 5 она появляется в инверсном виде.

При подаче на входы R и S логического нуля возможен сдвиг информации в триггерах микросхемы, который будет происходить по спадам импульсов, поступающих на вход С. В первый триггер информация будет записываться со входа D0.

Если соединить вход DO с одним из выходов 1 … 5, можно получить счетчик с коэффициентом пересчета 2, 4, 6, 8, 10. Для примера на рисунке 38 показана временная диаграмма работы микросхемы в режиме деления на 6, которая организуется в случае соединения входа D0 с выходом 3.

Рис. 37. Временная диаграмма работы микросхемы в режиме деления

Если необходимо получить нечетный коэффициент пересчета

3, 5, 7 или 9, следует использовать двухвходовый элемент И, входы которого подключить соответственно к выходам 1 и 2, 2 и 3, 3 и 4, 4 и 5, в выход ко входу D0. Для примера на рисунке 38 приведена схема делителя частоты на 5 и временная диаграмма его работы.

Следует иметь в виду, что использование микросхемы К561ИЕ19 в качестве сдвигающего регистра невозможно, так как она содержит цепи коррекции, в результате чего комбинации состояний триггеров, не являющиеся рабочими для счетного режима, автоматически исправляются. Наличие цепей коррекции позволяет аналогично использованию микросхем К561ИЕ8 и К561ИЕ9 не подавать импульс начальной установки на счетчик, если фаза выходных импульсов не важна.

Микросхема КР1561ИЕ20 двенадцатиразрядный двоичный счетчик с коэффициентам деления 212 = 4096.

Рис. 38. Схема делителя частоты на 5 и временная диаграмма работы

Рис. 39. Микросхема КР1561ИЕ20

У нее два входа R (для установки нулевого состояния) и С (для подачи тактовых импульсов). При логической единице на входе R счетчик устанавливается в нулевое состояние, а при логическом нуле считает по спадам поступающих на вход С импульсов.

Микросхема во многом повторяет микросхему К561ИЕ16, поэтому еѐ можно использовать для деления частоты на коэффициенты, являющиеся степенью числа 2.

Рис. 40. Микросхема КР1561ИЕ21

Микросхема КР1561ИЕ21 синхронный двоичный счетчик с возможностью параллельной записи информации по спаду тактового импульса.

Подача логического нуля на вход R независимо от состояния других входов приводит к установке триггеров микросхемы в состояние нуля. Для обеспечения режима счета на входе R необходимо подать логическую единицу, тот же сигнал должен быть подан на входы разрешения параллельной записи EL, разрешения ЕС, разрешения выдачи сигнала переноса ЕР.

Изменение состояния триггеров счетчика при счете происходит по фронту импульсов, подаваемых на вход С. При подаче логического нуля на вход EL микросхема переходит в режим параллельной записи информации со входов D1 … D8. Запись происходит по фронтам импульсов на входе С, что позволяет использовать микросхему в режиме сдвигающего регистра. При записи на входе R должна быть логическая единица, сигналы на входах ЕС и ЕР произвольны.

На выходе переноса Р логическая единица появляется в том случае, когда счетчик находится в состоянии 9, а на входе ЕР – логическая единица, в остальных случаях на выходе Р логический ноль. Подача логического нуля на вход ЕР запрещает выдачу логической единицы на выходе Р и счет импульсов. Подача логического нуля на вход ЕС запрещает счет, но не запрещает выдачу сигнала переноса. Сигнал запрета счета (логический ноль на входах ЕС и ЕР) действует лишь в том случае, если он полностью перекрывает по длительности импульс на входе С, в том числе он может совпадать с ним по времени.

Для обеспечения параллельной записи на вход EL необходимо подать логический ноль. Информация на входы D1 … D8 может быть подана как при логической единице, так и при логическом нуле на входе С и удерживаться до момента перехода логического нуля на входе С в логическую единицу, когда и произойдет запись.

Для обеспечения счета с числа, введенного в микросхему при параллельной записи, логический ноль на входе EL должен быть изменен на логическую единицу или одновременно с переходом логического нуля в логическую единицу на входе С, или при логической единице на входе С.

На рис. 41 приведена схема соединения микросхем КР1561ИЕ21 в многоразрядный синхронный счетчик.

Рис. 41. Схема соединения микросхем КР1561ИЕ21 в многоразрядный синхронный счетчик

Как уже указывалось выше, микросхема КР1561ИЕ21 может работать в режиме сдвигающего регистра. Для обеспечения такого режима необходимо входы D1 … D8 соединить с выходами 1-2-4-8 в необходимом порядке. Для сдвига информации на один двоичный разряд по каждому тактовому импульсу в сторону старших разрядов соединение необходимо произвести в соответствии с рисунком 42.

Рис. 42. Схема соединения микросхем

КОНТРОЛЬНЫЕ ВОПРОСЫ

1. Что такое счетчик?

2. Классификация счетчиков в зависимости от класса цифровых автоматов и способа кодирования внутренних состояний.

3. Двоичный счетчик, его устройство, свойства, временные диаграммы работы.

4. Синхронные и асинхронные счетчики. Счетчики с параллельным и последовательным переносом.

5. Функция переходов JK-триггера, функция возбуждения Т-триггера.

6. Построение графа переходов и диаграмм Вейча для переходов функций возбуждений Т.

7. Принцип кодирования в коде 8421BCD.

8. Функции и схемная реализация двоично-десятичного счетчика.

9. Принцип кода Грея.

10. Применение канонического метода синтеза для построения счетчика

Грея.

11. Счетчики Джонсона. Свойства, таблица истинности.

12. Схемное решение и временные диаграммы работы счетчика. В чем состоит недостаток счетчиков Джонсона?

13. Реверсивные счетчики. Свойства, схемное решение.

14. Принцип работы микросхемы 561ИЕ11.

15. Программируемый делитель. Определение, свойства.

16. Специализированная микросхема КА561ИЕ15Б. Принцип работы, свойства. Как происходит процесс деления?

17. Преимущества микросхем КМОП-логики перед микросхемами ТТЛлогики.

18. Объясните принцип работы, свойства и схемное решение микросхем:

серии К176: К176ИЕ1, К176ИЕ2, К176ИЕ3, К176ИЕ4, К176ИЕ5, К176ИЕ8, К176ИЕ12, К176ИЕ13, К176ИЕ17, К176ИЕ18;

|

серии К561: К561ИЕ8, К561ИЕ9, К561ИЕ10, К561ИЕ11, К561ИЕ14, К561ИЕ16, К561ИЕ19;

серии КР1561: КР1561ИЕ10, КР1561ИЕ20, КР1561ИЕ21.

Материал взят из книги Логические автоматы. Типовые последовательностные схемы (А.В. Илюхин)

Счетчики Микросхемы последовательностного типа Справочник по микросхемам ТТЛ и КМОП Любительская Радиоэлектроника

Счетчики

В состав рассматриваемых серий ТТЛ-микросхем входит большое число счетчиков и делителей частоты, различающихся по своим свойствам и назначению.

Микросхема К155ИЕ1 (рис. 24) — делитель частоты на 10. Установка триггеров микросхемы в 0 осуществляется подачей лог. 1 одновременно на два объединенных по схеме И входа R. Рабочая полярность входных счетных импульсов, подаваемых на входы С, отрицательная. Импульсы можно подавать или отдельно на каждый из входов (на второй вход должна при этом подаваться лог. 1), или одновременно на оба входа. Одновременно с каждым десятым входным импульсом на выходе формируется равный ему по длительности выходной импульс отрицательной полярности. Многокаскадные делители частоты можно строить, соединяя входы С последующих каскадов с выходами предыдущих.

Микросхемы ИЕ2, К155ИЕ4 и ИЕ5 (рис. 25) содержат по четыре счетных триггера. В каждой микросхеме один из триггеров имеет отдельный вход С1 и прямой выход, три оставшихся триггера соединены между собой так, что образуют делитель на 8 в микросхеме ИЕ5, на 6 в К155ИЕ4 и на 5 в ИЕ2.

При соединении выхода первого триггера с входом С2 цепочки из трех триггеров образуются соответственно делители на 16, 12 и 10. Делители на 10 и 16 работают в коде 1-2-4-8, делитель на 12 — в коде 1-2-4-6. Микросхемы имеют по два входа R установки в 0, объединенные по схеме И. Сброс (установка в 0) триггеров производится при подаче лог. 1 на оба входа R. Микросхема ИЕ2 имеет, кроме того, входы R9 для установки в состояние 9, при котором первый и последний триггеры декады находятся в единичном состоянии, остальные — в нулевом.

Наличие входов установки, объединенных по схеме И, позволяет строить делители частоты с различными коэффициентами деления в пределах 2-6 без использования дополнительных логических элементов. На рис. 26 приведены схема декады на микросхеме К155ИЕ4 и ее временная диаграмма. До прихода десятого импульса декада работает как делитель частоты на 12. Десятый импульс переводит триггеры микросхемы в состояние 10, при котором на выходах 4 и 6 микросхемы формируются уровни лог. 1.

Эти уровни, поступая на входы R микросхемы, переводят ее в 0, в результате чего коэффициент пересчета К становится равным 10.

Для установки рассмотренной декады в 0 внешним сигналом необходимо введение в нее логических элементов И-НЕ (рис 27).

В табл. 4 приведены номера выводов микросхем, которые нужно соединить между собой для получения различных К Все делители, полученные соединением выводов по табл. 4, работают по одному принципу — при достижении состояния, соответствующего необходимому коэффициенту пересчета, происходит установка счетчика в 0. Исключение составляет делитель на 7 на микросхеме ИЕ2. В этом делителе после подсчета шести импульсов на входах R9 формируются уровни лог. 1, поэтому из состояния 5 делитель сразу переходит в состояние 9, минуя 6,7 и 8. Код работы этого делителя — невесовой.

Делители на микросхемах ИЕ5 и ИЕ2 работают в весовом коде 1-2-4-8, на микросхеме К155ИЕ4 — в коде 1-2-4-6 при использовании входа 14 и в коде 1-2-3 — при использовании входа 1.

Микросхемы ИЕ6 и ИЕ7 — реверсивные счетчики. Первый из них — двоично-десятичный, второй — двоичный Оба работают в коде 1-2-4-8 Цоколевка обеих микросхем одинакова (рис 28), различие в том, что первый считает до 10, второй до 16.

Таблица 4

| К | К155ИЕ2 | К155ИЕ4 | К155ИЕ5 | ||||||

| Вход | Вых. | Соединить выводы | Вход | Вых. | Соединить выводы | Вход | Вых. | Соединить выводы | |

| 2 | 14 | 12 | 14 | 12 | — | 14 | 12 | — | |

| 3 | 1 | 8 | 9-2,8-3 | 1 | 9 | — | 1 | 8 | 9-2,8-3 |

| 4 | 1 | 8 | 11-2-3 | 1 | 8 | 11-6,8-7 | 1 | 8 | — |

| 5 | 1 | 11 | — | 1 | 8 | 9-6,8-7 | 1 | 11 | 9-2,11-3 |

| 6 | 14 | 8 | 12-1,9-2,8-3 | 1 | 8 | — | 1 | 11 | 8-2,11-3 |

| 7 | 14 | 11 | 12-1,9-6,8-7 | 14 | 8 | 12-1-6,8-7 | — | — | — |

| 8 | 14 | 8 | 12-1,11-2-3 | 14 | 8 | 12-1,11-6,8-7 | 1 | 11 | — |

| 9 | 14 | 11 | 12-1-2,11-3 | — | — | — | 14 | 11 | 12-1-2,11-3 |

| 10 | 14 | 11 | 12-1 | 14 | 8 | 12-1,9-6,8-7 | 14 | 11 | 12-1,9-2,11-3 |

| 12 | — | 14 | 8 | 12-1 | 14 | 11 | 12-1,8-2,11-3 | ||

| 16 | — | — | — | — | — | — | 14 | 11 | 12-1 |

Рассмотрим для примера работу микросхемы ИЕ6 В отличие от рассмотренных ранее счетчиков, эта микросхема имеет большее число выходов и входов Входы +1 и -1 служат для подачи тактовых импульсов, +1 — при прямом счете, -1 — при обратном. Вход R служит для установки счетчика в 0, вход L — для предварительной записи в счетчик информации, поступающей по входам D1 — D8.

Установка триггеров счетчика в 0 происходит при подаче лог 1 на вход R, при этом на входе L должна быть лог. 1. Для предварительной записи в счетчик любого числа от 0 до 9 его код следует подать на входы D1 — D8 (D1 — младший разряд, D8 — старший), при этом на входе R должен быть лог 0, и на вход L подать импульс отрицательной полярности

Режим предварительной записи можно использовать для построения делителей частоты с перестраиваемым коэффициентом деления для учета фиксированной частоты (например, 465 кГц) в цифровой шкале радиоприемника Если этот режим не используется, на выходе L должен постоянно поддерживаться уровень лог 1

Прямой счет осуществляется при подаче импульсов отрицательной полярности на вход +1, при этом на входах -1 и L должна быть лог 1, на входе R — лог 0 Переключение триггеров счетчика происходит по спадам входных импульсов, одновременно с каждым десятым входным импульсом на выходе >=9 формируется отрицательный выходной импульс переполнения, который может подаваться на вход +1 следующей микросхемы многоразрядного счетчика Уровни на выходах 1-2-4-8 счетчика соответствуют состоянию счетчика в данный момент (в двоичном коде) При обратном счете входные импульсы подаются на вход -1, выходные импульсы снимаются с выхода <=0 Пример временной диаграммы работы счетчика приведен на рис. 29.

Первый импульс установки в 0 устанавливает все триггеры счетчика в 0. Три следующих импульса, поступающих на вход +1, переводят счетчик в состояние 3, которому соответствуют лог. 1 на выходах 1 и 2 и лог 0 — на 4 и 8. Если на входах D1 — D4 лог. 0, на входе D8 лог. 1, импульс на входе L устанавливает счетчик в состояние 8.

Следующие шесть импульсов, поступающие на вход +1, переводят счетчик последовательно в состояния 9,0,1,2,3,4 Одновременно с импульсом, переводящим счетчик в 0, на выходе S9 появляется выходной импульс прямого счета Следующие импульсы, поступающие на вход -1, изменяют состояние счетчика в обратном порядке 3, 2, 1,0,9,8 и т д.

Одновременно с импульсом обратного счета, переводящим счетчик в состояние 9, на выходе <=0 появляется выходной импульс.

В микросхеме ИЕ7 импульс на выходе =>15 появляется одновременно с импульсом на входе +1 при переходе счетчика из состояния 15 в состояние 0, а на выходе <=0 — при переходе счетчика из 0 в 15 одновременно с импульсом на входе -1.

Предельная частота функционирования микросхем К155ИЕ6, К155ИЕ7 — 15 МГц, К555ИЕ6 и К555ИЕ7 — 25 МГц, КР1533ИЕ6 и КР1533ИЕ7 — 30 МГц.

Микросхему К155ИЕ8 обычно называют делителем частоты с переменным коэффициентом деления, однако это не совсем точно. Эта микросхема содержит шестиразрядный двоичный счетчик, элементы совпадения, позволяющие выделять не совпадающие между собой импульсы — каждый второй, каждый четвертый, каждый восьмой и т. д. и управляемый элемент И-ИЛИ, который позволяет подавать на выход часть или все выделенные импульсы, в результате чего средняя частота выходных импульсов может изменяться от 1/64 до 63/64 частоты входных импульсов.

Графическое обозначение микросхемы приведено на рис. 30, пример временной диаграммы ее работы — на рис. 31. Для наглядности на рис. 30 вынесен логический элемент И-НЕ, входящий в микросхему.

Микросхема имеет следующие входы: инверсный вход ЕС — разрешения счета, при подаче на который лог. 1 счетчик не считает, вход R — установки 0, установка триггеров счетчика в 0 происходит при подаче на него лог. 1; вход С — вход тактовых импульсов отрицательной полярности, переключение триггеров счетчика происходит по спадам входных импульсов; входы XI — Х32 позволяют управлять выдачей отрицательных выходных импульсов, совпадающих по времени с входными, на выход Z. На рис. 31 в качестве примера показано, какие импульсы выделяются на выходе Z при подаче лог. 1 на входы:

Х32 (диаграмма Х32), Х16 (диаграмма Х16) и Х8 (диаграмма Х8). В этих случаях на выходе Z выделяется соответственно 32, 16 или 8 равномерно расположенных импульсов. Если же одновременно подать лог. 1 на несколько входов, например, на Х32 и Х8, то, как показано на диаграмме Z, на выходе Z выделится 40 импульсов, но расположенных неравномерно. В общем случае число импульсов N на выходе Z за период счета составит

N = 32 х Х32 + 16 х Х16 + 8 х Х8 + 4 х Х4 + 2 х Х2 + X1, где X1-Х32 принимают значения соответственно 1 или 0 в зависимости от того, подана или нет лог. 1 на соответствующий вход.

На выходе Р выделяется отрицательный импульс, фронт которого совпадает со спадом 63-го тактового импульса, спад — со спадом 64-го. Этот импульс может использоваться при каскадном соединении интегральных микросхем К155ИЕ8. Вход S — вход стробирования, при подаче на него лог. 1 выдача импульсов на выходе Z прекращается.

На рис. 32 приведена схема соединения двух делителей К155ИЕ8, позволяющая получить на выходе от 1 до 4095 импульсов при подаче на вход 4096 =64^2 импульсов. Число импульсов на выходе подсчитывается по формуле, аналогичной приведенной выше, в которой коэффициенты имеют значения от 2048 до 1. Если требуется соединить большее число делителей, их соединение производится аналогично рис. 32.

Однако выходной элемент И-НЕ, выполняющий функцию ИЛИ-НЕ для отрицательных импульсов, поступающих с выходов Z делителей, необходимо использовать из отдельной микросхемы И-НЕ или И.

Микросхема ИЕ9 (рис. 33) — синхронный десятичный счетчик с возможностью параллельной записи информации по фронту тактового импульса, имеет девять входов. Подача лог. 0 на вход R независимо от состояния других входов приводит к установке триггеров микросхемы в состояние 0. Для обеспечения режима счета на входе R необходимо подать лог. 1, тот же сигнал должен быть подан на входы разрешения параллельной записи EL, разрешения ЕС, разрешения выдачи сигнала переноса ER Изменение состояния триггеров счетчика при счете происходит по спаду импульсов отрицательной полярности, подаваемых на вход С.

При подаче лог. 0 на вход EL микросхема переходит в режим параллельной записи информации со входов D1 — D8. Запись происходит по спадам импульсов отрицательной полярности на входе С, что позволяет использовать микросхему в режиме сдвигающего регистра. При записи на входе R должна быть лог. 1, сигналы на входах ЕС и ЕР произвольны.

На выходе переноса Р лог. 1 появляется в том случае, когда счетчик находится в состоянии 9, а на входе ЕР — лог. 1, в остальных случаях на выходе Р лог. 0. Подача лог. 0 на вход ЕР запрещает выдачу лог. 1 на выходе Р и счет импульсов. Подача лог. 0 на вход ЕС запрещает счет, но не запрещает выдачу сигнала переноса. Сигнал запрета счета (лог. 0 на входах ЕС и ЕР) действует лишь в том случае, если он полностью перекрывает по длительности импульс отрицательной полярности на входе С, в том числе он может совпадать с ним по времени.

Для обеспечения параллельной записи лог. 0 на вход EL информация на входы D1 — D8 может быть подана как при лог. 1, так и при лог. 0 на входе С и удерживаться до момента перехода лог. 0 на входе С в лог. 1, когда и произойдет запись.

Для обеспечения счета с числа, введенного в микросхему при параллельной записи, лог 0 на входе EL должен быть изменен на лог. 1 или одновременно с переходом лог. 0 в лог. 1 на входе С, или при лог. 1 на входе С.

На рис. 34 (а) приведена схема соединения микросхем ИЕ9 в многоразрядный синхронный счетчик, которая снижает быстродействие счетчика, так как для его нормальной работы необходимо, чтобы сигнал переноса от младшего разряда прошел через все микросхемы до старшего разряда до подачи очередного тактового импульса. Для получения максимального быстродействия многоразрядного счетчика, равного быстродействию отдельной микросхемы, микросхемы можно соединить по схеме рис. 34 (б). В этом случае сигнал переноса с выхода Р микросхемы DD1 разрешает работу остальных микросхем, соединенных в счетчик по схеме рис. 34 (а), лишь в те моменты, когда микросхема DD1 находится в состоянии 9, поэтому от счетчика DD2 — DD9 требуется быстродействие в 10 раз меньшее быстродействия микросхемы DD1, что обеспечивается при любой практически встречающейся длине счетчика.

Как уже указывалось выше, микросхемы ИЕ9 могут работать в режиме сдвигающего регистра. Для обеспечения такого режима необходимо входы D1 — D8 соединить с выходами 1-2-4-8 в нужном порядке. Для сдвига информации на один двоичный разряд по каждому тактовому импульсу в сторону старших разрядов соединение необходимо произвести в соответствии с рис. 35 (а). Для обеспечения динамической индикации удобно сдвигать информацию сразу на один десятичный разряд, а сдвигающий регистр замыкать в кольцо. Такая возможность проиллюстрирована на рис. 36.

На рис. 36 не показаны цепи подачи импульсов и управляющих сигналов, которые могут быть выполнены в соответствии с рис. 34 (а) или 34 (б). Роль входа разрешения сдвига выполняет вход Запись. Естественно, что при соединении микросхем в соответствии с рис. 35,36 параллельная запись информации в микросхемы невозможна.

Микросхемы ИЕ9 удобно использовать в делителе с переключаемым коэффициентом пересчета. Для получения указанного режима достаточно сигнал переноса старшего разряда одноразрядного или многоразрядного счетчика через инвертор подать на вход разрешения записи, а на входы D1 — D8 подать код, определяющий коэффициент пересчета (рис. 37).

При установке счетчика в процессе счета в состояние 99…9 счетчик перейдет в режим параллельной записи и при подаче следующего тактового импульса вместо перехода в состояние 00…0 произойдет запись параллельного кода, поданного на входы D1 — D8 микросхем. В результате общий коэффициент пересчета N уменьшится на величину К, соответствующую численному значению этого кода, и составит

Коэффициент пересчета может меняться для выхода 2 в пределах 1…10^м (длительность выходных импульсов положительной полярности равна длительности входных), для выхода 1 — в пределах 2…10^м (длительность импульсов отрицательной полярности равна периоду входных импульсов).

Если делитель собран по схеме рис. 34 (б), инвертор DD3 необходимо заменить на двухвходовый элемент И-НЕ, второй вход которого подключить к выходу переноса Р первой микросхемы делителя.

Микросхема ИЕ10 (рис. 38) по своему функционированию аналогична микросхеме ИЕ9 и отличается от нее тем, что считает в двоичном коде, и ее коэффициент пересчета равен 16. В остальном ее работа и правила включения те же.

Микросхема ИЕ11 — десятичный синхронный счетчик (рис. 38). Логика его работы соответствует логике работы счетчиков ИЕ9. Отличие лишь в том, что для сброса в состояние 0 счетчика ИЕ9 необходима подача на вход R лог. 0, а для сброса в состояние 0 счетчика ИЕ11 кроме подачи на вход ER (разрешение уст. 0) лог. 0

необходима подача тактового импульса отрицательной полярности на вход С, по спаду которого и происходит сброс счетчика. Таким образом, все изменения выходных сигналов этой микросхемы происходят по спаду импульсов отрицательной полярности на входе С.

Микросхема КР1533ИЕ12 (рис. 39) обеспечивает параллельную запись и режим счета. Входы Dl, D2, D4, D8 служат для подачи сигналов кода при параллельной записи информации. Запись в триггеры счетчика происходит асинхронно при поступлении на вход L лог. 0 независимо от состояния других входов. При лог. 1 на входе L и лог. 0 на входе разрешения работы Е счетчик изменяет состояние по спадам импульсов отрицательной полярности на входе С. Направление счета определяется сигналом на входе D/U: при лог. 0 происходит счет вверх, при лог. 1 — вниз.

Для построения многоразрядных счетчиков у микросхемы есть два специальных выхода: последнего состояния 0/9 и переноса Р. На выходе 0/9 лог. 1 появляется при достижении состояния 9 при прямом счете и состояния 0 при обратном. В остальных случаях на выходе 0/9 — лог. 0. При наличии лог. 1 на выходе 0/9 и лог. 0 на входе Е одновременно с импульсом на входе С на выходе переноса Р появляется импульс отрицательной полярности и той же длительности.

Счетчик КР1533ИЕ12 не имеет входа установки в 0. Для этой цели на входы Dl, D2, D4, D8 подают лог. 0, а на вход L — импульс отрицательной полярности. Смена сигналов на входах D/U и Е должна происходить в момент переключения сигнала на входе С из лог. 0 в лог. 1 или в паузе между импульсами на входе С (то есть при лог. 1 на этом входе).

Пример временной диаграммы работы счетчика представлен на рис. 40. По импульсу отрицательной полярности на входе L записываются сигналы кода числа 7 в триггеры счетчика (сигналы кода 0111 на входах D8, D4, D2, Dl не показаны). Первые пять импульсов на входе С переводят его последовательно в состояния 8, 9, 0, 1, 2. На выходе 0/9 лог. 1 появляется при переходе счетчика в состояние 9. Импульс на его выходе Р формируется одновременно с третьим импульсом на входе С, по спаду которого счетчик переключается в состояние 0.

В момент окончания пятого импульса происходит смена направления счета изменением сигнала на входе D/U и следующие пять импульсов на входе С переводят счетчик последовательно в состояния 1, 0, 9, 8,7 и т. д. При переходе счетчика в состояние 0 на выходе 0/9 появляется лог. 1, а одновременно с восьмым импульсом на входе С, переключающим счетчик в состояние 9, на выходе Р формируется импульс отрицательной полярности.

Схема соединения микросхем КР1533ИЕ12 в многоразрядный счетчик показана на рис. 41 (а). Из-за последовательного переключения быстродействие такого счетчика в реверсивном режиме снижается относительно быстродействия одной микросхемы.

Если необходим реверсивный счетчик с максимально возможным быстродействием, его собирают по схеме рис. 41 (б). В этом счетчике все триггеры микросхем переключаются одновременно и его быстродействие не зависит от числа разрядов. Однако для каждого десятичного разряда, кроме первого, требуется элемент И-НЕ с числом входов, возрастающим по мере роста номера разряда.

В зависимости от необходимого быстродействия возможно построение различных вариантов последовательно-параллельного счетчика. Можно, например, не использовать выход 0/9 микросхемы DD4 (рис. 41, б), а ее выход Р соединить с входом тактовых импульсов второго такого счетчика.

Микросхема КР1533ИЕ13 (рис. 39) аналогична КР1533ИЕ12, но ее коэффициент пересчета равен 16. Все правила ее использования и схемы включения соответствуют микросхеме КР1533ИЕ12.

Микросхема ИЕ14 (рис. 42) во многом напоминает микросхему ИЕ2. Она также содержит счетный триггер с входом С2. При соединении выхода 1 счетного триггера (вывод 5) с входом С2 образуется двоично-десятичный счетчик, работающий в коде 1-2-4-8. Срабатывание триггера и делителя на 5 происходит по спадам импульсов положительной полярности. Различие с микросхемой ИЕ2 заключается в полярности импульсов сброса — триггеры микросхемы ИЕ14 устанавливаются в 0 при подаче на вход R лог. 0. Кроме того, в микросхеме ИЕ14 есть возможность предварительной установки триггеров счетчика. Для установки триггеров необходимый код следует подать на входы D1 — D8, а на вход L — импульс отрицательной полярности. При лог. 0 на входе L сигналы на выходах 1-8 повторяют сигналы на входах D1 — D8, при лог. 1 происходит запоминание и возможен счетный режим работы микросхемы.

Микросхему можно использовать в счетчиках с предварительной установкой, например, в цифровых шкалах радиоприемников и трансиверов с учетом промежуточной частоты.

Микросхема ИЕ15 (рис. 42) по своей структуре и функционированию аналогична микросхеме ИЕ14, но делитель с входом С2 делит частоту на 8,

Микросхемы КР531ИЕ16 и КР531ИЕ17 — реверсивные синхронные четырехразрядные счетчики — двоично-десятичный и двоичный соответственно. Разводка их выходов совпадает (рис. 43), более того, она совпадает с разводкой микросхем ИЕ9 и ИЕ10, за исключением вывода 1, для описываемых микросхем это вход изменения направления счета U/D, вход сброса отсутствует.

При лог. 1 на входе U/D счетчик считает вверх, при лог. 0 — вниз. Синхронная параллельная запись информации в микросхемы КР531ИЕ16 и КР531ИЕ17 происходит со входов D1 — D8 по спаду тактового импульса отрицательной полярности на входе С и подаче лог. 0 на вход разрешения загрузки EL. При счете на входе EL должна быть лог. 1.

Отличием описываемых микросхем от ИЕ9 и ИЕ10 является также полярность сигналов разрешения переноса ЕР и разрешения счета ЕС (для разрешения работы на эти входы необходимо подать лог. 1). Соответственно выходным разрешающим сигналом на выходе переноса Р является лог. 0, он появляется в случае, когда микросхема КР531ИЕ16 досчитала до состояния 9 (КР531ИЕ17 — до состояния 15) при прямом счете или до 0 при обратном, а на входе разрешения переноса ЕР — лог. 0.

Примеры соединения микросхем КР531ИЕ16 и КР531ИЕ17 в многоразрядный счетчик приведены на рис. 44 и 45. При соединении микросхем по схеме рис. 44 максимальная частота счета снижается по отношению к максимально возможной для одной микросхемы, при соединении по схеме рис. 45 — не снижается. Следует помнить, что переключение направления счета на входе U/D и смену информации на входах ЕР и ЕС следует производить в паузе между тактовыми импульсами, то есть при лог. 1 на входах С микросхем или в момент изменения сигнала на этих входах с лог. 0 на лог. 1. Входной ток микросхем по входу ЕР в состоянии лог. 0-4 мА. Микросхема ИЕ18 (рис. 46) аналогична по функционированию микросхеме ИЕ11, но ее коэффициент пересчета равен 16.

Рассмотренные выше микросхемы счетчиков серии КР531 имеют входные токи по управляющим входам, как правило, больше стандартных. При подаче на входы лог. 0 токи составляют для микросхем КР531ИЕ9 и КР531ИЕ10 по выводу 2 — 5 мА, выводу 10-3 мА, выводу 9-4 мА. Для микросхем КР531ИЕ11 и КР531ИЕ18 ток по выводу 10 составляет 4 мА, а для КР531ИЕ14 и КР531ИЕ15 ток по выводу 8-8 мА, по выводу 6-10 мА, по выводам 1, 3, 4, 10, 11, 13 — 0,75 мА.

Микросхема К555ИЕ19 — два четырехразрядных двоичных счетчика (рис. 47), каждый из которых имеет два входа: R — для установки триггеров счетчика в 0 при подаче на вход R лог. 1 и С — для подачи счетных импульсов. Срабатывание триггеров счетчика происходит по спадам импульсов положительной полярности, подаваемых на вход С, выходной код счетчиков — стандартный, 1-2-4-8. Для соединения счетчиков в многоразрядный выходы 8 предыдущих разрядов необходимо соединить со входами С последующих.

Микросхема К555ИЕ20 (рис. 47) -два четырехразрядных двоично-десятичных счетчика, каждый из которых аналогичен счетчику микросхем ИЕ2, за исключением входов установки в 0 R.

Каждый счетчик имеет триггер со входом С1, выходом 1 и делитель частоты на 5 со входом С2 и выходами 2,4,8. Триггер и счетчик срабатывают по спадам положительных импульсов, подаваемых на входы С1 и С2, на входе R при счете должен быть лог. 0. Для получения десятичного счетчика выход 1 надо соединить со входом С2, при этом код счетчика будет 1-2-4-8. Если же выход 8 соединить со входом С1, входные импульсы подать на вход С2, выходной код будет 1-2-4-5, а на выходе 1 сигнал будет иметь форму меандра с частотой, в 10 раз меньше входной. Впрочем, так же можно соединять счетчики микросхем ИЕ2 и ИЕ14. Предельная частота работы триггера — 25 МГц, делителя на 5 — 20 МГц.

Счётчики

Счётчики

Соединив последовательно несколько триггерных схем — делителей частоты на два, получим простейший многоразрядный двоичный делитель. Более общее название для делителей частоты — счетчики. Коэффициент деления счетчика, состоящего из n-триггеров типа Т, составляет 2n; здесь n — число двоичных разрядов счетчика. В настоящее время используется много вариантов счетных схем: асинхронные и синхронные; двоичные и десятичные; однонаправленные, только с увеличением счета, и двунаправленные, счет в которых может увеличиваться или уменьшаться (такие счетчики называют реверсивными). Коэффициент деления счетчика может быть либо постоянным, либо переключаемым.

Основой любой из этих схем служит линейка из нескольких триггеров. Рассмотренные варианты счетчиков различаются схемой управления этими триггерами. Между триггерами добавляются логические связи, назначение которых — запретить прохождение в цикле счета лишним импульсам, К примеру, четырехтриггерный счетчик может делить исходную частоту на 16, так как 24 = 16. Получим минимальный выходной код 0000, а максимальный 1111. Чтобы построить счетчик-делитель на 10, трех триггеров недостаточно (10 23), поэтому десятичный счетчик содержит в своей основе четыре триггера, но имеет обратные связи, останавливающие счет при коде 9 = 1001.

Таким обазом, удобно выпускать четырехтриггерные счетчики в двух вариантах: двоичном и десятичном. Примеры таких микросхем — пары: ИЕ6 и ИЕ7, ИЕ16 и ИЕ17. Расширять функции счетчиков можно; видоизменяя их цепи управления. Первоначально счетчики были асинхронными. В асинхронном режиме предыдущий триггер вырабатывает для последующего тактовые импульсы. Такие счетчики иногда называют счетчиками пульсаций.

В синхронном счетчике все триггеры получают тактовый импульс одновременно, поскольку тактовые входы их соединяются параллельно. Поэтому Триггеры переключатся практически одновременно. В счетчике пульсаций каждый триггер, вносит в процесс счета определенную задержку, поэтому младшие разряды результирующего кода появляются на выходах триггеров неодновременно, т. е. несинхронно с соответствующим тактовым импульсом. Например, для четырехразрядного счетчика пульсаций выходной параллельный код 1111 появится на выходах триггеров уже после того, как поступит шестнадцатый тактовый импульс, кроме того, эти четыре единицы сформируются неодновременно.

Синхронная схема значительно сложнее асинхронной. На ее выходах данные от каждого разряда появляются одновременно и строго синхронно с последним входным импульсом. В синхронный счетчик разрешается синхронная (с тактовым импульсом) параллельная (в каждый триггер) загрузка начальных данных. Триггерная линейка синхронного счетчика снабжается специальным шифратором, который называется схемой ускоренного переноса (СУП).

Внутренние логические элементы управления, которыми часто снабжаются счетчики, позволяют сделать процесс счета реверсивным. Согласно команде, подаваемой на вход управления счетом больше/меньше, можно либо, увеличивать либо уменьшать на единицу содержимое счетчика при каждом очередном тактовом импульсе. У некоторых счетчиков тактовые входы на увеличение и на уменьшение отдельные.

Сброс данных счетчика, чтобы на всех выходах установился нулевой код, у одних схем асинхронный R, у других синхронный SR, происходит одновременно е приходом тактового импульса. Имеются счетчики с переменным коэффициентом деления. Устанавливаемый коэффициент деления зависит от кода, набранного на входах управления.

Рассмотрим микросхемы КМОП среднего уровня интеграции, необходимых для счета импульсов и деления частот. Счетчики-делители составляют несколько групп. Например, счетчики ИЕ3 ИЕ5 предназначены для построения схем электронных секундомеров, часов, таймеров. Их можно использовать, например, для обслуживания индикаторов цифровых мультиметров, термометров. Счетчики ИЕ8 и ИЕ9 имеют дешифрованные выходы (10 и 8 соответственно). Счетчики ИЕ11 и ИЕ14 однотипные четырехразрядные, реверсивные. Разнообразные возможности деления частот открывает применение счетчиков выполненых на микросхемах КМОП: ИЕ2, ИЕ10, ИЕ16 и ИЕ19. Имеются счетчики асинхронные, синхронные, разрядные и даже 14-разрядный — ИЕ16.

мир электроники — Микросхемы серии К176, К561, К564

Электронные компоненты

материалы в категории

Цоколевка и параметры микросхем серии К176, К561, К564

Микросхемы этой серии выполнены по технологии КМОП. Микросхемы, имеющие в своем обозначении после указания серии буквенное сочетание ЛА, а также четырехвходовые элементы микросхемы К176ЛП12, выполняют функцию И-НЕ. Микросхемы с сочетанием ЛЕ, а также трех- и четырехвходовые элементы микросхем К176ЛП4 и К176ЛП11, выполняют функцию ИЛИ-НЕ. В состав микросхемы К176ЛИ1 входит девятивходовый элемент И и инвертор, микросхема КР1561ЛИ2 — четыре двухвходовых элемента И.

|

Обозначение микросхемы |

Функциональное назначение |

Число выводов корпуса |

Предельная частота, МГц при Uпит, В |

Номер рис. |

||

|

5 |

9,10 |

15 |

||||

|

КР1561АГ1 |

2 ждущих мультивибратора |

16 |

— |

— |

— |

277 |

|

К176ИД1 К561ИД1 |

Дешифратор 4-10 с прямыми выходами |

16 |

— |

— |

— |

232 |

|

К176ИД2 К176ИДЗ |

Преобразователи двоично-десятичного кода в код семисегментного индикатора |

16 16 |

— |

— |

— |

235 235 |

|

564ИД4 564ИД5 |

Преобразователи двоично-десятичного кода в код семисегментного индикатора |

16 16 |

— |

— |

— |

235 235 |

|

КР1561ИД6 |

2 дешифратора 2-4 с прямыми выходами |

16 |

— |

— |

— |

238 |

|

КР1561ИД7 |

2 дешифратора 2-4 с инверсными выходами |

16 |

— |

— |

— |

238 |

|

К176ИЕ1 |

Шестиразрядный двоичный счетчик |

14 |

— |

1 |

— |

172 |

|

К176ИЕ2 |

Пятиразрядный двоичный и десятичный счетчик |

16 |

— |

2 |

— |

173 |

|

К176ИЕЗ |

Счетчик-делитель на 6 с выходом на семисегментный индикатор |

14 |

— |

1 |

— |

176 |

|

К176ИЕ4 |

Декада с выходом на семисегментный индикатор |

14 |

— |

1 |

— |

177 |

|

К176ИЕ5 |

Кварцевый генератор и делитель частоты на 32768 |

14 |

184 |

|||

|

К176ИЕ8 К561ИЕ8 |

Десятичный счетчик с дешифратором |

16 |

1 |

2 3 |

185 |

|

|

К561 ИЕ9 |

Двоичный счетчик с дешифратором |

16 |

1 |

3 |

— |

187 |

|

К561ИЕ10 КР1561 ИЕ10 |

2 четырехразрядных двоичных счетчика |

16 |

1,5 |

4 3 |

4 |

195 |

|

К561 ИЕ11 |

Четырехразрядный двоичный реверсивный счетчик |

16 |

— |

5 |

— |

200 |

|

К176ИЕ12 |

Кварцевый генератор и делители частоты на 32768 и 60 |

16 |

— |

1.2 |

— |

203 |

|

К176ИЕ13 |

Счетчик для часов с будильником |

16 |

— |

1,2 |

— |

205 |

|

К561ИЕ14 |

Четырехразрядный десятичный реверсивный счетчик |

16 |

1,5 |

3 |

— |

211 |

|

КА561ИЕ15А КА561ИЕ15Б |

Делитель частоты с переключаемым коэффициентом деления |

24 |

0,8 0,4 |

1,5 0,75 |

— |

212 |

|

К561ИЕ16 |

14-разрядный двоичный счетчик |

16 |

1,5 |

4 |

— |

214 |

|

К176ИЕ17 |

Счетчик-календарь |

16 |

— |

— |

— |

219 |

|

К176ИЕ18 |

Кварцевый генератор и делители частоты на 32768 и 60 |

16 |

1 |

1 |

— |

221 |

|

К561ИЕ19 |

Счетчик с переключаемым коэффициентом деления |

16 |

0,6 |

1.8 |

— |

222 |

|

Обозначение микросхемы |

Функциональное назначение |

Число выводов корпуса |

Предельная частота, МГц при Uпит,, В |

Номер рис. |

||

|

5 |

9, 10 |

15 |

||||

|

КР1561ИЕ20 |

12-разрядный двоичный счетчик |

16 |

— |

— |

— |

226 |

|

КР1561ИЕ21 |

Четырехразрядный двоичный синхронный счетчик |

16 |

— |

— |

— |

227 |

|

К561ИК1 |

3 мажоритарно-мультиплексорных элемента |

16 |

— |

— |

— |

268 |

|

564ИК2 |

Устройство управлений пятиразрядным индикатором |

24 |

— |

— |

— |

241 |

|

К176ИМ1 К561ИМ1 |

Четырехразрядный двоичный сумматор |

16 |

— |

— |

— |

262 |

|

К561ИП2 |

Элемент сравнения четырехразрядных чисел |

16 |

— |

— |

— |

271 |

|

564ИР1 |

18-разрядный сдвигающий регистр |

14 |

1,5 |

3 |

— |

228 |

|

К176ИР2 К561ИР2 |

2 четырехразрядных сдвигающих регистра |

16 |

— |

2 4.5 |

— |

228 |

|

К176ИРЗ |

Четырехразрядный сдвигающий регистр |

14 |

— |

2 |

— |

228 |

|

К561ИР6 |

Восьмиразрядный сдвигающий регистр (Z) |

24 |

— |

— |

— |

228 |

|

К561ИР9 |

Четырехразрядный сдвигающий регистр |

16 |

— |

— |

— |

228 |

|

К176ИР10 |

18-разрядный сдвигающий регистр |

14 |

— |

2 |

— |

228 |

|

564ИР13 |

Регистр последовательного приближения |

24 |

2 |

5 |

— |

231 |

|

КР1561ИР14 |

Четырехразрядный регистр хранения информации (Z) |

16 |

1.8 |

3.6 |

4,8 |

228 |

|

КР1561ИР15 |

Четырехразрядный реверсивный сдвигающий регистр |

16 |

— |

— |

— |

228 |

|

К561КП1 КР1561КП1 |

2 мультиплексора 4-1 |

16 |

— |

— |

— |

251 |

|

К561КП2 КР1561КП2 |

Мультиплексор 8-1 |

16 |

— |

— |

— |

259 |

|

К176КТ1 |

4 ключа |

14 |

— |

— |

— |

250 |

|

К561КТЗ КР1561КТЗ |

4 ключа |

14 |

— |

— |

— |

250 |

|

К176ЛА7 К561ЛА7 |

4 элемента 2И-НЕ |

14 |

— |

— |

— |

162 |

|

К176ЛА8 К561ЛА8 |

2 элемента 4И-НЕ |

14 |

— |

— |

— |

162 |

|

К176ЛА9 К561ЛАР КР1561ЛА9 |

3 элемента ЗИ-НЕ |

14 |

— |

— |

— |

162 |

|

Обозначение микросхемы |

Функциональное назначение |

Число выводов корпуса |

Предельная частота, МГц при Uпит, В |

Номер рис. |

||

|

5. |

9,10. |

15 |

||||

|

564ЛА10 |

2 элемента 2И-НЕ (ОС) |

14 |

— |

— |

— |

162 |

|

К176ЛЕ5 К561ЛЕ5 КР1561ЛЕ5 |

4 элемента 2ИЛИ-НЕ |

14 |

— |

— |

— |

162 |

|

К176ЛЕ6 К561ЛЕ6 КР1561ЛЕ6 |

3 элемента 4ИЛИ-НЕ |

14 |

— |

— |

— |

162 |

|

К176ЛЕ10 К561ЛЕ10 КР1561ЛЕ10 |

3 элемента 3 ИЛИ-НЕ |

14 |

— |

— |

— |

162 |

|

К176ЛИ1 |

9И+НЕ |

14 |

— |

— |

— |

162 |

|

КР1561ЛИ2 |

4 элемента 2И |

14 |

— |

— |

— |

162 |

|

К561ЛН1 |

б элемента НЕ (Z) |

16 |

— |

— |

— |

165 |

|

К561ЛН2 |

6 элемента НЕ |

14 |

— |

— |

— |

165 |

|

К561ЛНЗ |

6 повторителей (Z) |

16 |

— |

— |

— |

165 |

|

К176ЛП1 |

6 транзисторов |

14 |

— |

— |

— |

273 |

|

К176ЛП2 К561ЛП2 |

4 элемента ИЛИ с исключением |

14 |

— |

— |

— |

263 |

|

К176ЛП4 |

2 элемента ЗИЛИ-НЕ+НЕ |

14 |

— |

— |

— |

162 |

|

К176ЛП11 |

2 элемента 4ИЛИ-НЕ + НЕ |

14 |

— |

— |

— |

162 |

|

К176ЛП12 |

2 элемента 4И-НЕ + НЕ |

14 |

— |

— |

— |

162 |

|

К561ЛП13 |

3 мажоритарных элемента |

14 |

— |

— |

— |

267 |

|

КР1561ЛП14 |

4 элемента ИЛИ с исключением |

14 |

— |

— |

— |

263 |

|

К176ЛС1 |

3 мультиплексора 2-1 |

14 |

— |

— |

— |

269 |

|

К561ЛС2 |

4 элемента И-ИЛИ |

16 |

— |

— |

— |

270 |

|

К176ПУ1 |

5 преобразователей уровня КМОП-ТТЛ с инверсией |

14 |

— |

— |

— |

164 |

|

К176ПУ2 |

6 преобразователей уровня КМОП-ТТЛ с инверсией |

16 |

— |

— |

— |

164 |

|

К176ПУЗ |

6 преобразователей уровня КМОП-ТТЛ |

16 |

— |

— |

— |

164 |

|

К176ПУ4 КР1561ПУ4 |

6 преобразователей уровня КМОП-ТТЛ |

16 |

— |

— |

— |

164 |

|

К176ПУ5 |

4 преобразователя уровня ТТЛ-КМОП |

16 |

— |

— |

— |

164 |

|

564ПУ6 |

4 преобразователя уровня ТТЛ-КМОП (Z) |

16 |

— |

— |

— |

164 |

|

К561ПУ7 |

6 преобразователей уровня ТТЛ-КМОП с инверсией |

14 |

— |

— |

— |

164 |

|

К561ПУ8 |

6 преобразователей уровня ТТЛ-КМОП |

14 |

— |

— |

— |

164 |

|

К561СА1 |

13-входовый сумматор по модулю 2 |

16 |

— |

— |

— |

266 |

|

Обозначение микросхемы |

Функциональное назначение |

Число выводов корпуса |

Предельная частота, МГц при Uпит, В |

Номер рис. |

||

|

5 |

9,10 |

15 |

||||

|

К176ТВ1 К561 ТВ 1 КР1561ТВ1 |

2 JK-триггера |

14 |

3.5 |

2 8 8 |

12 |

169 |

|

К561ТЛ1 КР156ГГЛ1 |

4 триггера Шмитта 2И-НЕ |

14 |

— |

2 |

— |

163 |

|

К176ТМ1 |

2 D-триггера |

14 |

— |

1 |

— |

169 |

|

К176ТМ2 К561ТМ2 |

2 D-триггера |

14 |

— |

1 4.5 |

— |

169 |

|

К561ТМЗ |

4 D-триггера |

16 |

— |

2 |

— |

168 |

|

К561ТР2 |

4 RS-триггера (Z) |

16 |

— |

— |

— |

166 |

|

564УМ1 |

4 D-триггера с увеличенной амплитудой выходного сигнала |

16 |

— |

— |

— |

168

|