Транзисторно−транзисторная логика (ТТЛ) | Основы электроакустики

Характерной особенностью ТТЛ являются многоэмиттерные транзисторы. Эти транзисторы сконструированы таким образом, что не оказывают влияния друг на друга. Каждому эмиттеру соответствует свой p-n-переход. В первом приближении многоэмиттерный транзистор может моделироваться схемой на диодах (пунктир на рис. 18.8), в этом случае он работает как схема диодно-транзисторной логики И-НЕ.

К достоинствам ТТЛ-логики можно отнести: высокое быстродействие (10 нс), надежность, радиационную стойкость.

Недостатками являются: наличие резисторов, большая площадь на кристалле, большая потребляемая мощность, наличие паразитных транзисторов.

Рис. 18.8. Схема ТТЛ-элемента с простым инвертором, выполняющая логическую операцию И-НЕ

Из анализа схемы можно сделать вывод, что если на один из входов или на оба входа подать низкий уровень напряжения, то ток базы транзистора VT2 будет равен нулю, и на коллекторе транзистора VT2 будет высокий уровень напряжения. Если на оба входа подать высокий уровень напряжения, то через базу VT2 транзистора будет протекать большой базовый ток и на коллекторе транзистора VT2 будет низкий уровень напряжения, т. е. данный элемент реализует функцию И-НЕ.

Рис. 18.9. Базовый элемент ТТЛ со сложным инвертором, выполняющий логическую операцию И-НЕ

Если на один или оба входа одновременно подан низкий уровень напряжения, то многоэмиттерный транзистор находится в состоянии насыщения и транзистор VT2закрыт, а, следовательно, закрыти транзистор VT4, т. е. на выходе будет высокий уровень напряжения. Если на обоих входах одновременно действует высокий уровень напряжения, то транзистор VT2открывается и входит в режим насыщения, что приводит к открытию и насыщению транзистора VT4и запиранию транзистора VT3, т. е. реализуется функция И-НЕ.

Элементы с тремя состояниями и с открытым коллектором. Вентили ТТЛ и КМОП имеют двухтактные выходные схемы: ВЫСОКИЙ или НИЗКИЙ уровень подается на выход через открытый биполярный или МОП-транзистор. Такую схему, которая носит название активной нагрузки, а в ТТЛ называется также столбовым выходом, используют почти все логические элементы. Эта схема обеспечивает низкое выходное сопротивление в обоих состояниях, имеет малое время переключения и обладает более высокой помехоустойчивостью по сравнению с одиночным транзистором, который использует в качестве коллекторной нагрузки пассивный резистор.

В случае КМОП применение активного выхода, помимо всего прочего, позволяет понизить рассеиваемую мощность. Однако существует ряд ситуаций, при которых активный выход, оказывается неудобным.

В качестве примера представим себе вычислительную систему, в которой должны обмениваться данными несколько функциональных блоков. Центральный процессор (ЦП), память, а также различные периферийные устройства должны иметь возможность передавать и принимать 16-разрядные слова, и было бы, мягко говоря, неудобно использовать для соединения каждого устройства с каждым индивидуальный 16-жильный кабель.

Для решения этой проблемы используется так называемая шина (или магистраль) данных (databus), т. е. один 16-жильный кабель, доступный для всех устройств. Такая структура аналогична телефонному каналу коллективного пользования: в каждый момент времени «говорить» («передавать данные») может только одно устройство, а остальные могут только «слушать» («принимать данные»). При использовании шинной системы необходимо иметь соглашение о том, кому разрешено «говорить». В связи с этим употребляются такие термины, как «арбитр шины», «ведущее устройство» и «устройство управления шиной».

Для возбуждения шины нельзя использовать вентили (или другие схемы) с активным выходом, поскольку их нельзя отключить от общих информационных линий (в любой момент времени выходы устройств, подключенные к шине, будут находиться в состоянии ВЫСОКОГО или НИЗКОГО уровня). Для этого случая необходим вентиль, выход которого может находиться в «обрыве», т. е. быть «открытым». Такие устройства выпускаются промышленностью и имеют две разновидности, которые носят названия «элементов с тремя состояниями»и «элементов с открытым коллектором». Начнем с рассмотрения последних, подразумевая, что все сказанное применимо также и к элементам с тремя состояниями.

В выходной схеме вентиля с открытым коллектором отсутствует транзистор, являющийся активной нагрузкой (рис. 18.10).

Рис. 18.10. ТТЛ вентиль с открытым коллектором

При использовании таких элементов внешний нагрузочный резистор можно подключить к любому источнику. Величина этого резистора не является критичной: при малых значениях резистора обеспечиваются повышенные быстродействия и помехоустойчивость, однако повышаются рассеиваемая мощность и нагрузочный ток выходного каскада. Для ТТЛ типичные значения лежат в пределах от нескольких сотен до нескольких тысяч Ом. Как мы вскоре покажем, все, что далее будет говориться о вентилях с открытым коллектором, относится также и к вентилям с тремя состояниями.

Иногда возникает необходимость логического объединения выходов очень большого числа элементов. Например, для объединения 20 выходов потребовалось бы использовать логический элемент с 20 входами и вести к нему 20 отдельных проводов. Этого можно избежать, используя логические элементы с открытым коллектором. В качестве выходного каскада они содержат, как показано на рисунке 18.10,

Выходное напряжение имеет высокий уровень только тогда, когда все выходные транзисторы элементов заперты, следовательно, здесь реализуется функция ИЛИ. Так как логическая связь организуется с помощью внешнего монтажа, такое соединение условно называется

Другим применением схем с открытым коллектором является управление внешней нагрузкой, которая должна подключаться к источнику положительного напряжения, превышающего напряжение питания ИМС. Может, частности, потребоваться включить маломощную 12-вольтовую лампочку или сформировать перепад логических уровней напряжения 15 В с помощью резистора, установленного между выходом вентиля и источником +15 В (рис. 18.12).

Рисунок 18.11 Реализация функции «монтажное ИЛИ»

Однако такая схема имеет существенный недостаток: переход в высокоомное (единичное) состояние из-за паразитных емкостей происходит всегда медленнее, чем в низкоомное (нулевое). Поэтому вместо элементов с открытым коллектором лучше использовать элементы с

Рис. 18.12. Подключение вентиля с открытым коллектором к источнику 15В

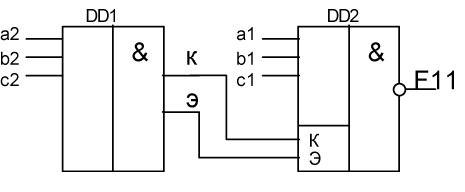

Соответствующая схема ТТЛ представлена на рис. 18.13.

Если уровень управляющего напряжения UEнизкий, запираются обатранзистора и . При высоком уровне UE получим обычную логическую связь И-НЕ между входными сигналами и . Аналогичным образом можно перевести в высокоомное (безразличное) состояние и трехстабильный элемент КМОП.

Логические элементы ттл.

В ИС ТТЛ логики удачно сочетаются хорошие функциональные показатели: быстродействие, помехоустойчивость, нагрузочная способность, умеренное потребление энергии, невысокая стоимость.

Принцип действия различных модификаций ТТЛ одинаков и различаются они главным образом временем задержки сигнала и потребляемой мощностью.

Основные электрические параметры для всех серий ТТЛ согласованы, поэтому элементы различных серий: могут непосредственно соединятся друг с другом.

Основные электрические параметры

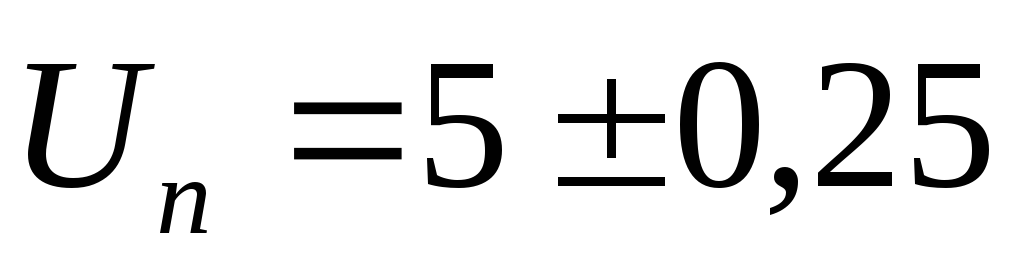

Напряжение питания:  В

В

Выходное напряжение

Высокий уровень  В

В

Низкий уровень  В

В

Входное напряжение

Высокий уровень

Низкий уровень  В

В

Основные характеристики серии ис ттл

Микросхема | Номер серии | один элемент, НС | потребления) на 1 эл. мВт | Эл, пДж |

Универсальная (стандартная) | 133 135 | 10 | 10 | 90 |

Быстродействующая | 130 К131 | 6 | 23 | 200 |

Микромощная | 134, КР134 | 33 | 1 | 30 |

На транзисторах Шоттки (маломощная) | 530, К531 533, К555 1533 1531 | 3 9,5 4 3 | 19 2 1,2 4 | 57 19 4,8 12 |

Основная особенность ИС ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор – он имеет несколько эмиттеров, объединенных общей базой.

Эквивалентен нескольким независимым транзистором с объединенными базами и коллекторами.

Рассмотрим принципиальную схему базового элемента И – НЕ 155 серии.

Схема содериний три каскада:

Входной

Выходной

.

.

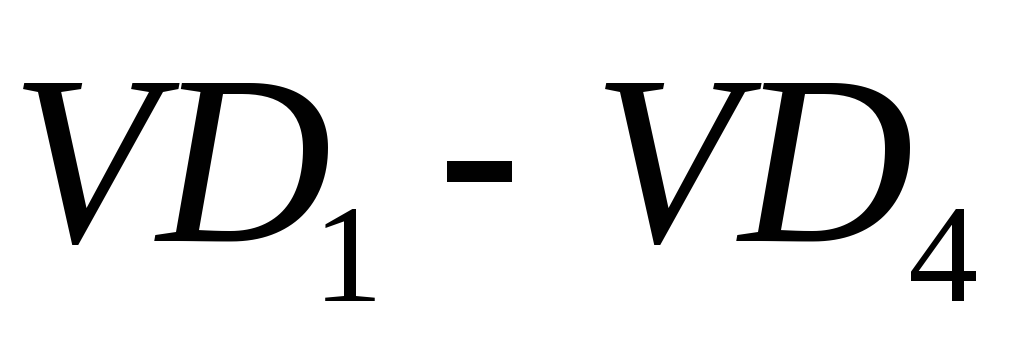

— смещены в обратном направлении и не

влияют на работу при нормальном

использовании.

— смещены в обратном направлении и не

влияют на работу при нормальном

использовании.

Когда один или несколько входов соединены

с ”землей” (лог. ”0”) то переход Б – Э

смещен в прямом направлении. Напряжение

по базе ~ 0,7 В недостаточно для открывания

трех переходов – коллекторного  и двух эмиттерных

и двух эмиттерных .

Так как

.

Так как заперт,

на его коллекторе – высокое напряжение.

Транзистор

заперт,

на его коллекторе – высокое напряжение.

Транзистор и диод

и диод открыты. Выходное напряжение

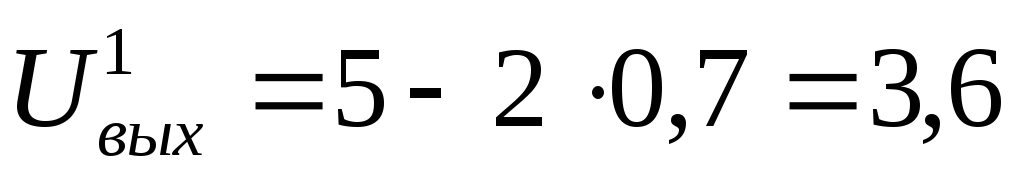

открыты. Выходное напряжение В

(без нагрузки)

В

(без нагрузки)

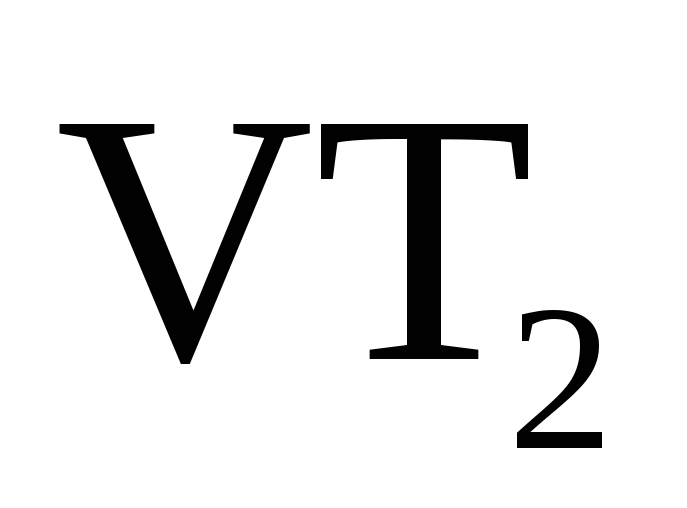

Когда на все входы действует напряжение

высокого уровня, транзистор  работает в инверсном режиме (переход Б

– Э смещен в обратном направлении, а Б

– К — в прямом.) Ток, протекающий через

работает в инверсном режиме (переход Б

– Э смещен в обратном направлении, а Б

– К — в прямом.) Ток, протекающий через ,

,

открывает

открывает .

Эмиттерный ток

.

Эмиттерный ток создает падение напряжения на

создает падение напряжения на ,

достаточное для открывания

,

достаточное для открывания .

. запрет, поэтому

запрет, поэтому В (напряжение насыщения

В (напряжение насыщения ).

Диод

).

Диод создает дополнительное смещение для

надежного запирания

создает дополнительное смещение для

надежного запирания в этом режиме.

в этом режиме.

Типичная передаточная характеристика

Быстродействие ИС ТТЛ можно повысить двумя способами:

Уменьшая сопротивление резисторов и паразитные ёмкости.

Предотвращая насыщение транзисторов, а следовательно, и накопление зарядов в базах.

В сериях 130, 131 выходной каскад выполнен на составном транзисторе, который обладает меньшим выходным сопротивлением, что способствует быстродействию.

В микромощных сериях мощность потребления снижена за счет повышения номиналов используемых резисторов.

Логические элементы ттлш

Другой метод повышения быстродействия, причем более результативный и перспективный состоит в применении транзисторов с барьером Шотки.

Диод Шотки – металлополупроводниковый выпрямляющий контакт. Отличие от диодов с р — nпереходов состоит:

время выключения ДШ очень мало (100 пс) и не зависит от температуры. У обычных диодов (1 – 100 нС).

Для отпирания диодов Шотки требуется напряжение 0,2 – 0,4 В против 0,5 – 0,8 В для диодов с р – nпереходом и может регулироваться подбором металла, образующего контакт с полупроводником.

Диоды Шотки подключаются параллельно коллекторному переходу транзистора и придают ему ряд новых качеств, которые называются транзисторами Шотки.

а) Распределение напряжений б) Транзистор в) Условное изображение

в насыщенном транзисторе с барьером Шотки транзистора Шотки

Когда Tзаперт потенциал

К выше потенциала Б, диод смещен в

обратном направлении и не влияет на

работу транзистора. Когда в процессе

открывания транзистора потенциал базы

становится больше потенциала коллектора

диод открывается и на нем устанавливается

напряжение .

Остаточное напряжение на коллекторе

транзистора

.

Остаточное напряжение на коллекторе

транзистора .

То есть режима насыщения не возникает.

Благодаря этому при запирании транзистора

исключается задержка, выраженная

рассасыванием избыточного заряда.

.

То есть режима насыщения не возникает.

Благодаря этому при запирании транзистора

исключается задержка, выраженная

рассасыванием избыточного заряда.

На рисунке приведена принципиальная схема и передаточная характеристика базового логического элемента И – НЕ.

Фазарасщипительный каскад имеет

корректирующую цепочку  ,

позволяющую получать передаточную

характеристику по форме, близкую к

прямоугольной. Благодаря применению

транзистора Дарлингтона, получается

малая выходное сопротивление,

обеспечивающее симметричную задержку

,

позволяющую получать передаточную

характеристику по форме, близкую к

прямоугольной. Благодаря применению

транзистора Дарлингтона, получается

малая выходное сопротивление,

обеспечивающее симметричную задержку .

.

Логические элементы И – НЕ наиболее характерны для семейства ТТЛ . Они производятся в виде самостоятельных изделий, а также служат основой для построения других устройств.

Увеличение числа входов (расширение по И) можно организовать из нескольких схем И – НЕ, пользуясь законом Де Моргана или подключением дополнительных, внешних диодов и резистора к любому из входов И – НЕ. Значение резистора

кОм.

кОм.

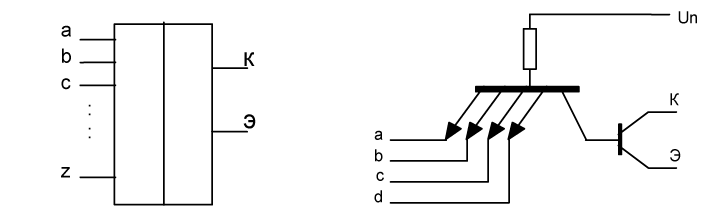

Существует так же специальные микросхемы расширителей по ИЛИ (экспандеры).

Существуют ИС двух типов:

ИС со входами расширения.

ИС микросхемы – расширители.

И С

со входами расширения имеют

С

со входами расширения имеют

Логические входы a,b,c,..z.

Входы расширения киэявляются дополнительными внешними выводамикиэтранзистора фазорасщипительного каскада логического элемента.

Микросхемы расширители имеют группу логических входов a,b,c,.. и выходы расширения киэ.

Представляет собой многоэмиттерный транзистор, выходами которого служат открытые киэ.

На выходах  и

и формируются сигналы, которые зависят

как от входных сигналов

формируются сигналы, которые зависят

как от входных сигналов так и от

так и от .

.

В данном случае

.

.

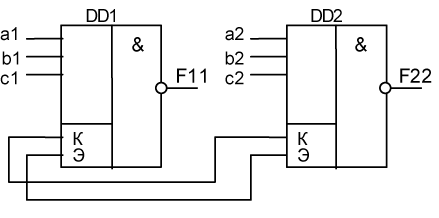

ИС с открытым коллектором.

Непосредственные соединения выхода в

разных ИС невозможно, так как если в

одном элементе будет открыт верхний, а

в другом нижний выходные транзисторы,

то с цепи потечет ток, ограниченный

только резистором  ,

что вызовет пробой транзисторов.

,

что вызовет пробой транзисторов.

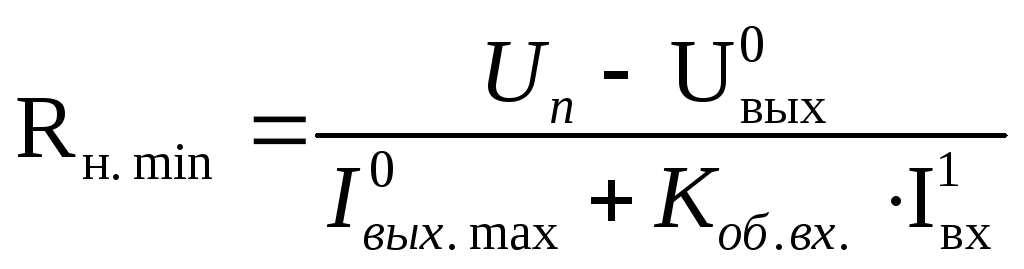

При соединении ИС параллельно, значение

резистора  выбирают из условия обеспечения

выбирают из условия обеспечения :

:

— число объединенных выходов и подключенных

входов.

— число объединенных выходов и подключенных

входов.

— ток утечки на выходе. Минимальное

сопротивление определяется из условия:

— ток утечки на выходе. Минимальное

сопротивление определяется из условия:

;

;

где  -maxдопустимый выходной

ток лог. “0” одного элемента.

-maxдопустимый выходной

ток лог. “0” одного элемента.

Логические элементы ТТЛ–технологии — КиберПедия

Логические элементы (узлы) предназначены для выполнения различных логических (функциональных) операций над дискретными сигналами при двоичном способе их представления.

Преимущественное распространение получили логические элементы потенциального типа. В них используются дискретные сигналы, нулевому значению которых соответствует уровень низкого потенциала, а единичному значению – уровень высокого потенциала (отрицательного или положительного). Связь потенциального логического элемента с предыдущим и последующими узлами в системе осуществляется непосредственно, без применения реактивных компонентов. Благодаря этому преимуществу именно потенциальные логические элементы нашли почти исключительное применение в интегральном исполнении в виде микросхем. С позиций использования логических микросхем потенциального типа и проводится далее рассмотрение логических элементов.

Логические биполярные микросхемы чаще выполняют на транзисторах типа п-р-п снапряжением питания Ек> 0. Этим объясняется, что используемые здесь сигналы имеют положительную полярность. Уровню высокого положительного потенциала («1») на выходе соответствует закрытое состояние транзистора, а уровню низкого потенциала («0») – его открытое состояние. С этой точки зрения, в частности, и следует понимать действие сигнала на входе логического элемента, имеющего непосредственную связь с другими элементами в конкретной схеме. Для упрощения уровень низкого потенциала сигнала полагаем равным нулю, а процесс перехода транзистора из одного состояния в другое – достаточно быстрым.

Логические интегральные микросхемы являются элементами, на основе которых выполняются схемы цифровой техники.

Логический элемент ИЛИ. Логический элемент ИЛИ имеет несколько входов и один общий выход. Его условное обозначение показано на рис. 6.1, а.

Логический элемент ИЛИ выполняет операцию логического сложения (дизъюнкции):

F = х1+ х2+ х3+ … + хn,

где F – функция;

х1 х2, х3,…, хn – аргументы (переменные, двоичные сигналы на входах).

Здесь функция F = 0, когда все ее аргументы равны нулю, и F = 1 при одном, нескольких или всех аргументах, равных единице.

Работу схемы двухвходового логического элемента ИЛИ иллюстрирует таблица истинности.

|

Рис. 6.1. УГО элемента ИЛИ (а), его таблица истинности

На практике возможны случаи, когда число входов используемого логического элемента ИЛИ превышает количество входных сигналов. Неиспользуемые входы заземляют. Тем самым исключается возможность прохождения помех через элемент ИЛИ от наводок по неиспользованным входам.

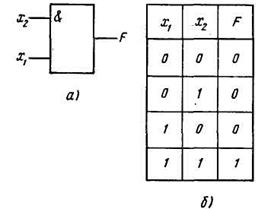

Логический элемент И. Логический элемент И также имеет несколько входов и один выход. Его условное обозначение показано на рис. 6.2, а.

Логический элемент И выполняет операцию логического умножения (конъюнкции):

F = х1• х2• х3• … • хn.

Здесь функция F = 0, когда хотя бы один из ее аргументов равен нулю, и F = 1 при всех аргументах, равных единице.

Рис. 6.2. Условное обозначение логического элемента И (а),

его таблица истинности

Работу схемы двухвходового логического элемента И иллюстрирует таблица истинности. Элемент И является схемой совпадения: сигнал «1» на выходе появляется при совпадении сигналов «1» на всех входах.

В случае применения логического элемента И, имеющего число входов, большее количества входных сигналов, неиспользуемые входы элемента соединяют с шиной «+» источника питания (подают сигнал логической «1»). Это уменьшает вероятность прохождения помех на выход элемента И от наводок по неиспользованным входам. Поведение логического элемента будет зависеть от комбинации входных сигналов.

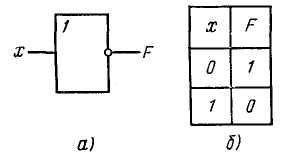

Логический элемент НЕ. Логический элемент НЕ имеет один вход и один выход. Его условное обозначение показано на рис. 6.3, а.

Рис. 6.3. Условное обозначение логического элемента НЕ (а),

его таблица истинности

Элемент НЕ выполняет операцию инверсии (отрицания), в связи, с чем его часто называют логическим инвертором. Им реализуется функция

F = х.

F = х.

Сигналу х = 0 на входе соответствует F = 1 и, наоборот, при х = 1 F = 0.

Работу схемы логического элемента НЕ иллюстрируют таблица истинности.

Логический элемент НЕ представляет собой ключевую схему на транзисторе (рис. 6.4.). Открытое состояние транзистора обеспечивается заданием тока базы, вводящего транзистор в режим насыщения.

Рис. 6.4. Схема логического элемента НЕ. Условное обозначение логического элемента ИЛИ – НЕ (а), его функциональный эквивалент (б)

и таблица истинности (в)

Логический элемент ИЛИ – НЕ. Условное обозначение логического элемента ИЛИ – НЕ показано на рис. 6.5, а. Он объединяет элементы ИЛИ и НЕ с очередностью проведения операций, показанной на рис. 6.5 , б. В связи с этим входным сигналам, равным единице, соответствует логический «0» на выходе, а при нулевых сигналах на всех входах F = 1. Для двухвходового элемента ИЛИ – НЕ соотношение иллюстрирует таблица истинности, приведенная на рис. 6.5, в.

Функциональная операция, выполняемая элементом ИЛИ – НЕ при n входах, определяется выражением

F = xl + x2+ x3 + … + хn.

F = xl + x2+ x3 + … + хn.

На рис. 6.6 приведена схема логического элемента ИЛИ – НЕ, представляющая собой последовательное соединение элемента ИЛИ на диодах и элемента НЕ. Логические схемы подобного сочетания определяют, в частности, класс элементов так называемой д и о д н о-транзисторной логики (ДТЛ).

Рис. 6.6

Логический элемент И – НЕ. Условное обозначение логического элемента И – НЕ показано на рис. 6.7, а. Ему эквивалентна структурная схема, показанная на рис 6.7, б. Логической «1» на всех информационных входах соответствует логический «0» на выходе элемента. При логическом «0» на одном из входов создается логическая «1» на выходе. Для двухвходового элемента И – НЕ сказанное отражено в таблице истинности на рис. 6.7, в. Логическая функция элемента И – НЕ при п входах отвечает выражению

F = xl • x2• x3 • … • хn.

F = xl • x2• x3 • … • хn.

Рис. 6.7.

|

На рис. 6.8 приведена другая схема элемента И–НЕ, реализованная на транзисторах Схемы такого типа образуют класс элементов так называемой транзисторно-транзисторной логики (ТТЛ).

Рис. 6.8.

Основой этого класса элементов является использование многоэмиттерного транзистора Тм. Функция многоэмиттерного транзистора сводится к замене диодной части схемы элемента И–НЕ. Подобная замена технологически выгодна, поскольку изготовление многоэмиттерного транзистора в микросхемах не намного сложнее, чем изготовление обычного транзистора, а площадь, занимаемая многоэмиттерным транзистором в кристалле полупроводника, меньше диодной части элемента И–НЕ ДТЛ. От обычного транзистора многоэмиттерный транзистор отличается наличием нескольких (например, трех) эмиттерных областей с общими для всего транзистора базовым и коллекторным слоями,

Наличие усилительного элемента – транзистора – в логических микросхемах ИЛИ–НЕ и И–НЕ классов ДТЛ и ТТЛ определяет такое их важное преимущество, как сохранение неизменного уровня напряжения, соответствующего логической «1», в процессе передачи сигнала при их последовательном соединении. В связи о этим указанные элементы, а также элемент НЕ являются базовыми в микросхемотехнике. В общем корпусе выпускаемых микросхем обычно содержится несколько элементов одного типа.

Комбинированные логические элементы. Существуют логические элементы в микросхемном исполнении, представляющие комбинацию ранее рассмотренных элементов и позволяющие осуществлять более сложные логические операции. На рис. 6.9.приведен элемент 2И–ИЛИ–НЕ.

Рис. 6.9.

Рис. 6.9.

Параметры логических элементов. К основным параметрам логических элементов (логических микросхем) относятся функциональные возможности элемента, быстродействие, потребляемая мощность и помехоустойчивость.

Функциональные возможности логического элемента определяются коэффициентом разветвления n по выходу и коэффициентом объединения m no входу. Под коэффициентом разветвления п логического элемента понимают количество входов аналогичных элементов, которое может быть подключено к его выходу, а под коэффициентом объединения т – число входов, которое может иметь элемент. Иными словами, коэффициент п характеризует нагрузочную способность микросхем.

Чем выше коэффициенты п и т, тем меньшее количество микросхем потребуется для создания конкретного устройства. Препятствием к увеличению коэффициента п является ухудшение других показателей элемента (помехоустойчивости, быстродействия) или нарушение нормального режима его работы.

Нагрузочная способность активного логического элемента существенно зависит от типа используемого в нем выходного транзисторного каскада (инвертора). Как правило, для большинства типов интегральных микросхем коэффициент п не превышает 4–10. Для увеличения нагрузочной способности к выходу элемента в случае необходимости подключают так называемый буферный усилитель с мощным многотранзисторным инвертором.

Быстродействие характеризует время реакции логического элемента на изменение сигналов на входах.

Показателем быстродействия логических микросхем является среднее время задержки прохождения сигнала через элемент: tз = (tз1 + tз2)/2.

Логические микросхемы подразделяются на сверхбыстродействующие (4.с <. 0,01 мкс), быстродействующие (4.с *в 0,01ч- 0,03 мкс), среднего быстродействия (t3.c< 0,03ч- 0,3 мкс), низкого быстродействия (4.с > 0,3 мкс).

Существенным параметром логических элементов является также потребляемая мощность от источника питания +£„• В зависимости от типа (серии) мощность, потребляемая логической микросхемой, составляет 250 мВт — 1 мкВт. Ее обычно определяют по средней мощности, потребляемой элементом в состояниях «0» и «1». Потребляемая мощность связана с быстродействием микросхем. В частности, микросхемы, потребляющие большую мощность, отличаются, как правило, и высоким быстродействием.

Снижение потребляемой мощности при сохранении высокого быстродействия является одной из важнейших задач микроэлектроники. Имеются два пути ее решения. Первый путь предполагает снижение мощности за счет уменьшения токов и напряжений питания. По такому пути идет развитие микросхем на биполярных транзисторах. Второй путь связан с созданием логических элементов, потребляющих мощность только в режиме переключения и не потребляющих ее в статических состояниях («0», «1»). Такие элементы основываются на применении дополняющих МДП-транзисторов.

Помехоустойчивость характеризует меру невосприимчивости логических элементов к изменению своих состояний под воздействием напряжения помех. Помехи, действующие на входе логической микросхемы, подразделяются на статические и импульсные (статическая и импульсная помехоустойчивость). Статическими называют помехи, напряжение которых остается постоянным в течение времени, значительно превышающего длительность переходных процессов в схеме Причиной их появления являются падения напряжения в проводниках, соединяющих микросхемы в устройстве. Статическая помехоустойчивость характеризуется максимальным напряжением помехи ип.стат, которое может быть подано на вход логического элемента, не вызывая при этом его ложного срабатывания.

Импульсные помехи обусловливаются различными наводками от окружающих работающих установок. По аналогии со статической помехоустойчивостью импульсная помехоустойчивость характеризуется напряжением импульса Uп.и. величина которого зависит от формы и длительности импульса.

К действию помех наиболее чувствительны микросхемы, имеющие низкий перепад логических уровней. На помехоустойчивость оказывают влияние вид схемы, режим работы транзисторов, напряжение источников питания и т. д.

Для уменьшения влияния помех необходимо рационально компоновать корпусы микросхем на печатных платах, осуществлять соответствующие развязки по целям напряжений питания, а в некоторых случаях экранировать цепи связи между элементами или отдельные блоки.

Элементной базой, используемой при построении ЦУ являются интегральные, логические элементы (ИЛЭ). В настоящее время выпускается широкая номенклатура ИЛЭ в составе различных серий интегральных микросхем на основе биполярных и полевых транзисторов. При построении ЦУ с заданными характеристиками выбор необходимых ИЛЭ производится в соответствии с определенным набором их параметров. Рассмотрим важнейшие из них.

Коэффициент разветвления по выходу Краз. Определяет число входов однотипных ИЛЭ, которые одновременно могут быть подключены к выходу данного логического элемента при сохранении его работоспособности в заданных условиях эксплуатации. Для различных элементов составляет от нескольких единиц до нескольких десятков.

Коэффициент объединения по входу Коб. Определяет число входных сигналов логического элемента, которые участвуют в формировании заданной логической функции.

Вид реализуемой логической функции. Используется широкий набор ИЛЭ: И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ. Перед обозначением логического элемента обычно указывается число его входов, по которым реализуется соответствующая логическая функция (т.е. коэффициент объединения по входу). В одной ИМС может быть несколько логических элементов, поэтому для сокращения обозначения состава микросхемы перед помещенным в круглые скобки наименованием элемента иногда указывают число этих элементов в одном корпусе микросхемы. Например, обозначению 4 (2И-НЕ) соответствует ИМС в составе четырех логических элементов И-НЕ с двумя входами каждый.

Статические характеристики: входная, определяющая зависимость входного тока от входного напряжения; выходная, задающая связь между выходными напряжениями и током; передаточная, которая определяет зависимость выходного напряжения от входного.

На рис. 6.10. приведена типовая передаточная характеристика ИЛЭ ТТЛ-типа. С ее помощью, например, можно оценить возможные уровни напряжения на всех входах и выходах логического элемента в том числе уровни напряжений, соответствующие состоянию логического нуля (U0) и логической единицы (U1), допустимые уровни статической помехи относительно этих уровней Uопом и U1пом, при которых еще не происходит ложного переключения логических элементов.

Временные (динамические) параметры

От них зависит быстродействие логического элемента. Чаще всего оценивается время перехода элемента из состояния единицы в состояние нуля t1,0 и перехода в обратное состояние t0,1 (рис. 6.11.).

Рис. 6.10.

Указанные временные интервалы измеряются на уровнях 0,1-0,9 от установившихся значений в цепочке из однотипных элементов. Другим важнейшим параметром, определяющим быстродействие, является время задержки распространения сигнала при включении t1,0здр. и выключении t0,1здр. логического элемента.

Рис. 6.11.

Измеряется на выходе по отношению к входу на уровнях 0,5 от установившихся значений. Во многих случаях удобно пользоваться средним временем задержки распространения сигнала tздр.ср., оцениваемым полусуммой t0,1здр. и t1,0здр.

Для построения ЦУ наиболее широкое применение находят ИДЭ на базе ТТЛ, ТТЛШ, ЭСЛ и КМОП-технологий.

| Технология ИЛЭ | Выполняемые функции | Краз | Коб | U, U, В | Tздр.ср. ИС |

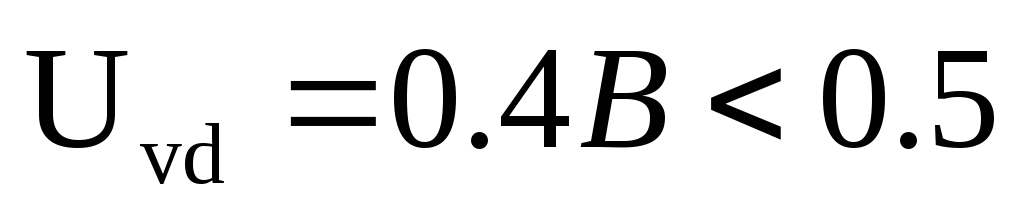

| ТТЛ ТТЛШ ЭСЛ КМОП | И-НЕ, И-ИЛИ-НЕ, И, НЕ,ИЛИ И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ, И, НЕ ИЛИ-НЕ, ИЛИ,И ИЛИ-НЕ, И-НЕ, И-ИЛИ | 8-30 8-20 | 2-8 2-8 2-5 2-4 | £0,4 ³2,4 £0,5 ³2,7 -1,6 -1,0 0 Uп | 18-32 3-5 60-1200 |

Уровни напряжения логических схем «0» и «1» и согласование транзисторно-транзисторной логики ТТЛ и КМОП логики с помощью обратной связи, резисторов, транзистора

Логические элементы оперируют сигналами двух типов: «высокий логический уровень» (1) и «низкий логический уровень» (0), которые характеризуются различным уровнем напряжения: полное напряжение питания принимается в качестве уровня «логической единицы», а нулевое напряжение — в качестве уровня «логического нуля».

В идеальном случае все сигналы логических элементов существовали бы в виде этих двух предельных уровней напряжения, и никогда бы от них не отклонялись (например, ниже полного напряжения для «высокого уровня», или выше нуля для «низкого уровня».) Однако в реальности уровни напряжения цифровых сигналов практически никогда не достигают этих идеальных величин.

Вследствие наличия паразитных падений напряжения в схемах на транзисторах, наводок, длины линии передачи сигнала и т.д.. Поэтому для логических схем интерпретируют сигналы как логическую единицу или логический нуль, даже в тех случаях, когда напряжение сигналов лежит в диапазоне между полным напряжением питания и нулём, то есть номинально не соответствует ни тому ни другом показателю.

Номинальное напряжение питания для логических радиоэлементов (микросхем) и номинальное значение логического 0 и логической 1

Элементы ТТЛ работают при номинальном напряжении питания 5 вольт, +/- 0,25 вольт. В идеале, сигнал высокого логического уровня должен быть равен ровно 5,00 В, а сигнал низкого уровня — ровно 0,00 вольт. Однако в реальных элементах ТТЛ не могут быть обеспечены подобные точные уровни напряжения, поэтому они могут принимать сигналы высокого и низкого уровней даже при значительном отклонении напряжения от идеальных величин. «Приемлемые» напряжения входного сигнала лежат в диапазоне от 0 до 0,8 вольт для низкого логического уровня, и от 2 до 5 вольт для высокого логического уровня. «Приемлемые» напряжения выходного сигнала (уровни напряжения, гарантируемые производителем элемента в указанных вариантах нагрузки) лежат в диапазоне от 0 до 0,5 вольт для низкого логического уровня, и от 2,7 до 5 вольт для высокого логического уровня.

Если бы на вход элемента ТТЛ поступил сигнал напряжения в диапазоне от 0,8 до 2 вольт, то мы не получили бы гарантированной реакции схемы. Подобный сигнал будет рассматриваться как неопределённый, и в этом случае ни один производитель не даст гарантии того, к какому логическому уровню отнесёт схема подобный сигнал.

Как вы видите, диапазон допусков по уровням выходного сигнала меньше, чем в случае для входного сигнала. Это необходимо для обеспечения того, что цифровой сигнал, поступающий с выхода одного элемента логики на вход другого элемента, воспринимался бы таковым же, но с учетом условий потери и воздействия на него. Разница допусков между входным и выходным сигналами называется запасом схемы по помехоустойчивости. Для ТТЛ-схем, запас помехоустойчивости для низкого логического уровня представляет разность между 0,8 В и 0,5 В (т.е. 0,3 В), в то время как запас помехоустойчивости для высокого уровня равен 0,7 В (2,7 В — 2,0 В). Проще говоря, запас помехоустойчивости есть некий запас на паразитное или шумовое напряжение, которое может быть наложено на исходный сигнал, прежде чем принимающая схема может неверно его проинтерпретировать.

Спецификации входных и выходных сигналов схем КМОП логических элементов совершенно отличны от уровней напряжения, используемых для ТТЛ-элементов. Для КМОП-элементов, работающих при напряжении питания 5 вольт, приемлемые напряжения входного сигнала лежат в диапазоне от 0 до 1,5 вольт для низкого логического уровня, и от 3,5 до 5 вольт для высокого логического уровня. «Приемлемые» напряжения выходного сигнала (уровни напряжения, гарантируемые производителем элемента при указанном варианте нагрузки) лежат в диапазоне от 0 до 0,05 вольт для низкого логического уровня, и от 4,95 до 5 вольт для высокого логического уровня.

Представленные значения дают понять, что запас помехоустойчивости КМОП логических элементов гораздо больше аналогичного показателя ТТЛ-элементов: 1,45 вольт как для логического нуля, так и для логической единицы, против максимального запаса в 0,7 В в случае ТТЛ. Другими словами, КМОП-схемы могут выдержать более чем вдвое высокий наложенный шум на входе без ошибок интерпретации сигнала как логического нуля или единицы.

Запас помехоустойчивости КМОП логических схем становится ещё больше при более высоких рабочих напряжениях. В отличие от элементов ТТЛ, напряжение питания которых не превышает 5 вольт, напряжение питания КМОП-схем может достигать 15 (а в некоторых случаях и 18) вольт. Ниже показаны приемлемые уровни логических нуля и единицы, для выхода и входа КМОП-ИС, работающих при напряжении питания 10 и 15 вольт соответственно:

Запас помехоустойчивости может быть выше того, что показано на предыдущем рисунке. На рисунке показан худший из возможных вариантов поведения сигнала на основании спецификаций производителя. На практике логическая схема может выдержать сигналы высокого логического уровня со значительно меньшим напряжением и сигналы низкого логического уровня с гораздо большим напряжением чем указано.

И наоборот, исключительно малые показанные запасы помехоустойчивости — гарантирующие выходное состояние сигналов высокого и низкого логических уровней с точностью до 0,05 вольта напряжения питания — практически реальны. Такие «добротные» уровни выходного напряжения будут доступны только при минимальной нагрузке. При значительном втекающем или вытекающем токе схемы выходное напряжение не будет поддерживаться на этих оптимальных уровнях, что обусловлено наличием внутреннего сопротивления каналов выходных МОП-транзисторов логических элементов.

Помехоустойчивость при единичных (разовых) скачках напряжения, появления помехи (наводки)

В пределах «неопределённого» диапазона для любого входа логического элемента, будет иметься точка разделения актуального сигнала низкого уровня от диапазона действительного входного сигнала высокого уровня. То есть, где-то между наименьшим напряжением сигнала высокого логического уровня и наибольшим напряжением сигнала низкого логического уровня гарантированного производителем, существует порог напряжения, при котором логическая схема будет менять интерпретацию сигнала с высокого на низкий и наоборот. В случае большей части логических схем, это напряжение соответствует одной определённой точке:

При наличии шумового напряжения переменного тока, наложенного на входной сигнал постоянного тока единственная точка, в которой схема переменит интерпретацию логического уровня будет обуславливать ошибочный сигнал на выходе.

Подобная проблема характерна также для аналоговых ОУ-компараторов напряжения. В случае одиночной пороговой точки смены логического уровня наличие значительного шума может привести к неверной интерпретации логического уровня на выходе.

Эту проблему можно решить путём введения в цепь усилителя положительной обратной связи. В случае операционного усилителя необходимо соединить выход с неинвертирующим входом через резистор. Схемы подобного типа называются триггерами Шмитта. Триггеры Шмитта идентифицируют логический уровень сигнала согласно двум пороговым уровням: при нарастающем напряжении (VT+), и при падающем напряжении (VT-):

На схемах триггеры Шмитта изображаются с символом «гистерезиса». Гистерезис, вызванный положительной обратной связью в схеме логического элемента, придаёт схеме дополнительную помехоустойчивость. Триггеры Шмитта часто используются в схемах с высокой вероятностью шума на входе, а также в тех случаях когда ошибочно интерпретированный сигнал на выходе приведёт к некорректной работе системы в целом.

Различные требования по уровням напряжения ТТЛ- и КМОП-элементов создают определённые проблемы при использовании в одной схеме элементов двух типов. Хотя работа КМОП логических элементов может осуществляться при том же напряжении питания 5,00 В, которое необходимо для элементов ТТЛ, выходные уровни напряжения ТТЛ логики несовместимы с входными требованиями по напряжению для КМОП-схем.

Возьмём к примеру ТТЛ-элемент НЕ-И, сигнал с выхода которого подаётся на вход КМОП-инвертора. Питание обоих элементов составляет 5,00 В (Vcc). Если с выхода элемента ТТЛ приходит сигнал логического нуля (т.е. между 0 и 0,5 В), то он будет верно интерпретирован на входе КМОП-схемы как сигнал низкого логического уровня (т.е. сигнал между 0 и 1,5 В):

Однако, если с выхода элемента ТТЛ приходит сигнал логической единицы (т.е. между 5 и 2,7 В), то он может быть неверно интерпретирован на входе КМОП-схемы как сигнал высокого логического уровня (т.е. ожидается сигнал между 5 и 3,5 В):

Такое несоответствие может привести к тому, что «правильный» сигнал высокого уровня на выходе ТТЛ- элемента (правильный с точки зрения стандартов ТТЛ) будет лежат в «неопределённом» диапазоне входа КМОП-схемы, и быть неверно воспринят как сигнал логического нуля принимающим элементом. Простым решением этой проблемы может стать повышение сигнала логической единицы элемента ТТЛ с помощью нагрузочного повышающего резистора:

Однако потребуется гораздо более серьёзная переделка схемы, если питание КМОП-схемы выше 5 вольт:

Проблемы не возникнет в случае логического нуля, однако всё обстоит совершенно иначе в случае сигнала высокого логического уровня с выхода элемента ТТЛ. Диапазон выходного напряжения 2,7-5 В с выхода элемента ТТЛ совершенно не соответствует приемлемому диапазону 7-10 В КМОП логической схемы. Если мы используем ТТЛ-схемы с открытым коллектором, то нагрузочный резистор, включённый в шину питания Vdd 10 вольт, поднимет сигнал высокого логического уровня до полного напряжения питания КМОП логической схемы. Поскольку в схеме с открытым коллектором в наличии только втекающий ток, напряжение логической единицы полностью определяется тем напряжением питания, к которому подключён повышающий резистор, что помогает решить проблему несоответствия уровней напряжения.

Благодаря прекрасным характеристикам выходного напряжения КМОП схем, проблем при подключения ТТЛ элемента к выходу КМОП схемы обычно не возникает. Единственной серьёзной проблемой может стать токовая нагрузка, поскольку КМОП-схема должна обеспечивать втекающий ток на каждый вход элемента ТТЛ в случае логического нуля.

Если КМОП-схема питается от источника напряжения выше 5 вольт (Vcc), то возникнет проблема. Напряжение логической единицы КМОП-схемы выше 5 вольт не будет находиться в диапазоне допустимых входные параметров элемента ТТЛ. Решением этой проблемы может стать инвертор с «открытым коллектором» на дискретном NPN-транзисторе, используемом для соединения двух логических схем:

Повышающий резистор Rpullup используется опционально, поскольку входы элементов ТТЛ принимают высокий логический уровень, когда находятся в плавающем состоянии, что и произойдёт, когда выход КМОП-схемы будет низким, а транзистор будет находиться в состоянии отсечки. Конечно, важным последствием такого решения является логическая инверсия, создаваемая транзистором: когда на выходе КМОП-схемы будет сигнал логического нуля, элемент ТТЛ будет «видеть» логическую единицу и наоборот. Однако, если принимать эту инверсию во внимание, то корректная работа схемы не будет нарушена.

Логические элементы ТТЛ цифровых микросхем

Рис. 1. Схема базового логического элемента ТТЛ 2И-НЕ

Рис. 2. Передаточная характеристика элемента ТТЛ 2И-НЕ

Схема базового элемента цифровых микросхем ТТЛ — элемента 2И-НЕ — приведена на рис. 1. Он состоит из входного многоэмиттерного транзистора VT1, парафазного усилительного каскада на транзисторе VT2 и двухтактного выходного каскада на транзисторах V73, VT4. Последние два каскада на транзисторах по своему построению напоминают фазоинверсный и выходной каскады бестрансформаторного усилителя звуковой частоты (34).

Передаточная характеристика такого логического элемента изображена на рис. 2. Если входное напряжение находится в пределах 0… 0,5 В, то эмиттер-ный р-п переход транзистора VT1 открыт, но напряжение на его базе недостаточно для открывания коллекторного перехода этого транзистора и эмит-терных переходов транзисторов VT2, VT4. Поэтому транзисторы VT2 и VT4 закрыты, a ѴТЗ — открыт напряжением, поступающим на его базу через резистор R2. Диод VD3 открыт и на выходе элемента напряжение составляет примерно 3… 4 В (рис. 2, точка а). Увеличение входного напряжения приводит к постепенному открыванию транзистора ѴТ2, уменьшению напряжения на базе транзистора ѴТЗ и его постепенному плавному закрыванию (рис. 2, участок б—в). Дальнейшее увеличение входного напряжения приводит к еще большему открыванию транзистора ѴТ2, увеличению напряжения на резисторе R3 и открыванию эмиттерного перехода транзистора VT4. Это приводит к тому, что эмиттерный переход транзистора VT4 шунтирует резистор R3, транзистор VT2 начинает резко открываться, а напряжение на выходе элемента уменьшаться. В этот момент (рис. 2, участок в—г) все транзисторы открыты и находятся в активном режиме — это участок характеристики элемента, который можно использовать для обработки аналоговых сигналов. Этот режим характеризуется высокой крутизной передаточной характеристики и максимальной потребляемой от источника питания мощностью, так как через открытые транзисторы ѴТЗ и ѴТ4 протекает сквозной ток, ограничиваемый резистором R4.

Если продолжать увеличивать входное напряжение, то транзисторы ѴТ2 и ѴТ4 перейдут в режим насыщения (рис. 2, участок г—д), что приведет к более плавному уменьшению выходного напряжения. Если же входное напряжение окажется выше 2…2,5 В, то транзистор ѴТЗ закроется и значение выходного напряжения не превысит напряжения насыщения транзистора ѴТ4 (0,4 В),

Передаточная характеристика элемента ТТЛ температурно зависима: при повышении температуры окружающей среды до +125 °С она сдвигается влево примерно на 0,3 В, а при уменьшении до —60 °С — вправо на ту же величину. Протяженность линейного участка по выходу составляет 1,5… 1,8 В.

Литература: И. А. Нечаев, Массовая Радио Библиотека (МРБ), Выпуск 1172, 1992 год.

Логические элементы ТТЛ–технологии

Логические элементы (узлы) предназначены для выполнения различных логических (функциональных) операций над дискретными сигналами при двоичном способе их представления.

Преимущественное распространение получили логические элементы потенциального типа. В них используются дискретные сигналы, нулевому значению которых соответствует уровень низкого потенциала, а единичному значению – уровень высокого потенциала (отрицательного или положительного). Связь потенциального логического элемента с предыдущим и последующими узлами в системе осуществляется непосредственно, без применения реактивных компонентов. Благодаря этому преимуществу именно потенциальные логические элементы нашли почти исключительное применение в интегральном исполнении в виде микросхем. С позиций использования логических микросхем потенциального типа и проводится далее рассмотрение логических элементов.

Логические биполярные микросхемы чаще выполняют на транзисторах типа п-р-п снапряжением питания Ек> 0. Этим объясняется, что используемые здесь сигналы имеют положительную полярность. Уровню высокого положительного потенциала («1») на выходе соответствует закрытое состояние транзистора, а уровню низкого потенциала («0») – его открытое состояние. С этой точки зрения, в частности, и следует понимать действие сигнала на входе логического элемента, имеющего непосредственную связь с другими элементами в конкретной схеме. Для упрощения уровень низкого потенциала сигнала полагаем равным нулю, а процесс перехода транзистора из одного состояния в другое – достаточно быстрым.

Логические интегральные микросхемы являются элементами, на основе которых выполняются схемы цифровой техники.

Логический элемент ИЛИ. Логический элемент ИЛИ имеет несколько входов и один общий выход. Его условное обозначение показано на рис. 6.1, а.

Логический элемент ИЛИ выполняет операцию логического сложения (дизъюнкции):

F = х1+ х2+ х3+ … + хn,

где F – функция;

х1 х2, х3,…, хn – аргументы (переменные, двоичные сигналы на входах).

Здесь функция F = 0, когда все ее аргументы равны нулю, и F = 1 при одном, нескольких или всех аргументах, равных единице.

Работу схемы двухвходового логического элемента ИЛИ иллюстрирует таблица истинности.

|

Рис. 6.1. УГО элемента ИЛИ (а), его таблица истинности

На практике возможны случаи, когда число входов используемого логического элемента ИЛИ превышает количество входных сигналов. Неиспользуемые входы заземляют. Тем самым исключается возможность прохождения помех через элемент ИЛИ от наводок по неиспользованным входам.

Логический элемент И. Логический элемент И также имеет несколько входов и один выход. Его условное обозначение показано на рис. 6.2, а.

Логический элемент И выполняет операцию логического умножения (конъюнкции):

F = х1• х2• х3• … • хn.

Здесь функция F = 0, когда хотя бы один из ее аргументов равен нулю, и F = 1 при всех аргументах, равных единице.

Рис. 6.2. Условное обозначение логического элемента И (а),

его таблица истинности

Работу схемы двухвходового логического элемента И иллюстрирует таблица истинности. Элемент И является схемой совпадения: сигнал «1» на выходе появляется при совпадении сигналов «1» на всех входах.

В случае применения логического элемента И, имеющего число входов, большее количества входных сигналов, неиспользуемые входы элемента соединяют с шиной «+» источника питания (подают сигнал логической «1»). Это уменьшает вероятность прохождения помех на выход элемента И от наводок по неиспользованным входам. Поведение логического элемента будет зависеть от комбинации входных сигналов.

Логический элемент НЕ. Логический элемент НЕ имеет один вход и один выход. Его условное обозначение показано на рис. 6.3, а.

Рис. 6.3. Условное обозначение логического элемента НЕ (а),

его таблица истинности

Элемент НЕ выполняет операцию инверсии (отрицания), в связи, с чем его часто называют логическим инвертором. Им реализуется функция

F = х.

F = х.

Сигналу х = 0 на входе соответствует F = 1 и, наоборот, при х = 1 F = 0.

Работу схемы логического элемента НЕ иллюстрируют таблица истинности.

Логический элемент НЕ представляет собой ключевую схему на транзисторе (рис. 6.4.). Открытое состояние транзистора обеспечивается заданием тока базы, вводящего транзистор в режим насыщения.

Рис. 6.4. Схема логического элемента НЕ. Условное обозначение логического элемента ИЛИ – НЕ (а), его функциональный эквивалент (б)

и таблица истинности (в)

Логический элемент ИЛИ – НЕ. Условное обозначение логического элемента ИЛИ – НЕ показано на рис. 6.5, а. Он объединяет элементы ИЛИ и НЕ с очередностью проведения операций, показанной на рис. 6.5 , б. В связи с этим входным сигналам, равным единице, соответствует логический «0» на выходе, а при нулевых сигналах на всех входах F = 1. Для двухвходового элемента ИЛИ – НЕ соотношение иллюстрирует таблица истинности, приведенная на рис. 6.5, в.

Функциональная операция, выполняемая элементом ИЛИ – НЕ при n входах, определяется выражением

F = xl + x2+ x3 + … + хn.

F = xl + x2+ x3 + … + хn.

На рис. 6.6 приведена схема логического элемента ИЛИ – НЕ, представляющая собой последовательное соединение элемента ИЛИ на диодах и элемента НЕ. Логические схемы подобного сочетания определяют, в частности, класс элементов так называемой д и о д н о-транзисторной логики (ДТЛ).

Рис. 6.6

Логический элемент И – НЕ. Условное обозначение логического элемента И – НЕ показано на рис. 6.7, а. Ему эквивалентна структурная схема, показанная на рис 6.7, б. Логической «1» на всех информационных входах соответствует логический «0» на выходе элемента. При логическом «0» на одном из входов создается логическая «1» на выходе. Для двухвходового элемента И – НЕ сказанное отражено в таблице истинности на рис. 6.7, в. Логическая функция элемента И – НЕ при п входах отвечает выражению

F = xl • x2• x3 • … • хn.

F = xl • x2• x3 • … • хn.

Рис. 6.7.

|

На рис. 6.8 приведена другая схема элемента И–НЕ, реализованная на транзисторах Схемы такого типа образуют класс элементов так называемой транзисторно-транзисторной логики (ТТЛ).

Рис. 6.8.

Основой этого класса элементов является использование многоэмиттерного транзистора Тм. Функция многоэмиттерного транзистора сводится к замене диодной части схемы элемента И–НЕ. Подобная замена технологически выгодна, поскольку изготовление многоэмиттерного транзистора в микросхемах не намного сложнее, чем изготовление обычного транзистора, а площадь, занимаемая многоэмиттерным транзистором в кристалле полупроводника, меньше диодной части элемента И–НЕ ДТЛ. От обычного транзистора многоэмиттерный транзистор отличается наличием нескольких (например, трех) эмиттерных областей с общими для всего транзистора базовым и коллекторным слоями,

Наличие усилительного элемента – транзистора – в логических микросхемах ИЛИ–НЕ и И–НЕ классов ДТЛ и ТТЛ определяет такое их важное преимущество, как сохранение неизменного уровня напряжения, соответствующего логической «1», в процессе передачи сигнала при их последовательном соединении. В связи о этим указанные элементы, а также элемент НЕ являются базовыми в микросхемотехнике. В общем корпусе выпускаемых микросхем обычно содержится несколько элементов одного типа.

Комбинированные логические элементы. Существуют логические элементы в микросхемном исполнении, представляющие комбинацию ранее рассмотренных элементов и позволяющие осуществлять более сложные логические операции. На рис. 6.9.приведен элемент 2И–ИЛИ–НЕ.

Рис. 6.9.

Рис. 6.9.

Параметры логических элементов. К основным параметрам логических элементов (логических микросхем) относятся функциональные возможности элемента, быстродействие, потребляемая мощность и помехоустойчивость.

Функциональные возможности логического элемента определяются коэффициентом разветвления n по выходу и коэффициентом объединения m no входу. Под коэффициентом разветвления п логического элемента понимают количество входов аналогичных элементов, которое может быть подключено к его выходу, а под коэффициентом объединения т – число входов, которое может иметь элемент. Иными словами, коэффициент п характеризует нагрузочную способность микросхем.

Чем выше коэффициенты п и т, тем меньшее количество микросхем потребуется для создания конкретного устройства. Препятствием к увеличению коэффициента п является ухудшение других показателей элемента (помехоустойчивости, быстродействия) или нарушение нормального режима его работы.

Нагрузочная способность активного логического элемента существенно зависит от типа используемого в нем выходного транзисторного каскада (инвертора). Как правило, для большинства типов интегральных микросхем коэффициент п не превышает 4–10. Для увеличения нагрузочной способности к выходу элемента в случае необходимости подключают так называемый буферный усилитель с мощным многотранзисторным инвертором.

Быстродействие характеризует время реакции логического элемента на изменение сигналов на входах.

Показателем быстродействия логических микросхем является среднее время задержки прохождения сигнала через элемент: tз = (tз1 + tз2)/2.

Логические микросхемы подразделяются на сверхбыстродействующие (4.с <. 0,01 мкс), быстродействующие (4.с *в 0,01ч- 0,03 мкс), среднего быстродействия (t3.c< 0,03ч- 0,3 мкс), низкого быстродействия (4.с > 0,3 мкс).

Существенным параметром логических элементов является также потребляемая мощность от источника питания +£„• В зависимости от типа (серии) мощность, потребляемая логической микросхемой, составляет 250 мВт — 1 мкВт. Ее обычно определяют по средней мощности, потребляемой элементом в состояниях «0» и «1». Потребляемая мощность связана с быстродействием микросхем. В частности, микросхемы, потребляющие большую мощность, отличаются, как правило, и высоким быстродействием.

Снижение потребляемой мощности при сохранении высокого быстродействия является одной из важнейших задач микроэлектроники. Имеются два пути ее решения. Первый путь предполагает снижение мощности за счет уменьшения токов и напряжений питания. По такому пути идет развитие микросхем на биполярных транзисторах. Второй путь связан с созданием логических элементов, потребляющих мощность только в режиме переключения и не потребляющих ее в статических состояниях («0», «1»). Такие элементы основываются на применении дополняющих МДП-транзисторов.

Помехоустойчивость характеризует меру невосприимчивости логических элементов к изменению своих состояний под воздействием напряжения помех. Помехи, действующие на входе логической микросхемы, подразделяются на статические и импульсные (статическая и импульсная помехоустойчивость). Статическими называют помехи, напряжение которых остается постоянным в течение времени, значительно превышающего длительность переходных процессов в схеме Причиной их появления являются падения напряжения в проводниках, соединяющих микросхемы в устройстве. Статическая помехоустойчивость характеризуется максимальным напряжением помехи ип.стат, которое может быть подано на вход логического элемента, не вызывая при этом его ложного срабатывания.

Импульсные помехи обусловливаются различными наводками от окружающих работающих установок. По аналогии со статической помехоустойчивостью импульсная помехоустойчивость характеризуется напряжением импульса Uп.и. величина которого зависит от формы и длительности импульса.

К действию помех наиболее чувствительны микросхемы, имеющие низкий перепад логических уровней. На помехоустойчивость оказывают влияние вид схемы, режим работы транзисторов, напряжение источников питания и т. д.

Для уменьшения влияния помех необходимо рационально компоновать корпусы микросхем на печатных платах, осуществлять соответствующие развязки по целям напряжений питания, а в некоторых случаях экранировать цепи связи между элементами или отдельные блоки.

Элементной базой, используемой при построении ЦУ являются интегральные, логические элементы (ИЛЭ). В настоящее время выпускается широкая номенклатура ИЛЭ в составе различных серий интегральных микросхем на основе биполярных и полевых транзисторов. При построении ЦУ с заданными характеристиками выбор необходимых ИЛЭ производится в соответствии с определенным набором их параметров. Рассмотрим важнейшие из них.

Коэффициент разветвления по выходу Краз. Определяет число входов однотипных ИЛЭ, которые одновременно могут быть подключены к выходу данного логического элемента при сохранении его работоспособности в заданных условиях эксплуатации. Для различных элементов составляет от нескольких единиц до нескольких десятков.

Коэффициент объединения по входу Коб. Определяет число входных сигналов логического элемента, которые участвуют в формировании заданной логической функции.

Вид реализуемой логической функции. Используется широкий набор ИЛЭ: И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ. Перед обозначением логического элемента обычно указывается число его входов, по которым реализуется соответствующая логическая функция (т.е. коэффициент объединения по входу). В одной ИМС может быть несколько логических элементов, поэтому для сокращения обозначения состава микросхемы перед помещенным в круглые скобки наименованием элемента иногда указывают число этих элементов в одном корпусе микросхемы. Например, обозначению 4 (2И-НЕ) соответствует ИМС в составе четырех логических элементов И-НЕ с двумя входами каждый.

Статические характеристики: входная, определяющая зависимость входного тока от входного напряжения; выходная, задающая связь между выходными напряжениями и током; передаточная, которая определяет зависимость выходного напряжения от входного.

На рис. 6.10. приведена типовая передаточная характеристика ИЛЭ ТТЛ-типа. С ее помощью, например, можно оценить возможные уровни напряжения на всех входах и выходах логического элемента в том числе уровни напряжений, соответствующие состоянию логического нуля (U0) и логической единицы (U1), допустимые уровни статической помехи относительно этих уровней Uопом и U1пом, при которых еще не происходит ложного переключения логических элементов.

Временные (динамические) параметры

От них зависит быстродействие логического элемента. Чаще всего оценивается время перехода элемента из состояния единицы в состояние нуля t1,0 и перехода в обратное состояние t0,1 (рис. 6.11.).

Рис. 6.10.

Указанные временные интервалы измеряются на уровнях 0,1-0,9 от установившихся значений в цепочке из однотипных элементов. Другим важнейшим параметром, определяющим быстродействие, является время задержки распространения сигнала при включении t1,0здр. и выключении t0,1здр. логического элемента.

Рис. 6.11.

Измеряется на выходе по отношению к входу на уровнях 0,5 от установившихся значений. Во многих случаях удобно пользоваться средним временем задержки распространения сигнала tздр.ср., оцениваемым полусуммой t0,1здр. и t1,0здр.

Для построения ЦУ наиболее широкое применение находят ИДЭ на базе ТТЛ, ТТЛШ, ЭСЛ и КМОП-технологий.

| Технология ИЛЭ | Выполняемые функции | Краз | Коб | U, U, В | Tздр.ср. ИС |

| ТТЛ ТТЛШ ЭСЛ КМОП | И-НЕ, И-ИЛИ-НЕ, И, НЕ,ИЛИ И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ, И, НЕ ИЛИ-НЕ, ИЛИ,И ИЛИ-НЕ, И-НЕ, И-ИЛИ | 8-30 8-20 | 2-8 2-8 2-5 2-4 | £0,4 ³2,4 £0,5 ³2,7 -1,6 -1,0 0 Uп | 18-32 3-5 60-1200 |

Дата добавления: 2017-05-02; просмотров: 2721;

Похожие статьи:

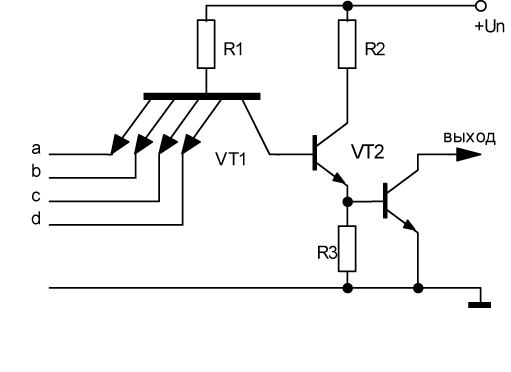

5.10 Ттл логический элемент или-не

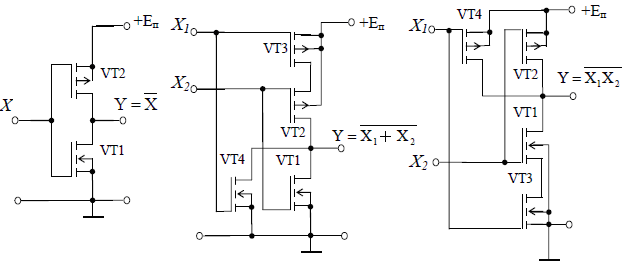

На рис.5.10 приведена схема логического элемента типа 2ИЛИ-НЕ. Основу такого логического элемента составляет схема инвертора, в которую дополнительно введен еще один входной узел на транзисторе VT3 и транзистор VT4. Эту схему может представить в виде двух инверторов, работающих на один выходной инвертор. В данной схеме выходной инвертор управляется либо по первому входу Х1, либо по второму Х2. Выходной сигнал в этой схеме принимает высокий уровень только в том случае, если на оба входа поданы низкие уровни. Во всех остальных случаях на выходе будет низкий уровень. При замене обычных транзисторов VT1 и VT3 на многоэмиттерные можно реализовать логическую функцию типа И-И-ИЛИ-НЕ.

5.1.9 Схемотехника кмоп логических элементов

а) б) в)

Рис. 5.11 КМОП логические элементы

Базовая схема КМОП – инвертора показана на рис.5.11, а. Схема включает два МОП – транзистора с индуцированным каналом с разной проводимостью каналов и объединенными затворами.

Если на вход подать высокий уровень сигнала (Х = 1), то напряжение на затворе транзистора VT1 превысит пороговое, а на затворе VT2 будет ниже порогового. Поэтому транзистор VT1 откроется и выход схемы окажется подключен к шине “земля” через открытый транзистор VT1, а транзистор VT2 будет заперт. В результате на выходе будет низкий уровень напряжения, т.е. Y = 0.

При подаче низкого входного уровня сигнала (Х = 0), состояние транзисторов меняется на противоположное. Теперь выход инвертора окажется подключенным через открытый транзистор VT2 к шине питания и на выходе будет высокий уровень напряжения, т.е. Y = 1.

Благодаря применению полевых транзисторов с изолированным затвором для управления КМОП – ИС требуются очень низкие мощности сигналов, так ток затвора не превышает 1 нА. Максимальное потребление мощности происходит при переключении логического элемента, что иллюстрируется рис. 5.12.

а) б)

Рис. 5.12 а) – переходные характеристики транзисторов;

б) – временные диаграммы переключения

В момент переключения оба транзистора оказываются приоткрытыми и сквозной ток IПОТР ограничивается видом переходных характеристик. Сквозной ток кратковременный но, с ростом частоты переключения вызванные им потери могут оказаться основными.

Рассмотренная схема инвертора является основой для построения логических элементов других типов. На рис. 5.11, б приведена схема, реализующая функцию 2ИЛИ-НЕ. В схеме ИЛИ-НЕ инвертор на транзисторах VT1 и VT2 подключается к шине питания через транзистор VT3. При подаче на оба входа низкого уровня транзисторы VT1 и VT4 запираются, а транзисторы VT2 и VT3 отпираются. Следовательно, на выходе появится высокий уровень напряжения. Если на один или оба входа подают напряжение высокого уровня, транзисторы VT2 и VT3 запираются, а один или оба нижних транзистора открываются, и на выходе будет низкий уровень напряжения.

В схеме И-НЕ (рис. 5.11, в)инвертор на транзисторах VT1 и VT2 подключается к шине “земля” через транзистор VT3, а VT4 подключается параллельно верхнему транзистору инвертора. При подаче на один или оба входа напряжения низкого уровня один из нижних транзисторов будет всегда заперт, а один из верхних открыт и на выходе будет высокий уровень напряжения. Для получения низкого уровня напряжения на выходе необходимо, чтобы оба нижних транзистора были открыты, а оба верхних транзистора – закрыты. Такое состояние возможно только в том случае, если на оба входа одновременно подается высокий уровень напряжения.

В КМОП–сериях также имеются логические элементы с открытым стоком и с тремя выходными состояниями.

Принцип действия ЭСЛ логических элементов основан на переключении тока, которое реализуется с помощью дифференциального усилительного каскада. Логические элементы отличаются повышенным быстродействием, но малым напряжением перепада между логическим уровнем нуля и единицы. Обладая низкой помехозащищенностью, в устройствах автоматики ЭСЛ логика не нашла применения.

на

на (мощность

(мощность

.

.