Как подключить заголовки портов LPT и COM на материнской плате?

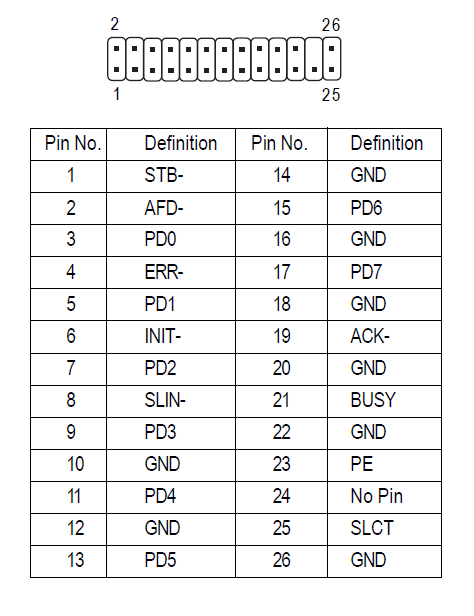

IDC заголовки и DB разъемы имеют контакты, пронумерованные в разном порядке.

The IDC заголовки нумеруются, как на диаграммах: сначала столбец, затем строка.

DB разъемы нумеруются первой строки, затем столбца.

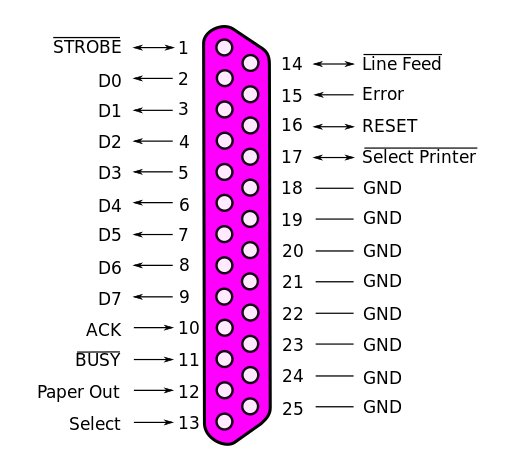

вот распиновка параллельного порта согласно Википедии…

используется нумерация контактов разъема DB25.

заголовок для параллельного порта LPT намеренно «неправильно пронумерован» (по сравнению с назначениями DB25), так что можно использовать разъемы IDC на обоих концах с плоским ленточным кабелем.

Это-предпочтительный макет для заголовка LPT к разъему IDC DB25.

IEEE 1284 предназначен для разъемов Centronics. IBM PC в 1980-х сократил количество контактов с 36 до 25, чтобы использовать оболочку DB25.

штыри DB25 организованы в два ряда, один ряд для первых 13 контактов, 1: 13, и второй ряд для последних 12 контактов, 14: 25:

1 2 3 4 5 6 7 8 9 10 11 12 13

14 15 16 17 18 19 20 21 22 23 24 25

когда DB25 IDC разъем использован, номера Штыря приказан на ленточном кабеле как:

1, 14, 2, 15, 3, 16, 4, 17, 5, 18, 6, 19, 7, 20, 8, 21, 9, 22, 10, 23, 11, 24, 12, 25, 13

основанный на этом заказе сигналов для DB25, после этого отображение штырей IDC к штырям DB25 является следующим:

IDC pin 1 = signal of DB25 pin 1

IDC pin 2 = signal of DB25 pin 14

IDC pin 3 = signal of DB25 pin 2

IDC pin 4 = signal of DB25 pin 15

IDC pin 5 = signal of DB25 pin 3

IDC pin 6 = signal of DB25 pin 16

...

это отображение является то, что вы воспринимаете как» перепутались » pin назначения (на конце заголовка), но совершенно логично, чтобы доставить сигналы к DB25.

эта таблица из руководства для заголовка LPT нарисована запутанным образом, потому что она использует макет DB25 вместо макета IDC. Один столбец для строки нечетных выводов и другой столбец для строки четных выводов поместили бы сигналы в порядке, который напоминает разъем DB25.

26-контактный разъем IDC для заголовка LPT:

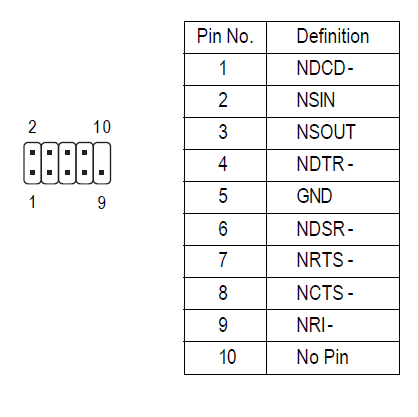

заголовок последовательного COM-порта материнская плата пронумерована ОДН-для-ОДН к серийному разъему DB9.

Но контакты разъема IDC организованы в два ряда: один ряд для четных контактов и второй ряд для нечетных контактов:

2 4 6 8 -

1 3 5 7 9

на ленточном кабеле номера Штыря были бы interleaved и приказаны как:

1, 2, 3, 4, 5, 6, 7, 8, 9

контакты DB9 организованы в два ряда, один ряд для первых 5 контактов, 1: 5 и второй ряд для последних 4 контактов, 6: 9:

1 2 3 4 5 6 7 8 9

когда DB9 IDC разъем использован, номера Штыря приказан на ленточном кабеле как:

1, 6, 2, 7, 3, 8, 4, 9, 5

этот порядок не будет должным образом соответствовать сигналам материнской платы с контактами разъема DB9.

заголовки для COM-портов расположены так, как вы показали (для вашей материнской платы) или

намеренно «неправильный номер» (по сравнению с назначениями DB9), чтобы разрешить подключения IDC к DB9_IDC.

Поэтому есть правило двух стилей или типов motherboard_header-на-DB9_connector кабелей.

это разъем DB9 IDC, который ваша материнская плата не может использовать с 10-контактным разъемом IDC и ленточным кабелем:

и что это за маленькие минусы? Это что-то указывает? Возможно, низкая или высокая логика?

знак «минус» означает, что сигнал использует обратную логику.

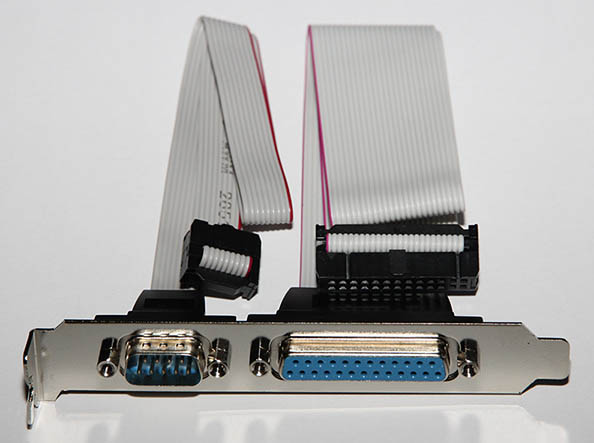

Я купил одну из этих комбинированных пластин ввода/вывода LPT и COM-порта.

итог:

Кабель + DB25 для порта LPT должен работать (при условии, что @Brian указал, что отмеченный край ленточного кабеля соответствует контакту 1 на заголовок.)

дополнительное соглашение

но я не уверен, как подключить его. Заголовки на материнской плате не в штучной упаковке, так что нет никакого способа сказать ориентацию, в которой для подключения кабелей.

правильный термин для «не в штучной упаковке» это shroudless, так как «коробка» — это саван.

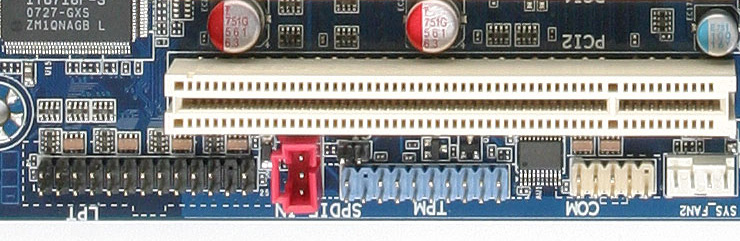

на фотографии материнской платы в левом нижнем углу заголовка LPT есть цифра «1» (в белой шелкографии). Это указывает на контакт #1 заголовка.

Красная полоса ленточного кабеля указывает на провод для вывода #1. Таким образом, сокет IDC должен быть ориентирован с красной полосой на этом конце заголовка с пометкой «1».

обратите внимание, что в белой пунктирной линии вокруг заголовка LPT шелкография указывает контур плащаницы.

Также обратите внимание, что есть удар или выскочить на нижнем краю этого контура, который соответствует ключ это только на одной стороне гнезда IDC. Это индикатор ориентации №2.

на фотографии материнской платы в левом нижнем углу заголовка COM отображается цифра «1».

Красная полоса ленточного кабеля (вывод № 1) должна быть на этом конце заголовка.

Но у вас есть 50/50 шанс, что COM-порт является правильным для вашей материнской платы. Удачно спецификации EIA / RS232 требуют, чтобы этот порт прибора был робастн достаточно для того чтобы отрегулировать краткости и misconnections. Так» неправильный » кабель можно прикрепиться для испытывать и не должен повредить материнскую плату.

дополнение #2

но, похоже, это не относится к заголовку COM-порта. В левом нижнем углу заголовка COM-порта нет «1». Что вы видите там, кажется, очень маленький пайки, или, возможно, действительно крошечный компонент SMD

но, кажется, есть контур для савана вокруг заголовка COM.

Так что используйте это, чтобы ориентировать сокет.

вы говорите, есть 50/50 шанс попасть в COM-порт. Я не вижу, как это будет совпадать в любом случае я включаю его. GND на заголовке COM находится на выводе 5, и это совпадает с TxD на гнезде IDC ленточного кабеля. Это не может быть правым? Если я поверну гнездо IDC вокруг, то GND совпадает с CTS на ленточном кабеле.

нет, вы не пытаетесь «повернуть»гнездо вокруг.

Существует только одна правильная ориентация для установки сокета на заголовке.

Сопоставьте ключ на гнезде с контуром плащаницы и/или выровняйте красный провод по контакту # 1 заголовка (эти две ориентации не должны противоречить).

50/50 шанс заключается в том, что кабель + DB9, который у вас есть, будет работать (или не работать) при установке в правильной ориентации.

DB9 имеет отлитый в форму конец, поэтому мы не можем осмотреть как ленточный кабель связан проволокой к DB9.

или вы можете использовать вольтамперомметр или тестер непрерывности для того чтобы определить как штыри DB9 отображают к штырям гнезда IDC на другом конце тесемки кабель

Или

Подключите его к материнской плате и попробуйте тест замыкания на себя (подключите выводы 2 и 3 на DB9) COM-порта.

у меня есть материнская плата ASUS с тем же выводом, что и у вас, и я видел COM-порты, описанные как специально предназначенные для этих типов заголовков mobo.

Поэтому я видел оба распиновки в использовании и читал о людях, жалующихся, почему их COM-порт не работает из-за неправильной проводки кабеля.

CTS должен встретиться с RTS, верно?

нет, это сопоставление сигнала будет происходить между двумя разъемами DB9 на каждом конце последовательного канала.

Этот кабель только расширяет сигналы от материнской платы к экстерьеру случая.

Так между заголовком материнской платы и этим DB9 вы хотите индивидуальное соответствие сигнала.

знаете ли Вы способ, возможно, какой-то справочный документ, чтобы расшифровать странные аббревиатуры имен сигналов, используемых Gigabyte?

нет, нет фиксированных или обязательных имен для сигналов платы.

Имена сигналов вы знакомы с для интерфейсов порт.

На стороне материнской платы порта, a часто используется другое название. Если на материнской плате имеется более одного COM-порта, то очевидно, что оба сигнала нельзя назвать «RxD»!

например, что такое «NSIN»? Было бы это как «сигнал»? Это похоже на RxD?

это кажется разумным.

должен ли я повторно припаять COM-порт, чтобы получить провода в правильном порядке?

только если вы определите, что существующий кабель+разъем не работает.

может легче открыть IDC разъем, переделать и закрыть его? Я никогда не имел дело с одним из них раньше, я не знаю, возможно ли открыть их после того, как они были закрыты, не нарушая их. Но обжимные провода легче, чем пайка.

давным-давно на форуме пользователей ASUS я описал, как подключить паяльную чашку DB9 для задней панели. В качестве ответа кто-то описал, как он разобрал IDC разъем, отделил провода ленточного кабеля, переупорядочил соединения и собрал его так же, как вы упомянули.

Это не рекомендуется, потому что пинчеры не предназначены для повторного использования, но это можно сделать.

Но беспокойтесь об этом только после того, как вы определите, что кабель+разъем не работает.

или это» вытеснение » проводов в терминологии IDC?

хорошо, ты меня туда привел.

Думаю, как обычно глагол-это просто «собрать». Обжимной инструмент (или жим) используется, чтобы собрать весь разъем на шлейф.

Вы должны использовать шлейф с IDC. Но если вы в конечном итоге попробуете IDC rewire,то это почти как «пробивание» дискретного провода на разъеме RJ45 keystone.

PC parallel LPT port распиновка и описание @ pinouts.ru

Parallel port allow the input of up to 9 bits or the output of 12 bits at any one given time. This port may be used for interfacing home made projects since external circuitry is minimal for many simple tasks. The port is composed of 4 control lines, 5 status lines and 8 data lines. Nowdays is obsolete and rarely found on the back of your PC (note, that 25 pin D-SUB male connector may represent RS-232 serial port, which is not compatible with LPT!).

There are differnt modes of Parallel port work in modern computer. Take a look to ECP Parallel LPT port (IEEE-1284A) interface for more detailed explanations. Information included in current page is about older SPP LPT port interface. ECP specification includes SPP as one of possible modes.

The data output of the Parallel Port is normally TTL logic levels. Most Parallel Ports implemented in ASIC, can sink and source around 12mA. However, there are other variations possible: Sink/Source 6mA, Source 12mA/Sink 20mA, Sink 16mA/Source 4mA, Sink/Source 12mA and others.

Centronics is an early used standard for transferring data from a host to the printer. The majority of printers use this handshake.

______ ___________________

nStrobe \ /

\______/

______________

Busy / \

______/ \___________

______________________ ____

nAck \ /

\_____/

___ _______ _________________

/ /

Data / /

/ /

__/ \_______/ \_________________

Data is first applied on the Parallel Port pins 2 to 7. The host then checks to see if the printer is busy. i.e. the busy line should be low. The program then asserts the strobe, waits a minimum of 1mS, and then de-asserts the strobe. Data is normally read by the printer/peripheral on the rising edge of the strobe. The printer will indicate that it is busy processing data via the Busy line. Once the printer has accepted data, it will acknowledge the byte by a negative pulse about 5mS on the nAck line. Host may ignore the nAck line to save time.

Note: Connecting as a SPP interface, it’s important to initialize the printer putting on low the Init Pin, (16 for the IEEE-1284A interface) and also to ground the ‘Select Printer’ (17 on the same interface). Otherwise, no matter how much data you send, the printer will not understand anything!

Разъем DB 25 (LPT) — распиновка, описание, фото

Разъем DB 25 (LPT) — распиновка, описание, фотоОписание DB 25 (LPT)

| штекер DB 25 (LPT) | гнездо DB 25 (LPT) |

Параллельный порт — тип интерфейса, разработанный для компьютеров (персональных и других) для подключения различных периферийных устройств. В вычислительной технике параллельный порт является физической реализацией принципа параллельного соединения. Он также известен как принтерный порт или порт Centronics. Стандарт IEEE 1284 определяет двунаправленный вариант порта, который позволяет одновременно передавать и принимать биты данных.

До появления USB параллельный интерфейс был адаптирован помимо принтеров к большому числу периферийных устройств. Вероятно, одним из первых таких устройств были электронные ключи для защиты программного обеспечения от копирования. Вскоре параллельный интерфейс нашёл применение в накопителях на гибких магнитных дисках Iomega Zip и сканерах, за которыми последовали и другие устройства: модемы, звуковые карты, веб-камеры, геймпады, джойстики, внешние жёсткие диски и CD-диски. Появились адаптеры для подключения SCSI-устройств через параллельный интерфейс. Могли подключаться параллельно и другие устройства, такие как EPROM и аппаратные контроллеры.

Для потребителей интерфейс USB, а в некоторых случаях Ethernet, эффективно заменили параллельный порт принтера. Многие производители персональных компьютеров и ноутбуков рассматривают параллельный порт как устаревшее наследие прошлого и больше не поддерживают параллельный интерфейс. Руководящие принципы для программы Windows Logo фирмы Microsoft «настоятельно рекомендуют» разработчикам систем воздерживаться от применения параллельных портов. Разработаны и доступны адаптеры «USB-параллельный интерфейс», которые позволяют подключать принтеры с параллельным интерфейсом к USB портам.

Распиновка DB 25 (LPT)

| штекер | гнездо |

| № вывода | Обозначение | Описание |

|---|---|---|

| 1 | /STROBE | Strobe (Строб) |

| 2 | D0 | Data Bit 0 (данные, нулевой бит) |

| 3 | D1 | Data Bit 1 (данные, 1-й бит) |

| 4 | D2 | Data Bit 2 (данные, 2-й бит) |

| 5 | D3 | Data Bit 3 (данные, 3-й бит) |

| 6 | D4 | Data Bit 4 (данные, 4-й бит) |

| 7 | D5 | Data Bit 5 (данные, 5-й бит) |

| 8 | D6 | Data Bit 6 (данные, 6-й бит) |

| 9 | D7 | Data Bit 7 (данные, 7-й бит) |

| 10 | /ACK | Acknowledge (Подтверждение) |

| 11 | BUSY | Busy (Занято) |

| 12 | PE | Paper End (Нет бумаги) |

| 13 | SEL | Select (Выбор) |

| 14 | /AUTOFD | Autofeed (Перевод строки) |

| 15 | /ERROR | Error (Ошибка) |

| 16 | /INIT | Initialize (Инициализация) |

| 17 | /SELIN | Select In (Выбор) |

| 18 | GND | Signal Ground (Корпус) |

| 19 | GND | Signal Ground (Корпус) |

| 20 | GND | Signal Ground (Корпус) |

| 21 | GND | Signal Ground (Корпус) |

| 22 | GND | Signal Ground (Корпус) |

| 23 | GND | Signal Ground (Корпус) |

| 24 | GND | Signal Ground (Корпус) |

| 25 | GND | Signal Ground (Корпус) |

© pinov.net 2018-2020

РАЗЪЁМЫ НА МАТЕРИНСКОЙ ПЛАТЕ

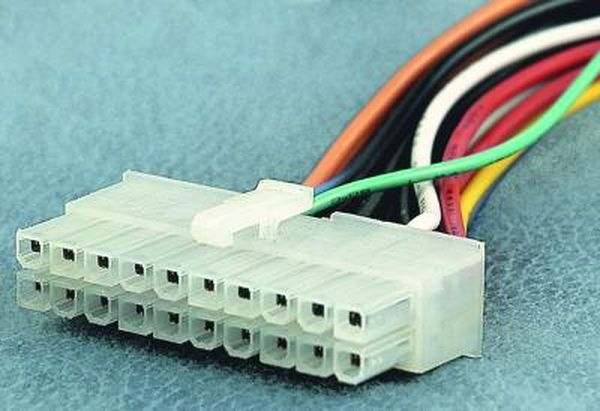

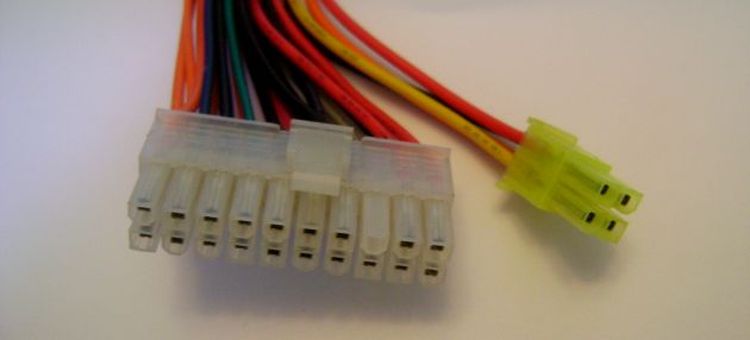

На материнской плате есть множество разъемов для подключения различных устройств. Это процессор, видеокарта, оперативная память и другие. Иногда также, по каким либо причинам, предпочитают пользоваться не встроенными звуковой и сетевой картой, а отдельными устанавливаемыми в PCI и PCI–E разъемы. С их подключением обычно проблем не возникает, достаточно установить карту в свой слот. Но иногда возникает надобность полной разборки компьютера и самостоятельной замены материнской платы с целью апгрейда, либо сгоревшей платы на аналогичную новую. Сверхсложного в этом ничего нет, но есть, как и везде, свои нюансы. Для работы материнской платы и установленных в неё устройств к ней нужно подключить питание. В материнских платах, выпускаемых до 2001-2002 года питание на материнские платы подавалось с помощью разъема 20 pin.

Разъем питания 20-пин гнездо

Такой разъем имел на корпусе специальную защелку для исключения самопроизвольного извлечения разъема, например в случае тряски, при перевозке. На рисунке она находится снизу.

Разъем питания 20-пин штекер

С появлением процессоров Pentium 4 добавился второй 4–х пиновый разъем 12 вольт, подключаемый отдельно к материнской плате. Называются такие разъемы 20+4 pin. Примерно с 2005 года стали поступать в продажу блоки питания и материнские платы 24+4 pin. В таком разъеме добавляются еще 4 контакта (не путать с 4 pin 12 вольт). Они могут быть, как соединены с общим разъемом и тогда 20 pin превращаются в 24 pin, так и подключаться отдельным 4 pin разъемом.

Разъем блока питания 20 + 4 пин

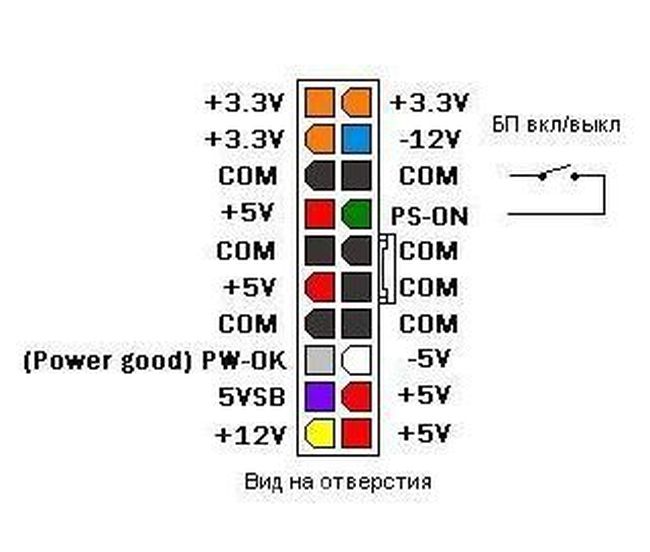

Это сделано для совместимости по питанию со старыми материнскими платами. Но для того чтобы компьютер включился, мало подать питание на материнскую плату. Это в древних компьютерах, в которых стояли материнские платы формата АТ, компьютер включался после подачи питания на блок питания, выключателем или силовой кнопкой с фиксацией. В блоках питания формата АТХ для их включения нужно замкнуть выводы блока питания PS–ON и СОМ. Кстати, таким способом можно проверить блок питания формата АТХ, замкнув проволочкой или разогнутой канцелярской скрепкой эти выводы.

Включение блока питания

При этом блок питания должен включиться, начнет вращаться кулер и появится напряжение на разъемах. Когда мы нажимаем кнопку включения, на лицевой панели системного блока, мы подаем на материнскую плату своего рода сигнал, что компьютер нужно включить. Также если мы нажмем во время работы компьютера эту же кнопку и подержим её около 4–5 секунд, компьютер выключится. Такое выключение нежелательно, потому что может наступить сбой в работе программ.

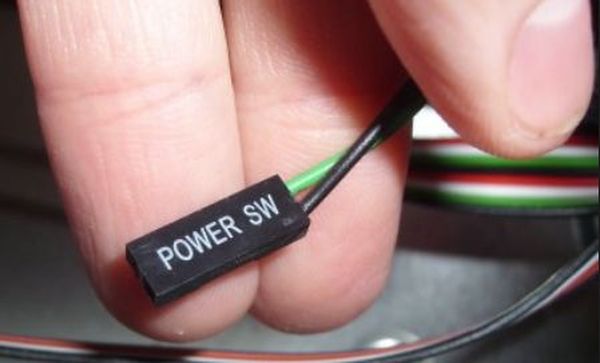

Разъем Power switch

Кнопка включения компьютера (Power) и кнопка сброса (Reset) подключаются к материнской плате компьютера с помощью разъемов Power switch и Reset switch. Выглядят они как двухконтактные черные пластмассовые разъемы, имеющие два провода белый (или черный) и цветной. Подобными разъемами, к материнской плате подключаются индикация питания, на зеленом светодиоде, подписанная на разъеме как Power Led и индикатор работы винчестера на красном светодиоде HDD Led.

Разъемы подключения светодиодов и кнопок

Разъем Power Led часто бывает разделен на два разъема по одному пину. Это сделано из за того, что на некоторых материнских платах эти разъемы находятся рядом, также как у HDD Led, а на других платах они разделены местом под пин.

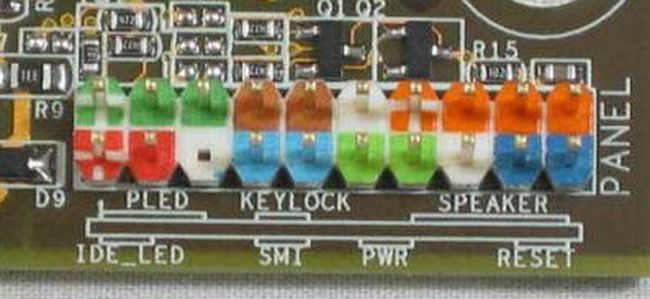

Фронт панель материнской платы

На рисунке выше изображено подключение разъемов Front panel или передней панели системного блока. Разберем более подробнее подключение Front panel. Нижний ряд, слева, красным (пласмассой) выделены разъемы для подключения светодиода винчестера (HDD Led), дальше идет разъем SMI, выделенный голубым, затем разъем для подключения кнопки включения, выделен светло зеленым (Power Switch), после идет кнопка сброса выделена синим (Reset Switch). Верхний ряд, начиная слева, светодиод питания, темно зеленым (Power Led), Keylock коричневым, и динамик оранжевым (Speaker). При подключении разъемов светодиодов Power Led, HDD Led и динамика Speaker нужно соблюдать полярность.

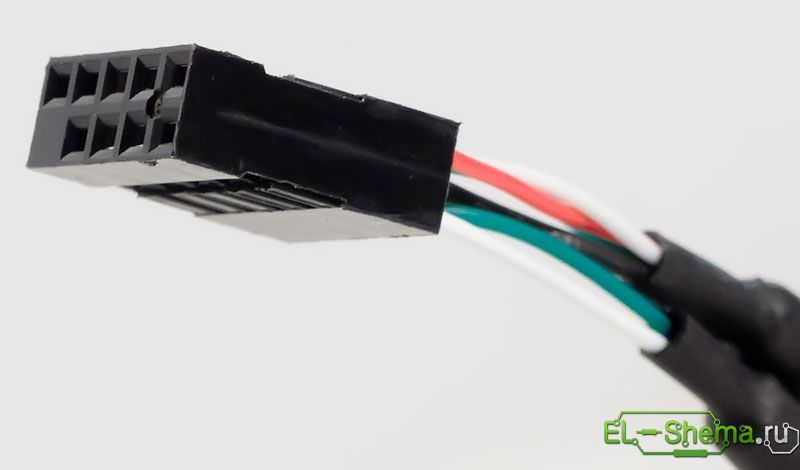

Планка USB разъемов

Также много вопросов возникает у начинающих при подключении на переднюю панель USB разъемов. Аналогично подключаются планка разъемов, размещаемая на задней стенке компьютера и внутренний кардридер.

Внутренний кардридер и шнур

Как видно из двух вышеприведенных рисунков кардридеры и планки подключаются с помощью 8 контактного слитного разъема.

USB разъем на кабеле для подключения к материнской плате

Но подключение USB разъемов на переднюю панель иногда бывает затруднено тем, что пины этого разъема бывают разъединены.

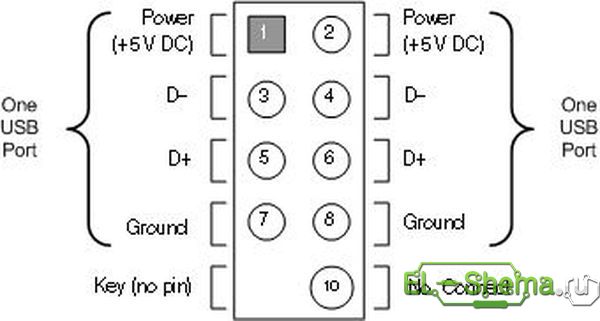

Подключение USB к материнской плате — схема

На них нанесена маркировка, подобной той которую мы видели на разъемах подключения передней панели. Как всем известно, в USB разъеме используются 4 контакта: питание +5 вольт, земля и два контакта для передачи данных D- и D+. В разъеме подключения к материнской плате мы имеем 8 контактов, 2 порта USB.

Разъем подключения к USB

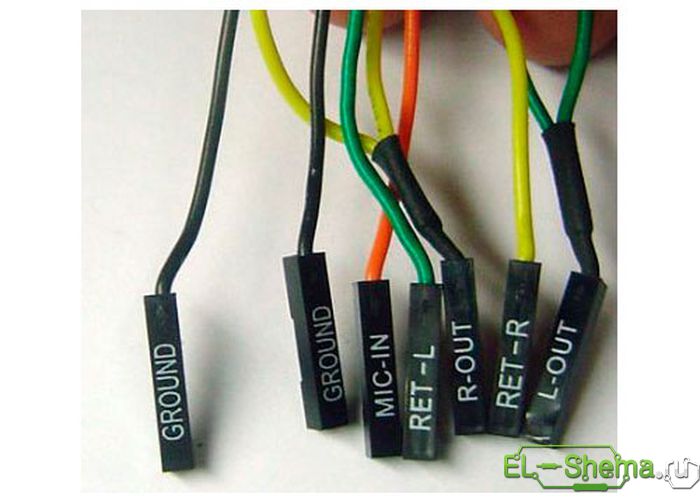

Если разъем все же будет состоять из отдельных пинов, цвета подключаемых проводов видно на рисунке выше. Помимо кнопок включения, сброса, индикации и USB разъемов, на переднюю панель выводятся гнезда подключения микрофона и наушников. Эти гнезда также подключаются к материнской плате отдельными пинами.

Подключение аудио разъемов передней панели ПК

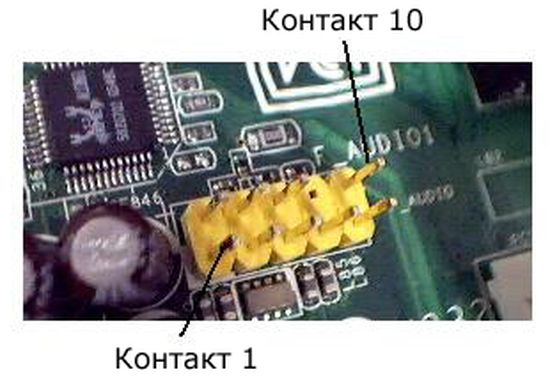

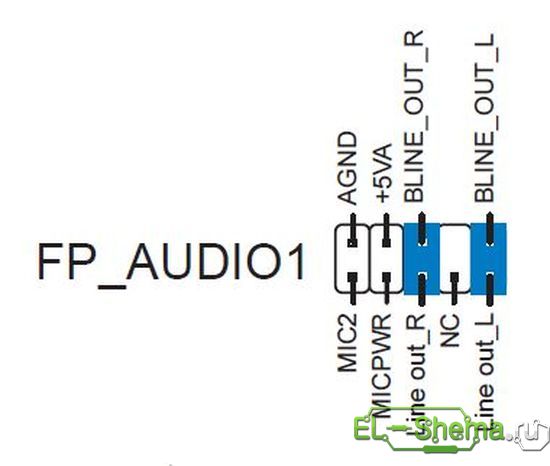

Подключение гнезд организовано таким образом, чтобы при подключении наушников отключались колонки, подключенные к разъему Line-Out в задней части материнской платы. Разъем, к которому подключаются гнезда на передней панели, называется FP_Audio, или Front Panel Audio. Этот разъем можно видеть на рисунке:

Фронт панель аудио системного блока

Распиновку или расположение контактов на разъеме видно на следующем рисунке:

Подключение fp audio

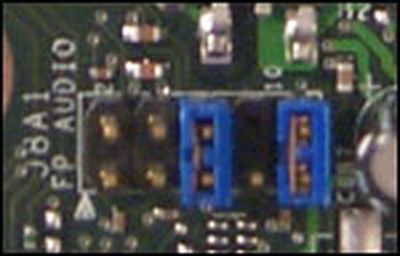

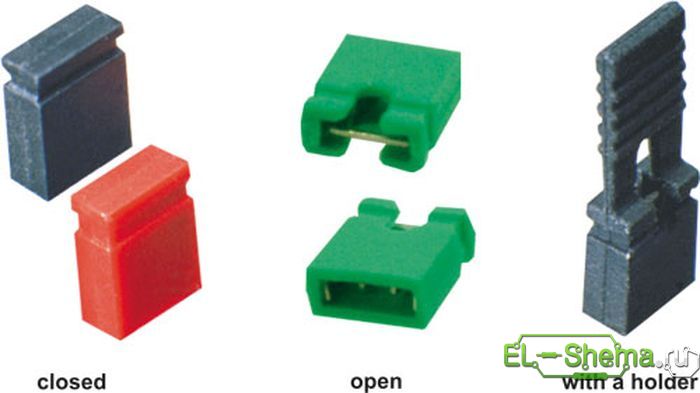

Здесь есть один нюанс, если вы пользовались корпусом с гнездами для микрофона и наушников, а после захотели поменять на корпус без таких гнезд. Соответственно не подключая разъемы fp_audio на материнскую плату. В таком случае при подключении колонок к разъему Line-Out материнской платы звука не будет. Для того чтобы встроенная звуковая карта заработала, нужно установить две перемычки (джампера) на 2 пары контактов, как на рисунке далее:

Перемычки на fp_audio

Такие джамперы — перемычки используются для установки на материнских платах, видео, звуковых картах и других устройствах для задания режимов работы.

Джамперы материнской платы фото

Устроена перемычка внутри очень просто: в ней два гнезда, которые соединены между собой. Поэтому, когда мы одеваем перемычку на два соседних штырька — контакта, мы их замыкаем между собой.

Планка LPT порта

Также на материнских платах встречаются распаянные разъемы LPT и COM портов. В таком случае для подключения используется планка с выводом соответствующего разъема на заднюю стенку системного блока.

Планка COM порта

При установке нужно быть внимательным и не подключить разъем неправильно, наоборот. Ещё на материнских платах находятся разъемы для подключения кулеров. Их количество бывает, в зависимости от модели материнской платы равным двум, в дешевых моделях плат, до трех в более дорогих. К этим разъемам подключаются кулер процессора и кулер на выдув, расположенный на задней стенке корпуса. К третьему разъему можно подключить кулер, устанавливаемый на передней стенке системного блока на вдув, либо кулер устанавливаемый на радиатор чипсета.

Разъем подключения кулера к материнке

Все эти разъемы взаимозаменяемы, так как они идут в основном трехпиновые, исключение составляют четырехпиновые разъемы подключения кулеров процессора.

motherboard — Как подключить заголовки LPT и COM-портов на материнской плате?

Я хотел бы добавить LPT и COM-порт на свой компьютер. Плата не имеет LPT или COM-порта на панели ввода-вывода на задней панели. Однако на плате есть LPT и COM-порты. Вы можете видеть их на рисунке ниже.

Поэтому вместо того, чтобы покупать одну из этих плат PCI с LPT и COM-портами, я решил использовать встроенную логику материнской платы. PCI-карты занимают место, и мне приходится беспокоиться о драйверах, какую платформу я использую (Linux против Windows), а что нет.

в штучной упаковке , поэтому нет никакой возможности указать ориентацию, в которой для подключения кабелей. Тогда есть также путаница с маркировкой контактов.

в штучной упаковке , поэтому нет никакой возможности указать ориентацию, в которой для подключения кабелей. Тогда есть также путаница с маркировкой контактов.

Порт LPT

Это распиновка, используемая материнской платой (взята из руководства).

Это согласно стандарту? Какой это был бы стандарт? … Мне это не похоже на IEEE1284. Вот раскладка параллельного порта в соответствии с Wikipedia .

Pin Signal

--------------

1 Strobe

2 Data0

3 Data1

4 Data2

5 Data3

6 Data4

7 Data5

8 Data6

9 Data7

10 Ack

11 Busy

12 Paper-out

13 Select

14 Linefeed

15 Error

16 Reset

17 Select-printer

18 Ground

19 Ground

20 Ground

21 Ground

22 Ground

23 Ground

24 Ground

25 Ground

Вот диаграмма:

Разве они не должны совпадать? Я должен догадаться, что на самом деле означают эти немые аббревиатуры, используемые производителем материнских плат. Некоторые из них очевидны, другие — нет. Например, STB означает Strobe, и это на первом булавке, так что это хорошо. Но почему BUSY на штыре 21 здесь и на булавке 11 там? Похоже, они испортили это, ошиблись или что-то в этом роде, возможно, чтобы вы купили свои проклятые пластины ввода-вывода. Или, возможно, существуют разные проводки для разных версий и ревизий порта?

И что с маленькими минусовыми знаками? Это что-то говорит? Возможно, низкая или высокая логика? Они не говорят об этом в руководстве. Как они ожидают, что я сам разойдусь. Кстати, это доска Gigabyte. Я спросил об этом в GGTS (Gigabyte Global Tech Support), и их ответ заключался в том, что они не могли дать мне больше подробностей, потому что это «секрет компании». Люди в Gigabyte, должно быть, потеряли рассудок! Или что-то …

COM-порт

Кажется, все в порядке, не так ли? Это, по-видимому, стандартная распиновка.

PCI Express 1x, 4x, 8x, 16x bus распиновка и описание @ pinouts.ru

PCI Express as a high-bandwidth, low pin count, serial, interconnect technology. It was designed to replace the older PCI and AGPbus standards. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. PCI Express architecture provides a high performance I/O infrastructure for Desktop Platforms with transfer rates starting at 2.5 Giga transfers per second over a x1 PCI Express lane for Gigabit Ethernet, TV Tuners, Firewire 1394a/b controllers, and general purpose I/O. PCI Express architecture provides a high performance graphics infrastructure for Desktop Platforms doubling the capability of existing AGP8x designs with transfer rates of 4.0 Gigabytes per second over a x16 PCI Express lane for graphics controllers. A lane is composed of two differential signaling pairs, with one pair for receiving data and the other for transmitting.

ExpressCard utilizing PCI Express interface, developed by the PCMCIA group for mobile computers. PCI Express Advanced Power Management features help to extend platform battery life and to enable users to work anywhere, without an AC power source. The PCI Express electrical interface is also used in some computer storage interfaces SATA Express and M.2.

The broad adoption of PCI Express in the mobile, enterprise and communication segments enables convergence through the re-use of a common interconnect technology.

PCI-E is a serial bus which uses two low-voltage differential LVDS pairs, at 2.5Gb/s in each direction [one transmit, and one receive pair]. PCI Express supports 1x [2.5Gbps], 2x, 4x, 8x, 12x, 16x, and 32x bus widths [transmit / receive pairs].

The differential pins [Lanes] listed in the pin out table above are LVDS which stands for: Low Voltage Differential Signaling.

PCI-Express 1x Connector Pin-Out

| Pin |

Side B Connector |

Side A Connector |

||

| # | Name | Description | Name | Description |

| 1 | +12v | +12 volt power | PRSNT#1 | Hot plug presence detect |

| 2 | +12v | +12 volt power | +12v | +12 volt power |

| 3 | +12v | +12 volt power | +12v | +12 volt power |

| 4 | GND | Ground | GND | Ground |

| 5 | SMCLK | SMBus clock | JTAG2 | TCK |

| 6 | SMDAT | SMBus data | JTAG3 | TDI |

| 7 | GND | Ground | JTAG4 | TDO |

| 8 | +3.3v | +3.3 volt power | JTAG5 | TMS |

| 9 | JTAG1 | +TRST# | +3.3v | +3.3 volt power |

| 10 | 3.3Vaux | 3.3v volt power | +3.3v | +3.3 volt power |

| 11 | WAKE# | Link Reactivation | PWRGD | Power Good |

|

Mechanical Key |

||||

| 12 | RSVD | Reserved | GND | Ground |

| 13 | GND | Ground | REFCLK+ | Reference Clock Differential pair |

| 14 | HSOp(0) | Transmitter Lane 0, Differential pair |

REFCLK- | |

| 15 | HSOn(0) | GND | Ground | |

| 16 | GND | Ground | HSIp(0) | Receiver Lane 0, Differential pair |

| 17 | PRSNT#2 | Hotplug detect | HSIn(0) | |

| 18 | GND | Ground | GND | Ground |

PCI-Express 4x Connector Pin-Out

| Pin |

Side B Connector |

Side A Connector |

||

| # | Name | Description | Name | Description |

| 1 | +12v | +12 volt power | PRSNT#1 | Hot plug presence detect |

| 2 | +12v | +12 volt power | +12v | +12 volt power |

| 3 | +12v | +12 volt power | +12v | +12 volt power |

| 4 | GND | Ground | GND | Ground |

| 5 | SMCLK | SMBus clock | JTAG2 | TCK |

| 6 | SMDAT | SMBus data | JTAG3 | TDI |

| 7 | GND | Ground | JTAG4 | TDO |

| 8 | +3.3v | +3.3 volt power | JTAG5 | TMS |

| 9 | JTAG1 | +TRST# | +3.3v | +3.3 volt power |

| 10 | 3.3Vaux | 3.3v volt power | +3.3v | +3.3 volt power |

| 11 | WAKE# | Link Reactivation | PWRGD | Power Good |

|

Mechanical Key |

||||

| 12 | RSVD | Reserved | GND | Ground |

| 13 | GND | Ground | REFCLK+ | Reference Clock Differential pair |

| 14 | HSOp(0) | Transmitter Lane 0, Differential pair |

REFCLK- | |

| 15 | HSOn(0) | GND | Ground | |

| 16 | GND | Ground | HSIp(0) | Receiver Lane 0, Differential pair |

| 17 | PRSNT#2 | Hotplug detect | HSIn(0) | |

| 18 | GND | Ground | GND | Ground |

| 19 | HSOp(1) | Transmitter Lane 1, Differential pair |

RSVD | Reserved |

| 20 | HSOn(1) | GND | Ground | |

| 21 | GND | Ground | HSIp(1) | Receiver Lane 1, Differential pair |

| 22 | GND | Ground | HSIn(1) | |

| 23 | HSOp(2) | Transmitter Lane 2, Differential pair |

GND | Ground |

| 24 | HSOn(2) | GND | Ground | |

| 25 | GND | Ground | HSIp(2) | Receiver Lane 2, Differential pair |

| 26 | GND | Ground | HSIn(2) | |

| 27 | HSOp(3) | Transmitter Lane 3, Differential pair |

GND | Ground |

| 28 | HSOn(3) | GND | Ground | |

| 29 | GND | Ground | HSIp(3) | Receiver Lane 3, Differential pair |

| 30 | RSVD | Reserved | HSIn(3) | |

| 31 | PRSNT#2 | Hot plug detect | GND | Ground |

| 32 | GND | Ground | RSVD | Reserved |

PCI-Express 8x Connector Pin-Out

| Pin |

Side B Connector |

Side A Connector |

||

| # | Name | Description | Name | Description |

| 1 | +12v | +12 volt power | PRSNT#1 | Hot plug presence detect |

| 2 | +12v | +12 volt power | +12v | +12 volt power |

| 3 | +12v | +12 volt power | +12v | +12 volt power |

| 4 | GND | Ground | GND | Ground |

| 5 | SMCLK | SMBus clock | JTAG2 | TCK |

| 6 | SMDAT | SMBus data | JTAG3 | TDI |

| 7 | GND | Ground | JTAG4 | TDO |

| 8 | +3.3v | +3.3 volt power | JTAG5 | TMS |

| 9 | JTAG1 | +TRST# | +3.3v | +3.3 volt power |

| 10 | 3.3Vaux | 3.3v volt power | +3.3v | +3.3 volt power |

| 11 | WAKE# | Link Reactivation | PWRGD | Power Good |

|

Mechanical Keycard |

||||

| 12 | RSVD | Reserved | GND | Ground |

| 13 | GND | Ground | REFCLK+ | Reference Clock Differential pair |

| 14 | HSOp(0) | Transmitter Lane 0, Differential pair |

REFCLK- | |

| 15 | HSOn(0) | GND | Ground | |

| 16 | GND | Ground | HSIp(0) | Receiver Lane 0, Differential pair |

| 17 | PRSNT#2 | Hotplug detect | HSIn(0) | |

| 18 | GND | Ground | GND | Ground |

| 19 | HSOp(1) | Transmitter Lane 1, Differential pair |

RSVD | Reserved |

| 20 | HSOn(1) | GND | Ground | |

| 21 | GND | Ground | HSIp(1) | Receiver Lane 1, Differential pair |

| 22 | GND | Ground | HSIn(1) | |

| 23 | HSOp(2) | Transmitter Lane 2, Differential pair |

GND | Ground |

| 24 | HSOn(2) | GND | Ground | |

| 25 | GND | Ground | HSIp(2) | Receiver Lane 2, Differential pair |

| 26 | GND | Ground | HSIn(2) | |

| 27 | HSOp(3) | Transmitter Lane 3, Differential pair |

GND | Ground |

| 28 | HSOn(3) | GND | Ground | |

| 29 | GND | Ground | HSIp(3) | Receiver Lane 3, Differential pair |

| 30 | RSVD | Reserved | HSIn(3) | |

| 31 | PRSNT#2 | Hot plug detect | GND | Ground |

| 32 | GND | Ground | RSVD | Reserved |

| 33 | HSOp(4) | Transmitter Lane 4, Differential pair |

RSVD | Reserved |

| 34 | HSOn(4) | GND | Ground | |

| 35 | GND | Ground | HSIp(4) | Receiver Lane 4, Differential pair |

| 36 | GND | Ground | HSIn(4) | |

| 37 | HSOp(5) | Transmitter Lane 5, Differential pair |

GND | Ground |

| 38 | HSOn(5) | GND | Ground | |

| 39 | GND | Ground | HSIp(5) | Receiver Lane 5, Differential pair |

| 40 | GND | Ground | HSIn(5) | |

| 41 | HSOp(6) | Transmitter Lane 6, Differential pair |

GND | Ground |

| 42 | HSOn(6) | GND | Ground | |

| 43 | GND | Ground | HSIp(6) | Receiver Lane 6, Differential pair |

| 44 | GND | Ground | HSIn(6) | |

| 45 | HSOp(7) | Transmitter Lane 7, Differential pair |

GND | Ground |

| 46 | HSOn(7) | GND | Ground | |

| 47 | GND | Ground | HSIp(7) | Receiver Lane 7, Differential pair |

| 48 | PRSNT#2 | Hot plug detect | HSIn(7) | |

| 49 | GND | Ground | GND | Ground |

PCI-Express 16x Connector Pin-Out

| Pin |

Side B Connector |

Side A Connector |

||

| # | Name | Description | Name | Description |

| 1 | +12v | +12 volt power | PRSNT#1 | Hot plug presence detect |

| 2 | +12v | +12 volt power | +12v | +12 volt power |

| 3 | +12v | +12 volt power | +12v | +12 volt power |

| 4 | GND | Ground | GND | Ground |

| 5 | SMCLK | SMBus clock | JTAG2 | TCK |

| 6 | SMDAT | SMBus data | JTAG3 | TDI |

| 7 | GND | Ground | JTAG4 | TDO |

| 8 | +3.3v | +3.3 volt power | JTAG5 | TMS |

| 9 | JTAG1 | +TRST# | +3.3v | +3.3 volt power |

| 10 | 3.3Vaux | 3.3v volt power | +3.3v | +3.3 volt power |

| 11 | WAKE# | Link Reactivation | PWRGD | Power Good |

|

Mechanical Key |

||||

| 12 | RSVD | Reserved | GND | Ground |

| 13 | GND | Ground | REFCLK+ | Reference Clock Differential pair |

| 14 | HSOp(0) | Transmitter Lane 0, Differential pair |

REFCLK- | |

| 15 | HSOn(0) | GND | Ground | |

| 16 | GND | Ground | HSIp(0) | Receiver Lane 0, Differential pair |

| 17 | PRSNT#2 | Hotplug detect | HSIn(0) | |

| 18 | GND | Ground | GND | Ground |

| 19 | HSOp(1) | Transmitter Lane 1, Differential pair |

RSVD | Reserved |

| 20 | HSOn(1) | GND | Ground | |

| 21 | GND | Ground | HSIp(1) | Receiver Lane 1, Differential pair |

| 22 | GND | Ground | HSIn(1) | |

| 23 | HSOp(2) | Transmitter Lane 2, Differential pair |

GND | Ground |

| 24 | HSOn(2) | GND | Ground | |

| 25 | GND | Ground | HSIp(2) | Receiver Lane 2, Differential pair |

| 26 | GND | Ground | HSIn(2) | |

| 27 | HSOp(3) | Transmitter Lane 3, Differential pair |

GND | Ground |

| 28 | HSOn(3) | GND | Ground | |

| 29 | GND | Ground | HSIp(3) | Receiver Lane 3, Differential pair |

| 30 | RSVD | Reserved | HSIn(3) | |

| 31 | PRSNT#2 | Hot plug detect | GND | Ground |

| 32 | GND | Ground | RSVD | Reserved |

| 33 | HSOp(4) | Transmitter Lane 4, Differential pair |

RSVD | Reserved |

| 34 | HSOn(4) | GND | Ground | |

| 35 | GND | Ground | HSIp(4) | Receiver Lane 4, Differential pair |

| 36 | GND | Ground | HSIn(4) | |

| 37 | HSOp(5) | Transmitter Lane 5, Differential pair |

GND | Ground |

| 38 | HSOn(5) | GND | Ground | |

| 39 | GND | Ground | HSIp(5) | Receiver Lane 5, Differential pair |

| 40 | GND | Ground | HSIn(5) | |

| 41 | HSOp(6) | Transmitter Lane 6, Differential pair |

GND | Ground |

| 42 | HSOn(6) | GND | Ground | |

| 43 | GND | Ground | HSIp(6) | Receiver Lane 6, Differential pair |

| 44 | GND | Ground | HSIn(6) | |

| 45 | HSOp(7) | Transmitter Lane 7, Differential pair |

GND | Ground |

| 46 | HSOn(7) | GND | Ground | |

| 47 | GND | Ground | HSIp(7) | Receiver Lane 7, Differential pair |

| 48 | PRSNT#2 | Hot plug detect | HSIn(7) | |

| 49 | GND | Ground | GND | Ground |

| 50 | HSOp(8) | Transmitter Lane 8, Differential pair |

RSVD | Reserved |

| 51 | HSOn(8) | GND | Ground | |

| 52 | GND | Ground | HSIp(8) | Receiver Lane 8, Differential pair |

| 53 | GND | Ground | HSIn(8) | |

| 54 | HSOp(9) | Transmitter Lane 9, Differential pair |

GND | Ground |

| 55 | HSOn(9) | GND | Ground | |

| 56 | GND | Ground | HSIp(9) | Receiver Lane 9, Differential pair |

| 57 | GND | Ground | HSIn(9) | |

| 58 | HSOp(10) | Transmitter Lane 10, Differential pair |

GND | Ground |

| 59 | HSOn(10) | GND | Ground | |

| 60 | GND | Ground | HSIp(10) | Receiver Lane 10, Differential pair |

| 61 | GND | Ground | HSIn(10) | |

| 62 | HSOp(11) | Transmitter Lane 11, Differential pair |

GND | Ground |

| 63 | HSOn(11) | GND | Ground | |

| 64 | GND | Ground | HSIp(11) | Receiver Lane 11, Differential pair |

| 65 | GND | Ground | HSIn(11) | |

| 66 | HSOp(12) | Transmitter Lane 12, Differential pair |

GND | Ground |

| 67 | HSOn(12) | GND | Ground | |

| 68 | GND | Ground | HSIp(12) | Receiver Lane 12, Differential pair |

| 69 | GND | Ground | HSIn(12) | |

| 70 | HSOp(13) | Transmitter Lane 13, Differential pair |

GND | Ground |

| 71 | HSOn(13) | GND | Ground | |

| 72 | GND | Ground | HSIp(13) | Receiver Lane 13, Differential pair |

| 73 | GND | Ground | HSIn(13) | |

| 74 | HSOp(14) | Transmitter Lane 14, Differential pair |

GND | Ground |

| 75 | HSOn(14) | GND | Ground | |

| 76 | GND | Ground | HSIp(14) | Receiver Lane 14, Differential pair |

| 77 | GND | Ground | HSIn(14) | |

| 78 | HSOp(15) | Transmitter Lane 15, Differential pair |

GND | Ground |

| 79 | HSOn(15) | GND | Ground | |

| 80 | GND | Ground | HSIp(15) | Receiver Lane 15, Differential pair |

| 81 | PRSNT#2 | Hot plug present detect | HSIn(15) | |

| 82 | RSVD#2 | Hot Plug Detect | GND | Ground |

PRSNT#1 is connected to GND on motherboard.

Add on card needs to have PRSNT#1 connected to one of PRSNT#2 depending what type of connector is in use.

PCI-express standards

PCI Express 1.0a

In 2003, PCI-SIG introduced PCIe 1.0a, with a per-lane data rate of 250 MB/s and a transfer rate of 2.5 gigatransfers per second (GT/s). Transfer rate is expressed in transfers per second instead of bits per second because the number of transfers includes the overhead bits, which do not provide additional throughput; PCIe 1.x uses an 8b/10b encoding scheme, resulting in a 20% (= 2/10) overhead on the raw channel bandwidth.

PCI Express 2.0

PCI-SIG announced the availability of the PCI Express Base 2.0 specification on 15 January 2007. The PCIe 2.0 standard doubles the transfer rate compared with PCIe 1.0 to 5 GT/s and the per-lane throughput rises from 250 MB/s to 500 MB/s. Consequently, a 32-lane PCIe connector (×32) can support an aggregate throughput of up to 16 GB/s. PCIe 2.0 motherboard slots are fully backward compatible with PCIe v1.x cards. PCIe 2.0 cards are also generally backward compatible with PCIe 1.x motherboards, using the available bandwidth of PCI Express 1.1. Overall, graphic cards or motherboards designed for v2.0 will work with the other being v1.1 or v1.0a. Like 1.x, PCIe 2.0 uses an 8b/10b encoding scheme, therefore delivering, per-lane, an effective 4 Gbit/s max transfer rate from its 5 GT/s raw data rate.

PCI Express 2.1

PCI Express 2.1 (dated March 4, 2009) supports a large proportion of the management, support, and troubleshooting systems planned for full implementation in PCI Express 3.0. However, the speed is the same as PCI Express 2.0. The increase in power from the slot breaks backward compatibility between PCI Express 2.1 cards and some older motherboards with 1.0/1.0a, but most motherboards with PCI Express 1.1 connectors are provided with a BIOS update by their manufacturers through utilities to support backward compatibility of cards with PCIe 2.1.

PCI Express 3.0

PCI Express 3.0 specification was made available in November 2010. New features for the PCI Express 3.0 specification include a number of optimizations for enhanced signaling and data integrity, including transmitter and receiver equalization, PLL improvements, clock data recovery, and channel enhancements for currently supported topologies. PCI Express 3.0 upgrades the encoding scheme to 128b/130b from the previous 8b/10b encoding, reducing the bandwidth overhead from 20% of PCI Express 2.0 to approximately 1.54% (= 2/130). This is achieved by XORing a known binary polynomial as a scrambler to the data stream in a feedback topology. PCI Express 3.0’s 8 GT/s bit rate effectively delivers 985 MB/s per lane, nearly doubling the lane bandwidth relative to PCI Express 2.0.

PCI Express 4.0

PCI Express 4.0 was officially announced on 2017, providing a 16 GT/s bit rate that doubles the bandwidth provided by PCI Express 3.0, while maintaining backward and forward compatibility in both software support and used mechanical interface. PCI Express 4.0 specs will also bring OCuLink-2, an alternative to Thunderbolt connector. OCuLink version 2 will have up to 16 GT/s (8 GB/s total for ×4 lanes), while the maximum bandwidth of a Thunderbolt 3 connector is 5 GB/s. Additionally, active and idle power optimizations are to be investigated.

Распайка LPT | Схемы компьютерного железа

LPT — параллельный порт, в современных устройствах почти не используется, до появления USB использовался для подключения принтеров и факсов к компьютеру.

Распиновка lpt порта

| N | Направление | Сигнал |

|---|---|---|

| 1 | Выход | Data Strobe |

| 2 | Выход | Data 0 |

| 3 | Выход | Data 1 |

| 4 | Выход | Data 2 |

| 5 | Выход | Data 3 |

| 6 | Выход | Data 4 |

| 7 | Выход | Data 5 |

| 8 | Выход | Data 6 |

| 9 | Выход | Data 7 |

| 10 | Вход | Acknowledge |

| 11 | Вход | Busy |

| 12 | Вход | Paper Out |

| 13 | Вход | Select |

| 14 | Выход | Auto feed |

| 15 | Вход | Error |

| 16 | Выход | Init |

| 17 | Выход | Select Input |

| 18-25 | Ground |

Распайка LPT