Сравнение основных характеристик ТТЛ и КМОП микросхем

Основной родовой признак ТТЛ — использование биполярных транзисторов, причем структуры только п-р-п. КМОП же, как следует из ее названия, основана на полевых транзисторах с изолированным затвором структуры МОП, причем комплементарных, то есть обоих полярностей — и с w- и с /^-каналом. Схемотехника базовых логических элементов ТТЛ и КМОП приведена на рис. 15.1. На западе их еще называют вентилями — чем можно оправдать такое название, мы увидим в конце главы.

Входной многоэмиттерный транзистор ТТЛ мы уже рисовали в главе И — он может иметь сколько угодно (на практике — до восьми) эмиттеров, и элемент тогда будет иметь соответствующее число входов. Если любой из эмиттеров транзистора VT1 замкнуть на «землю», то транзистор откроется, а фа-зорасщепляющий транзистор VT2 (с его работой мы знакомы по рис. 6.8) — закроется. Соответственно, выходной транзистор VT3 откроется, а VT4 — закроется, на выходе будет высокий логический уровень, или уровень логической единицы. Если же все эмиттеры присоединены к высокому потенциалу (или просто «висят» в воздухе), то ситуация будет обратная — VT2 откроется током через переход база-коллектор VT1 (такое включение транзистора называется «инверсным»), и на выходе установится ноль за счет открытого транзистора VT4. Такой ТТЛ-элемент будет осуществлять функцию «И-НЕ» (логический ноль на выходе только при единицах на всех входах).

ТТЛ

Выходной каскад ТТЛ-элемента представляет собой некое подобие комплементарного («пушпульного») каскада класса В, знакомого нам по аналоговым усилителям (см. рис. 8.2). Однако воспроизведение р-п-р-транзисторов оказалось для ТТЛ-технологии слишком сложным, потому такой каскад носит еще название псевдокомплементарного— верхний транзистор VT3 работает в режиме эмиттерного повторителя, а нижний — в схеме с общим эмиттером.

Рис. 15.1. Схемы базовых элементов ТТЛ и КМОП

Кстати, заметим, что из-за недоступности p-w-p-транзисторов воспроизведение схемы «ИЛИ» для ТТЛгтехнологии оказалось крепким орешком, и ее, схемотехника довольно существенно отличается от показанной на рис. 15.1 базовой схемы элемента «И-НЕ».

Заметки на полях

На заре транзисторной техники псевдокомплементарные каскады, подобные выходному каскаду ТТЛ, использовались — о ужас! — для усиления звука. Это построение дало основания для многочисленных попыток приспособить логические элементы, которые, в сущности, представляют собой усилитель с довольно большим (несколько десятков) коэффициентом усиления, для усиления аналоговых сигналов. Излишне говорить, что результаты оказались довольно плачевными, даже с КМОП-элементом, который построен куда более симметрично.

Как видно из схемы, ТТЛ-элемент существенно несимметричен и по входам, и по выходам. По входу напряжение логического нуля должно быть достаточно близко к «земле», при напряжении на эмиттере около 1,5 В (при стандартном для ТТЛ питании 5 В) входной транзистор уже запирается. Причем при подаче нуля нужно обеспечить отвод довольно значительного тока база-эмиттер— около 1,6 мА для стандартного элемента, отчего для элементов ТТЛ всегда оговаривается максимальное количество одновременно подсоединенных к выходу других таких элементов (стандартно — не более десятка). В то же время логическую единицу на входы можно не подавать вовсе. Практически, однако, подавать ее следует — по правилам незадействованные входы ТТЛ должны быть присоединены к питанию через резисторы 1 кОм.

Еще хуже дела обстоят на выходе: напряжение логического нуля обеспечивается открытым транзистором и действительно довольно близко к нулю — даже при нагрузке в виде десятка входов других таких же элементов оно не превышает 0,5 В, а в нормах на сигнал ТТЛ оговорена величина не более 0,8 В. А вот напряжение логической единицы довольно далеко отстоит от питания и составляет при питании 5 В в лучшем случае (без нагрузки) от 3,5 до 4 В, практически же в нормах оговаривается величина 2,4 В.

Такое балансирование десятыми вольта (напряжение нуля 0,8 В, напряжение порога переключения от 1,2 до 2 В, напряжение единицы 2,4 В) приводит к тому, что все ТТЛ-микросхемы могут работать в довольно узком диапазоне напряжений питания — практически от 4,5 до 5,5 В, многие даже от 4,75 до 5,25 В, то есть 5 В ±5%. Максимально допустимое напряжение питания составляет для разных ТТЛ-серий от 6 до 7 В, и при его превышении они обычно горят ясным пламенем. Низкий и несимметричный относительно питания порог срабатывания элемента приводит и к плохой помехоустойчивости.

Самым крупным (и даже более серьезным, чем остальные) недостатком ТТЛ является высокое потребление — до 2,5 мА на один такой элемент, это без учета вытекающих токов по входу и потребления нагрузки по выходу. Так что приходится только удивляться, почему микросхемы ТТЛ, содержащие много базовых элементов, вроде счетчиков или регистров, не требуют охлаждающего радиатора. Сочетание низкой помехоустойчивости с высоким потреблением — смесь довольно гремучая, и при разводке плат с ТТЛ-микросхемами приходится ставить по развязывающему конденсатору на каждый корпус. Все перечисленное в совокупности давно бы заставило отказаться от технологии ТТЛ вообще, однако у них до некоторого времени было одно неоспоримое преимущество: высокое быстродействие, которое для базового элемента в виде, показанном на рис. 15.1, может достигать десятков мегагерц.

В дальнейшем развитие ТТЛ шло по линии уменьшения потребления и улучшения электрических характеристик, в основном за счет использования т. н. переходов Шоттки, на которых падение напряжения может составлять 0,2—0,3 В вместо обычных 0,6—0,7 В (технология ТТЛШ, обозначается буквой S в наименовании серии, отечественный аналог— серии 531 и 530). Базовая технология, которая составляла основу широко распространенной в 1960—70-х годах серии 74 без дополнительных букв в обозначении (аналоги— знаменитые отечественные серии 155 и 133), сейчас практически не используется. ТТЛ-микросхемы в настоящее время можно выбирать из вариантов, представленных малопотребляющими сериями типа 74LSxx (серии 555 и 533) или быстродействующими типа 74Fxx (серия 1531). Причем потребление последних практически равно потреблению старых базовых серий при более высоком (до 125 МГц) быстродействии, а для первых все наоборот— быстродействие сохранено на уровне базового, зато потребление питания снижено раза в три-четыре.

КМОП

КМОП-элементы намного ближе к представлению о том, каким должен быть идеальный логический элемент. Для начала, как можно видеть из рис. 15.1, они практически симметричны, как по входу, так и по выходу. Открытый полевой транзистор на выходе (либо /?-типа для логической единицы, либо «-типа для логического нуля) фактически представляет собой, как мы знаем.

просто сопротивление, которое для обычных КМОП-элементов может составлять от 100 до 300 Ом (под «обычными» или «классическими» КМОП мы подразумеваем здесь серию 4000А или 4000В, см. далее). Для дополнительной симметрии на выходе обычно ставят последовательно два инвертора, подобных показанному на рис. 15.1 справа (жалко, что ли, транзисторов, если потребление не растет?). Поэтому на выходе не сказывается то, что в нижнем плече для схемы «И-НЕ» стоят два таких транзистора последовательно.

Для схемы «ИЛИ» такие транзисторы будут стоять в верхнем плече — она полностью симметрична схеме «И», что тоже плюс технологии КМОП по сравнению с ТТЛ. Обратите также внимание, что выходной каскад инвертора построен не по схеме «пушпульного» каскада, то есть это не потоковые повторители напряжения, а транзисторы в схеме с общим истоком, соединенные стоками, что позволяет получить дополнительный коэффициент усиления по напряжению.

На практике особенности построения элемента приводят к тому, что в КМОП-микросхемах:

? на ненагруженном выходе напряжение логической единицы практически равно напряжению питания, а напряжение логического нуля практически равно потенциалу «земли»;

? порог переключения близок к половине напряжения питания;

? входы практически не потребляют тока, так как представляют собой изолированные затворы МОП-транзисторов;

? в статическом режиме весь элемент также не потребляет тока от источника питания.

Из последнего положения вытекает, что схема любой степени сложности, построенная с помощью КМОП-элементов, в «застывшем» состоянии и даже при малых рабочих частотах, не превышающих десятка-другого килогерц, практически не потребляет энергии! Отсюда ясно, как стали возможными такие фокусы, как наручные часы, которые способны идти от малюсенькой батарейки годами, или sleep-режим микроконтроллеров, в котором они потребляют от 1 до 50 мкА на все десятки тысяч составляющих их логических элементов.

Другое следствие вышеперечисленных особенностей — исключительная помехоустойчивость, достигающая половины напряжения питания. Но это еще не все преимущества. КМОП-микросхемы «классических» серий могут работать в диапазоне напряжений питания от 2 до 18 В, а современные быстродействующие — от 2 до 7 В. Единственное, что при этом происходит— при

снижении питания довольно резко— в разы— падает быстродействие и ухудшаются некоторые другие характеристики.

Кроме того, выходные транзисторы КМОП, как и любые другие полевые транзисторы, при перегрузке (например, в режиме короткого замыкания) работают как источники тока — при напряжении питания 15 В этот ток составит около 30 мА, при 5 В — около 5 мА. Причем это в принципе может быть долгосрочный режим работы таких элементов, единственное, что при этом надо проверить — не превышается ли значение суммарного допустимого тока через вывод питания, которое обычно составляет около 50 мА. То есть, возможно, придется ограничить число выходов, одновременно подключенных к низкоомной нагрузке. Естественно, о логических уровнях в таком режиме уже речи не идет, только о втекающем или вытекающем токе.

И тут мы подходим к основному недостатку «классической» КМОП-технологии — низкому в сравнении ТТЛ быстродействию. Это обусловлено тем, что изолированный затвор МОП-транзистора представляет собой конденсатор довольно большой емкости— в базовом элементе до 10—15 пФ. В совокупности с выходным резистивным сопротивлением предыдущей схемы такой конденсатор образует фильтр низких частот. Обычно рассматривают не просто частотные свойства, а время задержки распространения сигнала на один логический элемент. Задержка возникает из-за того, что фронт сигнала не строго вертикальный, а наклонный, и напряжение на выходе еще только начнет нарастать (или снижаться), когда напряжение на входе достигнет уже значительной величины (в идеале— половины напряжения питания). Время задержки могло достигать у ранних серий КМОП величины 200—250 НС (сравните — у базовой серии ТТЛ всего 7,5 не). На практике при напряжении питания 5 В максимальная рабочая частота «классического» КМОП не превышает 1—3 МГц— попробуйте соорудить на логических элементах генератор прямоугольных сигналов по любой из схем, которые будут разобраны в главе 16, и вы увидите, что уже при частоте 1 МГц форма сигнала будет скорее напоминать синусоиду, чем прямоугольник.

Другим следствием наличия высокой входной емкости является то, что при переключении возникает импульс тока перезарядки этой емкости, то есть чем выше рабочая частота, тем больше потребляет микросхема, и считается, что при максимальных рабочих частотах ее потребление может сравниться с потреблением ТТЛ (по крайней мере, ТТЛ серии 74LS). Дело еще усугубляется тем, что из-за затянутых фронтов импульсов элемент достаточно длительное время находится в активном состоянии, когда оба выходных транзистора приоткрыты (то есть возникает так называемый эффект «сквозного тока»).

Это же затягивание фронтов в сочетании с высокоомным входом приводит к снижению помехоустойчивости при перею1ючении — если на фронте сигнала «сидит» высокочастотная помеха, то это может приводить к многократным переключениям выхода, как это было у компаратора (см. главу 13). По этой причине в спецификациях на микросхемы часто указывают желательную максимальную длительность фронтов управляющего сигнала.

Однако в современных КМОП, в отличие от «классических», большинство недостатков, связанных с низким быстродействием, удалось преодолеть (правда, за счет снижения допустимого диапазона питания). Подробнее о сериях КМОП рассказано далее, а пока несколько еще несколько слов об особенностях этих микросхем.

Незадействованные входы элемента КМОП нужно обязательно подключать куда-нибудь — либо к земле, либо к питанию (резисторов при этом не требуется, так как вход тока не потребляет), либо объединять с соседним входом — иначе наводки на столь высокоомном входе полностью нарушат работу схемы. Причем в целях снижения потребления следует делать это и по отношению к незадействованным элементам в том же корпусе (но не ко всем незадействованным выводам, конечно). «Голый» вход КМОП из-за своей вы-сокоомности может быть также причиной повышенной «смертности» чипов при воздействии статического электричества, однако на практике входы всегда шунтируют диодами, как показано на рис. 11.4. Допустимый ток через эти диоды также оговаривается в спецификациях.

Логические уровни кмоп микросхем

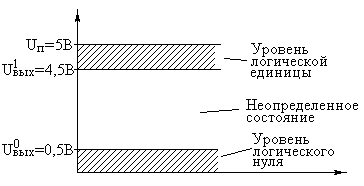

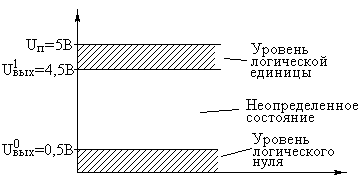

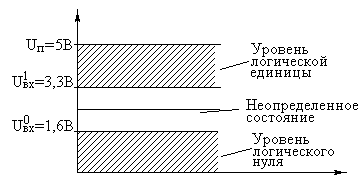

Логические уровни КМОП микросхем при пятивольтовом питании показаны на рис.9.

Рис.9.

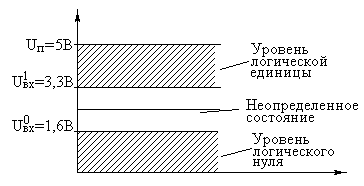

Границы уровней логического нуля и единицы для КМОП микросхем при пятивольтовом питании приведена на рис. 10.

Рис. 10. Уровни логических сигналов на входе цифровых КМОП микросхем.

Из рисунка 10 видно, что запас по уровням срабатывания для обеспечения помехоустойчивости у КМОП более 1,1 В. Это почти втрое больше чем у ТТЛ.

При уменьшении напряжения питания границы логического нуля и логической единицы смещаются пропорционально изменению напряжения питания.

Семейства кмоп микросхем

Первые КМОП микросхемы не имели защитных диодов на входе, поэтому их монтаж представлял значительные трудности. Это семейство микросхем серии К172. Следующее улучшенное семейство микросхем серии К176 получило эти защитные диоды. Оно достаточно распространено и в настоящее время. Серия К1561 (иностранный аналог этих микросхем — C4000В.) завершает развитие первого поколения КМОП микросхем. В этом семействе было достигнуто быстродействие на уровне 90нс и диапазон изменения напряжения питания 3..15В.

Дальнейшим развитием КМОП микросхем стала серия SN74HC. Эти микросхемы отечественного аналога не имеют. Они обладают быстродействием 27нс и могут работать в диапазоне напряжений 2..6В. Они совпадают по цоколёвке и функциональному ряду с ТТЛ микросхемами, но не совместимы с ними по логическим уровням, поэтому одновременно были разработаны микросхемы серии SN74HCT (отечественный аналог — К1564), совместимые с ТТЛ микросхемами и по логическим уровням.

В это время наметился переход на трёхвольтовое питание. Для него были разработаны микросхемы SN74ALVC с временем задержки сигнала 5,5нс и диапазоном питания 1,65..3,6В. Эти же микросхемы способны работать и при 2,5 вольтовом питании. Время задержки сигнала при этом увеличивается до 9нс.

Наиболее перспективным семейством КМОП микросхем считается семейство SN74AUC с временем задержки сигнала 1,9нс и диапазоном питания 0,8..2,7В.

Цифровые микросхемы эмиттерно-связанной логики Общие сведения об эсл имс

Интегральные микросхемы на основе эмиттерно-связанной логики (ЭСЛ) получили широкое распространение в качестве элементной базы быстродействующей вычислительной и радиоэлектронной аппаратуры. Микросхемы на основе ЭСЛ имеют ряд достоинств, которые обеспечили их преимущество перед другими микросхемами при построении данного класса аппаратуры:

1. Хорошая схемно-техническая отработанность и, как следствие, сравнительно невысокая стоимость при изготовлении.

Высокое быстродействие при средней потребляемой мощности или сверхвысокое быстродействие при большой потребляемой мощности.

Малая энергия переключения.

Высокая относительная помехоустойчивость.

Высокая стабильность динамических параметров при изменении рабочей температуры и напряжения питания.

Большая нагрузочная способность.

Независимость тока потребления от частоты переключения.

Способность ИМС работать на низкоомные линии связи и нагрузки.

Широкий функциональный набор микросхем.

10. Удобство применения в условиях повышенной плотности компоновки с использованием многослойного печатного монтажа и низкоомных коаксиальных и плоских кабелей.

В настоящее время ИС ЭСЛ являются самыми быстродействующими микросхемами на основе кремния, выпускаемыми промышленностью как у нас в стране, так и за рубежом. Опыт проектирования аппаратуры, показывает, что применение ИС ЭСЛ оптимально для построения быстродействующих радиоэлектронных устройств, в частности ЭВМ высокого быстродействия, и менее эффективно при разработке радиоэлектронных устройств малого и среднего быстродействия.

Высокое быстродействие обусловлено тем, что в этих элементах транзисторы работают в ненасыщенном режиме, в результате чего исключается накопление и рассасывание неосновных носителем заряда.

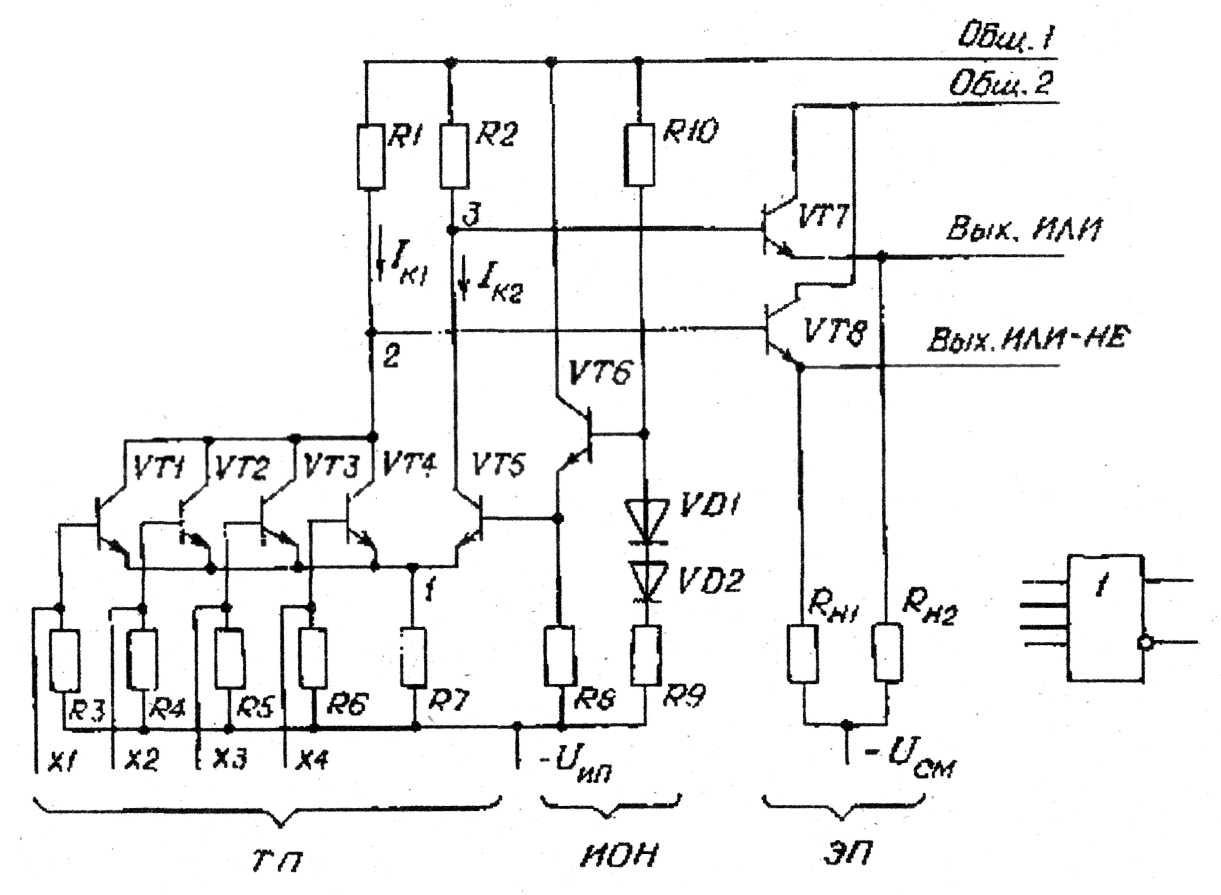

Структурно базовый элемент ЭСЛ содержит: источник опорного напряжения (ИОН), токовый переключатель (ТП) и эмиттерные повторители.

В основу токового переключателя на входе положена схема с объединенными эмиттерами (рис.11). Главные ее достоинства: постоянство суммарного тока эмиттеров /э= 1э1+ I э2 в процессе работы; наличие прямого и инверсного выходов Uвых1, Uвых2.

Рис. 11. Базовый логический элемент ЭСЛ

К современным цифровым микросхемам ЭСЛ относятся ИС серий 100, К100, 500, К500, 1500, KI500.

Типовое время задержки логических элементов ИМС серии К1550 0,7 нс, серии К500 0,5…2 нс; серии 138 2,9 нс. ЭСЛ микросхемы имеют помехоустойчивость по напряжению низкого и высокого уровней не менее 125 мВ и 150 мВ, разброс выходного напряжения низкого уровня 145…150 мВ, высокого уровня 200 мВ. Амплитуда логического сигнала Uл до 800 мВ. В ИМС серии 500 уровень интеграции до 80 логических элементов на кристалле; функциональный набор микросхем — 48 модификаций, потребляемая элементом мощность Рпот=8…25мВт (в ненагруженном состоянии), энергия, потребляемая при переключении А = 50 пДж.

Базовый логический элемент ИМС К500 благодаря наличию прямого и инверсного выхода одновременно выполняет две функций: ИЛИ-НЕ и ИЛИ. В отрицательной логике выполняются функции И/И-НЕ. Электрическая схема базового элемента ЭСЛ состоит из трех цепей (рис.12): токового переключателя (ТП), выходных эмиттерных повторителей (ЭП) и источника опорного напряжения (ИОН).

Токовый переключатель построен на транзисторах VT1—VT5 и резисторах R1-R7 и представляет собой дифференциальный усилитель, работающий в режиме ключа, имеющий несколько входов. Увеличение числа входов ТП достигается параллельным подключением дополнительных входных транзисторов VT1—VT4.

Рис. 12

Базовый ЛЭ работает следующим образом. При подаче на все входы схемы XI—X4 напряжения низкого уровня (-1,7 В) входные транзисторы VT1-VT4 закрыты, транзистор VT5 открыт, так как напряжение на его базе UОП = -1,3 В выше.

Большая потребляемая и рассеиваемая мощности являются недостатками микросхем ЭСЛ, что является следствием их работы в ненасыщенном режиме. Малый логический перепад, с одной стороны, повышает быстродействие, а с другой снижает помехоустойчивость.

Сопряжение логических КМОП и ТТЛ элементов

Иногда в одних и тех же устройствах приходится по тем или иным соображениям применять элементы разных схемотехнологических типов. Наиболее часто встречающаяся ситуация – одновременное использование элементов ТТЛ и КМОП. Так как ТТЛ и ТТЛШ близки по параметрам и схемотехнике, будем рассматривать только ТТЛ, как представителя от этих обоих семейств. Знание входных и выходных характеристик логического семейства необходимо для организации любых взаимосвязей с внешним миром.

Входные и выходные характеристики элементов ТТЛ и КМОП. Все цифровые логические семейства строятся таким образом, чтобы к выходу каждого элемента можно было подключить большое число входов, принадлежащих элементам того же семейства. Типичное значение коэффициента разветвления по выходу равно 10. Это означает, что к выходу, например, вентиля или триггера без нарушения технических требований можно подсоединить 10 входов.

Другими словами, в обычной практике цифровых разработок можно обходиться без каких-либо сведений, касающихся электрических свойств используемых кристаллов. Это возможно до тех пор, пока схема состоит только из цифровых логических элементов одного и того же семейства и фактически нечасто приходится думать о том, что же в действительности происходит на логических входах и выходах.

Однако как только необходимо управлять цифровыми схемами при помощи внешних сигналов, аналоговых или цифровых, или же использовать выходы цифровой логики для управления другими устройствами, придется выяснить, что в действительности потребляет логический вход и чем может нагружаться логический выход. Кроме того, при объединении логических семейств надо знать схемотехнические свойства входов и выходов.

Между микросхемами возможны три возможных типа несовместимости логических семейств: либо ИС-приемник управляется слишком высоким напряжением, либо ИС-источник не обеспечивает достаточно высокое напряжение, которое достоверно распознавалось бы ИС-приемником как сигнал высокого логического уровня, либо ИС-источник не может обеспечить необходимого тока для управления ИС-приемником.

Для того чтобы воспользоваться современными, все более доступными БИС, выполненными по МОП-технологии, необходимо знать, каким образом объединяются логические схемы различных типов. В последующих разделах подробно рассматриваются схемотехнические свойства логических входов и выходов и приводятся примеры сопряжения, как между разными логическими семействами, так и между логическими устройствами и внешним миром.

Входные характеристики. На рисунке 19.1 показаны важные характеристики входов ТТЛ и КМОП – зависимости входных токов от входных напряжений. По оси входного напряжения графики расширены за пределы диапазона, встречающегося в чисто цифровых схемах, так как при сопряжении схем значения входных сигналов могут легко превысить напряжение питания.

Когда на вход элемента ТТЛ подается низкий уровень, он действует как источник тока заметной величины, а при высоком уровне – как нагрузка, потребляющая малый ток (до 40 мкА). Входной ток высокого уровня фактически представляет собой коллекторный ток «инверсного» выходного транзистора VT3 (рис. 20.11). Для правильного управления входом элемента ТТЛ необходимо обеспечить отвод тока порядка 1 мА при уровне входного напряжения не более 0.4 В. Недопонимание этого условия часто приводит к неправильной работе элемента в интерфейсной схеме.

Для отрицательных напряжений вход ТТЛ действует как фиксирующий диод, включенный на землю, а для напряжений выше +5 В вход эквивалентен транзистору с небольшим напряжением пробоя (несколько выше +5,5 В).

У элементов КМОП отсутствует входной ток при входных напряжениях в диапазоне от 0 до EПИТ (за исключением тока утечки). Для сигналов, превышающих диапазон напряжений питания, вход микросхемы представляет собой два фиксирующих диода, один из которых подключен к положительному полюсу источника, а второй – к земле (рис. 19.2).

Эти входные диоды защищают элементы КМОП, которые крайне подвержены повреждениям от статического электричества.

Выходные характеристики. Выходная схема вентиля ТТЛ содержит n-p-n-транзистор, включенный на землю, и n-p-n-повторитель, подключенный к шине EПИТ с токоограничивающим резистором в коллекторной цепи, а иногда диодом, включенным последовательно с эмиттером (рис. 20.10). Когда один из транзисторов насыщен, другой закрыт. В результате элемент ТТЛ может отводить на землю значительный ток (до 16 мА) при небольшом падении напряжения (насыщение), а при высоком уровне на выходе (около +3,5 В) может служить источником тока порядка нескольких миллиампер. Схема выхода предназначена для управления входами ТТЛ и имеет коэффициент разветвления по выходу 10.

Рис. 19.2. Модель КМОП вентиля для больших входных сигналов

Выходная схема элемента КМОП представляет собой двухтактную пару комплементарных полевых МОП-транзисторов, один из которых открыт, а другой закрыт (рис. 19.2). При малых токах выходная схема ведет себя как резистор в несколько сотен Ом, подключенный к земле или к шине EПИТ, а при выходных токах, для которых выходное напряжение приблизительно на 1В отличается от EПИТ, выход в известном смысле превращается в «источник тока». Суммарные выходные характеристики представлены на рисунке 19.3.

Рис. 19.3. Выходные характеристики логических вентилей

Здесь приведены зависимости выходного напряжения от выходного тока для обоих состояний – высокого и низкого. Для упрощения рисунка выходной ток показан положительным. Заметим, что в элементах КМОП выходы в любом случае подключены либо к земле, либо к шине EПИТ, что обеспечивает при отсутствии перегрузки полный перепад напряжения питания.

При нормальном использовании выходы КМОП управляют входами КМОП. Так как входной ток отсутствует (за исключением токов заряда небольшой входной емкости), на выходах происходит полный перепад до EПИТ или до нуля. Для сравнения отметим, что уровни ТТЛ в типичном случае составляют 50…200 мВ (низкий) или 3,5 В (высокий), если в качестве нагрузки используются также элементы ТТЛ. При включении нагрузочного резистора (почти любого номинала) высокий уровень на выходе элемента ТТЛ приближается к 5 В.

Сопряжение ТТЛ и КМОП. Для того чтобы не испытывать затруднений при работе с обоими семействами, нужно знать, как элементы этих семейств стыкуются друг с другом.

На элементах КМОП реализованы некоторые функции, которых нет на ТТЛ. Имея систему на элементах ТТЛ, работающую с невысокой скоростью, без труда можно добавить к ней некоторые функции, выполняемые на элементах КМОП. Кроме того, для облегчения стыковки с внешними устройствами, совместимыми с ТТЛ, а также при согласовании логической КМОП-схемы с кабелем на входах и выходах бывает полезно использовать буферные элементы ТТЛ. Для согласования ТТЛ и КМОП также применяются преобразователи уровня, описанные в п. 20.9.

Управление КМОП от ТТЛ. Если элемент КМОП работает от напряжения +5 В, то уровни почти совместимы. Единственная трудность заключается в том, что высокий уровень ТТЛ (типичное значение 3,4 В) является граничным для КМОП и желательно, чтобы он был не ниже 3,4 В. Однако достаточно подключить к выходу ТТЛ подтягивающий резистор (например, 5 кОм, что эквивалентно нагрузке одним элементом ТТЛ), соединенный с шиной EПИТ, выходное напряжение будет практически равно 5 В (рис. 19.4, а). Резисторы можно устанавливать как на выходах с открытым коллектором, так и с активной нагрузкой. Если элемент КМОП работает от более высокого напряжения питания, можно также включить нагрузочный резистор, но для этого нужно использовать «высоковольтные» кристаллы ТТЛ, имеющие выходы с открытым коллектором.

Другой способ заключается в использовании преобразователя уровня КМОП типа 40109, на вход которого подаются сигналы относительно источника EПИТ1 (уровни ТТЛ), а на выходе формируются сигналы с уровнями КМОП относительно второго источника EПИТ2 (рисунок 19.4, б).

Для того чтобы схема ТТЛ могла управлять элементом КМОП, работающим от источника напряжением EПИТ > 5 В, контактный вывод EПИТ1 соединяется с источником питания ТТЛ (5В), а вывод EПИТ2 подключается к источнику питания КМОП. Как и прежде, на стандартных выходах ТТЛ надо устанавливать нагрузочные резисторы.

Рис. 19.4. Преобразование уровня от ТТЛ к КМОП

Управление ТТЛ от КМОП. Если элемент КМОП питается от источника напряжения +5 В, то его можно непосредственно нагрузить одним элементом ТТЛ. От буферных схем КМОП типа КР1561ПУ4 (шесть инверторов) можно при подключении ее входов к выходам КМОП-микросхем подключать к каждому из ее выходов от двух до восьми микросхем ТТЛ в зависимости от их схемотехнической реализации. При питании элементов КМОП более высоким напряжением также существует несколько способов сопряжения. В первом методе можно использовать схемы 4049/4050 (рис. 19.5 а). Для этих ИМС допускается превышение входными уровнями напряжения питания, поэтому контакты EПИТ можно соединять непосредственно с цепью +5В. Это позволит обеспечить на выходе перепад напряжения от нуля до +5 В и даст возможность подключать к нему до восьми элементов ТТЛ.

Рис. 19.5. Преобразование от КМОП к ТТЛ

Логика на комплементарных моп транзисторах (кмдп)

Микросхемы на комплементарных транзисторах строятся на основе МОП транзисторов с n- и p-каналами. Один и тот же потенциал открывает транзистор с n-каналом и закрывает транзистор с p-каналом. При формировании логической единицы открыт верхний транзистор, а нижний закрыт. В результате ток через микросхему не протекает. При формировании логического нуля открыт нижний транзистор, а верхний закрыт. И в этом случае ток через микросхему не протекает. Простейший логический элемент — это инвертор. Его схема приведена на рисунке 1.

Рисунок 1. Принципиальная схема инвертора, выполненного на комплементарных МОП транзисторах.

На этой схеме для упрощения понимания принципов работы микросхемы не показаны защитные и паразитные диоды. Особенностью микросхем на комплементарных МОП транзисторах является то, что в этих микросхемах в статическом режиме ток практически не потребляется. Потребление тока происходит только в момент переключения микросхемы из единичного состояния в нулевое и наоборот. Этим током производится перезаряд паразитной ёмкости нагрузки.

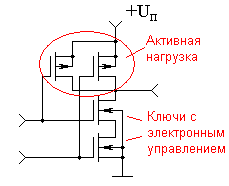

Схема логического элемента «И-НЕ» на КМОП микросхемах практически совпадает с упрощенной схемой «И» на ключах с электронным управлением, которую мы рассматривали ранее. Отличие заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику питания. Принципиальная схема элемента «2И-НЕ», выполненного на комплементарных МОП транзисторах приведена на рисунке 2.

Рисунок 2. Принципиальная схема элемента «2И-НЕ», выполненного на комплементарных МОП транзисторах.

В этой схеме можно было бы применить в верхнем плече обыкновенный резистор, однако при формировании низкого уровня схема постоянно потребляла бы ток. Вместо этого, в качестве нагрузки используются p-МОП транзисторы. Эти транзисторы образуют активную нагрузку. Если на выходе требуется сформировать высокий потенциал, то транзисторы открываются, а если низкий — то закрываются.

В приведённой на рисунке 2 схеме ток от источника питания на выход микросхемы будет поступать через один из транзисторов, если хотя бы на одном из входов (или на обоих сразу) будет присутствовать низкий потенциал (уровень логического нуля). Если же на обоих входах будет присутствовать уровень логической единицы, то оба p-МОП транзистора будут закрыты и на выходе микросхемы сформируется низкий потенциал. В этой схеме, так же как и в схеме на рисунке 1, если транзисторы верхнего плеча будут открыты, то транзисторы нижнего плеча будут закрыты, поэтому в статическом состоянии ток микросхемой от источника питания потребляться не будет.

Условно-графическое изображение такого логического элемента показано на рисунке 3, а таблица истинности приведена в таблице 1. В таблице 1 входы обозначены как x1 и x2, а выход — F.

Рисунок 3. Условно-графическое изображение элемента «2И-НЕ».

Таблица 1. Таблица истинности схемы, выполняющей логическую функцию «2И-НЕ»

x1 | x2 | F |

0 | 0 | 1 |

0 | 1 | 1 |

1 | 0 | 1 |

1 | 1 | 0 |

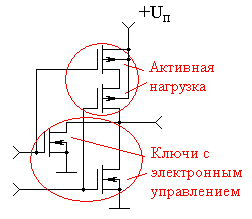

Логический элемент «ИЛИ-НЕ», выполненный на КМОП транзисторах, представляет собой параллельное соединение ключей с электронным управлением. Отличие от схемы «2ИЛИ», рассмотренной ранее, заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику питания. Вместо резистора в качестве нагрузки используются p-МОП транзисторы. Принципиальная схема элемента «2ИЛИ-НЕ», выполненного на комплементарных МОП транзисторах приведена на рисунке 4.

Рисунок 4. Принципиальная схема элемента «2ИЛИ-НЕ», выполненного на комплементарных МОП транзисторах.

В схеме логического элемента «2ИЛИ-НЕ» в качестве нагрузки используются последовательно включенные p-МОП транзисторы. В ней ток от источника питания на выход микросхемы будет поступать только если все транзистора в верхнем плече будут открыты, т.е. если сразу на всех входах будет присутствовать низкий потенциал (уровень логического нуля). Если же хотя бы на одном из входов будет присутствовать уровень логической единицы, то верхнее плечо будет закрыто и ток от источника питания поступать на выход микросхемы не будет.

Таблица истинности, реализуемая этой схемой, приведена в таблице 2, а условно-графическое обозначение этих элементов приведено на рисунке 5.

Рисунок 5. Условно-графическое изображение элемента «2ИЛИ-НЕ».

Таблица 2. Таблица истинности схемы, выполняющей логическую функцию «2ИЛИ-НЕ»

x1 | x2 | F |

0 | 0 | 1 |

0 | 1 | 0 |

1 | 0 | 0 |

1 | 1 | 0 |

В настоящее время именно КМОП микросхемы получили наибольшее развитие. Причём наблюдается постоянная тенденция к снижению напряжения питания. Первые серии микросхем такие как К1561 (иностранный аналог C4000В) обладали достаточно широким диапазоном изменения напряжения питания (3..18В). При этом при понижении напряжения питания у конкретной микросхемы понижается её предельная частота работы. В дальнейшем, по мере совершенствования технологии производства, появились улучшенные микросхемы с лучшими частотными свойствами и меньшим напряжением питания.

Особенности применения КМОП микросхем

Первой и основной особенностью КМОП микросхем является большое входное сопротивление этих микросхем. В результате на вход этой цифровой микросхемы может наводиться любое напряжение, в том числе и равное половине напряжения питания, и храниться на нём достаточно долго. При подаче на вход КМОП микросхемы половины питания открываются транзисторы как в верхнем, так и в нижнем плече выходного каскада микросхемы, в результате микросхема начинает потреблять недопустимо большой ток и может выйти из строя. Вывод: входы цифровых микросхем ни в коем случае нельзя оставлять неподключенными!

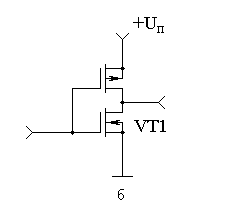

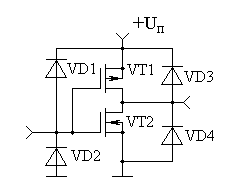

Второй особенностью КМОП микросхем является то, что они могут работать при отключенном питании. Однако работают они чаще всего неправильно. Эта особенность связана с конструкцией входного каскада КМОП микросхем. Полная схема КМОП инвертора приведена на рисунке 6.

Рисунок 6. Полная схема КМОП инвертора.

Диоды VD1 и VD2 были введены для защиты входного каскада от пробоя статическим электричеством. В то же самое время при подаче на вход микросхемы высокого потенциала он через диод VD1 попадёт на шину питания микросхемы, и так как она потребляет достаточно малый ток, то микросхема начнёт работать. Однако в ряде случаев тока может не хватить. В результате микросхема может работать неправильно. Вывод: при неправильной работе микросхемы тщательно проверьте питание микросхемы, особенно выводы корпуса. При плохо пропаянном выводе отрицательного питания его потенциал будет отличаться от потенциала общего провода схемы.

Третья особенность КМОП микросхем связана с паразитными диодами VD3 и VD4, которые могут быть пробиты при неправильно подключенном источнике питания (микросхемы ТТЛ выдерживают кратковременную переполюсовку питания). Для защиты микросхем от переполюсовки питания следует в цепи питания предусмотреть защитный диод.

Четвёртая особенность КМОП микросхем — это протекание импульсного тока по цепи питания при переключении микросхемы из нулевого состояния в единичное и наоборот. В результате при переходе с ТТЛ микросхем на КМОП резко увеличивается уровень помех. В ряде случаев это важно и приходится отказываться от применения КМОП микросхем в пользу ТТЛ или BICMOS.

Логические уровни КМОП микросхем

Логические уровни КМОП микросхем существенно отличаются от логических уровней ТТЛ микросхем. При отсутствии тока нагрузки напряжение на выходе КМОП микросхемы совпадает с напряжением питания (логический уровень единицы) или с потенциалом общего провода (логический уровень нуля). При увеличении тока нагрузки напряжение логической единицы может уменьшается до 2,8В (Uп=15В) от напряжения питания. Допустимый уровень напряжения на выходе цифровой КМОП микросхемы (серия микросхем К561) при пятивольтовом питании показан на рисунке 7.

Рисунок 7. Уровни логических сигналов на выходе цифровых КМОП микросхем.

Как уже говорилось ранее, напряжение на входе цифровой микросхемы по сравнению с выходом обычно допускается в больших пределах. Для КМОП микросхем договорились о 30% запасе. Границы уровней логического нуля и единицы для КМОП микросхем при пятивольтовом питании приведена на рисунке 8.

Рисунок 8. Уровни логических сигналов на входе цифровых КМОП микросхем.

При уменьшении напряжения питания границы логического нуля и логической единицы можно определить точно так же (разделить напряжение питания на 3).

Семейства КМОП микросхем

Первые КМОП микросхемы не имели защитных диодов на входе, поэтому их монтаж представлял значительные трудности. Это семейство микросхем серии К172. Следующее улучшенное семейство микросхем серии К176 получило эти защитные диоды. Оно достаточно распространено и в настоящее время. Серия К1561 завершает развитие первого поколения КМОП микросхем. В этом семействе было достигнуто быстродействие на уровне 90нс и диапазон изменения напряжения питания 3..15В. Так как в настоящее время распространена иностранная аппаратура, то приведу иностранный аналог этих микросхем — C4000В.

Дальнейшим развитием КМОП микросхем стала серия SN74HC. Эти микросхемы отечественного аналога не имеют. Они обладают быстродействием 27нс и могут работать в диапазоне напряжений 2..6В. Они совпадают по цоколёвке и функциональному ряду с ТТЛ микросхемами, но не совместимы с ними по логическим уровням, поэтому одновременно были разработаны микросхемы серии SN74HCT (отечественный аналог — К1564), совместимые с ТТЛ микросхемами и по логическим уровням.

В это время наметился переход на трёхвольтовое питание. Для него были разработаны микросхемы SN74ALVC с временем задержки сигнала 5,5нс и диапазоном питания 1,65..3,6В. Эти же микросхемы способны работать и при 2,5 вольтовом питании. Время задержки сигнала при этом увеличивается до 9нс.

Наиболее перспективным семейством КМОП микросхем считается семейство SN74AUC с временем задержки сигнала 1,9нс и диапазоном питания 0,8..2,7В.

Часто бывает необходимо подобрать серию микросхем логики под определенные требования — энергопотребление, предельная рабочая частота, уровни напряжений логики и питания, нагрузочная способность и т. д. Так же проблемой бывает подобрать отечественный аналог для импортной микросхемы, и наоборот. В этой статье сделана попытка предоставить такую информацию. Параметры серий обобщенно закодированы в названиях серий: HCT, ALS, F, LVC и т. п. Для начала давайте разберемся, что обозначают буквы, составляющие название серий. К сожалению, это общие обозначения, смысл букв иногда может меняться, потому что многие серии являются одновременно и торговыми марками производителей микросхем. A — advanced, т. е. улучшенный, продвинутый. Показывает, что эта серия основана на базовой, с улучшением каких-то параметров (обычно это скорость работы и уменьшение энергопотребления). Примеры: AC — семейство Advanced CMOS. С помощью таблицы быстрого выбора, размещенной ниже выберите самый важный для Вас параметр — скорость переключения, минимальное потребление, нагрузочная способность, устойчивость к помехам — и определите, какое семейство больше подходит. Затем с помощью дополнительной справочной информации уточните Ваш выбор. Таблица 1. Быстрый выбор серии микросхем (основные характеристики серий).

Обозначения: High Speed высокая скорость. Рис. 1. Эволюция развития серий микросхем логики. Таблица 2. Общее описание возможностей различных серий.

Примечания: (1) CROSSVOLT™, марка FAIRCHILD Semiconductor. Параметр задержки распространения сигнала вместе с временем нарастания и спада на выходе определяют максимальную рабочую частоту серии. Таблица 3. Величина задержки распространения сигнала(1). Примечания: (1) Даны максимальные значения из даташита на указанные модели микросхем. Таблица 4. Время нарастания и спада уровня(1). Примечания: (1) Даны значения для логики ‘244, емкость нагрузки CLOAD = 50 пФ, сопротивление нагрузки RL = 500 Ω. Таблица 5. Уровень генерируемого шума(1). VOLP уровень положительного выброса, VOLV уровень отрицательного выброса. Примечания: (1) Даны значения для логики ‘244, емкость нагрузки CLOAD = 50 пФ, сопротивление нагрузки RL = 500 Ω, типовые значения сопротивлений для 4.5V, переключение семи выходов, минимальный наклон перепадов на входе. Таблица 6. Динамическое потребление тока (мА)(1).

Примечание (1): даны значения для логики ‘244, емкость нагрузки CLOAD = 50 пФ. Все значения представляют типовые параметры. Рис. 2. Различные серии микросхем преобразователей уровней. Примечания: † Устройства с автоматическим определением направления передачи данных не требуют для этого специальных выводов управления. Таблица 7. Сравнение параметров семейств.

Примечания: * Для примеров применялась логика функции ’244, если не указано нечто другое. Ниже приведена сравнительная таблица размеров и параметров корпусов различного типа. Примечание (1): в скобках приведены коды корпусов компании FAIRCHILD Semiconductor. [Ссылки] 1. Logic Selection Guide site:fairchildsemi.com. | |||||||

Эмиттерно-связанная логика — Википедия

Материал из Википедии — свободной энциклопедии

Текущая версия страницы пока не проверялась опытными участниками и может значительно отличаться от версии, проверенной 6 августа 2017; проверки требуют 11 правок. Текущая версия страницы пока не проверялась опытными участниками и может значительно отличаться от версии, проверенной 6 августа 2017; проверки требуют 11 правок. Типичная схема (4ИЛИ/ИЛИ-НЕ).Эми́ттерно-свя́занная ло́гика (ЭСЛ, ECL) — способ построения логических элементов на основе дифференциальных транзисторных каскадов. ЭСЛ является самой быстродействующей из всех типов логики, построенной на биполярных транзисторах. Это объясняется тем, что транзисторы в ЭСЛ работают в линейном режиме, не переходя в режим насыщения, выход из которого замедлен. Низкие значения логических перепадов в ЭСЛ-логике способствуют снижению влияния на быстродействие паразитных ёмкостей[1].

Основная деталь ЭСЛ-логики — схема потенциального сравнения, собранная не на диодах (как в ДТЛ), а на транзисторах. Схема представляет собой транзисторы, соединённые эмиттерами и подключенные к корпусу (или питанию) через резистор. При этом транзистор, у которого напряжение на базе выше, пропускает через себя основной ток. Как правило, один транзистор в схеме сравнения подключен к опорному уровню, равному напряжению логического порога, а остальные транзисторы являются входами. Выходные цепи схемы сравнения поступают на усилительные транзисторы, а с них — на выходные эмиттерные повторители.

Особенностью ЭСЛ является повышенные скорость (150 МГц уже в первых образцах 1960-х годов и 0,5…2 ГГц в 1970-1980-х) и энергопотребление по сравнению с ТТЛ и КМОП (на низких частотах, на высоких — примерно равное), низкая помехоустойчивость, низкая степень интеграции (ограниченная, в частности, большой потребляемой мощностью каждого элемента, что не позволяет разместить в одном корпусе много элементов, так как это приведёт к перегреву) и как следствие — высокая стоимость.

«Переключатель тока» Хэнона Йорка (1955 г.)[2]ЭСЛ была изобретена в августе 1956 года инженером IBM Хэноном Йорком (англ. Hannon S. Yourke)[3][4]. Первоначально имела название «управляемая током логика», применялась в компьютерах Stretch, IBM 7090, и IBM 7094[2]. Также использовалось название схема токового режима[5].

Переключатель тока Йорка представлял собой дифференциальный усилитель, в котором входные логические уровни сигналов отличались от выходных[5]. В схеме Йорка отличие опорных уровней напряжения составляло 3 вольта. В связи с этим использовались две взаимодополняющих версии логических элементов: NPN и PNP. Выход NPN версии мог управлять входами PNP версии и наоборот. Недостатками схемы являлись использование дополнительных источников напряжения и использование как PNP, так и NPN транзисторов[2].

Позже, вместо чередования NPN и PNP версий логических элементов, был предложен метод с использованием стабилитронов и резисторов для сдвига выходных логических уровней к значениям входных логических уровней[5]. В ЭВМ БЭСМ-6 для этой же цели в состав переключателя тока был введён вторичный источник электропитания на основе трансформатора и двухполупериодного выпрямителя со средней точкой, названный «подвешенным источником питания»[6].

С появлением цифровых интегральных микросхем ЭСЛ логики для сдвига выходных логических уровней стал использоваться эмиттерный повторитель, также обеспечивающий повышение коэффициента разветвления.

Первая серия микросхем ЭСЛ логики, MECL I, была представлена фирмой Motorola в 1962 году[7]. Motorola разработала улучшенные серии MECL II в 1966 году и MECL III в 1968 году. MECL III обладала задержкой распространения сигнала в 1 наносекунду и частотой переключения триггеров до 500 МГц. В 1971 году выпущена серия 10000 с пониженным энергопотреблением и быстродействием[7].

Высокое энергопотребление ЭСЛ ограничило её применение только в схемах, где было важно максимальное быстродействие. ЭСЛ применялась в мейнфреймах IBM серии IBM System/390[8], суперкомпьютере Cray-1[9], первом поколении мейнфреймов Amdahl, ЕС ЭВМ ряда 2, ЭВМ «Эльбрус-2».

Серии микросхем отечественного производства:

- 137, 187, 229 — совместимые серии, 137 отличается более высоким быстродействием, 187 — меньшей потребляемой мощностью. Давно устарели.

- 138 — серия с лучшими параметрами, чем 137, 187. Устарела с появлением серий 100 и 500.

- 100, 500, 700 — это одна и та же серия в плоских корпусах (100), DIP-корпусах (500), бескорпусная для гибридных микросхем (700). Аналог серии Motorola 10000.

- 1500 — серия с субнаносекундным быстродействием, использовалась в ЭВМ «Эльбрус-2».

- 1590 — последняя отечественная серия ЭСЛ-логики, аналоги серии Motorola MC10Hxxx. По сравнению с предыдущей, 1500ой серией, при том же быстродействии энергопотребление снижено примерно втрое.

- 1800 — разрядно-модульный микропроцессорный комплект, некоторые микросхемы использовались в ЭВМ серии ЕС

- ↑ С.В. Якубовский, Л.И. Ниссельсон, В.И. Кулешова и др. Цифровые и аналоговые интегральные микросхемы: Справочник / под ред. С.В. Якубовского. — М: Радио и связь, 1990. — С. 496. — ISBN 5-256-00259-7.

- ↑ 1 2 3 E. J. Rymaszewski et al. Semiconductor Logic Technology in IBM // IBM Journal of Research and Development. — 1981. — Т. 25, вып. 5. — С. 607–608. — ISSN 0018-8646. — doi:10.1147/rd.255.0603. Архивировано 5 июля 2008 года.

- ↑ Early Transistor History at IBM

- ↑ Hannon S. Yourke. Millimicrosecond non-saturating transistor switching circuits (неопр.). Stretch circuit memo #3 (октябрь 1956).

- ↑ 1 2 3 High-Speed Switching Transistor Handbook / William D. Roehr, Darrell Thorpe. — Motorola, 1963. — С. 37-40.

- ↑ Лаут В.Н. БЭСМ-6 (неопр.). Воспоминания сотрудников.

- ↑ 1 2 William R. Blood, Jr. MECL System Design Handbook. — 4-th edition. — On Semiconductor, 2000. Архивная копия от 14 июля 2014 на Wayback Machine

- ↑ A. E. Barish et al. Improved performance of IBM Enterprise System/9000 bipolar logic chips // IBM Journal of Research and Development. — 1992. — Т. 36, вып. 5. — С. 829-834. — doi:10.1147/rd.365.0829.

- ↑ R. M. Russell. The CRAY1 computer system // Communications of the ACM. — 1978. — Т. 21, вып. 1. — С. 63–72. — doi:10.1145/359327.359336.