Конфигурируемые логические ячейки в PIC микроконтроллерах / Habr

Первоначальный замысел статьи состоял в описании Периферии Независимой от Ядра микроконтроллеров Microchip, но тема оказалась весьма обширной, поэтому в качестве первого шага расскажем о CLC – конфигурируемых логических ячейках (Configurable Logic Cell).

В статье (Использование конфигурируемых логических ячеек для управления светодиодной лентой WS2812 [1]) было рассмотрено как логические ячейки CLC PIC-контроллеров могут существенно упростить решение задачи формирования сигналов управления драйверами WS2812 и аппаратно реализовать функции, на программное решение которых может не хватать быстродействия простого микроконтроллера.

Цель представленной статьи заключается в более близком знакомстве с конфигурируемыми логическими ячейками в PIC микроконтроллерах Microchip, в демонстрации примеров реализаций и, по возможности, натолкнуть читателя на мысли по использованию CLC своих проектах.

Если очень кратко, то CLC это одна из частей

Часть 1. Конфигурируемые логические ячейки в PIC микроконтроллерах

Часть 2. Порты Ввода/Вывода

Часть 3. АЦП с вычислителем

Конфигурируемые логические ячейки CLC являются частью ПНЯ – Периферии Независимой от Ядра (Core Independent Peripheral, CIP), т.е. функционирование такой периферии не зависит (почти) от тактовой частоты микроконтроллера и его состояния (RUN, IDLE, SLEEP).

Конечно же, подобная периферия конфигурируется программой микроконтроллера, но дальнейшее функционирование может быть независимым.

Каждая ячейка содержит входной мультиплексор, логическую функцию, управление выходом, подключение к контроллеру прерываний.

Общая схема одной логической ячейки приведена на рис.1.

Рис.1. Структура одной логической ячейки CLC

Каждая из логических ячеек имеет 4 входа, сигналы для которых выбираются входным мультиплексором, при этом каждый вход может быть прямым или инверсным. Часть входов может не использоваться и подключаться к уровню лог.0 или лог.1.

Входы для ячеек могут иметь внешние подключения (порты ввода/вывода) и внутренние (сигналы другой периферии: ШИМ, компараторы, таймеры и др. и выходы самих CLC).

Выход ячейки CLC имеет управляемую полярность, может подключаться на выходной порт микроконтроллера, к другой периферии, формировать запрос на прерывание по изменению состояния (по фронту и/или спаду).

Логическая функция каждой ячейки выбирается из 8-и вариантов (см. табл.1)

Таблица 1. Варианты функций логических ячеек.

Так как логические ячейки имеют массу настроек, то проще всего конфигурировать CLC через плагин MPLAB Code Configurator в среде разработки MPLAB X, который создает Си файлы настроек задействованной периферии.

Рис. 2. Среда разработки Mplab X IDE с запущенным плагином Mplab Code Configurator (MCC)

где:

1 – редактируемая ячейка;

2 – настройка входного мультиплексора и полярности входов;

3 – функция логической ячейки;

4 – резервирование портов ввода/вывода.

Обратите внимание на входные гейты на входе CLC (рис.2, п.2), которые выполнены как элементы 4-ИЛИ.

Таблица 2. Преобразование логических функций

| Логическая функция | Эквивалентное представление в CLC |

|---|---|

| 4-ИЛИ (OR) | |

| 4-ИЛИ-НЕ (NOR) | |

| 4-И-НЕ (NAND) | |

| 4-И (AND) |

Плавное изменение яркости светодиода (мерцание)

Если сигналы двух ШИМ с близкими частотами подключить к входам CLC сконфигурированной как элемент XOR (исключающее ИЛИ), то можно организовать «мерцание» светодиода (периодическое изменение скважности). При этом решение полностью аппаратное и не требует участия ядра МК (программы).

Рис. 3a. Схема «ШИМ модулятора»

Рис. 3b. Диаграммы демонстрирующие принцип изменения скважности

Если под такую простую задачу жалко использовать два ШИМ-модуля, то возможны варианты реализации без ШИМ:

А) Используем сигналы переполнения двух таймеров (события), плюс три ячейки CLC.

На два JK- триггера в счетном режиме подаем сигналы с таймеров (postscaled out) – получаем на выходе меандры, которые затем подаем на элемент XOR.

Рис. 3c. Реализация ШИМ модулятора без входных ШИМ сигналов

Б) Используем сигналы переполнения двух таймеров и одну CLC.

На входы RS триггера подаем сигналы с Таймера (postscaled out) – получаем на выходе «пилообразный ШИМ» (рис. 3e).

Рис. 3d.

Рис. 3e.

Делитель частоты

Схема делителя частоты на 2 приведена на рис. 4a. Используется один D-триггер в счетном режиме. Входной сигнал подается на вход тактирования, вход D соединен с инверсным выходом триггера. В момент поступления на вход тактирования фронта на входе D всегда будет инверсный сигнал относительно текущего состояния триггера, т.е. состояние триггера будет меняться только по фронту входного сигнала.

Рис.4а. Делитель на 2.

В плагине MPLAB Code Configurator подобная схема может выглядеть так:

Рис. 4b. Делитель на 2 в настройках MCC.

Рис.4c. Диаграмма на входе и выходе делителя.

Делитель на 3 изображен на рис. 4d.

Рис. 4d. Делитель на 3.

Делитель на 4 это два последовательно включенных делителя на 2 😉

Где могут применяться делители? Там, где нужно поделить частоту.

Следующий пример использует делители частоты.

Драйвер шагового двигателя

Один из самых простых вариантов управления Шаговым Двигателем (ШД) это полношаговое управление (full step). В этом варианте сигналы управления сдвинуты на 90°. Поэтому можно взять периодический сигнал, на один делитель частоты подать его в прямом виде, на другой – в инверсном.

Рис. 5a. Формирователь сигналов управления шаговым двигателем.

Рис. 5b. Диаграмма на выходе формирователя.

Изменение частоты на входе CLC будет изменять частоту управляющих сигналов шагового двигателя. Входную частоту можно брать с входа микроконтроллера (внешний сигнал), либо от внутреннего источника – ШИМ или NCO генератора.

При управлении ШИМ-ом нужно менять 2 параметра: регистр периода (частота) и регистр скважности, так как управляющий сигнал должен быть с 50% скважностью.

Применение NCO (Numerically Controlled Oscillator, управляемый генератор) выглядит более привлекательным, так как это генератор может автоматически формировать меандр, поэтому для изменения частоты нужно менять значения только в одном регистре.

Задержка. Формирование импульса по фронту, спаду, изменениям

Для некоторых задач может понадобиться формирование задержанного импульса.

Для этого можно применить D-триггер. На счетный вход подаем входной сигнал, на вход тактирования – какой либо высокочастотный сигнал (например тактовой частоты Fosc). Таким образом, изменение выхода триггера будет происходить только по фронту тактового сигнала.

Данный метод будет сдвигать фронт и спад сигала на период Fosc (тактовой частоты) только если оба сигнала синхронны. Поэтому для гарантированного сдвига на 1 период Fosc сдвигаемый сигнал должен формироваться самим микроконтроллером (ШИМ, NCO и др.). Если входной сигнал асинхронный, то на входе можно поставить синхронизатор на точно таком же D-триггере (т.е. сперва сдвинуть асинхронный сигнал до первого тактового импульса, а затем сдвинуть на полный период тактового сигнала).

Рис. 6a. Формирователь задержанного сигнала.

Рис. 6b. Диаграммы на входе и выходе формирователя задержанного сигнала.

На основе этой схемы легко реализовать формирователь импульсов по изменению состояния входа, по фронту и по спаду.

Формирование импульсов по фронту и спаду

Рис. 7a. Формирователь импульсов по фронту и спаду

Рис. 7b. Диаграммы на входе и выходе формирователя импульсов по фронту и спаду

Формирование импульсов по фронту

Рис. 8a. Формирователь импульсов по фронту.

Рис. 8b. Диаграммы на входе и выходе формирователя импульсов по фронту

Формирование импульсов по спаду

Рис. 9a. Формирователь импульсов по спаду

Рис. 9b. Диаграммы на входе и выходе формирователя импульсов по спаду

Где могут применяться подобные схемы?

Подавление дребезга контакта

При замыкании и размыкании контактов наблюдается дребезг. Наверняка с этим явлением многие сталкивались при опросе состояния механических кнопок. Логические ячейки совместно с таймером могут решить задачу аппаратно.

Схема реализации точно такая же как для формирования задержанного импульса, только период тактового сигнала нужно брать побольше. Суть метода заключается в том, что выход триггера не реагирует на вход если нет сигнала тактирования, поэтому схема не реагирует на каждое переключение входа.

Рис.10a. подавление дребезга.

Рис.10b. Диаграммы сигналов на входе и выходе схемы подавления дребезга.

Где применяется?

Собственно опрос кнопок, предотвращение многократных ложных срабатываний.

Еще варианты

Рис.10c. Подавление дребезга с задержкой с RC-цепочкой

Рис.10d. подавление дребезга

В отличие от предыдущего примера задержка определяется параметрами RC цепи и не требует задействование таймера.

Квадратурный энкодер

Квадратурный энкодер это устройство, при вращении оси которого формируются два квадратурных сигнала (сдвинутых по фазе). Применяется в определении скорости (угла поворота или числа оборотов) и направления вращения/перемещения. Пожалуй, самое известное применение это колесо мышки.

Ниже приведены две схемы декодирования сигналов квадратурного энкодера.

Рис. 11a. Квадратурный декодер со счетным выходом и сигналом направления.

Эта схема детектирует фазы входных сигналов (состояние выхода D показывает направление вращения энкодера) и выдает тактовые сигналы (выход С).

Рис 11b. Квадратурный декодер с двумя счетными выходами

Эта схема выдает импульсы. Один выход при вращении по часовой стрелке, второй выход – при обратном вращении.

При переключении контактов энкодер выдает множественные ложные срабатывания (дребезг контактов).

Рис. 11c. Сигналы с выходов механического квадратурного энкодера

Вот тут фрагмент покрупнее:

Рис. 11d. Сигналы с выходов механического квадратурного энкодера

Поэтому обе схемы нуждаются в очищенных от дребезга сигналов. Ранее мы уже рассматривали варианты подавления дребезга аппаратно на ячейках CLC.

Рис. 11e. Входные сигналы с энкодера и очищенные от дребезга.

Под обработку сигналов квадратурного энкодера понадобятся 4 ячейки CLC – две для подавления дребезга и две для детектирования.

Рис. 11f. Диаграммы сигналов обработки квадратурного энкодера для схемы с выходом направления

Рис. 11g. Диаграммы сигналов обработки квадратурного энкодера для схемы с двумя счетными выходами.

Входы и выходы логических ячеек могут подключаться к портам микроконтроллера, а могут иметь только внутренние соединения. Для данного примера необходимы только два входа, выходы декодера могут подключаться к внутренним счетчикам микроконтроллера, формировать прерывания, опрашиваться программой и пр… Но для задач тестирования можно все выходы CLC вывести наружу и проверить правильность работы схемы.

Где применяется?

Механические и оптические энкодеры, подсчет числа входящих и выходящих людей, закрытие турникета при прохождении в неположенном направлении ))

Манчестерский кодер

Манчестерское кодирование широко применяется при передаче сигналов. Каждый бит делится на два интервала, после первого интервала (в середине информационного бита) происходит смена уровня сигнала. Передача каждого информационного бита сопровождается изменением уровня, Нули и Единицы отличаются фазой (1 – перепад из 0 в 1, «0» — из 1 в 0). Таким образом, манчестерский код имеет следующие особенности:

- Самосинхронизирующийся – нет необходимости передачи специальных синхро сигналов, так как уровень передаваемого сигнала гарантировано меняется в середине информационного бита; высокая плотность информации

- Нет постоянной составляющей (сигнал меняется каждый такт)

Схема кодирования очень проста и использует один логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ.

На выходе получаем кодированный поток.

Рис. 12. Диаграммы формирователя Манчестерского кода

Декодер манчестерского кода

Схема манчестерского декодера гораздо сложнее. Её задача выделить синхро-импульсы и битовый поток.

В примере применения AN1470 [2] предлагается следующая реализация аппаратного декодирования Минчестерского кода на основе CLC и NCO (управляемого генератора).

Рис.13a. Схема декодера Манчестерского кода

Рис. 13b. Диаграммы, поясняющие работу декодера

Стадия 1 – D-Триггер

Ячейка CLC4 (D-триггер) защелкивает входной поток по спаду сигнала синхронизации. Выход с этого триггера будет являться декодированными (восстановленными) данными из входного потока.

Стадия 2 – элемент XOR (CLC2)

Поскольку в Манчестерском кодировании изменение сигнала происходит в середине каждого информационного бита, то можно использовать элемент ИСКЛЮЧАЮЩЕЕ ИЛИ чтобы обеспечить нарастающий фронт на стадии 3 в середине каждого бита, т.е. мы синхронизируем декодер в середине каждого бита.

Стадия 3 – NCO + AND-OR (CLC1)

модуль NCO, используется для генерации ¾ битового интервала по завершении которого производится захват (фиксация) данных. NCO используется в режиме с активным низким состоянием. Длительность импульсов можно регулировать с помощью регистров. Модулю NCO необходим источник тактовых импульсов, которые поступают ему из CLC1.

Эти два блока являются наиболее важными в декодере. Они создают импульсы фиксированной длины после каждого нарастающего фронта сигнала, выходящего из «стадия 2». Выходной сигнал NCO подается обратно в элемент И-ИЛИ так, что если выход из «стадия 2» становится равным нулю, то NCO будет продолжать тактироваться до своего переполнения.

Выделенные сигналы синхронизации и данных можно завести на модуль SPI. Тогда, по приему кодовой посылки, в буфере SPI получим декодированные данные и прерывание по приему.

Ждущий мультивибратор

Для формирования одиночного импульса по фронту или спаду входного сигнала служат ждущие мультивибраторы.

Рис. 14a. Схема ждущего мультивибратора на JK-триггере.

Рис. 14b. Реализация ждущего мультивибратора на JK-триггере в PIC-контроллере.

Рис. 14c. Диаграммы поясняющие работу ждущего мультивибратора

Инвертирование сигнала на входе синхронизации реализует ждущий мультивибратор с запуском по спаду входного сигнала (Рис.14d).

Рис. 14d. Диаграммы ждущего мультивибратора с запуском по спаду.

В отличие от рассмотренных ранее формирователей импульса по фронту и спаду (см.рис 8а, 9а) у данной схемы длительность импульса задается не частотой сигнала на входе тактирования, а параметрами RC-цепочки.

Мультивибратор

Простейший генератор можно сделать на двух CLC (D-триггер + инвертер).

Недостатком является низкая стабильность, так как пороги переключения зависят от уровней лог.0 и 1 конкретного типа микроконтроллера, которые могут «гулять» от температуры, напряжения питания и др. К тому же не очень правильно когда на цифровом входе уровень сигнала продолжительное время находится между 0 и 1.

Рис. 15a. Простейший мультивибратор на D-триггере.

Следующая схема использует два встроенных компаратора и одну CLC. В этой схеме пороги срабатывания компараторов задаются источником опорного напряжения и внешним делителем (или встроенным ЦАП). Схема будет более стабильной и к тому же компараторы имеют аналоговые входы и позволяют любые напряжения на входе в пределах напряжения питания.

Рис.15b. Мультивибратор на двух компараторах и RS-триггере.

Для данного примера от ПНЯ помимо CLC нам понадобятся 2 компаратора, а так же источники опорного напряжения (внешние на делителе или внутренние).

В начальном состоянии на выходе триггера установлен уровень лог.0, конденсатор разряжен, на компараторе COMP1 на выходе появляется лог.1, триггер устанавливается в 1, конденсатор заряжается через резистор до уровня напряжения верхнего порога (Vref hi), при достижении которого на входе R триггера появляется лог.1. Триггер перекидывается в противоположное состояние, конденсатор начинает разряжаться через резистор и т.д… Таким образом, мы получили полностью программно-независимый генератор. Но в данной схеме микроконтроллер может программно изменять частоту с помощью изменения порога срабатывания одного из компараторов (изменением опорного напряжения встроенным ЦАП или др.).

Рис.15c. Диаграммы сигналов мультивибратора

Измерение Емкости. Емкостной сенсор. Сенсорная кнопка

Частота мультивибратора (рис.15) зависит от значения емкости конденсатора и сопротивления резистора. Если один из параметров изменяется, то изменяется частота. Поэтому данная схема позволяет измерять сопротивление или емкость, например с помощью таймера микроконтроллера.

В качестве конденсатора может использоваться проводящая площадка, при касании которой мы будем вносить в схему дополнительную емкость, что приведет к уменьшению частоты генератора.

| сигналы | комментарий |

|---|---|

| Осциллограммы без касания сенсора | |

| Осциллограмма при «нажатом» сенсоре |

Рис.16a. Диаграммы работы мультивибратора при изменении времязадающей емкости.

Подобным методом можно детектировать протечку воды или определять влажность почвы и использовать для автоматизации полива цветов ))

Импульсный источник питания

Еще один пример использования конфигурируемых логических ячеек совместно со встроенными компараторами.

Таймер TMR периодически устанавливает RS-триггер и открывает силовой транзистор. Ток начинает течь через индуктивность, напряжение на резисторе R1 линейно увеличивается. При достижении напряжения на R1 порогового значения срабатывает компаратор COMP1 и сбрасывает триггер, транзистор закрывается. Ток через индуктивность не может прерваться мгновенно, поэтому ток начинает течь через диод D1 и заряжает выходной конденсатор. По срабатыванию таймера триггер снова устанавливается и процесс повторяется.

Рис.17a. Простейший импульсный источник питания.

На рисунке приведена схема повышающего источника, но для других топологий (см. рис. 17b) работа схемы будет аналогичной, поэтому выходной каскад далее рисовать не буду.

| схема | описание |

|---|---|

| повышающий | |

| понижающий | |

| Sepic |

Рис.17b. Различные топологии импульсных источников питания

Приведенная на рис. 17a схема выполняет функцию преобразования энергии и работает по пиковому значению тока в индуктивности. Можно ввести еще контур регулирования выходного напряжения. Наиболее просто сделать гистерезисное управление: когда напряжение на выходе ниже нормы – происходит накачка источника, когда напряжение выше – выдача управляющих импульсов на силовой транзистор блокируется.

Рис.17c. ИИП с гистерезисным управлением

Включение силового транзистора будет генерировать помеху, которая может приводить к преждевременному срабатыванию компаратора COMP1. Для избавления от этого можно включить RC-фильтр в цепь между R1 и компаратором, а можно добавить рассматриваемый ранее блок бланкирования (формирование импульса по фронту, см. рис 8а, или рис. 14а), который после включения транзистора будет блокировать сброс триггера на короткий интервал времени.

Рис.17d. Помеха при коммутации силового ключа

Рис.17e. ИИП с гистерезисным управлением и бланкированием помехи переключения.

Элементы U1 и U2 можно привести к реализации на элементах ИЛИ и отнести к входу CLC1, тогда вся логическая часть схемы реализуется на трех ячейках CLC (обычно в микроконтроллерах Microchip имеется 4 ячейки).

Все что на схеме изображено левее силового ключа – находится внутри микроконтроллера, связи периферийных модулей так же осуществляются внутри кристалла микроконтроллера. Напряжения порогов Ref и Ref1 могут задаваться встроенными источниками опорного напряжения или ЦАП. Таким образом, импульсный источник питания с регулируемым выходным напряжением можно реализовать на периферийных модулях микроконтроллера. После первоначального конфигурирования схема будет работать полностью аппаратно без необходимости участия ядра в поддержании функции преобразователя. Ядро может заниматься интерфейсными задачами, индикации контроля и др.

Вообще, для построения импульсных источников питания в новых семействах PIC16F17xx микроконтроллеров Microchip есть дополнительные аналоговые (операционные усилители) и специализированные периферийные модули: модули пилообразной компенсации (Slope Compensation) и программируемый рамп-генератор (Programmable Ramp Generator, PRG), операционные усилители, модуль формирования комплементарных выходных сигналов (COG), HLT таймера. Но об этих частях ПНЯ постараемся рассказать в следующий раз.

Периферия независимая от ядра интересна сама по себе, но наибольшую пользу может принести возможность синтеза функциональных блоков, т.е. совместное использование нескольких периферийных модулей для решения конкретных задач. В этом случае тактовая частота, быстродействие и разрядность ядра уходят на второй план – аппаратная часть выполняет специализированные функции, а ядро занимается программной поддержкой работы изделия.

Литература

- Использование конфигурируемых логических ячеек для управления светодиодной лентой WS2812

- AN1470. Manchester Decoder Using the CLC and NCO

Продолжение. Часть 2. Порты ввода/вывода.

Формирователи импульсов по фронту сигналов

Формирователи импульсов по фронту сигналов.

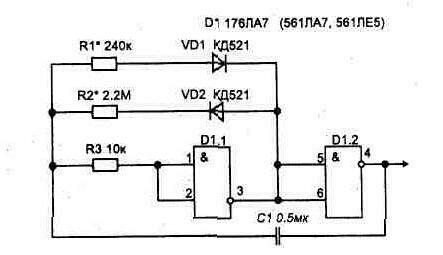

Рис. 1.49. Формирователь импульсов на дифференцирующих цепях

Рис. 1.50. Формирователи импульсов на основе интегрирующих цепей

Рис. 1.51. Формирователь импульса по фронту сигнала

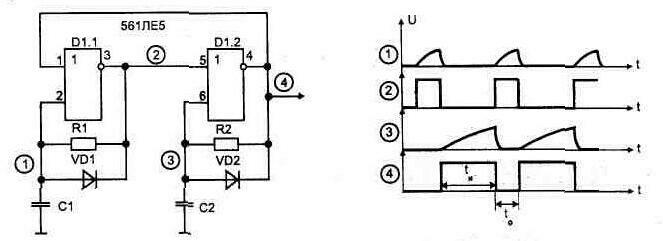

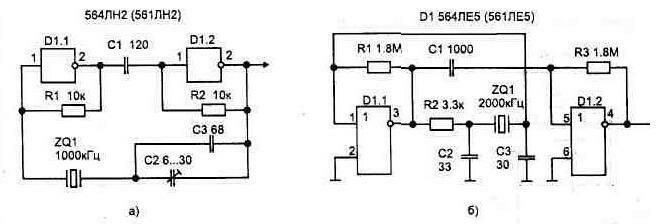

При разработке цифровых устройств нередко требуется формировать импульсы, привязанные к входному сигналу. Если не предъявляются высокие требования к стабильности и длительности формируемого импульса, могут применяться схемы на основе дифференцирующих (рис. 1.49) или интегрирующих (рис. 1.50 и 1.51) RC-цепей. В этом случае для расчета длительности импульса используются те же соотношения, что и для одновибраторов.

Рис. 1 52. Формироватеть пмпульса

Рис. 1.53. Формирователь импульсов по переднему и заднему фронту входного сигнала

На рис. 1.52 показана схема формирователя, в которой в зависимости от длительности запускающего импульса формируемый выходной импульс будет иметь фиксированную или укороченную длительность. Схема, приведенная на рис. 1.53, генерирует импульсы по переднему и заднему фронту входного сигнала. Причем выходные импульсы имеют всегда полную длительность, независимо от момента снятия сигнала запуска. Здесь допускается раздельная регулировка. Длительности и периода следования импульсов.

Pис 1.54. Повторитель входных импульсов с защитой от помех

Схема, рис. 1.54, может использоваться для повторения входного сигнала с помехами по фронтам (от удаленного источника). Она позволяет улучшить форму импульсных сигналов со «звоном» (колебаниями по фронтам импульсов), что бывает при передаче сигнала по длинной, плохо согласованной линии или радиоканалу. Постоянная времени цепи R1-C1 зависит от периода следования входных импульсов и выбирается такой, чтобы к приходу спада входного импульса напряжение на конденсаторе С1 было близко к напряжению питания. Тогда первый же перепад входного импульса установит триггер D2.1 снова в единичное состояние.

Рис. 1.55. Формирователь импульсов с синхронизацией тактовой частотой

Рис. 1.56. Формирование двух импульсов

Рис. 1.57. Формирователь импульсов

Большую помехоустойчивость и стабильность в работе обеспечивают схемы формирователей импульсов без использования RC-цепей, рис. 1.55…1.57. В этом случае выходные сигналы получаются синхронными с внутренней тактовой частотой. Процесс синхронизации сводится к сдвигу фронта импульса входной информации до совпадения его с фронтом ближайшего тактового импульса. При этом длительность преобразованных таким образом информационных импульсов будет также определяться длительностью импульса синхрочастоты.

Длительность формируемых схемой, рис. 1.55а, импульсов будет равна периоду тактовой частоты (T=1/fт), и ее легко можно изменить, меняя частоту на входе 2. Используя счетчики и комбинационную логику, можно получить выходной сигнал практически любой длительности.

Схема на рис. 1.56 обеспечивает на выходе формирование двух импульсов, привязанных к фронтам входного сигнала.

Схема, показанная на рис. 1.57, в зависимости от длительности информационного импульса на выходе дает синхронизированные с тактовой частотой одиночный импульс или же серию импульсов.

Цифровые схемы применяют также при передаче (обмене) не синхронизированных сигналов между устройствами. Каждый источник, как правило, имеет свой тактовый генератор и непосредственное использование этих сигналов может привести к сбоям из-за случайного разброса фаз тактовых импульсов. В этом случае становится обязательным привязка в приемном устройстве всех внешних управляющих сигналов к собственной тактовой частоте.

Источник материала

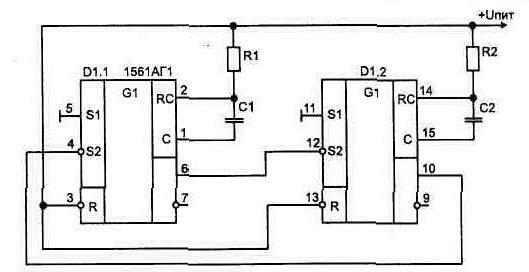

5. Формирователи пачки заданного числа импульсов

Формирователи пачки заданного числа импульсов

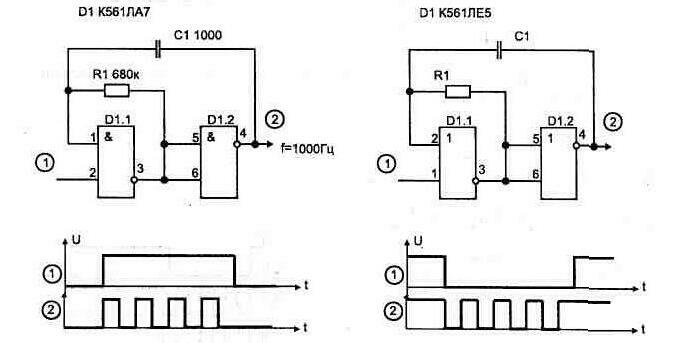

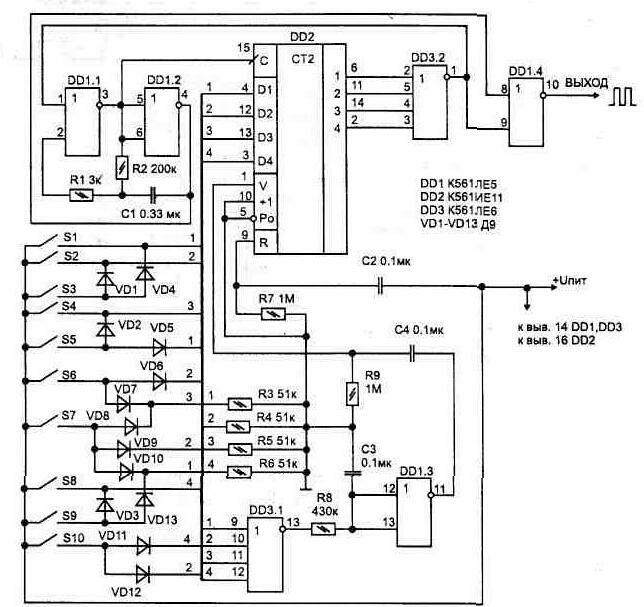

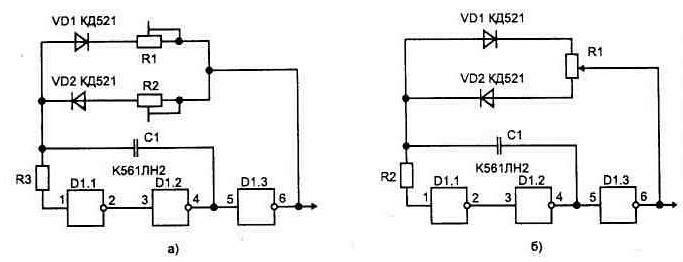

Для устройств автоматики, дистанционного управления или проверки работы отдельных узлов схемы иногда требуется передавать пачку из определенного числа импульсов Простейшие схемы таких формирователей показаны на рис. 1.43. В них последний импульс пачки может получиться укороченным, если сигнал управления имеет произвольную длительность.

Часто в схемах управления необходимо использовать генераторы, в которых независимо от положения фронтов управляющих сигналов обеспечивается неискаженное (по длительности) формирование первого и последнего

импульсов на выходе. Причем начало первого импульса должно совпадать с началом управляющего сигнала.

а) б)

Рис. 1.43. Простейшие схемы формирования пачки импульсов

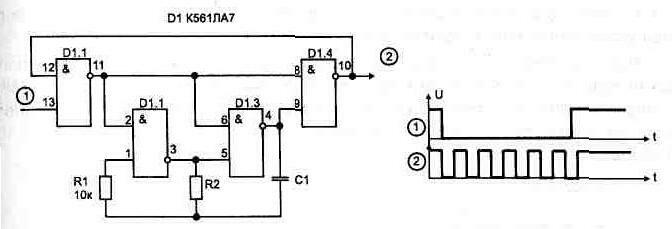

Два варианта таких генераторов показаны на рис. 1.44 и рис. 1.45. Если входной запускающий импульс меньше по длительности периода колебаний, на выходах формируется один импульс. При большей длительности правляющего

сигнала на выходе будет пачка, показанная на диаграмме. Таким же свойством обладает схема формирователя импульсов, рис. 1.45.

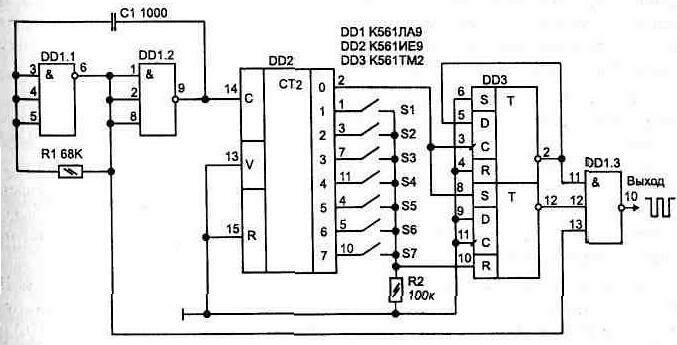

Электрическая схема, рис. 1.46, формирует от 1 до 7 импульсов в пачке с последующим повторением цикла через время 16Т, пока нажата кнопка. В процессе работы счетчика-дешифратора DD2 на его выходах появляются импульсы, которые управляют переключением триггера DD3.2. Таким образом задается интервал, в течение которого на выходе DD3/12 будет лог. «1», что разрешает прохождение импульсов от автогенератора (DD1.1, DD1.2) через элемент DD1.3 на выход. Второй триггер DD3.1 включен по схеме делителя и обеспечивает появление интервала между пачками.

Количество импульсов в пачке соответствует номеру нажатой кнопки. Поформуле T=1,32R1C1 определяется период формируемых импульсов. При этом R1 может иметь номинал от 20 кОм до 10 МОм. Заменой микросхемы DD2 на

561 ИЕ8 количество импульсов в пачке может быть увеличено до 9.

Рис. 1.44. Управляемый генератор с неискаженной длительностью последнего

формируемого импульса

Рис. 1.45. Вариант управляемого генератора с неискаженной длительностью

последнего формируемого импульса

Рис. 1.46. Формирователь пачки до 7-ми импульсов

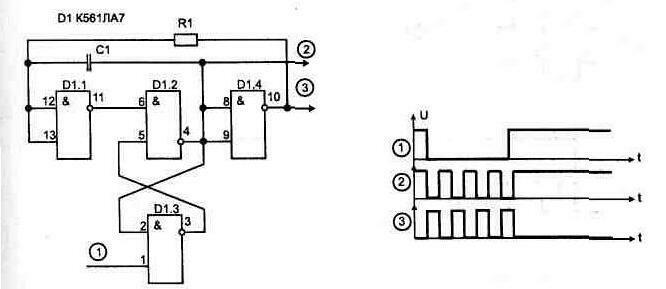

Схема, приведенная на рис 1.47, обеспечивает при нажатии кнопки однократное формирование пачки до 15 импульсов (на схеме показаны только 10 кнопок). Для повторной выдачи пачки необходимо повторно нажать на соответствующую кнопку. При этом происходит запись соответствующего числа в двоичном коде в регистр предварительной установки счетчика DD2, и он начинает считать на вычитание до момента времени, пока на всех его выходах не установится лог. «0». Логический «0» установится и на выходе DD1.4.

Рис. 1.47 Формирователь пачки импульсов

Номиналы элементов (R2, С1) на схеме указаны для частоты генератора 10 Гц (частота набора номера в телефонной линии). На схеме показан также пример дешифратора десятичных чисел в двоичный код на диодах типа Д9 (Д2)

однако для уменьшения габаритов вместо них удобнее использовать две диодные матрицы типа КДС627А.

Воспользовавшись принципом работы данной схемы, можно выполнить формирователь пачки с любым количеством импульсов Для этого последовательно со счетчиком DD2 можно включить еще такие же счетчики, а вместо ди-

одов VD1…VD13 применить тумблеры для начальной установки необходимого числа импульсов (в двоичном коде) Для запуска работы формирователя необходимо подать кратковременный положительный импульс на входы

DD2/1….DDn/1 — при этом происходит запись установленного кода.

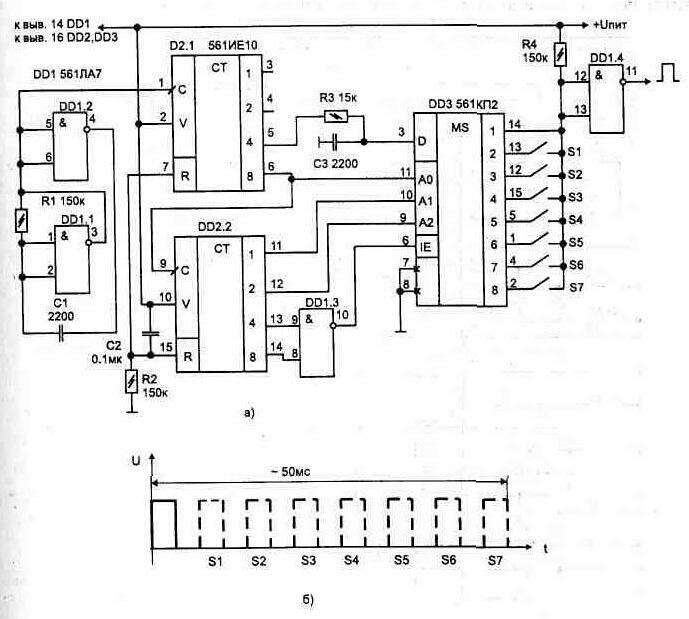

Рис. 1.48. а) Формирователь кодовой последовательности, б) форма импульсов

Иногда требуется иметь пачки импульсов, состоящие из произвольной комбинации положения импульсов относительно начального, — кодовую после довательность. Такой режим обеспечивает схема, рис. 1.48а. Если ни одна из кнопок не нажата, то на выходе (DD1/11) будут появляться одинарные импульсы, с периодом, определяемым частотой задающего генератора на элементах DD1.1, DD1.2.

В зависимости от того, какая кнопка нажата, на выходе появится пачка из комбинации импульсов. Причем каждой нажатой кнопке будет соответство

Рис. 1.48. в) Дешифратор кодовой последовательности

вать определенное положение импульса относительно начального. Эпюры выходного напряжения, рис. 1.48в, поясняют работу схемы.

Кнопки могут быть нажаты в любой комбинации или все одновременно. Что позволяет использовать схему в устройствах, где требуется для дистанционного управления одновременная передача нескольких команд.

Вариант схемы дешифратора кодовой последовательности показан на рис. 1.48в. При обработке входных пачек импульсов на соответствующих выходах мультиплексора DD4 будут кратковременно появляться импульсы, а для

фиксации принятой команды можно воспользоваться любыми триггерами.

4. Генераторы импульсов | Техническая библиотека lib.qrz.ru

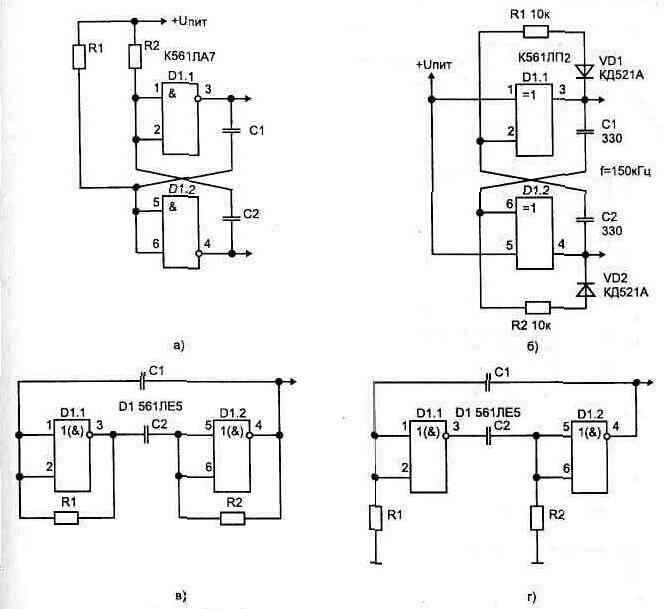

Генераторы импульсов

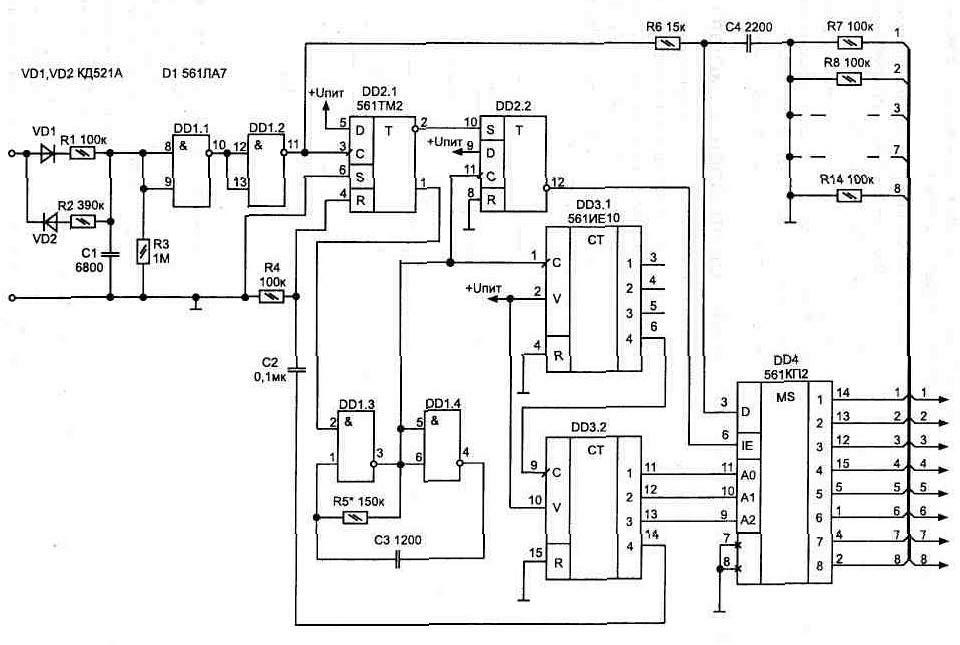

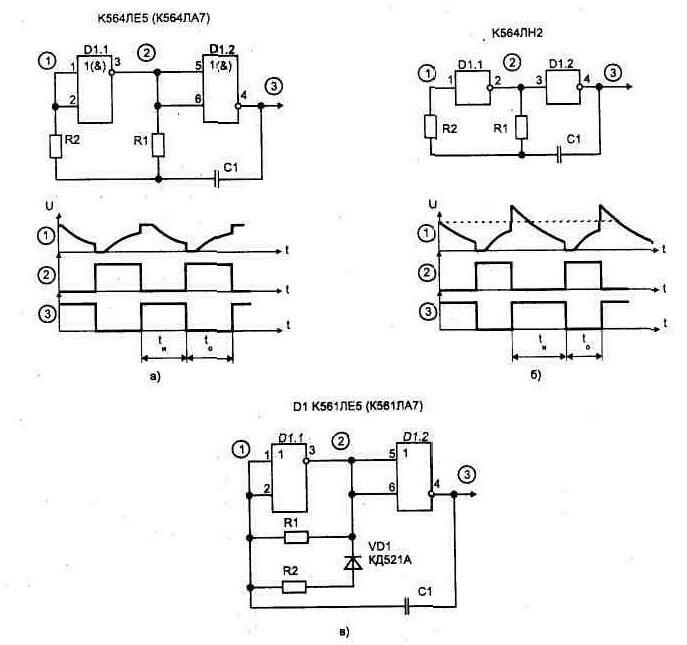

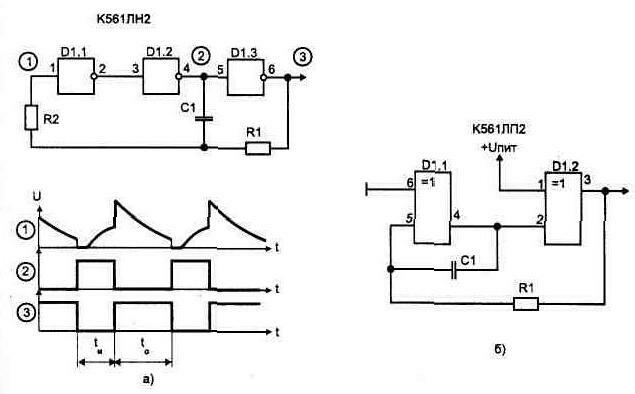

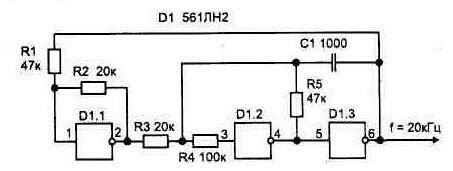

Вариант простейшего генератора (мультивибратора) показан на рис. 1.30а. Схема имеет два динамических состояния. В первом из них, когда на выходе D1.1 состояние лог. «1» (выход D1.2 лог. «0»), конденсатор С1 заряжается. В процессе заряда напряжение на входе инвертора D1.1 возрастает, и при достижении значения Uпор=0,5Uпит происходит скачкообразный переход во второе динамическое состояние, в котором на выходах D1.1 лог. «О», D1.2 — «1». В этом состоянии происходит перезаряд емкости (разряд) током обратного направления. При достижении напряжения на С1 Unop происходит возврат схемы в первое динамическое состояние. Диаграмма напряжений поясняет работу. Резистор R2 является ограничительным, и его сопротивление не должно быть меньше 1 кОм, а чтобы он не влиял на расчетную частоту, номинал резистора R1 выбираем значительно больше R2 (R2<0,01R1). Ограничительный резистор (R2) иногда устанавливают последовательно с конденсатором. При использовании неполярного конденсатора С1 длительность импульсов (tи) и пауза (tо) будут почти одинаковыми: tи=to=0,7R1C1. Полный период T=1,4R1C1. Резистор R1 и конденсатор С1 могут находиться в диапазоне 20 к0м…10 МОм; 300 пф…100 мкФ.

При использовании в схеме (рис. 1.30б) двух инверторов микросхемы К561ЛН2 (они имеют на входе только один защитный диод) перезаряд конденсатора будет происходить от уровня Uпит+Unop. В результате чего симметрич-

ность импульсов нарушается tи=1,1R1C1, to=0,5R1C1, период T=1,6R1C1.

Рис. 1.30. Генератор импульсов на двух инверторах

Рис 1.31. Генератор импульсов с раздельной установкой длительности

импульса и паузы между ними

Рис. 1.32. Генератор импульсов на трех инверторах

Так как порог переключения логических элементов не соответствует точно половине напряжения питания, чтобы получить симметричность импульсов, в традиционную схему генератора можно добавить цепь из R2 и VD1, рис. 1.ЗОв.Резистор R2 позволяет подстройкой получить меандр (tи=to) на выходе генератора.

Схема на рис. 1.31 дает возможность раздельно регулировать длительность и паузу между импульсами: tи=0,8C1R1, to=0,8C1R2. При номиналах элементов, указанных на схеме, длительность импульсов около 0,1 с, период повторения 1 с.

Более стабильна частота у генераторов, выполненных на трех инверторах (Рис. 1.32). Процесс перезаряда С1 в сторону уменьшения напряжения на левой обкладке начинается от напряжения Uпит+Unop, в результате чего на это уходит больше времени tи=1,1C1R2. Полный период колебаний составит

T=1,8C1R2.

На рис. 1.33 приведены схемы аналогичных генераторов, которые позволяют раздельно регулировать длительность и паузу между импульсами или при неизменной частоте регулировать скважность импульсов. Мультивибратор на основе триггера Шмитта показан на рис. 1.34.

Если требуется получить на выходе приведенных выше схем генераторов симметричные импульсы без подстройки, то после схемы необходимо ставить триггер или же воспользоваться схемой на трех инверторах, рис. 1.35. Элемент

D1.1 используется для создания второй цепи отрицательной обратной связи, охватывающей инвертор D1.2 (главную цепь обратной связи для сигнала образует резистор R5) Элемент микросхемы D1 1 работает в режиме с низким

коэффициентом усиления при замкнутой обратной связи подобно операционному усилителю работающему в линейной части характеристики В результате этого инвертированное пороговое напряжение инвертора D1 1 может быть просуммировано с напряжением отрицательной обратной связи и подано на вход

Рис 133 Генератор пмпульсов с раздельнои регулировкой

а) длительности импульсов и паузы между ними б) скважности импульсов

Рис 1 34 Генератор перекрывающихся импульсов

Рис 1 35 Генератор с симметричными импульсами на выходе

элемента D1.2. Если соотношение R2/R1 равно отношению R3/R5 может быть получена полная компенсация ошибок обусловленных изменением пороговых напряжении элементов D1.1 и D1.2 При этом предполагается, что все элементы схемы расположены в одном корпусе и их пороговые напряжения фактически равны Частота импульсов такой схемы определяется из соотношения F=1/R5C1 (она будет примерно в два раза выше по сравнению со схемой, показанной на рис. 1.30)

Симметричный мультивибратор можно выполнить на основе RS-триггере, рис 1.36. Вариант схемы на рис 1.31в позволяет резисторы R1 и R2 выби

Рис1.36 Симметричные мультивибраторы

а) на RS триггере с двумя конденсаторами, б) с одним конденсатором,

в) с резисторами соединенными с источником питания, г) на двух RS триггерах

рать более низкоомными, потому что диоды разделяют цепь заряда от выходов триггера. Вторым преимуществом этой схемы является то, что она позволяет легко и независимо регулировать в определенных границах период и скважность генерируемых импульсов. Скважность можно регулировать линейно, если R1 и R2 объединить в один потенциометр, а период — если общий конец R1 и R2 соединить с источником питания через потенциометр.

С целью уменьшения количества дискретных элементов предложена схема мультивибратора на двух RS-триггерах, рис. 1.36г.

Рис. 1.37 Автогенератор на основе двух логических элементов

Рис. 1 38. Автогенератор на двух одновибраторах

Симметричный мультивибратор можно выполнить на двух ЛЭ, рис. 1 37 или одновибраторах, рис. 1.38. Это также позволяет иметь раздельную регулировку длительности импульсов и интервала между ними.

Простейшие схемы симметричных мультивибраторов приведены на рис. 1.39. При этом, если R1=R2, R3=R4, С1=С2, полный период определяется из соотношения Т=1,4RC.

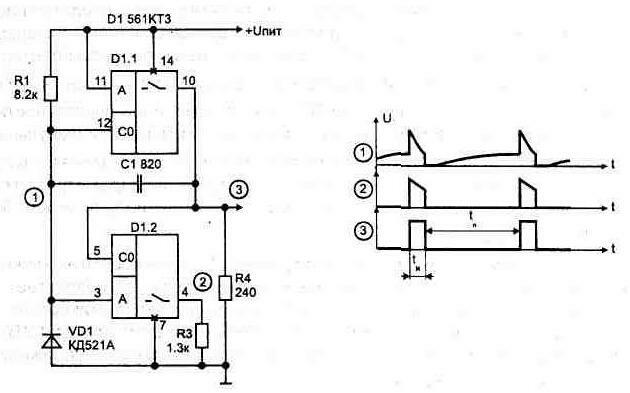

Генератор с малым потреблением энергии можно выполнить на двух ключах микросхемы К561КТЗ, рис. 1.40. После включения напряжения питания оба ключа разомкнуты. Конденсатор С1 разряжен, поэтому напряжения на нем нет

Рис 1 39 Симметричные мультивибраторы

Зарядный ток от источника питания протекает через последовательно включенные резисторы R1 и R2. Так как R1>R2, напряжение на резисторе R2 не достигнет порога срабатывания ключа D1.2, а в дальнейшем, по мере уменьшения зарядного тока, это напряжение стремится к 0. В то же время по мере накопления заряда на конденсаторе напряжение на выводе D1/12 экспоненциально возрастает. Когда оно достигнет порога срабатывания ключа D1.1, соединится цепь между выводами 11 и 10, что приведет к срабатыванию ключа D1.2. Сразу пос-

ле замыкания обоих ключей нижняя обкладка конденсатора С1 подключается к шине «+» питания. Заряд, накопленный ранее на конденсаторе, не может измениться мгновенно, поэтому напряжение на D1/12 скачком возрастает до уровня, превышающего Uпит на величину, равную порогу срабатывания ключа D1.1. После этого напряжение на С1 начинает уменьшаться с постоянной времени, равной C1R1R3/(R1+R3), и стремится достичь уровня, задаваемого делителем напряжения на резисторах R1, R3. В процессе перезаряда конденсатора напря-

жение на С1 уменьшится до порога размыкания ключа D1.1. В результате развивается лавинообразный процесс размыкания обоих ключей. Для защиты

Рис. 1.40. Генератор импульсов с повышенной нагрузочной способностью

Рис. 1.41. Простейшие схемы мультивибраторов с кварцевой

стабилизацией частоты

ключа D1.2 от отрицательного выброса напряжения в схему вводится диод. После размыкания ключей конденсатор начинает заряжаться через последовательно включенные резисторы R1 и R2 — описанные выше процессы повторяются.

При заданной емкости конденсатора длительность паузы t2 между импульсами регулируется резистором R1, однако изменение длительности паузы подбором резистора R1 приводит и к изменению длительности импульса t1. По-

этому, чтобы установить нужную длительность импульса, не меняя паузу, необходимо воспользоваться резистором R3. Регулирование параметров импульсов осуществляется в широких пределах, при этом отношение t1/t2 может быть как меньше, так и больше 1.

Относительно всех автогенераторов на МОП микросхемах можно отметить, что если схема мультивибратора не симметрична, то возрастает ее чувствительность к изменению питающего напряжения (для микросхем 561-ой

серии период может меняться на 35% при изменении Uпит от 3 до 15 В), поэтому расчетные соотношения справедливы для максимального напряжения питания.

Рис. 1.42. Схемы обеспечивающие повышенную стабильность частоты при

изменении окружающей температуры в широком диапазоне

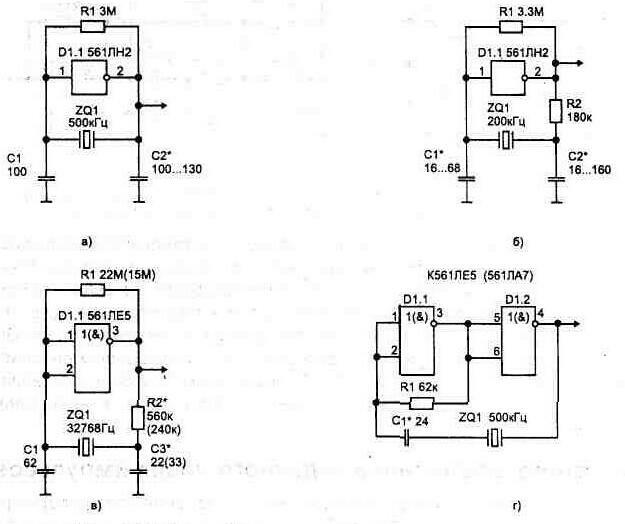

При стабилизированном питании, изменение длительности импульсов мультивибраторов и частоты в генераторах на RC-цепях обычно не лучше 1% на 15°С (в случае применения термостабильных конденсаторов). Большую стабиль-

ность частоты можно получить, используя кварцевую стабилизацию. На рис. 1.41 и 1.42 приведены типовые схемы построения таких генераторов. Для небольшой подстройки частоты иногда последовательно с кварцевым резонато-

ром устанавливают конденсатор 10…100 пФ. Частота импульсов и их стабильность в этом случае у генератора задается параметрами кварцевого резонатора.

Формирователи импульсов по фронту сигнала Справочник по микросхемам ТТЛ и КМОП Любительская Радиоэлектроника

Формирователи импульсов по фронту сигнала

При разработке цифровых устройств нередко требуется формировать импульсы, привязанные к входному сигналу. Если не предъявляются высокие требования к стабильности и длительности формируемого импульса, могут применяться схемы на основе дифференцирующих (рис. 1.49) или интегрирующих (рис. 1.50 и 1.51) RC-цепей. В этом случае для расчета длительности импульса используются те же соотношения, что и для одновибраторов.

Рис. 1.49. Формирователь импульсов на дифференцирующих цепях

На рис. 1.52 показана схема формирователя, в которой в зависимости от длительности запускающего импульса формируемый выходной импульс будет иметь фиксированную или укороченную длительность. Схема, приведенная на рис. 1.53, генерирует импульсы по переднему и заднему фронту входного сигнала. Причем выходные импульсы имеют всегда полную длительность, независимо от момента снятия сигнала запуска. Здесь допускается раздельная регулировка. Длительности и периода следования импульсов.

Схема, рис. 1.54, может использоваться для повторения входного сигнала с помехами по фронтам (от удаленного источника). Она позволяет улучшить форму импульсных сигналов со «звоном» (колебаниями по фронтам импульсов),

Рис. 1.50. Формирователи импульсов на основе интегрирующих цепей

Рис. 1.51. Формирователь импульса по фронту сигнала

Рис. 1 52. Формирователь импульса

Рис. 1.53. Формирователь импульсов по переднему и заднему

фронту входного сигнала

Pис 1.54. Повторитель входных импульсов с защитой от помех

что бывает при передаче сигнала по длинной, плохо согласованной линии или радиоканалу. Постоянная времени цепи R1-C1 зависит от периода следования входных импульсов и выбирается такой, чтобы к приходу спада входного импульса напряжение на конденсаторе С1 было близко к напряжению питания

Тогда первый же перепад входного импульса установит триггер D2.1 снова в единичное состояние.

Рис. 1.55. Формирователь импульсов с синхронизацией тактовой частотой

Большую помехоустойчивость и стабильность в работе обеспечивают схемы формирователей импульсов без использования RC-цепей, рис. 1.55…1.57. В этом случае выходные сигналы получаются синхронными с внутренней тактовой частотой. Процесс синхронизации сводится к сдвигу фронта импульса входной

информации до совпадения его с фронтом ближайшего тактового импульса. При этом длительность преобразованных таким образом информационных импульсов будет также определяться длительностью импульса синхрочастоты.

Рис. 1.56. Формирование двух импульсов

Рис. 1.57. Формирователь импульсов

Длительность формируемых схемой, рис. 1.55а, импульсов будет равна периоду тактовой частоты (T=1/fт), и ее легко можно изменить, меняя частоту на входе 2. Используя счетчики и комбинационную логику, можно получить выходной сигнал практически любой длительности.

Схема на рис. 1.56 обеспечивает на выходе формирование двух импульсов, привязанных к фронтам входного сигнала.

Схема, показанная на рис. 1.57, в зависимости от длительности информационного импульса на выходе дает синхронизированные с тактовой частотой одиночный импульс или же серию импульсов.

Цифровые схемы применяют также при передаче (обмене) не синхронизированных сигналов между устройствами. Каждый источник, как правило, имеет свой тактовый генератор и непосредственное использование этих сигналов может привести к сбоям из-за случайного разброса фаз тактовых импульсов. В этом случае становится обязательным привязка в приемном устройстве всех внешних управляющих сигналов к собственной тактовой частоте.

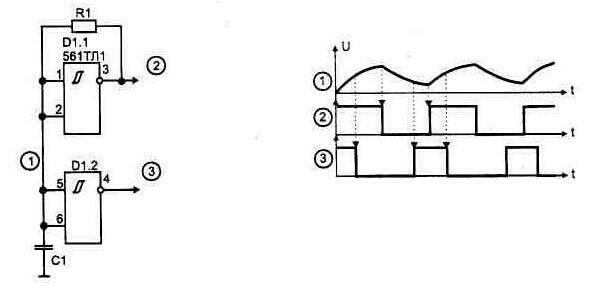

Что такое формирователь импульсов | Техника и Программы

Все приведенные схемы генераторов выдают меандр, в котором длительность паузы приблизительно равна длительности импульса, то есть скважность их равна примерно двум (на величину скважности влияет и величина резистора R2, см. схемы на рис. 16.2). Но нам могут потребоваться симметричные импульсы со скважностью, равной двум с большой точностью, или вообще с другим значением скважности. На рис. 16.5 показана схема, которая формирует импульсы со скважностью ровно 2 и 4 из исходного сигнала с любой скважностью. В ней используется делитель частоты на два (счетный триггер) — элемент, который мы еще «не проходили», но будем разбирать далее, а пока он приводится без пояснений. Диаграммы выходного напряжения приведены на рис. 16.5 внизу.

Следует отметить, что за счет задержки сигнала в триггере в момент, соответствующий фронту второго по счету сигнала исходной последовательности, на втором выходе может возникнуть короткая «иголка», так как спад импульса на выходе триггера наступит несколько позже наступления этого фронта. Она не страшна для статических схем (например, дешифраторов с выводом на индикаторы) или для управления внешними достаточно инерционными устройствами, но может вызвать срабатывание другого триггера или одновибратора (см. далее), если к его входу подключить выход этой схемы. Если это критично, то в таких схемах вместо простого счетного триггера обычно используют специальные синхронные счетчики (о них также далее). Разумеется, если требуется только симметричный меандр, то одного триггера достаточно, элемент «И-НЕ» можно исключить.

Рис. 16.5. Схема формирователя последовательности со скважностью 2 и 4

Микросхема 561ТМ2 (CD4013) содержит два триггера, поэтому схему легко дополнить, получив на выходе другие значения частоты и скважности. Применяя дополнительные логические элементы, можно получить 4 выхода, на каждом из которых фаза сдвинута ровно на полпериода исходной частоты — такие схемы применяют, например, для управления шаговыми двигателями или для управления елочной гирляндой «бегущие огни» (попробуйте составить такую схему сами!).

Большое значение на практике имеют формирователи коротких импульсов, называемые еще «схемами выделения фpoнтoв»^ На рис. 16.6, а приведена схема, которая делает это, как положено, используя эффект задержки сигнала в логическом элементе. При поступлении положительного фронта на вход он сразу же переключает выход последнего элемента «И-НЕ» в состояние логического нуля. На выходе цепочки из трех инверторов также возникнет логический ноль, который вернет выход в единичное состояние, но это прризойдет не сразу, а спустя время, равное утроенной задержке срабатывания логических .элементов. Поэтому на выходе возникнет короткая «иголка», достаточная по длительности (задержка-то тройная!) для надежного срабатывания других элементов схемы. Длительность таких импульсов составит для КМОП несколько десятков или сотен наносекунд. При желании можно выделить не фронт, а спад импульса (и получить при этом на выходе «иголку» положительной полярности^), для этого нужно использовать элементы «ИЛИ-НЕ». А если использовать «Исключающее ИЛИ», то можно получать положительные импульсы при каждом переключении сигнала — и по фронту и по спаду.

Все здорово, но схема уж больно громоздкая для такой простой функции — целый корпус! К тому же такие короткие импульсы очень сложно наблюдать на осциллографе. Поэтому на рис. 16.6, бив приведены гораздо более экономичные схемы, которые делают то же самое, но с нарушением чистоты цифровых принципов, ибо являются наполовину аналоговыми. Длительность импульса на выходе схем выделения фронтов при указанных на схеме номиналах составит около 10 мкс.

А на рис. 16.6, г показано использование интегрирующей цепочки для задержки импульса на фиксированное время. Диаграмм я не привожу, так как работа схемы понятна — передний фронт импульса задерживается на время, необходимое для заряда конденсатора до порога срабатывания инвертора. Задний фронт импульса, соответственно, задерживается на время разряда. Однако если при этом входной импульс сравним по длительности с постоянной времени RC, то на выходе импульс может быть уменьшенной длительности, а если входной импульс еще короче— выходной может вообще пропасть, поэтому такой схемой на практике пользуются редко, предпочитая одновибраторы, о которых мы сейчас и поговорим.

Рис. 16.6. Схемы формирователей импульсов: а — стандартная схема выделения фронтов; б, в — схемы с использованием дифференциальных RC-цепочек г — простейшая схема задержки

Формирователь одиночного импульса при включении

Что-то не так?

Пожалуйста, отключите Adblock.

Портал QRZ.RU существует только за счет рекламы, поэтому мы были бы Вам благодарны если Вы внесете сайт в список исключений. Мы стараемся размещать только релевантную рекламу, которая будет интересна не только рекламодателям, но и нашим читателям. Отключив Adblock, вы поможете не только нам, но и себе. Спасибо.

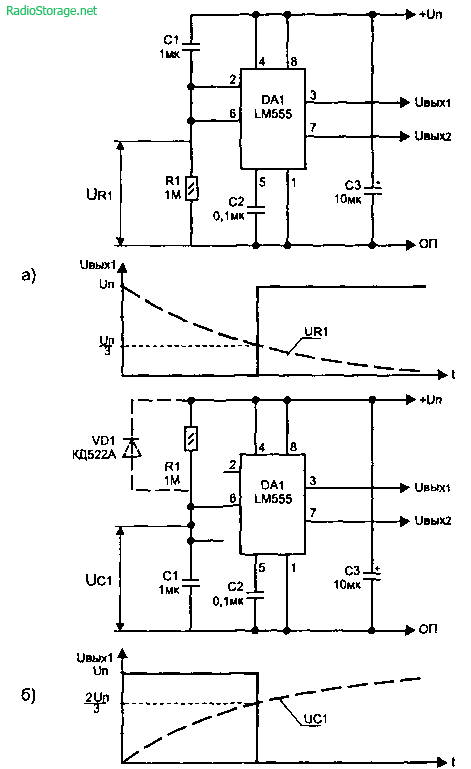

Как добавить наш сайт в исключения AdBlockНередко бывает необходимо сформировать одиночный импульс в момент включения устройства с некоторой задержкой на время окончания переходных процессов или по другой причине. Данная микросхема и в этом случае вас сможет выручить. На рис. 5.61 приведены два варианта таких формирователей. При номиналах, указанных на схеме, формируется интервал задержки 1,1 с. Для ускорения разряда времязадающего конденсатора (при отключении питания) параллельно с резистором в цепи заряда иногда устанавливают диод VD1 , включенный обратной полярностью.

Рис. 5.61. Формирователь одиночного импульса в момент включения питания: а — с задержкой включения; б — с задержкой отключения

Каскадное включение разных микросхем позволяет получить нужный вид задержки сигнала, например, как показано на рис. 5.62 (t, = 1,1 * R1 * С1; t2 = 1,1 * R2 * СЗ). При этом имеется возможность использовать два выхода. Микросхема позволяет прервать процесс заряда конденсатора в любой момент, если на вывод 4 подать нулевое напряжение. Этот вход обладает приоритетом при обнулении триггера, и если он не используется, то обычно соединяется с +Un, как это показано на рисунках.

Литература: Радиолюбителям: полезные схемы, Книга 5. Шелестов И.П.