Лабораторная работа 6. Мультиплексоры и демультиплексоры

1. Цель работы

1.Практическое освоение принципов построения мультиплексоров и демультиплексоров и экспериментальное их исследование на лабораторном стенде.

2. Теоретические основы

2.1 Мультиплексоры

Мультиплексор – это комбинационная многовходовая схема с одним выходом. Входы мультиплексора подразделяются на информационные Д0, Д1, …, Дn-1 и управляющие (адресные) А0, А1, …, Аk-1. Обычно 2k = n, где k и n – число адресных и информационных входов соответственно. Двоичный код, поступающий на адресные входы, определяет (выбирает) один из информационных входов, значение переменной с которого передается на выход

,

если

,

если  (1)

(1)

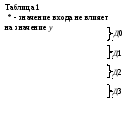

Таблица функционирования, описывающая работу мультиплексора, имеющего, например, n = 4 информационных (Д0, Д1, Д2, Д3) и k = 2 адресных (А0, А1) входов, представлена в таблице 1.

Вариант схемной реализации мультиплексора “4-1” (“четыре в один”, т.е. коммутирующего данные от одного из четырех входов на единственный выход) и его условное графическое изображение представлены на рисунке 2.1.1.

Здесь мультиплексор построен как совокупность двухвходовых конъюкторов данных (их число равно числу информационных входов), управляемых выходными сигналами дешифратора, дешифрирующего двоичный адресный код. Выходы конъюкторов объединены схемой ИЛИ.

Рисунок 2.1.1 Схема мультиплексора с дешифратором (а) и его условное графическое изображение

В интегральном исполнении применяется более простая схема, в которой конъюкторы дешифратора одновременно выполняют и функцию конъюкторов данных. Работа мультиплексора при этом описывается соотношением

(2)

(2)

Из (2) следует, что при любом значении адресного кода все слагаемые, кроме одного равны нулю. Ненулевое слагаемое равно Дi, где i – значение текущего адресного кода.

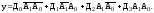

В соответствии с этим соотношением строятся реальные схемы мультиплексоров, одна из которых для мультиплексора “четыре в один” приведена на рисунке 2.1.2. Как правило, схема дополняется входом разрешения работы – Е (показан пунктирной линией). При отсутствии разрешения работы (Е=0) выход у становится нулевым и не зависит от комбинации сигналов на информационных и адресных входах мультиплексора.

Мультиплексоры 4-1, 8-1, 16-1 выпускаются в составе многих серий цифровых интегральных схем и имеют буквенный код КП. Например, К555КП1 – мультиплексор 2-1 (в данном корпусе размещаются четыре мультиплексора), К555КП12 – мультиплексор 4-1 (в одном корпусе размещаются два мультиплексора) и т.д.

В тех случаях, когда функциональные возможности ИС мультиплексоров не удовлетворяют разработчиков по числу информационных входов, прибегают к их каскадированию с целью наращивания числа входов до требуемого значения. Наиболее универсальный способ наращивания размерности мультиплексора состоит в построении пирамидальной структуры, состоящей из нескольких мультиплексоров. При этом первый ярус схемы представляет собой столбец, содержащий столько мультиплексоров, сколько необходимо для получения нужного числа информационных входов. Все мультиплексоры этого столбца коммутируются одним и тем же адресным кодом, составленным из соответствующего числа младших разрядов общего адресного кода. Старшие разряды адресного кода используются во втором ярусе, мультиплексор которого обеспечивает поочередную работу мультиплексоров первого яруса на общий выход.

Пирамидальная схема, выполняющая функцию мультиплексора “16-1” и построенная на мультиплексорах “4-1”, показана на рис. 2.1.3.

2.4 Мультиплексоры КМОП

Выше отмечалось, что по принципу действия мультиплексоры КМОП существенно отличаются от подобных устройств ТТЛ. В функциональном отношении между ними также существуют различия. Поскольку коммутация осуществляется при помощи управляемых вентильных ключей, проводящих в обоих направлениях, эта разновидность приборов с равным успехом может применяться в качестве мультиплексора и демультиплексора.

Сопротивление открытых вентильных ключей невелико (примерно 80 Ом) и мало зависит от проходящего сигнала. Такие ключи хорошо проводят аналоговые и импульсные сигналы. Разомкнутые ключи обеспечивают практически полный разрыв цепи, так как токи утечки ничтожно малы (не более 1 нА).

Когда на соответствующем входе микросхемы отсутствует разрешающий сигнал, все коммутируемые цепи разомкнуты, благодаря чему эту категорию приборов можно использовать с другими, имеющими три выходных состояния. Подобно прочим приборам КМОП они рассеивают очень малую статическую мощность независимо от состояния управляемых ключей.

Микросхема 564KП2 представляет собой восьмиканальный коммутатор (мультиплексор — демультиплексор) импульсных и аналоговых сигналов. Состоит она из дешифратора (с выходным устройством) и восьми двунаправленных вентильных ключей (рисунок 2.2.1). Управление вентильными ключами производится трехразрядным двоичным кодом, который подают на адресные входы С, В и А. На разрешающем входе

Неискаженная передача аналоговых сигналов большой амплитуды обеспечивается выбором питающих напряжений и схемой их подключения. Для питания микросхемы имеются три вывода. Ножка 8 служит общим выводом и, как правило, заземляется. Максимальное напряжение, прикладываемое к двум выводам микросхемы, не должно быть более 15 В. Амплитуды коммутируемых сигналов не должны превышать напряжения питания. Максимальный ток через открытый ключ 10 мА.

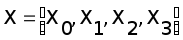

Таблица истинности микросхемы 564КП2

Входы | Проводящие ключи | ||||

V | C | B | A | ||

0 | 0 | 0 | 0 | Х=х0 | |

0 | 0 | 0 | 1 | =х1 | |

0 | 0 | 1 | 0 | =х2 | |

0 | 0 | 1 | 1 | =х3 | |

0 | 1 | 0 | 0 | =х4 | |

0 | 1 | 0 | 1 | =х5 | |

0 | 1 | 1 | 0 | =х6 | |

0 | 1 | 1 | 1 | =х7 | |

1 | Х | Х | Х | Все ключи разомкнуты | |

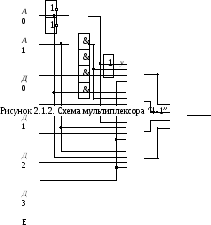

На рисунке 2.2.2 показаны примеры включения источников питания для нескольких вариантов коммутации аналоговых сигналов. Наращивание числа входов осуществляется тем же способом, что и у мультиплексоров ТТЛ.

Рис. 2.2.2 Примеры подключения источников питания к микросхемам 564КП2 и 564КП1 в зависимости от коммутируемых сигналов: а — paзмах сигнала от 0 до 15 В; б —от —7.5 до + 7.5 В; в —от —10 до +5 В; г —от —3 до +3 В

В микросхеме 564КП1 также восемь каналов, но они разделены на две синхронно работающие группы по четыре канала в каждой (рисунок 2.2.3). Управление осуществляется по двум адресным входам A и B. Действие разрешающего входа не отличается от описанного ранее. Микросхема предназначена для коммутации дифференциальных аналоговых сигналов, но может быть использована и для управления двумя независимыми сетями. Таблица истинности микросхемы 564КП1 приведена в виде таблице 2. В отношении питания данная микросхема подобна прибору 564КП2

а

а

Рисунок 2.2.3 Логическая структура микросхемы 564КП1

Таблица 2

Таблица истинности микросхемы 564КП1

Входы | Проводящие ключи | |||

V | B | A | ||

0 | 0 | 0 | Х=х0 ;Y=y0 | |

0 | 0 | 1 | =х1; =y1 | |

0 | 1 | 0 | =х2; =y2 | |

0 | 1 | 1 | =х3; =y3 | |

1 | Х | Х | Все ключи разомкнуты | |

2.3 Демультиплексоры

Демультиплексор – схема, выполняющая функцию, обратную функции мультиплексора, т.е. это комбинационная схема, имеющая один информационный вход (Д), n информационных выходов (у0, у1, …, уn-1) и k управляющих (адресных) входов (А0, А1, …, Аk-1). Обычно, также как и мультиплексоров, 2k= n. Двоичный код, поступающий на адресные входы, определяет один из n выходов, на который передается значение переменной с информационного входа (Д), т.е. демультиплексор реализует следующие функции:

(3)

Таблица функционирования демультиплексора, имеющего n = 4 информационных выходов (у0, у1, у2, у3) и k = 2 адресных входов (А0, А1), представлена в таблице 3.

Таблица 3

Д | А0, А1 | у0у1у2у3 | Д | А0, А1 | у0у1у2у3 |

0 1 0 1 | 0 0 0 0 0 1 0 1 | 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 | 0 1 0 1 | 1 0 1 0 1 1 1 1 | 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 |

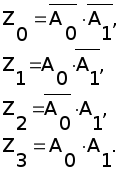

Уравнения, описывающие работу демультиплексора:

(4)

(4)

Схема демультиплексора, построенная по данным уравнениям и его графическое изображение представлены на рисунке 2.3.1.

Рисунок 2.3.1 Схема демультиплексора «1-4» (а) и его условное изображение (б)

Функция, выполняемая демультиплексором, сходна с функцией дешифратора. Разница состоит лишь в том, что в демультиплексоре выход, обозначенный кодом адреса, активизируется только тогда, когда входной информационный сигнал активен, то есть функция для некоторого выхода демультиплексора имеет вид:

mi= mi’W

где mi— функция, полученная при синтезе дешифратора, W – входной информационный сигнал.

Функция демультиплексора легко реализуется с помощью дешифратора, если его вход “Разрешение” (Е) использовать в качестве информационного входа демультиплексора, а входы 1, 2, 4 … — в качестве адресных входов демультиплексора А0, А1, А2, … Действительно, при активном значении сигнала на входе Е избирается выход, соответствующий коду, поданному на адресные входы. Поэтому ИС дешифраторов, имеющих разрешающий вход, иногда называют не просто дешифраторами, а дешифраторами-демультиплексорами.

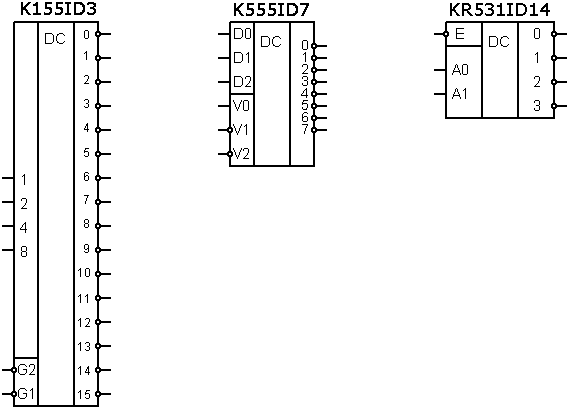

Примеры ИС:

К555ИДЗ — дешифратор-демультиплексор (дешифратор 4-16 с двумя входами стробирования: демультиплексор на 16 выходов со входом стробирования).

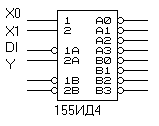

К555ИД4 — дешифратор-демультиплексор (два дешифратора 2-4; два демультиплексора на 4 выхода с объединенными адресными входами и раздельными входами стробирования).

Примечание: ввиду схожести функций дешифратора и мультиплексора промышленностью, как правило, выпускаются стробируемые дешифраторы, которые в зависимости от использования стробирующего входа могут использователя как дешифраторы или демультиплексоры.

2.4 Применение мультиплексоров и демультиплексоров

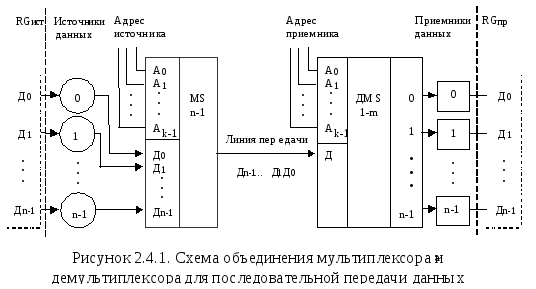

Под термином “мультиплексирование” называют процесс передачи данных от нескольких источников по общему каналу, а устройство, осуществляющее на передающей стороне операцию сведения данных в один канал, принято называть мультиплексором. Подобное устройство способно осуществлять временное разделение сигналов, поступающих от нескольких источников, и передавать их в канал (линию) связи друг за другом в соответствии со сменой кодов на своих адресных входах.

На приемной стороне обычно требуется выполнить обратную операцию – демультиплексирование, т.е. распределение порций данных, поступивших по каналу связи в последовательные моменты времени, по своим приемникам. Эту операцию выполняет демультиплексор. Совместное использование мультиплексора и демультиплексора для передачи данных от n источников к n приемникам по общей линии иллюстрирует рисунок 2.4.1. (В общем случае число источников данных не равно числу приемников).

Если в схеме (рисунок 2.4.1) n различных источников и приемников заменить n-разрядными источником и приемником, например, регистрами RGист. и RGпр. (изображены пунктирными линиями), то схема может быть использована для преобразования n-разрядного параллельного кода на передающей стороне в последовательный код (с помощью мультиплексора) и последовательного кода в параллельный на приемной стороне (с помощью демультиплексора). При подобном применении мультиплексора и демультиплексора в качестве их адресных кодов используются выходные сигналы двоичного счетчика, последовательно формирующего на своих выходах двоичные коды чисел от 0 до n-1.

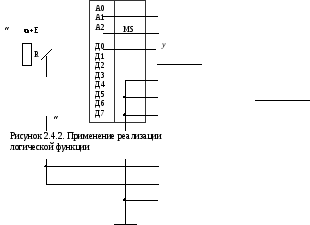

Мультиплексор можно использовать в качестве универсального логического элемента для реализации любой логической функции от числа аргументов, равного числу адресных входов мультиплексора. Покажем это на примере логической функции, заданной своей таблицей истинности (таблица 4).

Выбираем мультиплексор, имеющий три адресных (по числу аргументов функции) и восемь информационных входов. Для реализации заданной функции информационные входы мультиплексора соединим с уровнями логических “1” и “0” в такой последовательности, которая полностью копирует последовательность единиц и нулей функции в таблице истинности (рисунок 2.4.2). При этом не требуется ни записи СДНФ, ни ее минимизации. Кстати, функция, заданная таблицей 1 (четность числа единиц в трехразрядном слове), не упрощается, поэтому для своей реализации, например, в базисе ЛЭ “И-НЕ” требует четырех ЛЭ “3И-НЕ” и трех инверторов, т.е. в сумме потребуется три ИС. В то же время для реализации схемы по рисунку 2.4.2, требуется всего одна ИС мультиплексора “8-1”. По этой причине, способ реализации функций трех или большего числа аргументов с помощью ИС мультиплексоров весьма популярен у разработчиков.

3. Порядок выполнения работы

1. Используя ЛЭ, установленные на лабораторном стенде, спроектировать схему мультиплексора и исследовать его работу (снять таблицу истинности).

2. Исследовать работу (снять таблицу истинности) ИС мультиплексора К531КП1(2), селектора-мультиплексора 555КП2, демультиплексора ИД4.

4. Контрольные вопросы

Понятие мультиплексор. Принцип действия мультиплексора 4-1.

Как можно увеличить размерность мультиплексора?

КМОП-мультиплексоры. Особенности и применение.

Принцип действия микросхем 564КП1 и 54КП2.

Понятие демультиплексора. Принцип действия демультиплексора 1-4.

Где применяются мультиплексоры и демультиплексоры?

Как организовать логические функции на мультиплексорах?

Мультиплексор и демультиплексор.

Мультиплексор — комбинационное

устройство, предназначенное для

подключения одного из n информационных

входов к единственному выходу. Помимо

информационных входов мультиплексор

имеет адресные входы, на которые подается

в параллельном коде адресное слово.

Между количеством информационных входов

и разрядностью адресного слова существует

однозначное соотношение  ,

где: n — количество информационных

входов, k — количество разрядов адресного

слова.

,

где: n — количество информационных

входов, k — количество разрядов адресного

слова.

Рис. 60. Структурная схема мультиплексора.

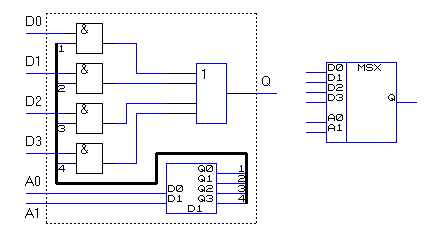

На рисунке представлен вариант структурной схемы мультиплексора. В ее состав входят: дешифратор D1(выходы активны высоким уровнем), логические элементы 2И, выполняющие функции ключей, логический элемент 4ИЛИ. Схема работает следующим образом. Дешифратор имеет активный уровень только на одном из выходов, номер активного выхода определяется значением адреса А0, А1. Сигнал высокого уровня с выхода дешифратора разрешает прохождение информационного сигнала через один элемент 2И. На выходах других элементов 2И будет нулевой уровень и, следовательно, на выходе элемента 4ИЛИ будет сигнал прошедший через элемент 2И. При изменении адресного слова будет меняться открываемый элемент 2И. Таким образом, изменяя адресное слово можно изменять разряды информационного слова подключаемые к единственному выходу.

Если выходную переменную мультиплексора

обозначить y, а информационные входные

— ,

то функционирование мультиплексора

может быть описано уравнением

,

то функционирование мультиплексора

может быть описано уравнением

,

,

где:  —

вектор строка входных переменных;

—

вектор строка входных переменных; —

селекторная матрица, получаемая из

адресного слова по уравнениям дешифрации.

—

селекторная матрица, получаемая из

адресного слова по уравнениям дешифрации.

Таким образом, селекторная матрица является диагональной. Выполнив скалярное умножение получаем:

Полученное логическое уравнение, описывающее работу мультиплексора, показывает, что мультиплексор — это универсальное логическое устройство.

x | y | z | f |

0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 |

0 | 1 | 0 | 1 |

0 | 1 | 1 | 0 |

1 | 0 | 0 | 1 |

1 | 0 | 1 | 0 |

1 | 1 | 0 | 0 |

1 | 1 | 1 | 1 |

Таблица 11

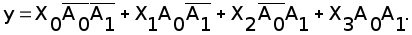

Рис. 61. Реализация функции на мультиплексоре.

ра соответственно подавать либо “0”, либо “1”. Подобная реализация функции, в соответствии с заданием (табл. 11), показана на рис. 61. На входах и выходе мультиплексора указаны обозначения функции и ее аргументов в соответствии с заданием.

Однако такая реализация функции приводит к недоиспользованию аппаратуры.

Для более эффективного использования аппаратуры желательно один или несколько аргументов функции использовать не в качестве адресных переменных, а в качестве информационных переменных. Так, если в рассмотренном примере один из аргументов подавать на информационные входы, то для адресных переменных останется только два аргумента и, следовательно, потребуется мультиплексор только на четыре информационных входа. Предположим, что на информационные входы будем подавать переменную “z”. Тогда в качестве адресных останутся — “x” и “y”, при этом таблица задания функции примет вид — см. табл. 12. Как видно из таблицы и рисунка реализуется та же самая функция, но необходим мультиплексор только на четыре входа. Использована половина микросхемы 155КП2.

Т аблица

12.

аблица

12.

x

y

f

0

0

z

0

1

1

0

1

1

z

Рис. 62. Реализация минимизированной функции.

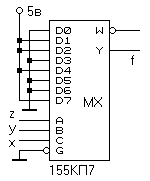

Операция мультиплексирования состоит в подключении одного из многих входов к единственному выходу. Однако часто требуется выполнить операцию демультиплексирования — информацию с единственного входа передать на один из многих выходов. Такая операция легко выполняется на дешифраторе, у которого есть вход стробирования, на который подается сигнал разрешения выполнения операции. Обычно этот сигнал активен низким уровнем. При обычном использовании дешифратора, если на этом входе низкий уровень, то выполняется операция дешифрации, если же — высокий, то на всех выходах дешифратора имеются сигналы высокого уровня и операция дешифрации не выполняется. Часто дешифратор, имеющий вход стробирования называют — дешифратор-демультиплексор. Рассмотрим, как выполняется демультиплексирование.

В

Рис.62. Демультиплексор.

качестве демультиплексора будем использовать половину микросхемы 155ИД4, обозначенную А. На входы 1 и 2 подадим разряды адресного слова, соответственно X0 и X1. На входы стробирования 1А и 2А подадим соответственно: входные данные и Y. Второй дешифратор будет в нерабочем состоянии, так как его входы стробирования никуда не подключены, а это соответствует подачи на них высокого уровня напряжения. Входы стробирования для дешифратора В активны низким уровнем, а на них подан высокий уровень, и, следовательно, дешифратор не работает. Работа демультиплексора полностью отображена на временной диаграмме рис. 63.Анализируя временную диаграмму, приходим к выводу:

— при Y=1 разрешена работа и выполняется демультиплексирование,

— при Y=0 работа микросхемы запрещена,

— при X0=X1=0 входная информация DI появляется на выходе А0,

— при X0=1 и X1=0 входная информация на выходе А1,

— при X0=0 и X1=1 входная информация на выходе А2,

— при X0=1 и X1=1 входная информация на выходе А3.

Рис.63. Временная диаграмма работы дешифратора- демультиплексора.

Таким образом, изменяя состояния адресных переменных X0 и X1 осуществляется разнос входной информации на один из выходов микросхемы — осуществляется операция демультиплексирования.

Следовательно, любой дешифратор, имеющий вход стробирования может быть использован в качестве демультиплексора.

Лекция 21.

Демультиплексор — это… Что такое Демультиплексор?

Условное графическое обозначение (УГО) демультиплексора «1 в 4».Демультиплексор — это логическое устройство, предназначенное для переключения сигнала с одного информационного входа на один из информационных выходов. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. На схемах демультиплексоры обозначают через DMX или DMS.

Суть и схема реализации

В случае ТТЛ логики для коммутации каналов применяются логические элементы «И». В КМОП микросхемах широко применяются ключи на полевых транзисторах. Поэтому в них отсутствует понятие демультиплексора. Информационные входы и выход можно поменять местами, в результате чего мультиплексор может служить в качестве демультиплексора.

Если между числом выходов и числом адресных входов действует соотношение n=2m для двоичных демультиплексоров или n=3m для троичных демультиплексоров, то такой демультиплексор называют полным. Если n<2m для двоичных демультиплексоров или n<3m для троичных демультиплексоров, то демультиплексор называют неполным. Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют роль входов дешифратора. Поэтому в обозначении как дешифраторов, так и демультиплексоров в отечественных микросхемах используются одинаковые буквы — ИД.

Демультиплексоры выполняют унарные (одновходовые, однооперандные) логические функции с n-арным выходом.

Схема демультиплексора «2 на 4»См. также

- Мультиплексор

- Дешифратор — это коммутатор сигналов на один из нескольких выходов. При наличии разрешающего входа дешифратор можно использовать как демультиплексор.

Примечания

Литература

- Цифровая схемотехника Е. Угрюмов

Ссылки

Микросхемы, производившиеся в СССР Микросхемы, производившиеся в СССР | |||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Технологии | РТЛ • ДТЛ • ТТЛ • ЭСЛ • N-МОП • КМОП • И3Л | ||||||||||||||||||||||||||||||||||||||||

| Система обозначения по ГОСТ 18682-73 |

| ||||||||||||||||||||||||||||||||||||||||

| Тип корпуса (ГОСТ 17467-72) | Тип 1 • Тип 2 • Тип 3 • Тип 4 • | ||||||||||||||||||||||||||||||||||||||||

| Производители | Ангстрем • Алмаз • ВНИИС • ЕРЗ • ИРЗ • Интеграл • Полёт • МНИИПА • НИИЭТ • МЦСТ | ||||||||||||||||||||||||||||||||||||||||

§ 2.4. Мультиплексоры и демультиплексоры

Функциональные узлы комбинационного типа | 91 |

Мультиплексоры

Мультиплексоры осуществляют подключение одного из входных каналов к выходному под управлением адресующего кода. Разрядности каналов могут быть различными, мультиплексоры для коммутации многоразрядных слов составляются из одноразрядных.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| б | |||

Рис. 2.10. Упрощенное представление мультиплексора многопозиционным ключом (а) и реализация мультиплексора на элементах И-НЕ (б)

Входы мультиплексора делятся на две группы: информационные и адресующие (управляющие). Работу мультиплексора можно упрощенно представить с помощью многопозиционного ключа. Для одноразрядного мультиплексора это представлено на рис. 2.10, а. Адресующий код А задает переключателю определенное положение, соединяя с выходом F один из информационных входов xi. При нулевом адресующем коде переключатель занимает верхнее положение x0, с увеличением кода на единицу переходит в соседнее положение x1 и т. д.

Работа мультиплексора описывается соотношением

F = x0аn-1an 2 …a1a0 x1an 1an 2 …a1a n 2 …a1a0 … x2n 1a n 1a n 2 …a1a0 ,

которое иногда называют мультиплексной формулой. При любом значении адресующего кода все слагаемые, кроме одного, равны нулю. Ненулевое слагаемое равно хi, где i — значение текущего адресного кода.

Схемотехнически мультиплексор реализует электронную версию показанного переключателя, имея, в отличие от него, только одностороннюю передачу данных. На рис. 2.10, б показан мультиплексор с четырьмя информационными входами, двумя адресными входами и входом разрешения работы. При отсутствии разрешения работы (Е = 0) выход F становится нулевым независимо от информационных и адресных сигналов. В стандартных сериях размерность мультиплексоров не более 16×1.

Мультиплексоры в КМОП-схемотехнике

Схемотехника мультиплексоров на элементах КМОП имеет свои особенности. В число элементов схемы здесь наряду с обычной логикой входят специальные двунаправленные ключи, что позволяет строить экономичные структуры как мультиплексоров, так и других устройств (в частности, триггеров).

Двунаправленный ключ. Ключ (рис. 2.11) составлен из двух параллельно включенных транзисторов с взаимоинверсными напряжениями C и С на затворах. Один из транзисторов имеет n-канал, а другой — p-канал.

Упр

C

Рис. 2.11. Двунаправленный ключ

Такая схема позволяет получать замкнутое состояние ключа с приблизительно постоянным и малым сопротивлением независимо от величины переключаемого напряжения (т. е. напряжения UA ≈ UB, что имеет место в замкнутом ключе). При этом ключ может работать при идентичных уровнях переключаемого и управляющего напряжений, как это и требуется для цифровых схем.

Обычный однотранзисторный ключ указанного свойства не имеет. У него уровни входного (управляющего) и переключаемого напряжений не могут быть одинаковыми. Если, например, на затвор транзистора с n-каналом подать отпирающее напряжение U1 (уровень логической единицы), то переключаемое напряжение (UA ≈ UB) должно быть меньше чем U1, по меньшей мере на величину порогового напряжения, т. е. приблизительно вдвое. Иначе нарушится условие возникновения в транзисторе проводящего канала (Uзи >Uпор, где Uзи — напряжение на затворе относительно истока и Uпор — пороговое напряжение транзистора). Практически же максимальное переключаемое напряжение долж-

Функциональные узлы комбинационного типа | 93 |

но быть еще меньше, т. к. при приближении к порогу резко увеличивается сопротивление канала и ухудшаются условия передачи сигналов. Указанное обстоятельство исключает применение однотранзисторных ключей для передачи логических сигналов под управлением других логических сигналов, поскольку в этом случае не обеспечивается превышение сигналов на затворах ключей над переключаемыми сигналами.

Иначе выглядит ситуация для ключей с параллельным включением двух разнотипных транзисторов. Подача на затвор транзистора с p-каналом низкого напряжение, а на затвор транзистора с n-каналом — высокого напряжения приводит ключ в замкнутое состояние. Изменение переключаемого напряжения при постоянстве напряжений на затворах изменяет напряжения «затвор-исток» и «затворсток», но при этом сопротивление одного из транзисторов растет, а другого падает, так что общее сопротивление ключа остается низким и приблизительно постоянным и, тем самым, решается проблема успешной передачи логических сигналов без потери их амплитуды. При подаче на затвор транзистора с р-каналом высокого напряжения, а на затвор транзистора с n-каналом — низкого напряжения, оба транзистора запираются и ключ размыкается.

Рис. 2.12. Структура мультиплексора, реализованного в КМОП-схемотехнике

В КМОП-схемотехнике одна и та же схема функционирует как мультиплексор или демультиплексор (при перемене местами входов и выходов). Кроме того, схема может работать не только с цифровыми, но и с аналоговыми сигналами, поскольку двунаправленный ключ на двух транзисторах обладает высоким качеством и способен передавать уровни сигналов с весьма высокой точностью. Схема мультиплексора/демультиплексора показана на рис. 2.12.

Рассмотрим режим мультиплексора «4—1». Входные сигналы D0…D3 подключены к КМОП-ключам, выходы которых соединены друг с другом в точке выхода мультиплексора. Адресующий код A1A0 дешифрируется и вырабатывает управляющий

сигнал разрешения работы, т. е. замыкания, для ключа, номер которого соответствует коду A1A0. Остальные ключи остаются запертыми. Таким образом, на выход передается один из входных сигналов под управлением адресующего кода. Сигнал EN разрешает или запрещает работу мультиплексора.

Многоразрядные мультиплексоры

Для коммутации многоразрядных данных строятся мультиплексоры, представляющие собою совокупность одноразрядных схем. В этом случае мультиплексор характеризуется числом входных каналов n и их разрядностью m (рис. 2.13, а ).

|

|

| DI | MUX DO |

|

|

|

| MUX |

|

|

| 00 |

|

|

|

| 01 |

|

|

|

| 10 | 0 |

|

|

| 11 |

|

|

|

| 20 | 1 |

m |

| log2n | 21 |

|

| 30 | 2 | ||

|

|

| 31 |

|

m |

| m | 3 |

|

|

| |

|

|

| A |

n |

|

|

|

m |

|

| EN |

|

|

| |

| а |

| б |

|

|

|

Рис. 2.13. Структура (а) и условное графическое обозначение (б) многоразрядного мультиплексора

EN

A1

1

1

DI00

&

1 DO0

DI30

&

DO3

1

Рис. 2.14. Функциональная схема двухканального четырехразрядного мультиплексора

3.3.3 Мультиплексоры и демультиплексоры

Мультиплексором

называется функциональный узел,

обеспечивающий передачу информации,

поступающей по нескольким входным

линиям связи, на одну выходную линию

(рис. 3.7). При наличии n адресных входов

можно реализовать М=2nкомбинаций

адресных сигналов, каждая из которых

обеспечивает выбор одной из М входных

линий. Вход Е — разрешающий: при Е=1

мультиплексор работает как обычно, при

Е=0 выход узла находится в неактивном

состоянии, мультиплексор заперт. Входы

D0 — D3 информационные входы, А1 и А2 —

адресные.

Рис.3.7. Условное обозначение мультиплексора

В общем виде выходная функция мультиплексора «из М в 1» записывается в виде:

,

,

Выбор той или иной входной линии осуществляется в соответствии с поступающим адресным кодом.

Один из способов увеличения числа коммутируемых каналов в схемах построенных на мультиплексорах со стробированием показан на рис 3.8. Приведенная схема представляет собой мультиплексор из 16 в 1.

Рис 3.8. Мультиплексор со стробированием

Второй способ увеличения числа коммутируемых каналов показан на рис 3.9. Вместо элемента И-НЕ на выходе используется дополнительный мультиплексор, производящий выбор одного из мультиплексоров с помощью адресных сигналов А4, A5, A6. Такое соединение называют мультиплексорное дерево. Мультиплексоры MS1 и MS2 являются мультиплексорами первого уровня, а MS3 второго. На первом и втором уровнях можно использовать мультиплексоры с разным числом входов. Если на первом уровне используются мультиплексоры с числом адресных входов n1, на втором – с числом n2 то общее количество входов мультиплексорного дерева составит n = 2n1+ 2n2, а число мультиплексоров 2n2+ 1.

Рис 3.9. Мультиплексорное дерево

Применение мультиплексоров не ограничивается операцией мультиплексирования. Мультиплексоры применяют для сдвига информации, для реализации логических функций заданных какой-либо таблицей функционирования, для передачи слова прямым или обратным кодом в зависимости от управляющего уровня. Мультиплексор можно использовать в качестве универсального логического элемента для реализации любой функции от числа переменных, равного числу адресных входов. Мультиплексор показанный на рисунке реализует функцию согласно таблице. Если бы эта функция реализовывалась на базисе И-НЕ то понадобилось бы четыре элемента 3И-НЕ и три инвертора.

При коммутации многоразрядных слов в каждом разряде используется свой мультиплексор.

Для восстановления мультиплексированной информации используют демультиплексоры, которые в соответствии с принятым адресом направляют информацию в одну из выходных линий. При этом на остальных выходных линиях поддерживается логический 0.

В роли демультиплексора успешно выступает декодер, если к его разрешающему входу Е подключить мультиплексированную магистраль данных, а на адресные входы подавать друг за другом коды адресов приемника.

3.3.4 Комбинационные сумматоры

Основной операцией при выполнении арифметических действий в современных цифровых системах является сложение. Поэтому основным блоком операционных устройств обычно является сумматор (рис. 3.10), который используется также для вычитания, умножения, деления, преобразования чисел в дополнительный код, код «с избытком 3» и в ряде других операций.

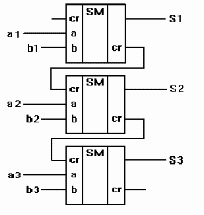

Рис.3.10. Сумматор

Сумматор имеет nвходов разрядов слагаемого А,nвходов разрядов слагаемогоBи вход переносаcr. Выходами сумматора являютсяnвыходов разрядов суммыSи выход переноса (переполнения)cr.

Суммирование многоразрядных чисел производится путем их поразрядного сложения с переносом между разрядами. Поэтому многоразрядные сумматоры состоят из комбинационных одноразрядных сумматоров. Такой сумматор выполняет сложение одноразрядных двоичных чисел Ai, Bi и переноса из младшего разряда Ci, образуя на выходах значение суммы Si и перенос в старший разряд Ci+1.

Многоразрядные сумматоры в зависимости от способа ввода кодов слагаемых делятся на последовательного и параллельного действия.

В сумматоры первого типа коды чисел вводятся в последовательной форме, т.е. разряд за разрядом (младшим разрядом вперед), в сумматоры второго типа каждое слагаемое подается в параллельной форме, т.е. одновременно всеми разрядами.

Сумматор последовательного действия (рис 3.11) состоит из одноразрядного сумматора, выход Рi+1 которого соединен с входом Pi через D –триггер. С первым тактовым импульсом на входы сумматора поступают с выходов регистров (1,2) цифры первого разряда слагаемых aiиbi, а из D –триггера на вход Pi подается логический 0. Суммируя поданные на входы цифры, сумматор формирует на выходе первый разряд суммы S1 и перенос Рi+1 принимаемый в D –триггер. Со следующим тактовым импульсом на входы подаются цифры второго разряда и перенос Рi+1 и т.д.

Рис 3.11. Сумматор с последовательным переносом

Достоинство такого сумматора заключается в небольших аппаратных затратах. Однако он обладает малым быстродействием.

Сумматоры параллельного действия строятся с использованием нескольких одноразрядных сумматоров. В зависимости от способа организации переноса между ними сумматоры параллельного действия бывают с последовательным, параллельным и комбинированным переносом.

В сумматорах с последовательным переносом выход переноса cr каждого разряда подключен ко входу переноса cr самого младшего разряда. Таким образом, задача построения сумматора с последовательным переносом сводится к построению схемы одноразрядного сумматора. В сумматоре с последовательным переносом тракты переносов всех одноразрядных сумматоров соединены последовательно. Поэтому даже при минимальной задержке тракта переноса в 1tззадержка n – разрядного сумматора будет не менее ntз.

Для уменьшения задержки используется принцип параллельного переноса, когда входной перенос каждого разряда вырабатывается независимо от переноса соседнего младшего разряда. Для всех разрядов сигналы переноса формируются параллельно. Общая структурная схема многоразрядного сумматора с параллельным переносом представлена на рис 3.12

Рис 3.12. Сумматор с параллельным переносом

В этой схеме блоки суммы одинаковы для всех разрядов и реализуют функцию суммы. Блок переноса вырабатывает сигнал переноса одновременно для всех блоков суммы. Однако аппаратурные затраты такого сумматора превышают затраты сумматора с последовательным переносом и быстро растут с ростом разрядности. Поэтому разрядность реально используемых сумматоров с параллельным переносом редко превышает восьми.

Для ускорения переноса в сумматорах с большой разрядностью используется принцип группового переноса. Сумматор разбивается на группы, представляющие собой сумматоры с разрядностью от 2 до 8. Каждый такой мини сумматор имеет свой вход переноса. При разбиении сумматора на группы соблюдают условие n=ml, где n-общее число разрядов сумматора; l-число выделенных групп; m-число одноразрядных сумматоров.

Суть группового переноса заключается в том, что в дополнение к тракту переноса внутри группы строят тракт переноса между группами, который вырабатывает сигналы групповых переносов. При этом как в каждой группе, так и между группами возможны различные виды переноса. Среди таких структур наибольшее распространение получили схемы с цепным и параллельно-параллельным переносом.

Сумматоры с цепным переносом реализуют внутри выделенных групп параллельный перенос, в то время как между группами используется последовательный перенос. Такой подход позволяет повысить быстродействие по сравнению с последовательными сумматорами большой разрядности.

Сумматоры с параллельно-параллельным переносом реализуют как внутри группы, так и между ними принцип параллельного переноса. Такие сумматоры большой разрядности обладают наибольшим быстродействием.

Полусумматор — это комбинационное устройство выполняющее сложение разрядов двоичных чисел. В отличии от сумматора полусумматор воспринимает только два сигнала: сигнал разряда числа А и сигнал разряда числа В. Сигнал переноса полусумматор не воспринимает.

9. Мультиплексоры и демультиплексоры

9.1. Общие сведения

Мультиплексором (MUX) называется комбинационное устройство, предназначенное для коммутации в желаемом порядке сигналов с нескольких входных шин на одну выходную (бесконтактный многопозиционный переключатель). С помощью мультиплексора осуществляется временное разделение информации, поступающей по разным каналам (коммутатор с n входов на один выход).

Функции демультиплексора противоположны функциям мультиплексора – это коммутатор с одного входа на n выходов.

Мультиплексоры и демультиплексоры в микросхемном исполнении имеют несколько групп входов. Число выходов мультиплексора один или два (мультиплексоры с парафазным выходом). Число выходов демультиплексора определяется числом адресных входов. Входы делятся на следующие группы: информационные, управления, адресные, разрешающие. Если адресных входов n, то число информационных входов мультиплексора D = 2n. Общее число входов мультиплексора равно

N = n + 2n + v + с,

где v – число разрешающих входов;

с – число управляющих входов;

n – число адресных входов.

Кроме прямого назначения мультиплексор может использоваться для преобразования параллельного кода на входах в последовательный код на выходе. Для этого код на адресных входах должен циклически изменяться, принимая все последовательные значения. Такое изменение кода можно обеспечить, присоединив к адресным входам выходы счетчика, последовательно изменяющего свое состояние под действием импульсов генератора.

9.2. Мультиплексоры

Набор сигналов на адресных входах определяет конкретный информационный вход Di, который будет соединен с выходом. Пример мультиплексора на два информационных входа представлен на рис. 9.1.

Рис. 9.1. Мультиплексор 2 : 1

Наличие разрешающих входов расширяет возможности мультиплексора, позволяя синхронизировать его работу с работой других узлов. Эти входы используются также для наращивания разрядности. На рис. 9.2 представлены структура четырехвходового мультиплексора с одним разрешающим входом и условное графическое обозначение мультиплексора на восемь входов с одним инверсным разрешающим входом.

Работа мультиплексора 4:1 описывается следующим логическим уравнением:

Из уравнения следует, что структура мультиплексора состоит из 2nсхем совпадения, каждая из которых имеет n адресных, один информационный и один стробирующий вход, и одной схемы ИЛИ с 2n входами. Ее выход является выходом мультиплексора.

В интегральном исполнении мультиплексоры выпускают на четыре, восемь или шестнадцать входов. Большее число входов обеспечивается путем объединения нескольких микросхем. Используют два способа наращивания числа входов: объединение (каскадирование) нескольких мультиплексоров в пирамидальную (древовидную) систему и использование разрешающих входов с подключением дополнительных логических элементов.

Пирамидальные мультиплексоры строят по ступенчатому принципу и применяют обычно две, реже три и более ступеней (рис. 9.3). Младшие разряды кода адреса подают на адресные входы первой ступени, а ступеням более высокого ранга соответствуют старшие разряды кода адреса. На рис. 9.3 представлен вариант мультиплексора 32:1 на основе четырех мультиплексоров 8:1 в первой ступени и одного мультиплексора 4:1 во второй ступени.

а б

Рис. 9.2. Структура мультиплексора 4:1 (а) и условное графическое

обозначение мультиплексора 8:1 (б)

Недостатками пирамидального наращивания являются повышенный расход микросхем и снижение быстродействия из-за суммирования задержек при последовательном прохождении сигналов по ступеням пирамиды.

Рис. 9.3. Пирамидальный двухступенчатый мультиплексор 32:1

Мультиплексор 32:1 можно получить на основе двух микросхем 16:1. Такая схема на базе двух мультиплексоров 155КП1 представлена на рис. 9.4.

Рис. 9.4. Мультиплексор с использованием разрешающих входов

Работа мультиплексоров КМОП серий отличается от работы мультиплексоров ТТЛ.

При работе с логическими элементами КМОП электронный ключ очень легко получить на одном или двух МОП-транзисторах, поэтому в КМОП схемах логический элемент И в качестве электронного ключа не используется. Упрощённая схема электронного ключа, выполненного на комплементарных МОП-транзисторах, приведена на рис. 9.5. Даже одиночный n-канальный или p-канальный полевой транзистор может служить аналоговым ключом, но его сопротивление в открытом состоянии будет значительно зависеть от величины коммутируемого сигнала. Соединение n-канального и p-канального МОП-транзистора в параллель резко снижает эту зависимость.

Рис. 9.5. Схема электронного ключа, выполненного на МОП-транзисторах

Такой ключ может коммутировать как цифровые, так и аналоговые сигналы. Сопротивление открытых транзисторов составляет, обычно, от единиц до десятков Ом, а сопротивление закрытых транзисторов превышает десятки мегом. В этом есть как преимущества, так и недостатки. То, что ключ, собранный на МОП-транзисторах, не является обычным логическим элементом, позволяет объединять выходы электронных ключей в соответствии со схемой, приведенной на рис. 9.6.

Рис. 9.6. Мультиплексор, управляемый двоичным кодом

Как отмечено выше, мультиплексор на основе КМОП-транзисторов может быть использован для коммутации аналоговых сигналов. Поскольку аналоговые сигналы, в общем случае, могут быть двуполярными, современные мультиплексоры могут быть запитаны как от однополярного, так и от двуполярного источника напряжения. Причём напряжения питания могут быть несимметричны. При любом варианте подключения питания (одно- или двуполярного) необходимо, чтобы диапазон амплитуд коммутируемых аналоговых сигналов укладывался в диапазон от –Uпит до + Uпит.

Реальные схемы мультиплексоров обычно содержат на входах и выходах дополнительные логические элементы. Только в этом случае цифровая схема в целом будет функционировать правильно и надёжно. Обычно эти элементы уже заложены в схемы серийно выпускаемых ИС мультиплексоров.

В мультиплексоре требуется подключать к выходу только один из входных сигналов. Точно так же, как и в ТТЛ-микросхемах, для управления электронными ключами двоичным кодом в состав мультиплексора вводится дешифратор. Схема такого мультиплексора приведена на рис. 9.6.

В отечественных микросхемах мультиплексоры обозначаются буквами КП, следующими непосредственно за номером серии микросхем. Например, микросхема К1533КП2 является сдвоенным четырехканальным мультиплексором, выполненным по ТТЛ-технологии, а микросхема К1561КП1 является сдвоенным четырехканальным мультиплексором, выполненным по КМОП-техно-логии.

Условное графическое обозначение мультиплексоров не зависит от технологии изготовления микросхем, т. е. КМОП-мультиплексор обозначается точно так же, как это приведено на рис. 9.2.

Микросхемы К561КП1 и КР1561КП1 содержат по два четырехвходовых мультиплексора. Микросхемы имеют два адресных входа 1 и 2, общие для обоих мультиплексоров, общий вход стробирования S, информационные входы ХО – ХЗ первого мультиплексора и его выход, входы Y0 – Y3 второго мультиплексора и его выход. Два варианта изображения микросхемы КП1 приведены на рис. 9.7.

Рис. 9.7 Мультиплексоры К561КП1 и К1561КП1:

а – структурная схема; б – условное изображение

При подаче на адресные входы 1 и 2 двоичного кода адреса и на вход S логического 0 выходы мультиплексоров соединяются со входами, номера которых соответствуют десятичному эквиваленту кода адреса. Если на входе S логическая 1, выходы мультиплексоров отключаются от входов и переходят в высокоимпедансное состояние. Соединение входов с выходом в мультиплексорах К176КП1, К561КПЗ и КР1561КПЗ осуществляется двунаправленными ключами на КМОП-транзисторах, схемы которых аналогичны приведённым на рис. 9.5. Передаваемый через мультиплексор сигнал может быть как аналоговым, так и цифровым. Он может передаваться как со входов на выход (микросхема работает в режиме мультиплексора), так и с выхода распределяться на входы (режим демультиплексора).

Кроме подключения к выходу одного из входов, заданного его адресом, мультиплексоры применяют для мультиплексирования шин (см. рис. 8.5). Мультиплексирование шин – это поочередное переключение шин (групп линий) от нескольких источников информации к одному приемнику. Такие функции выполняются схемами на основе коммутаторов одиночных линий. Количество мультиплексоров определяется числом источников информации (количеством коммутируемых шин), а разрядность мультиплексоров – разрядностью коммутируемых шин.

Мультиплексоры и демультиплексоры

<Мультиплексор ><(MS)><—><это><функциональный><узел,><осуществляющий><подключение><(коммутацию)><одного><из><нескольких><входов><данных><к><выходу.><Номер><выбранного><входа><соответствует><коду,><поданному><на><адресные><входы><мультиплексора.><Условное><изобра><жение><мультиплексора><на><четыре><входа><и><возможный><вариант><его><структурной><схемы><показаны><на><рис.><2.9,><а,>б.

<При состоянии адресных входов 00><><><><(код><адреса><х2><=><0,><х><1><><=><0)><у><=><а; при состоянии><><><01><(x2=><><0,><х><1><><=1)у><><=><><b; при состоянии><><><10><(х2><=><1,х><1><><=><0)><у><=><с;><в><положении><11><(x2><=><l,x><1><><=><1)><у><=d.><Функционирование><мультиплексора><описывается><выражением:>

<>

<>

<Вход><Е><—><разрешающий:><при><Е=><><1><мультиплексор><работает><как><обычно,><при><Е><=><0 его><выход><><находится><в><неактивном><состоянии,><мультиплексор>заперт.

Рисунок 2.9 — Мультиплексор из 4 в 1: а — условное обозначение; б — внутренняя структура

<><Серийные><ИМС><выпускаются><с><числом><адресных><входов><n><=><2,><3><и><4><при><возмож><ном><числе><2n><><><коммутируемых><входов (рис. 2.10).><При><необходимости><коммутировать><большее><количество><входов><используют><несколько><мультиплексоров.>

Рисунок 2.10 — Мультиплексоры разной размерности

<Мультиплексоры><находят><широкое><применение><в><устройствах><отображения><инфор><мации><в><различных><микропроцессорных><устройствах><управления><и><ЭВМ.>

<Демультиплексоры><выполняют><функцию,><обратную><мультиплексорам,><т.><е.><произ><водят><коммутацию><одного><входного><сигнала><на><2n><выходов,><где><n><—><число><адресных><входов><xi.><Они могут><осуществлять><преобразование><информации><из><последовательной><фор><мы><(последовательно-параллельной)><в><параллельную.><Демультиплексор><имеет><один><информационный><вход><D><и><несколько><выходов,><причем><вход><подключается><к><выходу><yi><имеющему адрес,><заданный кодом на адресных входах><.>

<В><качестве><примера><на><рис.><2.11,><а><дано><условное><графическое><обозначение><демуль><типлексора><(DMS),><имеющего><четыре><выхода,><закон><функционирования><которого><задан><(><табл.><2.2).><Пользуясь><таблицей><2.2,><запишем><переключательные><функ><ции><для><выхода><устройства:>

<><.>

<><.>

<Функциональная><схема><демультиплексора,><реализующая><эти><выражения,><приведена><на><рис.><2.11,>б.

а б

<Рисунок ><2.11 — Демультиплексор 1-4: а — условное обозначение; б — внутренняя структура>

Таблица 2.2 — Таблица истинности демультиплексора 1–4

<D> | <x2> | <х1> | <y3> | <y2> | <y1> | <y0> |

<1> | <0> | <0> | <0> | <0> | <0> | <1> |

<1> | <0> | <1> | <0> | <0> | <1> | <0> |

<1> | <1> | <0> | <0> | <1> | <0> | <0> |

<1> | <1> | <1> | <1> | <0> | <0> | <0> |

<Функции><демультиплексоров><сходны><с><функциями><де><шифраторов.><Дешифратор><можно><рассматривать><как><де><мультиплексор,><у><которого><информационный><вход><под><держивает><напряжение><выходов><в><активном><состоянии,><а><адресные><входы><выполняют><роль><входов><дешифратора.><Поэтому><в><обозначении><как><дешифраторов,><так><и><демуль><типлексоров><используются><одинаковые><буквы><—><ИД.><Вы><пускают><дешифраторы><(демультиплексоры)><К155ИДЗ,><К531ИД7 и др.><><>

<Так, ><если ><в ><дешифраторе ><КР531ИД14А (рис. 2.13) ><вход ><разреше><ния ><Е использовать как вход данных, ><><><><><><><><><><><><><><а ><информационные ><входы ><де><шифратора ><считать ><за ><адресные ><входы ><демультиплексора, ><то ><получим ><демультиплексор ><1><><4, который работает аналогично демультиплексору рис. 2.11 (за небольшим исключением — у этих устройств разные пассивные уровни выходов)><><><.>

Рисунок 2.12 — Демультиплексоры