6. Логические элементы компьютера.

Дискретный преобразователь, который после обработки входных двоичных сигналов выдаёт на выходе сигнал, являющийся значением одной из логических операций, называется логическим элементом.

Ниже приведены условные обозначения (схемы) базовых логических элементов, реализующих логическое умножение (конъюнктор), логическое сложение (дизъюнктор) и отрицание (инвертор).

Рис. Конъюнктор, дизъюнктор и инвертор

Устройства компьютера (сумматоры в процессоре, ячейки памяти в оперативной памяти и др.) строятся на основе базовых логических элементов.

Сегодня мы изучим еще один способ представления логических выражений – логические схемы.

Существует три базовых логических элемента, которые реализуют рассмотренные нами три основные логические операции:

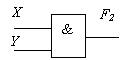

логический элемент «И» — логическое умножение – конъюнктор;

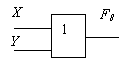

логический элемент «ИЛИ» — логическое сложение – дизъюнктор;

логический элемент «НЕ» — инверсию – инвертор.

Поскольку любая логическая операция может быть представлена в виде комбинации трех основных, любые устройства компьютера, производящие обработку или хранение информации, могут быть собраны из базовых логических элементов, как из “кирпичиков”.

Логические элементы компьютера оперируют с сигналами, представляющими собой электрические импульсы. Есть импульс — логический смысл сигнала — 1, нет импульса — 0. На входы логического элемента поступают сигналы-значения аргументов, на выходе появляется сигнал-значение функции.

Преобразование сигнала логическим элементом задается таблицей состояний, которая фактически является таблицей истинности, соответствующей логической функции, только представлена в форме логических схем. В такой форме удобно изображать цепочки логических операций и производить их вычисления.

Пример 1. По

заданной логической функции F(A, B) = B& Ú

Ú &A построить

логическую схему.

&A построить

логическую схему.

Построение необходимо начинать с логической операции, которая должна выполняться последней. В данном случае такой операцией является логическое сложение, следовательно, на выходе логической схемы должен быть дизъюнктор. На него сигналы подаются с двух конъюнкторов, на которые, в свою очередь подаются один входной сигнал нормальный и один инвертированный (с инверторов).

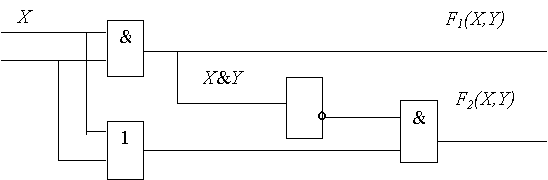

Пример 2. Логическая схема имеет два входа X и Y. Определить логические функции F1(X,Y) и F2(X,Y), которые реализуются на ее двух выходах.

Функция F1(X,Y) реализуется на выходе первого конъюнктора, т.е. F1(X,Y) = X&Y.

Одновременно

сигнал с конъюнктора подается на вход

инвертора, на выходе которого реализуется

сигнал  ,

который, в свою очередь, подается на

один из входов второго конъюнктора.

,

который, в свою очередь, подается на

один из входов второго конъюнктора.

На другой вход второго конъюнктора подается сигнал XÚ

& (XÚY).

& (XÚY).

Рассмотрим схему сложения двух n-разрядных двоичных чисел. При сложении цифр i-го разряда складываются аi и bi, а также pi-1 — перенос из i-1разряда. Результатом будет si – сумма и pi — перенос в старший разряд. Таким образом, одноразрядный двоичный сумматор — это устройство с тремя входами и двумя выходами.

Пример 3. Построить таблицу истинности одноразрядного двоичного сумматора, воспользовавшись таблицей сложения двоичных чисел.

Входы Выходы

Ai Bi Pi-1 Si Pi

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Логические элементы компьютера

В 1938 году была опубликована магистерская диссертация (1937 года) Клода Шеннона «Символьный анализ реле и коммутаторов». В публикации Шеннон представил работу релейных схем с помощью булевой алгебры и двоичной арифметики, тем самым по сути заложив основы цифровой техники.

Устройства компьютера, предназначенные для выполнения арифметических и логических операций можно рассматривать как преобразователь, который получает на входы двоичные сигналы, а на выходе новую двоичную последовательность.

Определение. Дискретный преобразователь, который выдает после обработки двоичных сигналов значение одной из логических операций, называется логическим элементом (вентилем).

Логические элементы преобразуют сигнал в соответствие с таблицей состояния, которая по сути является таблицей истинности реализуемой логической функции.

Любую логическую функцию можно представить с помощью базиса «НЕ», «И» и «ИЛИ». Таким образом, для реализации сложных логических функций будет достаточно комбинаций трех элементов, реализующих указанные операции:

- Логический элемент «И» (конъюнктор) реализует операцию конъюнкции.

- Логический элемент «ИЛИ» (дизъюнктор) реализует операцию дизъюнкции.

- Логический элемент «НЕ» (инвертор) реализует операцию дизъюнкции.

В микроэлектронике базовыми также являются

Для обозначения логических элементов в компьютерной схемотехнике используются несколько стандартов. Наиболее распространенными являются международный (IEC), российский (ГОСТ), американский (ANSI) и европейский (DIN).

Согласно ГОСТ 2.743-91 условные графические обозначения в электронных схемах простейших логических элементов выглядят следующим образом:

Небольшой кружок на выходе (или на входе) условного обозначения логического элемента означает операцию «НЕ».

5.3. Какая связь между алгеброй логики и двоичным кодированием? 5.5. Что такое логический элемент компьютера?

Математический аппарат алгебры логики очень удобен для описания того, как функционируют аппаратные средства компьютера, поскольку основной системой счисления в компьютере является двоичная, в которой используются цифры 1 и 0, а значений логических переменных тоже два: «1» и «0».

Из этого следует два вывода:

-

1. одни

и те же устройства компьютера могут применяться для обработки и

хранения как числовой информации, представленной в двоичной системе

счисления, так и логических переменных;

2. на этапе конструирования аппаратных средств алгебра логики позволяет значительно упростить логические функции, описывающие функционирование схем компьютера, и, следовательно, уменьшить число элементарных логических элементов, из десятков тысяч которых состоят основные узлы компьютера.

5.4. В каком виде записываются в памяти компьютера и в регистрах процессора данные и команды?

Данные и команды представляются в виде двоичных последовательностей различной структуры и длины.

Существуют различные физические способы кодирования двоичной информации, но чаще всего единица кодируется более высоким уровнем напряжения, чем ноль (или наоборот), например:

5.5. Что такое логический элемент компьютера?

| Логический элемент компьютера |

Логическими элементами компьютеров являются электронные схемы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и другие (называемые также вентилями), а также триггер.

С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у вентилей бывает от двух до восьми входов и один или два выхода.

Чтобы представить два логических состояния — «1» и «0» в вентилях, соответствующие им входные и выходные сигналы имеют один из двух установленных уровней напряжения. Например, +5 вольт и 0 вольт.

Высокий уровень обычно соответствует значению «истина» («1»), а низкий — значению «ложь» («0»).

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Это упрощает запись и понимание сложных логических схем.

Работу логических элементов описывают с помощью таблиц истинности.

Таблица истинности это табличное представление логической схемы (операции), в котором перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значением истинности выходного сигнала (результата операции) для каждого из этих сочетаний.

Что такое логический элемент компьютера?

| Логический элемент компьютера — это часть электронной логичеcкой схемы, которая реализует элементарную логическую функцию. |

Логическими элементами компьютеров являются электронные схемы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и другие (называемые также вентилями), а также триггер.

С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у вентилей бывает от двух до восьми входов и один или два выхода.

Чтобы представить два логических состояния — “1” и “0” в вентилях, соответствующие им входные и выходные сигналы имеют один из двух установленных уровней напряжения. Например, +5 вольт и 0 вольт.

Высокий уровень обычно соответствует значению “истина” (“1”), а низкий — значению “ложь” (“0”).

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Это упрощает запись и понимание сложных логических схем.

Работу логических элементов описывают с помощью таблиц истинности.

| Таблица истинности это табличное представление логической схемы (операции), в котором перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значением истинности выходного сигнала (результата операции) для каждого из этих сочетаний. |

Что такое схемы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ?

С х е м а И

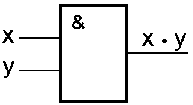

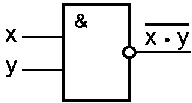

Схема И реализует конъюнкцию двух или более логических значений.

Условное обозначение на структурных схемах схемы И с двумя входами представлено на рис. 5.1. Таблица истинности — в таблице 5.1.

Рис. 5.1

Таблица 5.1

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль.

Связь между выходом z этой схемы и входами x и y описывается соотношением: z = xЧy (читается как «x и y»).

Операция конъюнкции на функциональных схемах обозначается знаком “&” (читается как «амперсэнд»), являющимся сокращенной записью английского слова and.

С х е м а ИЛИ

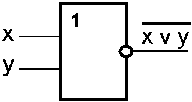

Схема ИЛИ реализует дизъюнкцию двух или более логических значений.

Когда хотя бы на одном входе схемы ИЛИ будет единица, на её выходе также будет единица.

Условное обозначение схемы ИЛИ представлено на рис. 5.2. Знак “1” на схеме — от устаревшего обозначения дизъюнкции как «>=1» (т.е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1). Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x v y (читается как «x или y«). Таблица истинности — в табл. 5.2.

Рис. 5.2

Таблица 5.2

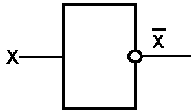

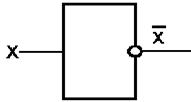

С х е м а НЕ

Схема НЕ (инвертор) реализует операцию отрицания. Связь между входом x этой схемы и выходом z можно записать соотношением z =, где читается как «не x» или «инверсия х«.

Если на входе схемы 0, то на выходе 1. Когда на входе 1, на выходе 0. Условное обозначение инвертора — на рисунке 5.3, а таблица истинности — в табл. 5.3.

Рис. 5.3

Таблица 5.3

| x | |

С х е м а И — НЕ

Схема И-НЕ состоит из элемента И и инвертора и осуществляет отрицание результата схемы И.

Связь между выходом z и входами x и y схемы записывают следующим образом:, где читается как «инверсия x и y«.

Условное обозначение схемы И-НЕ представлено на рисунке 5.4. Таблица истинности схемы И-НЕ — в табл. 5.4.

Рис. 5.4

Таблица 5.4

С х е м а ИЛИ — НЕ

Схема ИЛИ-НЕ состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата схемы ИЛИ.

Связь между выходом z и входами x и y схемы записывают следующим образом:, где, читается как «инверсия x или y«. Условное обозначение схемы ИЛИ-НЕ представлено на рис. 5.5.

Таблица истинности схемы ИЛИ-НЕ — в табл. 5.5.

Рис. 5.5

Таблица 5.5

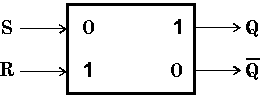

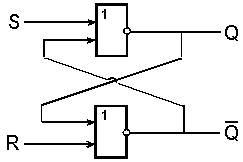

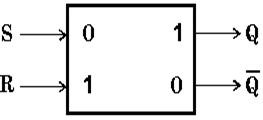

Что такое триггер?

| Триггер — это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю. |

Термин триггер происходит от английского слова trigger — защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает “хлопанье”. Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить (“перебрасываться”) из одного электрического состояния в другое и наоборот.

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс). Условное обозначение триггера — на рис. 5.6.

Рис. 5.6

Он имеет два симметричных входа S и R и два симметричных выхода Q и, причем выходной сигнал Q является логическим отрицанием сигнала.

На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов ().

Наличие импульса на входе будем считать единицей, а его отсутствие — нулем.

На рис. 5.7 показана реализация триггера с помощью вентилей ИЛИ-НЕ и соответствующая таблица истинности.

Рис. 5.7

| S | R | Q | |

| запрещено | |||

| хранение бита |

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ-НЕ (табл. 5.5).

1. Если на входы триггера подать S=“1”, R=“0”, то (независимо от состояния) на выходе Q верхнего вентиля появится “0”. После этого на входах нижнего вентиля окажется R=“0”, Q=“0” и выход станет равным “1”.

2. Точно так же при подаче “0” на вход S и “1” на вход R на выходе появится “0”, а на Q — “1”.

3. Если на входы R и S подана логическая “1”, то состояние Q и не меняется.

4. Подача на оба входа R и S логического “0” может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 • 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

Что такое сумматор?

| Сумматор — это электронная логическая схема, выполняющая суммирование двоичных чисел. |

Сумматор служит, прежде всего, центральным узлом арифметико-логического устройства компьютера, однако он находит применение также и в других устройствах машины.

Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров, с рассмотрения которых мы и начнём. Условное обозначение одноразрядного сумматора на рис. 5.8.

Рис. 5.8

При сложении чисел A и B в одном i-ом разряде приходится иметь дело с тремя цифрами:

1. цифра ai первого слагаемого;

2. цифра bi второго слагаемого;

3. перенос pi–1 из младшего разряда.

В результате сложения получаются две цифры:

1. цифра ci для суммы;

2. перенос pi из данного разряда в старший.

Таким образом, одноразрядный двоичный сумматор есть устройство с тремя входами и двумя выходами, работа которого может быть описана следующей таблицей истинности:

| Входы | Выходы | |||

| Первое слагаемое | Второе слагаемое | Перенос | Сумма | Перенос |

Если требуется складывать двоичные слова длиной два и более бит, то можно использовать последовательное соединение таких сумматоров, причём для двух соседних сумматоров выход переноса одного сумматора является входом для другого.

Например, схема вычисления суммы C = (с3 c2 c1 c0) двух двоичных трехразрядных чисел A = (a2 a1 a0) и B = (b2 b1 b0) может иметь вид:

Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

Что такое логический элемент компьютера?

| Логический элемент компьютера — это часть электронной логичеcкой схемы, которая реализует элементарную логическую функцию. |

Логическими элементами компьютеров являются электронные схемы И, ИЛИ, НЕ, И—НЕ, ИЛИ—НЕ и другие (называемые также вентилями), а также триггер.

С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у вентилей бывает от двух до восьми входов и один или два выхода.

Чтобы представить два логических состояния — “1” и “0” в вентилях, соответствующие им входные и выходные сигналы имеют один из двух установленных уровней напряжения. Например, +5 вольт и 0 вольт.

Высокий уровень обычно соответствует значению “истина” (“1”), а низкий — значению “ложь” (“0”).

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Это упрощает запись и понимание сложных логических схем.

Работу логических элементов описывают с помощью таблиц истинности.

| Таблица истинности это табличное представление логической схемы (операции), в котором перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значением истинности выходного сигнала (результата операции) для каждого из этих сочетаний. |

Что такое схемы И, ИЛИ, НЕ, И—НЕ, ИЛИ—НЕ?

С х е м а И

Схема И реализует конъюнкцию двух или более логических значений. Условное обозначение на структурных схемах схемы И с двумя входами представлено на рис. 5.1.

Рис. 5.1

Таблица истинности схемы И

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль.

Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x . y

(читается как «x и y»). Операция конъюнкции на структурных схемах обозначается знаком «&» (читается как «амперсэнд»), являющимся сокращенной записью английского слова and.

С х е м а ИЛИ

Схема ИЛИ реализует дизъюнкцию двух или более логических значений. Когда хотя бы на одном входе схемы ИЛИ будет единица, на её выходе также будет единица.

Условное обозначение на структурных схемах схемы ИЛИ с двумя входами представлено на рис. 5.2. Знак «1» на схеме — от устаревшего обозначения дизъюнкции как «>=1» (т.е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1). Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x v y (читается как «x или y»).

Рис. 5.2

Таблица истинности схемы ИЛИ

С х е м а НЕ

Схема НЕ (инвертор) реализует операцию отрицания. Связь между входом x этой схемы и выходом z можно записать соотношением z =  , x где

, x где  читается как «не x» или «инверсия х».

читается как «не x» или «инверсия х».

Если на входе схемы 0, то на выходе 1. Когда на входе 1, на выходе 0. Условное обозначение на структурных схемах инвертора — на рисунке 5.3

Рис. 5.3

Таблица истинности схемы НЕ

| x |  |

С х е м а И—НЕ

Схема И—НЕ состоит из элемента И и инвертора и осуществляет отрицание результата схемы И. Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  читается как «инверсия x и y». Условное обозначение на структурных схемах схемы И—НЕ с двумя входами представлено на рисунке 5.4.

читается как «инверсия x и y». Условное обозначение на структурных схемах схемы И—НЕ с двумя входами представлено на рисунке 5.4.

Рис. 5.4

Таблица истинности схемы И—НЕ

| x | y |  |

С х е м а ИЛИ—НЕ

Схема ИЛИ—НЕ состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата схемы ИЛИ. Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  , читается как «инверсия x или y «. Условное обозначение на структурных схемах схемы ИЛИ—НЕ с двумя входами представлено на рис. 5.5.

, читается как «инверсия x или y «. Условное обозначение на структурных схемах схемы ИЛИ—НЕ с двумя входами представлено на рис. 5.5.

Рис. 5.5

Таблица истинности схемы ИЛИ—НЕ

| x | y |  |

Что такое триггер?

| Триггер — это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю. |

Термин триггер происходит от английского слова trigger — защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает “хлопанье”. Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить (“перебрасываться”) из одного электрического состояния в другое и наоборот.

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс). Условное обозначение триггера — на рис. 5.6.

Рис. 5.6

Он имеет два симметричных входа S и R и два симметричных выхода Q и  , причем выходной сигнал Q является логическим отрицанием сигнала

, причем выходной сигнал Q является логическим отрицанием сигнала  .

.

На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов (  ).

).

Наличие импульса на входе будем считать единицей, а его отсутствие — нулем.

На рис. 5.7 показана реализация триггера с помощью вентилей ИЛИ—НЕ и соответствующая таблица истинности.

Рис. 5.7

| S | R | Q |  |

| запрещено | |||

| хранение бита |

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ—НЕ (табл. 5.5).

1. Если на входы триггера подать S=“1”, R=“0”, то (независимо от состояния) на выходе Q верхнего вентиля появится “0”. После этого на входах нижнего вентиля окажется R=“0”, Q=“0” и выход  станет равным “1”.

станет равным “1”.

2. Точно так же при подаче “0” на вход S и “1” на вход R на выходе  появится “0”, а на Q — “1”.

появится “0”, а на Q — “1”.

3. Если на входы R и S подана логическая “1”, то состояние Q и  не меняется.

не меняется.

4. Подача на оба входа R и S логического “0” может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 х 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

Дата добавления: 2016-05-31; просмотров: 1818;

Похожие статьи:

Что такое логический элемент компьютера?

⇐ ПредыдущаяСтр 2 из 2| Логический элемент компьютера — это часть электронной логичеcкой схемы, которая реализует элементарную логическую функцию. |

Логическими элементами компьютеров являются электронные схемы И, ИЛИ, НЕ, И—НЕ, ИЛИ—НЕ и другие (называемые также вентилями), а также триггер.

С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у вентилей бывает от двух до восьми входов и один или два выхода.

Чтобы представить два логических состояния — “1” и “0” в вентилях, соответствующие им входные и выходные сигналы имеют один из двух установленных уровней напряжения. Например, +5 вольт и 0 вольт.

Высокий уровень обычно соответствует значению “истина” (“1”), а низкий — значению “ложь” (“0”).

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Это упрощает запись и понимание сложных логических схем.

Работу логических элементов описывают с помощью таблиц истинности.

| Таблица истинности это табличное представление логической схемы (операции), в котором перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значением истинности выходного сигнала (результата операции) для каждого из этих сочетаний. |

Что такое схемы И, ИЛИ, НЕ, И—НЕ, ИЛИ—НЕ?

С х е м а И

Схема И реализует конъюнкцию двух или более логических значений. Условное обозначение на структурных схемах схемы И с двумя входами представлено на рис. 5.1.

Рис. 5.1

Таблица истинности схемы И

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль.

Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x . y

(читается как «x и y»). Операция конъюнкции на структурных схемах обозначается знаком «&» (читается как «амперсэнд»), являющимся сокращенной записью английского слова and.

С х е м а ИЛИ

Схема ИЛИ реализует дизъюнкцию двух или более логических значений. Когда хотя бы на одном входе схемы ИЛИ будет единица, на её выходе также будет единица.

Условное обозначение на структурных схемах схемы ИЛИ с двумя входами представлено на рис. 5.2. Знак «1» на схеме — от устаревшего обозначения дизъюнкции как «>=1» (т.е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1). Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x v y (читается как «x или y»).

Рис. 5.2

Таблица истинности схемы ИЛИ

С х е м а НЕ

Схема НЕ (инвертор) реализует операцию отрицания. Связь между входом x этой схемы и выходом z можно записать соотношением z =  , x где

, x где  читается как «не x» или «инверсия х».

читается как «не x» или «инверсия х».

Если на входе схемы 0, то на выходе 1. Когда на входе 1, на выходе 0. Условное обозначение на структурных схемах инвертора — на рисунке 5.3

Рис. 5.3

Таблица истинности схемы НЕ

| x |  |

С х е м а И—НЕ

Схема И—НЕ состоит из элемента И и инвертора и осуществляет отрицание результата схемы И. Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  читается как «инверсия x и y». Условное обозначение на структурных схемах схемы И—НЕ с двумя входами представлено на рисунке 5.4.

читается как «инверсия x и y». Условное обозначение на структурных схемах схемы И—НЕ с двумя входами представлено на рисунке 5.4.

Рис. 5.4

Таблица истинности схемы И—НЕ

| x | y |  |

С х е м а ИЛИ—НЕ

Схема ИЛИ—НЕ состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата схемы ИЛИ. Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  , читается как «инверсия x или y «. Условное обозначение на структурных схемах схемы ИЛИ—НЕ с двумя входами представлено на рис. 5.5.

, читается как «инверсия x или y «. Условное обозначение на структурных схемах схемы ИЛИ—НЕ с двумя входами представлено на рис. 5.5.

Рис. 5.5

Таблица истинности схемы ИЛИ—НЕ

| x | y |  |

Что такое триггер?

| Триггер — это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю. |

Термин триггер происходит от английского слова trigger — защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает “хлопанье”. Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить (“перебрасываться”) из одного электрического состояния в другое и наоборот.

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс). Условное обозначение триггера — на рис. 5.6.

Рис. 5.6

Он имеет два симметричных входа S и R и два симметричных выхода Q и  , причем выходной сигнал Q является логическим отрицанием сигнала

, причем выходной сигнал Q является логическим отрицанием сигнала  .

.

На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов (  ).

).

Наличие импульса на входе будем считать единицей, а его отсутствие — нулем.

На рис. 5.7 показана реализация триггера с помощью вентилей ИЛИ—НЕ и соответствующая таблица истинности.

Рис. 5.7

| S | R | Q |  |

| запрещено | |||

| хранение бита |

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ—НЕ (табл. 5.5).

- Если на входы триггера подать S=“1”, R=“0”, то (независимо от состояния) на выходе Q верхнего вентиля появится “0”. После этого на входах нижнего вентиля окажется R=“0”, Q=“0” и выход

станет равным “1”.

станет равным “1”. - Точно так же при подаче “0” на вход S и “1” на вход R на выходе

появится “0”, а на Q — “1”.

появится “0”, а на Q — “1”. - Если на входы R и S подана логическая “1”, то состояние Q и

не меняется.

не меняется. - Подача на оба входа R и S логического “0” может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 х 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

Что такое сумматор?

| Сумматор — это электронная логическая схема, выполняющая суммирование двоичных чисел. |

Сумматор служит, прежде всего, центральным узлом арифметико-логического устройства компьютера, однако он находит применение также и в других устройствах машины.

Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров, с рассмотрения которых мы и начнём. Условное обозначение одноразрядного сумматора на рис. 5.8.

Рис. 5.8

При сложении чисел A и B в одном i-ом разряде приходится иметь дело с тремя цифрами:

1. цифра ai первого слагаемого;

2. цифра bi второго слагаемого;

3. перенос pi–1 из младшего разряда.

В результате сложения получаются две цифры:

1. цифра ci для суммы;

2. перенос pi из данного разряда в старший.

Таким образом, одноразрядный двоичный сумматор есть устройство с тремя входами и двумя выходами, работа которого может быть описана следующей таблицей истинности:

| Входы | Выходы | |||

| Первое слагаемое | Второе слагаемое | Перенос | Сумма | Перенос |

Если требуется складывать двоичные слова длиной два и более бит, то можно использовать последовательное соединение таких сумматоров, причём для двух соседних сумматоров выход переноса одного сумматора является входом для другого.

Например, схема вычисления суммы C = (с3 c2 c1 c0) двух двоичных трехразрядных чисел A = (a2 a1 a0) и B = (b2 b1 b0) может иметь вид:

⇐ Предыдущая12

Что такое логический элемент компьютера?

⇐ ПредыдущаяСтр 2 из 4Следующая ⇒

| Логический элемент компьютера — это часть электронной логичеcкой схемы, которая реализует элементарную логическую функцию. |

Логическими элементами компьютеров являются электронные схемы И, ИЛИ, НЕ, И—НЕ, ИЛИ—НЕ и другие (называемые также вентилями), а также триггер.

С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у вентилей бывает от двух до восьми входов и один или два выхода.

Чтобы представить два логических состояния — “1” и “0” в вентилях, соответствующие им входные и выходные сигналы имеют один из двух установленных уровней напряжения. Например, +5 вольт и 0 вольт.

Высокий уровень обычно соответствует значению “истина” (“1”), а низкий — значению “ложь” (“0”).

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Это упрощает запись и понимание сложных логических схем.

Работу логических элементов описывают с помощью таблиц истинности.

| Таблица истинности это табличное представление логической схемы (операции), в котором перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значением истинности выходного сигнала (результата операции) для каждого из этих сочетаний. |

Что такое схемы И, ИЛИ, НЕ, И—НЕ, ИЛИ—НЕ?

С х е м а И

Схема И реализует конъюнкцию двух или более логических значений. Условное обозначение на структурных схемах схемы И с двумя входами представлено на рис. 5.1.

Рис. 5.1

Таблица истинности схемы И

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль.

Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x . y

(читается как «x и y»). Операция конъюнкции на структурных схемах обозначается знаком «&» (читается как «амперсэнд»), являющимся сокращенной записью английского слова and.

С х е м а ИЛИ

Схема ИЛИ реализует дизъюнкцию двух или более логических значений. Когда хотя бы на одном входе схемы ИЛИ будет единица, на её выходе также будет единица.

Условное обозначение на структурных схемах схемы ИЛИ с двумя входами представлено на рис. 5.2. Знак «1» на схеме — от устаревшего обозначения дизъюнкции как «>=1» (т.е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1). Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x v y (читается как «x или y»).

Рис. 5.2

Таблица истинности схемы ИЛИ

С х е м а НЕ

Схема НЕ (инвертор) реализует операцию отрицания. Связь между входом x этой схемы и выходом z можно записать соотношением z =  , x где

, x где  читается как «не x» или «инверсия х».

читается как «не x» или «инверсия х».

Если на входе схемы 0, то на выходе 1. Когда на входе 1, на выходе 0. Условное обозначение на структурных схемах инвертора — на рисунке 5.3

Рис. 5.3

Таблица истинности схемы НЕ

| x |  |

С х е м а И—НЕ

Схема И—НЕ состоит из элемента И и инвертора и осуществляет отрицание результата схемы И. Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  читается как «инверсия x и y». Условное обозначение на структурных схемах схемы И—НЕ с двумя входами представлено на рисунке 5.4.

читается как «инверсия x и y». Условное обозначение на структурных схемах схемы И—НЕ с двумя входами представлено на рисунке 5.4.

Рис. 5.4

Таблица истинности схемы И—НЕ

| x | y |  |

С х е м а ИЛИ—НЕ

Схема ИЛИ—НЕ состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата схемы ИЛИ. Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  , читается как «инверсия x или y «. Условное обозначение на структурных схемах схемы ИЛИ—НЕ с двумя входами представлено на рис. 5.5.

, читается как «инверсия x или y «. Условное обозначение на структурных схемах схемы ИЛИ—НЕ с двумя входами представлено на рис. 5.5.

Рис. 5.5

Таблица истинности схемы ИЛИ—НЕ

| x | y |  |

Что такое триггер?

| Триггер — это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю. |

Термин триггер происходит от английского слова trigger — защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает “хлопанье”. Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить (“перебрасываться”) из одного электрического состояния в другое и наоборот.

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс). Условное обозначение триггера — на рис. 5.6.

Рис. 5.6

Он имеет два симметричных входа S и R и два симметричных выхода Q и  , причем выходной сигнал Q является логическим отрицанием сигнала

, причем выходной сигнал Q является логическим отрицанием сигнала  .

.

На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов (  ).

).

Наличие импульса на входе будем считать единицей, а его отсутствие — нулем.

На рис. 5.7 показана реализация триггера с помощью вентилей ИЛИ—НЕ и соответствующая таблица истинности.

Рис. 5.7

| S | R | Q |  |

| запрещено | |||

| хранение бита |

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ—НЕ (табл. 5.5).

- Если на входы триггера подать S=“1”, R=“0”, то (независимо от состояния) на выходе Q верхнего вентиля появится “0”. После этого на входах нижнего вентиля окажется R=“0”, Q=“0” и выход

станет равным “1”.

станет равным “1”. - Точно так же при подаче “0” на вход S и “1” на вход R на выходе

появится “0”, а на Q — “1”.

появится “0”, а на Q — “1”. - Если на входы R и S подана логическая “1”, то состояние Q и

не меняется.

не меняется. - Подача на оба входа R и S логического “0” может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 х 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

Что такое сумматор?

| Сумматор — это электронная логическая схема, выполняющая суммирование двоичных чисел. |

Сумматор служит, прежде всего, центральным узлом арифметико-логического устройства компьютера, однако он находит применение также и в других устройствах машины.

Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров, с рассмотрения которых мы и начнём. Условное обозначение одноразрядного сумматора на рис. 5.8.

Рис. 5.8

При сложении чисел A и B в одном i-ом разряде приходится иметь дело с тремя цифрами:

1. цифра ai первого слагаемого;

2. цифра bi второго слагаемого;

3. перенос pi–1 из младшего разряда.

В результате сложения получаются две цифры:

1. цифра ci для суммы;

2. перенос pi из данного разряда в старший.

Таким образом, одноразрядный двоичный сумматор есть устройство с тремя входами и двумя выходами, работа которого может быть описана следующей таблицей истинности:

| Входы | Выходы | |||

| Первое слагаемое | Второе слагаемое | Перенос | Сумма | Перенос |

Если требуется складывать двоичные слова длиной два и более бит, то можно использовать последовательное соединение таких сумматоров, причём для двух соседних сумматоров выход переноса одного сумматора является входом для другого.

Например, схема вычисления суммы C = (с3 c2 c1 c0) двух двоичных трехразрядных чисел A = (a2 a1 a0) и B = (b2 b1 b0) может иметь вид:

Рекомендуемые страницы: